國立交通大學

電機與控制工程學系

碩 士 論 文

功率積體電路之接面隔離研究

Study on the Junction Isolation of

Power Integrated Circuits

研 究 生:蘇建仁

功率積體電路之接面隔離研究

Study on the Junction Isolation of

Power Integrated Circuits

學 生:蘇建仁 Student : Chien-Jen Su

指導教授:張隆國 博士 Advisor : Dr. Lon-Kou Chang

國立交通大學 電機與控制工程學系

碩士論文

A Thesis

Submitted to Institute of Electrical and Control Engineering College of Electrical Engineering and Computer Science

National Chiao Tung University in Partial Fulfillment of the Requirements

for the Degree of Master in

Electrical and Control Engineering June 2000

Hsinchu, Taiwan, Republic of China

功率積體電路之接面隔離研究

研究生:蘇建仁 指導老師:張隆國博士

國立交通大學電機與控制工程學系

摘要

功率積體電路乃是把高壓功率元件和 CMOS 低壓元件,整合在同一晶 片上的積體電路,以提供使用者更完整的功能及更低廉的成本。但在整合 時高壓功率元件與低壓電路或高壓功率元件之間的串音問題,使得元件隔 離技術的發展成為功率積體電路設計上不可或缺的一環。本論文將針對此 關鍵技術進行整合高壓功率元件與 CMOS 低壓電路之接面隔離技術研 究。在接面隔離方面本論文藉由 N 型及 P 型保護環設計隔離結構。使用 MEDICI 電性模擬軟體模擬高壓功率元件在順向偏壓及反向偏壓下,不同 的隔離佈局參數及偏壓對漏電流的影響。調變的佈局參數包括元件 P-sink 寬度、元件間距離、隔離結構(N 型及 P 型保護環寬度)。論文中分析討論 各項參數對隔離效果的影響,並於文末列舉最佳隔離方式的選擇,以做為 將來設計功率積體電路時隔離結構設計的參考。Study on the Junction Isolation of

Power Integrated Circuits

Student: Chien-Jen Su Advisor: Dr. Lon-Kou Chang

Department of Electrical and Control Engineering

National Chiao-Tung University

ABSTRACT

Since Power Integrated Circuit( PIC ) combines power devices with low voltage CMOS logic circuits on the same chip, it offers more intact function, and cheaper cost. However, the cross-talk happens between the power device and CMOS circuits or between one power device and the others. Therefore, the development of the isolation technology is indispensable in the power integrated circuit design. This thesis studies the junction isolation functions held between the power devices and CMOS logic circuits. The N-type and P-type guard ring are used to be the isolation structure. MEDICI, a 2-D device simulator, is used to simulate the relation of the leakage current between the layout parameters and the bias of the isolation structure when the power device is in forward bias and reverse bias, respectively. The design parameters of the layout include the width of P-sink, the distance between devices, and the changes of the widths of the N-type and P-type guard ring. We have simulated and analyzed variety of isolation performance resulted in the changes of the layout parameters and the bias of the isolation structure. Finally, we propose the most proper isolation design for each combination of high and low power devices.

致謝

對於本論文能夠順利完成,首先要感謝我的指導教授張隆國老師,由 於他的指導和鼓勵,使我在研究工作遇到瓶頸時有能力和信心去突破,在 論文的內容上給予我豐富的建議,使本論文能夠更完整。 我要感謝我的父母,在我心情低落時給我的鼓勵跟支持,讓我沒有壓 力地處理研究的課業。同時也要感謝實驗室的阿暉學長、阿信學長及晏銘 學長,平時做研究的技術指導讓我獲益良多,還有實驗室的同學,阿修, 小右及高偉仁陪伴我一同學習、一同成長,一同經歷研究生活的種種酸甜 苦辣,並在課業上提供我的幫助。還要感謝實驗室的學弟們,在我準備口 試忙不過來時給我友情的贊助和幫忙,讓我能無後顧之憂地參加論文口 試。 感謝所有關心我的人,在此僅將本論文獻給他們。目錄

中文摘要 i 英文摘要 ii 誌謝 iii 目錄 iv 圖例 vi 表格 xv 第一章 緒論...1 1.1 研究動機...1 1.2 文獻回顧...2 1.3 論文架構...4 第二章 相關理論探討...5 2.1 高壓元件的操作原理 ...5 2.2 閂鎖效應的產生 ...7 2.3 PN 接面 ...8 2.3.1 零外加偏壓 ...9 2.3.2 反向偏壓 ...14 2.3.3 順向偏壓 ...16 2.4 PIN 二極體 ...16 2.5 雙極性電晶體...18 2.5.1 電晶體電流關係 ...20 2.5.2 操作模式 ...232.6 溫度效應...25 2.6.1 本徵載子濃度 ...25 2.6.2 載子遷移率 ...26 第三章 研究方法...28 3.1 軟體模擬規劃...28 3.2 實作驗證規劃...37 第四章 模擬結果與討論...38 4.1 順向偏壓...42 4.1.1 高壓整合 ...44 4.2 反向偏壓……….. ..56 4.2.1 高低壓整合 ...57 4.2.2 高壓整合 ...72 4.3 總結……… ...85 第五章 製程與佈局...88 5.1 製程及其模擬...88 5.2 佈局………..……...93 第六章 結論與展望...95 6.1 結論...95 6.2 展望………..……...95

圖例

圖 1.1 多磊晶層結構圖...3 圖 1.2 保護環隔離結構圖...3 圖 1.3 將埋藏層與保護環部份重疊示意圖 ...3 圖 1.4 示意圖 (a) 利用 BJT 防制漏電流 ...4 (b) 利用控制電路及 MOS 防制漏電流 ...4 圖 2.1 LDMOS 結構示意圖...6 圖 2.2 LIGBT (a) 結構示意圖 ...6 (b) 等效電路圖...6 圖 2.3 SA-LIGBT (a) 結構示意圖 ...7 (b) 等效電路圖...7 圖 2.4 低壓電路寄生電路示意圖...7 圖 2.5 閂鎖效應等效電路圖...8 圖 2.6 PN 接面的簡化幾何結構 ...9 圖 2.7 PN 接面的空乏區及電場圖 ...9 圖 2.8 PN 接面在熱平衡時能帶圖 ...9 圖 2.9 均勻 PN 接面及陡峭接面近似時空間電荷密度圖 ...11 圖 2.10 空乏區中的電場...12 圖 2.11 PN 接面中整個空乏區的電位...13 圖 2.12 反向偏壓 PN 接面能帶圖 ...14 圖 2.13 順向偏壓 PN 接面能帶圖 ...16圖 2.14 P-i-N 二極體與 PN 二極體空乏區及電場圖 ...17 圖 2.15 P-i-N 二極體正向導通波形...18 圖 2.16 P-i-N 二極體反向回復電流波形...18 圖 2.17 NPN 雙極性電晶體的理想化掺雜輪廓 ...19 圖 2.18 (a) NPN 雙極性電晶體在順向主動模式的偏壓 ...20 (b) NPN 雙極性電晶體在順向主動模式操作下少數載子分佈20 (c) NPN 雙極性電晶體在零偏壓及順向主動模式偏壓能帶圖 20 圖 2.19 順向偏壓的 NPN 雙極性電晶體中少數載子分佈及基本電流21 圖 2.20 在共射極電路中的一個 NPN 雙極性電晶體 ...23 圖 2.21 雙極性電晶體的共射極電流-電壓特性及負載線 ...24 圖 2.22 (a) 載子濃度與溫度關係圖 ...25 (b) 定性解釋載子濃度與溫度關係...25 圖 2.23 在各種掺雜濃度的矽中,載子遷移率與溫度關係圖 (a) 電子載子 ...27 (b) 電洞載子...27 圖 3.1 LDMOS 整合示意圖 (a) LDMOS 與低壓電路 ...29 (b) LDMOS 與 LDMOS...29 圖 3.2 LIGBT 整合示意圖 (a) LIGBT 與低壓電路 ...29 (b) LIGBT 與 LIGBT ...29 圖 3.3 SA-LIGBT 整合示意圖 (a) SA-LIGBT 與低壓電路...30 (b) SA-LIGBT 與 SA-LIGBT ...30

圖 3.4 順向偏壓時,漏電流示意圖 (a) 高低壓整合 ...31 (b) 高壓整合...31 圖 3.5 反向偏壓時,寄生等效電路圖 (a) 高低壓整合 ...32 (b) 高壓整合...32 圖 3.6 高壓整合中,改變元件間 N 型磊晶層偏壓示意圖...33 圖 3.7 高低壓整合中,改變高低壓元件間 N 型磊晶層偏壓示意圖 ..33 圖 3.8 調變佈局參數示意圖 (a) 高低壓整合 ...33 (b) 高壓整合...34 圖 3.9 調變隔離佈局參數示意圖 (a) 高低壓整合 ...34 (b) 高壓整合...34 圖 3.10 雙組隔離結構截面示意圖...35 圖 3.11 高低壓整合模擬基板漏電流流程圖...36 圖 4.1 MEDICI 結構圖 (a) 高低壓整合 ...38 (b) 高壓整合...38 圖 4.2 MEDICI 結構模擬圖 (a) CMOS 低壓電路...40 (b) LDMOS ...40 (c) LIGBT ...40 (d) SA-LIGBT...40

圖 4.3 LDMOS 導通時電流流密圖 (a) 高低壓整合 ...42 (b) 高壓整合...42 圖 4.4 高低壓整合,導通時電流流密圖 (a) LIGBT ...43 (b) SA-LIGBT...43 圖 4.5 高壓整合,導通時電流流密圖及等效電路圖 (a) LIGBT ...44 (b) SA-LIGBT...44 圖 4.6 高壓整合,元件間 N 型磊晶層不同偏壓比較 (a) LIGBT ...45 (b) SA-LIGBT...45 圖 4.7 LIGBT 高壓整合,元件間 N 型磊晶層不同偏壓電位圖及等效電路 圖 (a) 元件間 N 型磊晶層浮接 ...46 (b) 元件間 N 型磊晶層偏壓 5V ...46 圖 4.8 高壓整合,P-sink 寬度與漏電流關係圖 (a) LIGBT ...47 (b) SA-LIGBT...47 圖 4.9 高壓整合,元件間距離與漏電流關係圖 (a) LIGBT ...48 (b) SA-LIGBT...48 圖 4.10 高壓整合,隔離結構不同偏壓下,陽極電流與漏電流關係圖 (a) LIGBT ...49

圖 4.11 高壓整合 LIGBT 含隔離結構,P 型保護環不同偏壓電流流密及等 效電路圖 (a) N 型保護環浮接,P 型保護環浮接...50 (b) N 型保護環浮接,P 型保護環接地...50 圖 4.12 高壓整合 LIGBT 含隔離結構,N 型保護環不同偏壓電位圖及等效 電路圖 (a) N 型保護環浮接,P 型保護環接地...50 (b) N 型保護環偏壓在 5V,P 型保護環接地...50 圖 4.13 高壓整合含隔離結構,P-sink 寬度與漏電流關係圖 (a) LIGBT ...52 (b) SA- LIGBT...52 圖 4.14 高壓整合含隔離結構,N 型保護環寬度與漏電流關係圖 (a) LIGBT ...53 (b) SA-LIGBT...53 圖 4.15 高壓整合含隔離結構,P 型保護環寬度與漏電流關係圖 (a) LIGBT ...54 (b) SA-LIGBT...54 圖 4.16 相同面積下,高壓整合,不同佈局參數隔離效果比較 (a) LIGBT ...55 (b) SA-LIGBT ...55 圖 4.17 LIGBT 等效電路圖...56 圖 4.18 LIGBT 陽極 PN 接面電場...56 圖 4.19 等效電路圖 (a) LDMOS ...57 (b) SA-LIGBT...57

圖 4.20 高低壓整合,高壓元件反向偏壓下電流流密圖 (a) LDMOS ...58 (b) SA-LIGBT...58 圖 4.21 高低壓整合,P-sink 寬度與漏電流關係圖 (a) LDMOS ...59 (b) SA-LIGBT...59 圖 4.22 高低壓整合,高低壓元件間距離與漏電流關係圖 (a) LDMOS ...60 (b) SA-LIGBT...60 圖 4.23 高低壓整合,隔離結構在不同偏壓下陽極偏壓與漏電流關係圖 (a) LDMOS ...61 (b) SA-LIGBT...61 圖 4.24 LDMOS 高低壓整合含隔離結構,N 型保護環不同偏壓電流流密 圖及寄生等效電路圖 (a) N 型保護環浮接,P 型保護環浮接...63 (b) N 型保護環偏壓 5V,P 型保護環浮接...63 圖 4.25 LDMOS 高低壓整合含隔離結構,P 型保護環不同偏壓電位圖及 寄生等效電路圖 (a) N 型保護環偏壓 5V,P 型保護環偏壓浮接 ...64 (b) N 型保護環偏壓 5V,P 型保護環偏壓接地...64 圖 4.26 高低壓整合含隔離結構,P-sink 寬度與漏電流關係圖 (a) LDMOS ...65 (b) SA-LIGBT...65 圖 4.27 高低壓整合含隔離結構,N 型保護環寬度與漏電流關係圖

圖 4.28 高低壓整合含隔離結構,P 型保護環寬度與漏電流關係圖 (a) LDMOS ...67 (b) SA-LIGBT...67 圖 4.29 相同面積下,高低壓整合,不同佈局參數隔離效果比較 (a) LDMOS ...68 (b) SA-LIGBT...68 圖 4.30 高低壓整合,兩組隔離結構不同偏壓組合比較 (a) LDMOS ...70 (b) SA-LIGBT...70 圖 4.31 單組隔離結構與雙組隔離結構的比較 (a) LDMOS ...71 (b) SA-LIGBT...71 圖 4.32 高壓整合,反向偏壓電流流密圖 (a) LDMOS ...72 (b) SA-LIGBT...72 圖 4.33 高壓整合,元件間 N 型磊晶層不同偏壓比較 (a) LDMOS ...73 (b) SA-LIGBT...73 圖 4.34 LDMOS 高壓整合,元件間 N 型磊晶層不同偏壓電流流密圖及寄 生等效電路圖 (a) N 型磊晶層浮接 ...74 (b) N 型磊晶層偏壓 5V ...74 圖 4.35 高壓整合,P-sink 寬度與漏電流關係圖 (a) LDMOS ...75 (b) SA-LIGBT...75

圖 4.36 高壓整合,元件間距離與漏電流關係圖 (a) LDMOS ...76 (b) SA-LIGBT...76 圖 4.37 高壓整合,隔離結構不同偏壓下,陽極偏壓與漏電流關係圖 (a) LDMOS ...77 (b) SA-LIGBT...77 圖 4.38 LDMOS 高壓整合,隔離結構不同偏壓電流流密圖及寄生電效電 路圖 (a) N 型保護環浮接,P 型保護環浮接...78 (b) N 型保護環浮接,P 型保護環接地...79 (c) N 型保護環偏壓 5V,P 型保護環浮接 ...79 (d) N 型保護環偏壓 5V,P 型保護環接地...79 圖 4.39 高壓整合含隔離結構,P-sink 寬度與漏電流關係圖 (a) LDMOS ...81 (b) SA-LIGBT...81 圖 4.40 高壓整合含隔離結構,N 型保護環寬度與漏電流關係圖 (a) LDMOS ...82 (b) SA-LIGBT...82 圖 4.41 高壓整合含隔離結構,P 型保護環寬度與漏電流關係圖 (a) LDMOS ...83 (b) SA-LIGBT...83 圖 4.42 相同面積下,高壓整合,不同佈局參數隔離效果比較 (a) LDMOS ...84 (b) SA-LIGBT...84

圖 5.1 製程模擬 (a)掺雜 N 型保護環及 N 埋藏層 ...89 (b)掺雜 P-sink 及 P 型保護環 ...89 (c)成長 N 型磊晶層 ...89 (d)掺雜 N 型保護環 ...89 (e)掺雜 P 型保護環及 P-Sink ...90 (f)掺雜 N 緩衝區...90 (g)掺雜 P 基極...90 (h)定義主動區...90 (i)成長閘極下方二氧化矽...91 (j)沉積多晶矽閘極...91 (k)掺雜 P+ ...91 (l)掺雜 N+...91 (m)沉積二氧化矽保護層(BPSG) ...92 (n)蝕刻出接觸點...92 (o)沉積鋁 ...92 圖 5.2 TSUPERM4 1D 光罩圖 ...93 圖 5.3 TSUPREM4 製程模擬圖 ...93

表格

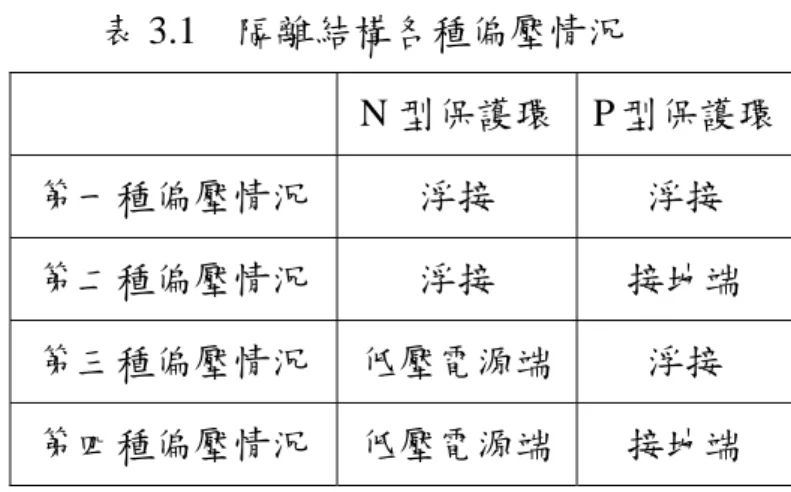

表 3.1 隔離結構各種偏壓情況...35 表 4.1 LIGBT 結構參數表...39 表 4.2 不同偏壓的漏電流比較 (a)LIGBT ...51 (b)SA-LIGBT ...51 表 4.3 不同偏壓的漏電流比較 (a)LDMOS...62 (b)SA-LIGBT ...62 表 4.4 兩組隔離結構的不同偏壓組合...69 表 4.5 不同偏壓的漏電流比較 (a)LDMOS...78 (b)SA-LIGBT ...78 表 4.6 LDMOS 含隔離結構不同偏壓,漏電流比 ...86 表 4.7 LDMOS 在相同面積下,漏電流比 (a)高低壓整合...86 (b)高壓整合 ...86 表 4.8 SA-LIGBT 隔離結構不同偏壓,漏電流比 ...87 表 4.9 SA-LIGBT 高低壓整合,雙層隔離結構不同偏壓,漏電流比 87 表 4.10 SA-LIGBT 改變隔離結構,漏電流比 ...87第一章 緒論

1.1 研究動機

近來功率半導體元件被廣泛的應用於工業、通訊、交通與電力電子等 領域。從 60 年代的 SCR,到目前的 LDMOS 和 IGBT,每一個世代的功率 半導體元件在電力電子產品上都扮演著舉足輕重的角色。由於電力電子技 術的急速進步,電力電子與微電子技術的結合更造成許多相關產業的躍 進,如電動汽機車、變頻器、伺服驅動器、小型智慧能源處理系統、電池 儲能系統等等,這些產品已與我們日常生活息息相關,因此先進國家如美 日等國均視其為科技競爭的主要發展目標之一。 將不同電性與製造技合至一積體電路中,一直是電子電機領域努力的 目標。過去由於製造技術的缺乏,在電力電子元件一直較少有人涉及這方 面的研究與設計,近幾年來由於元件製程上的突破,此領域已經成為廣泛 討論的課題[1]。 自從第一個功率元件在 1960 年代被製造出來後,由於功率元件的耐高 壓、高電流特性,且具有高功率處理能力的產品不斷的在改進中,在電路 應用上也逐漸受到重視。藉由這種高功率的特性,再結合類比或數位電路 而成為功率積體電路(Power Integrated Circuit,PIC)。提供更完整的功能 且成本更加低廉,取代傳統上笨重且昂貴的離散電路。由於製程的突破及 電路設計的進步,功率積體電路在效率上、功能上更趨於完整,可以預見 將來的應用範圍更加廣泛。在考慮價位較合經濟效益的前題下,本論文將探討利用接面隔離 (Junction Isolation,JI)整合高低壓元件及高壓元件,研究如何透過佈局參

數及偏壓減少基板漏電流對鄰近電路及元件的影響,並找出設計準則。

1.2 文獻回顧

近年來,在探討高低壓元件整合的功率積體電路文獻漸增[2][3],但對 於利用接面隔離技術的探討甚少,多採用價位較高的介電隔離技術

(Dielectric Isolation, DI)[4][5]。

在文獻中指出若高壓元件在導通時,會產生基板漏電流流向鄰近元 件。當元件關閉後,需等待基板中的載子完全移除,才可再做切換動作, 否則會產生相互耦合的現象(cross-coupling) [6]。在接面隔離技術上,由於 採用多磊晶層(multi- epitaxial layers)的隔離方法在製程上較為複雜[7],如 圖 1.1 所示,因此主要仍是採用保護環(guard ring)的方法[8]-[11],來隔離 高低壓元件,如圖 1.2 所示。除了一般的保護環設計外,可利用 N+埋藏層 (N+ buried layer)與保護環部份重疊來增加隔離效果[12],如圖 1.3 所示。除 了利用保護環被動地隔離漏電流,外加電路設計可以主動地防止漏電流的 產生[13][14],如圖 1.4 所示。 由於高壓元件在操作時,溫度隨著操作電流增加而增加。因為在高溫 下,N 阱及 P 阱的電阻均會上升,寄生電晶體的電流增益增加且 PN 接面 的導通壓降降低,更容易發生閂鎖現象[15]。因此在佈局規畫上,需盡量 使電流均勻分布,避免電流集中[16]。

圖 1.1 多磊晶層結構圖 LDMOS C ollector Isolator C MOS P+ N+ P+ P P-sub N-epi N -epi N -buffer N+ N+ N+ N+ P+ P+ P+ N-well P-well 圖 1.2 保護環隔離結構圖 V<0

Drain Ring1 Ring2

Gnd 5V 5V

N -epi N -epi N -epi BL HV BL Protection BL LV

P-sub PISO/BL A lignment

(a) 利用 BJT 防制漏電流 Ve<0 V<0 +10V Control circuit Active pulldown MOS protection Power

NLDMOS Piso ring

Power NLDMOS N+ N+ N+ N+ N+ N+ Riso Rsub

Par asitic NPN P sub str ate Body Diode V>0 (b) 利用控制電路及 MOS 防制漏電流 圖 1.4 示意圖

1.3 論文架構

本論文架構概述如下:第一章說明論文的研究動機及相關文獻的探 討。第二章介紹元件操作原理及接面隔離產生寄生現象的相關理論。第三 章為研究方法的規劃。第四章為利用軟體模擬隔離設計並比較及討論其結 果。第五章介紹製程流程及光罩規劃等。最後第六章為結論與未來展望。第二章 相關理論探討

在本論文中將探討的重點放在高低壓元件整合及高壓元件整合時所產 生的基板漏電流。我們所探討的高壓元件以目前較適合半導體製程的高壓 橫向擴散式金氧半電晶體(Lateral Double-diffused

Metal-Oxide-Semiconductor field-effect-transistor, LDMOS)、高壓橫向絕緣 雙極性電晶體(Lateral Insulated Gate Bipolar Transistor, LIGBT)及高壓橫向 陽極短路絕緣雙極性電晶體(Shorted-Anode Lateral Insulated Gate Bipolar Transistor, SA-LIGBT)為探討對象。由於高壓元件在導通或切換時,會因元 件的操作原理或與相鄰元件耦合的寄生電路造成漏電流,而此漏電流使得 高壓元件產生誤動作或低壓電路準位的漂移,甚至產生閂鎖現象。因此要 解決漏電流的問題必須先瞭解高壓元件的操作原理及相關的半導體元件 物理。

2.1 高壓元件的操作原理

LDMOS 是我們選擇探討的高壓元件的第一個目標。這是因為 LDMOS 製作容易,頻率響應高,可應用於手機頻段,易於積體化。在 LDMOS 中, 如圖 2.1 所示,為了讓電流從汲極流向源極,在源極和汲極之間必須先建 立一個通道,以提供載子流通的路徑。當閘極被施以足夠的正偏壓時,閘 極會吸引 P 基極區中的電子,而 P 基極區和絕緣層間形成反轉層(inversion layer),這層反轉層就成為導通源極和汲極間的通道,閘極電壓越高,導通 電阻就越小。N+ P-Sink Drain Gate Source N+ N-Buffer P-Base LDMOS N-Epi P-Sub 圖 2.1 LDMOS 結構示意圖 LIGBT 是一四層半導體功率元件,結構中金氧半電晶體的汲極與 PNP 的電晶體基極相接,如圖 2.2(a)所示。其操作原理是利用將金氧半電晶體 打開,使 N 型漂移區的電位下降,有足夠的跨壓使 PNP 寄生電晶體導通, 如圖 2.2(b)所示。由於大量的電洞注入 N 型漂移區, N 型漂移區會感應出 相當數量的電子以維持電中性,降低導通阻,此現象稱導電度調變 (conductivity modulation)效應。關閉元件時,由於 N 型漂移區中儲存大量 的載子需要移除,因此 LIGBT 的工作頻率較 LDMOS 低。 P+ P-Sink Anode Gate Cathode N+ N-Buffer P-Base LIGBT N-Epi P-Sub Cathode Anode Gate PNP PNP NMOS (a) 結構示意圖 (b) 等效電路圖 圖 2.2 LIGBT SA-LIGBT 的結構圖及等效電路圖,如圖 2.3 所示。其操作原理與 LIGBT 相似。由於陽極 P+和 N+短路,可在電晶體開與關時皆能帶來極為 有利的效益,如當關閉元件時,N 型漂移區中的電子除了可藉由復合

因此關閉時間(turn-off time)較短,切換速度較快[17]。但也因為陽極短路, 陽極與陰極間需要較大的跨壓,才能使寄生 PNP 電晶體導通。 P+ P-Sink Anode Gate Cathode N+ N-Buffer P-Base SA_LIGBT N-Epi P-Sub N+ Cathode Anode Gate PNP PNP NMOS RNbuffer (a) 結構示意圖 (b) 等效電路圖 圖 2.3 SA-LIGBT

2.2 閂鎖效應的產生

低壓電路會發生閂鎖效應,這是由 N 阱與 P 阱等大量結構接面形成的 寄生元件造成的問題。在電源端及接地端由寄生 PNPN 半導體及 N 阱與 P 阱的寄生電阻所引發的,如圖 2.4 所示。 P well N well RNW Q2 CMOS Structure RPW Q1 N+ P+ P+ N+ P+ N+ Vdd 圖 2.4 低壓電路寄生電路示意圖在電源端及接地端由寄生電路形成一條可以導通的路徑,如圖 2.5 所 示。假如有足夠的基板電流使得跨在 RNW上的電壓足以導通電晶體 Q1, 或者使跨在 RPW上的電壓足以導通電晶體 Q2 均會造成寄生閘流體導通, 引發閂鎖效應,使得低壓電路損毀。 VDD RN W Q 1 Q 2 RPW 圖 2.5 閂鎖效應等效電路圖

2.3 PN 接面

圖 2.6 是 PN 接面的示意圖。為了簡化起見,我們將考慮一個步階接面 (step junction),其中在每個區域的掺雜濃度都是均勻的,而且在接面處為 陡峭的掺雜改變。在 N 型區中的多數載子電子會擴散進入 P 型區中,而在 P 型區中的多數載子電洞則會擴散進入 N 型區中。電子因擴散而離開 N 型 區,會留下帶正電的施體原子(donor);而電洞因擴散離開 P 型區,留下帶 負電的受體原子(acceptor)。在 N 型區及 P 型區中,正電荷及負電荷會在接 近接面的地方產生由正電荷至負電荷的電場。淨正電荷區及淨負電荷區稱 為空間電荷區(space charge region)或空乏區(depletion region) ,如圖 2.7 所 示。P

N

圖 2.6 PN 接面的簡化幾何結構 P N -+ -+ -+ + + + + + + 空乏區 電場 圖 2.7 PN 接面的空乏區及電場圖 2.3.1 零外加電壓 當沒有電壓跨降在 PN 接面上,則接面是處於熱平衡的狀況—整個系 統的費米能階是一個固定的常數。在 P 型區與 N 型區間,傳導帶與價帶相 對於費米能階的位置會有所改變,因此在空乏區的地方,傳導帶和價帶的 能量必然會彎曲,如圖 2.8 所示。在 N 型區傳導帶中的電子試圖移動至 P 型區傳導帶會遇到一個位勢障礙。這個位勢障礙稱為內建位勢障礙(built-in potential barrier),以符號 Vbi表示。 圖 2.8 PN 接面在熱平衡時能帶圖由能帶圖中,我們可知 Vbi = φFn +φ Fp (2.1a) eφFn =EFi −EF (2.1b) eφFp =EFi −EF (2.1c) 在 N 型區中的傳導帶的電子濃度為 n n E E kT n e kT i F Fi i Fn 0 = −

L

NM

O

QP

=L

NM

−O

QP

exp exp ( φ ) (2.2) 其中ni及EFi分別為本徵載子濃度及本徵費米能階,φFn為 N 型區中的位勢。 對(2.2)兩邊取自然對數,並設n0 = Nd,Nd為施體濃度。求解位勢,我們 可得 φFn d i kT e N n = − lnF

HG

I

KJ

(2.3) 同樣地,在 P 型區中的電洞濃度為 p N n E E kT n e kT a i Fi F i Fp 0 = = −L

NM

O

QP

=L

NM

O

QP

exp exp φ (2.4) 其中Na是受體濃度,φFp是 P 型區中的位勢。經過計算可得 φFp a i kT e N n = lnF

HG

I

KJ

(2.5) 最後,將(2.3)與(2.5)代入(2.1)中,可得到步階接面的內建位勢障礙為 V kT e N N n V N N n bi a d i t a d i = lnF

HG

2I

KJ

= lnF

HG

2I

KJ

(2.6) 其中V kT e t = ,被定義為熱電壓(thermal voltage)。-+ -xp +xn +e Nd -e Na P N p (C /cm3) 圖 2.9 均勻 PN 接面及陡峭接面近似時空間電荷密度圖 假設均勻掺雜及陡峭接面近似時,在 PN 接面的體積電荷密度的分佈 圖,如圖 2.9 所示,正負空間電荷的分隔會產生電場。假設在 N 型區中的 x= +xn處,以及在 P 型區中的x= −xp處,空間電荷會突然停止。由圖 2.9 可知,電荷密度為 ρ( )x = −eNa −xp < <x 0 (2.7a) ρ( )x =eNd 0< <x xn (2.7b) 對一維的分析而言,電場可由帕松方程式(Poisson equation)來決定 d x dx x dE x dx s 2 2 φ ρ ε ( ) = − ( ) = − ( ) (2.8) 其中φ( )x 是電位,E x( )是電場,ρ( )x 是體積電荷密度,而εs是半導體的電 容率。 將(2.8)積分,可求得 P 型區中的電場。對於在x< −xp的 P 型區而言, 由於熱平衡時的電流為零,因此可以假設電場為零,故設x= −xp處E =0, 因此可求得 P 型區中的電場為 E eNa x x s p = − + ε ( ) −xp ≤ ≤x 0 (2.9) 同樣的,我們也可以設x= +xn處E =0,求得 N 型區中的電場為 E eNd x x s n = − − ε ( ) 0≤ ≤x xn (2.10) 在x=0,PN 接面處的電場也是一個連續函數,因此(2.9)與(2.10)在x=0處 彼此相等,得到

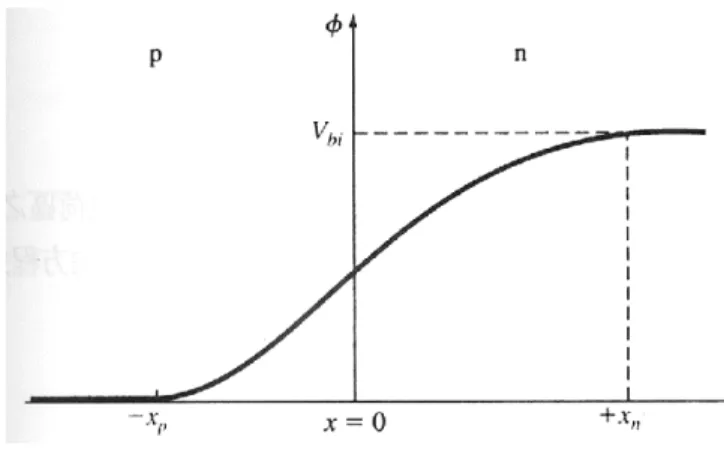

N xa p = N xd n (2.11) (2.11)說明,在 P 型區中單位面積的負電荷數目會等於 N 型區中單位面積 的正電荷數目。 圖 2.10 是空乏區之內的電場圖形。對於均勻掺雜的 PN 接面而言,電 場是穿過接面的距離的一個線性函數,而最大電場值發生在 PN 接面處。 既使沒有外加電壓於 P 型區及 N 型區,在空乏區之中仍然會有電場存在。 -xp +x n P N E 0 圖 2.10 空乏區中的電場 將電場積分,可以求得接面中的位勢。為了求 PN 接面的位勢差,我 們設在x= −xp處電位為零,可求得在 P 型區中的電位為 φ ε ( )x eNa (x x ) s p = + 2 2 − ≤ ≤ xp x 0 (2.12) 同樣的,將 N 型區中的電場積分,可求的 N 型區中的電位,且由於位 勢是一個連續的函數,因此在 PN 接面,x= 0處彼此相等,可得 φ ε ε ( )x eNa (x x x ) eN x s n a s p = − 2 + 2 2 2 0≤ ≤x xn (2.13) 圖 2.11 是通過接面的位勢圖。在x= xn處,位勢大小等於內建位勢障 礙。由(2.13),可得 Vbi x xn e N x N x s d n a p = φ = = + ε ( ) 2 2 2

d

i

(2.14)圖 2.11 PN 接面中整個空乏區的電位

PN 接面空乏區的長度稱空間電荷寬度(space charge width)。可將(2.11) 改寫成 x N x N p d n a = (2.15) 將(2.15)代入(2.14)並求解xn,可得 x V e N N N N n s bi a d a d =

L

NM

O

QP

+L

NM

O

QP

RS

T

2 1UV

W

1 2 ε (2.16) 其中xn是在零外加電壓下,延伸進入 N 型區中的空間電荷寬度。 同樣的,由(2.11)代入(2.14)亦可求得 x V e N N N N p s bi d a a d =L

NM

O

QP

+L

NM

O

QP

RS

T

2 1UV

W

1 2 ε (2.17) 其中xp是在零外加電壓下,延伸進入 P 型區中的空間電荷寬度。 空乏區或空間電荷的總寬度W是(2.16)及(2.17)的和,因此將兩式將 加,可得 W V e N N N N s bi a d a d =L

+NM

O

QP

RS

T

2UV

W

1 2 ε (2.18) 由上述的式子可知,空間電荷寬度是掺雜濃度的倒數函數;因此,空 乏區會向掺雜濃度低的區域延伸較多。2.3.2 反向偏壓 在 N 型區相對於 P 型區之間加上一個正電壓時,則半導體將不再是處 在一個平衡狀態下,通過系統的費米能階也不再是固定不變的,如圖 2.12 所示。由於正電壓在圖 2.12 的電子位能圖中是往下遞增的,N 型區的費米 能階會低於 P 型區的費米能階。 圖 2.12 反向偏壓 PN 接面能帶圖 在外加位勢是反向偏壓時,標示為Vtotal的總位勢障礙升高, Vtotal = φFn +φFp +VR =Vbi+VR (2.19) 其中VR是外加反向偏壓電壓的大小,Vbi是在熱平衡時所定義的內建位勢障 礙。 由於外加電壓的作用,空間電荷區中的電場會升高。電場是源自於正 電荷,而會在負電荷處終止;這表示如果電場升高,正電荷與負電荷的數 目必須增大。因此只有當空間電荷寬度W增大時,空乏區中的正電荷及負 電荷數目才能增加。所以空間電荷寬度W會隨著反向偏壓VR的增加而變

將內建位勢障礙用總位勢障礙來取代,由(2.18),可以得到空間電荷寬 度為 W V V e N N N N s bi R a d a d = +

L

+NM

O

QP

RS

T

2UV

W

1 2 ε ( ) (2.20) 由於xn與xp會隨著反向偏壓的電壓增加而增加,因此電場強度也會變 大。而最大的電場仍然是發生在 PN 接面處。將(2.16)或(2.17)之一與總位 勢障礙Vbi +VR合併使用代入(2.9)或(2.10),則可得最大電場 E e V V N N N N bi R s a d a d max ( ) = − + +L

NM

O

QP

RS

T

2UV

W

1 2 ε (2.21) 亦可表示為 E V V W bi R max ( ) = −2 + (2.22) 其中W是空間電荷總寬度。 若考慮一個單邊的 P+N 接面,則最大電場是 E eN xd n s max = ε (2.23) 空乏區寬度xn可以近似為 x V eN n s R d ≅RS

T

2UV

W

1 2 ε (2.24) 其中VR是外加反向偏壓電壓的大小。在上式中,我們忽略內建位勢Vbi。 若將VR設定為崩潰電壓VB,則最大電場Emax將被界定為崩潰時的臨界 電場Ecrit。將(2.23)及(2.24)合併,可以得到 V E eN B s crit B = ε 2 2 (2.25) 其中NB是單邊接面中低掺雜區域的半導體掺雜濃度。2.3.3 順向偏壓 圖 2.13 順向偏壓 PN 接面能帶圖 在順向偏壓的情況下,由於總位勢障礙被降低了,如圖 2.13 所示。較 小的位勢障礙意指電場也會被降低。較小的電場則無法將電子與電洞分別 拉回 N 型區與 P 型區。電洞將會由 P 型區中流向 N 型區;電子則由 N 型 區流向 P 型區。這種電荷的流動會產生一個通過接面的電流。電流密度與 順偏電壓的關係[18]如下 J J eV kT S a =

L

F

HG

I

KJ

−NM

exp 1O

QP

(2.26) 其中Js為理想反向飽和電流密度,Va為外加順偏電壓。由(2.26)可知,順 向偏壓電流是順向偏壓電壓的指數函數。2.4 PIN 二極體

由於 PN 二極體所能承受的崩潰電壓相當有限,因此在需要高耐壓的 情況下便使用 P-i-N 二極體[19]。從帕松方程式可知,電位是由電場積分所 得。在圖 2.14 中可知,可推得 P-i-N 二極體及 PN 二極體的跨壓分別為VR = E1+E2 Wd 2

b

g

(2.27) VR E Wd '= 1 ' 2 (2.28) 且Wd>>Wd',因此當 P-i-N 二極體與 PN 二極體在相同的E1電場下,P-i-N 二極體的跨壓遠大於 PN 二極體。隨著低濃度掺雜區寬度的增加,可增加 P-i-N 二極體的耐壓,因此我們可依所需要的耐壓調整低濃度掺雜區的寬 度。 P+ N- N+ Wd V - + x E P+ N+ V + x E Wd E1 E1 E2 Wd’P-i-N Diode PN Diode

-圖 2.14 P-i-N 二極體與 PN 二極體空乏區及電場-圖 雖然 P-i-N 二極體因為低掺雜濃度區可以承受較大的耐壓,但也因此 有兩個缺點。第一,導通初期,會產生正向過沖電壓(forward voltage overshoot),如圖 2.15 所示。這是由於導通初期,低濃度掺雜區為高阻抗, 因此跨壓較大;等進入穩態後,因為高注入(high injection)的關係,使低濃 度掺雜區有導電度調變效應,降低阻抗,而使導通壓降下降。第二,切換 特性差。導通時,低濃度掺雜區儲存著大量載子。當關閉時,需要反向電 流(reverse current)來移除載子,增加功率的損耗,如圖 2.16 所示。

圖 2.15 P-i-N 二極體正向導通波形 圖 2.16 P-i-N 二極體反向回復電流波形

2.5 雙極性電晶體

圖 2.17 表示一個 NPN 雙極性電晶體的理想化雜質掺雜輪廓,這是當 每一個區域都是均勻掺雜時的狀況。由圖 2.17(b)可知,射極具有最大的掺 雜濃度;而集極則具有最小的掺雜濃度。N++ P+ N

C

B

E

(a) (b) 圖 2.17 NPN 雙極性電晶體的理想化掺雜輪廓 如圖 2.18(a)所示,在正常的偏壓組態下,基極-射極(B-E)PN 接面是順 向偏壓,而基極-集極(B-C)PN 接面則是反向偏壓。這種組態被稱為是順向 主動(forward active)的操作模式。由於 B-E 接面是順向偏壓,因此電子會 由射極射入基極。被注入的電子會在基極中造成過量的的少數載子濃度。 而 B-C 接面為反向偏壓,因此在 B-C 接面邊緣處的少數載子濃度為零,如 圖 2.18(b)所示。在基極中,電子濃度具有很大的梯度,意指由射極注入的 電子將會擴散跨越基極區域進入 B-C 接面的空乏區中,在空乏區中的電場 會將電子掃入集極,如圖 2.18(c)所示。我們希望會有較多的電子到達集 極,而不會在基極與電洞復合,因此基極寬度必須比少數載子的擴散長度 還要小。N++ P+ N C B E - VC C + - VBB + - VC B + - VBE + iC iE RE RC (a) (b) (c) 圖 2.18 (a)NPN 雙極性電晶體在順向主動模式的偏壓。(b)NPN 雙極性電 晶體在順向主動模式操作下的少數載子分佈。(c) NPN 雙極性電晶體在零 偏壓及順向主動模式偏壓下的能帶圖 2.5.1 電晶體電流關係 理想而言,基極中的少數載子濃度是距離的一個線性函數,這暗示在 基極中並沒有復合。電子會擴散跨越基極,並被 B-C 接面空乏區中電場掃 進集極中。 集極電流 假設在基極中有理想的線性電子分佈,經過簡化,則集極電流可以寫 成給予的一個擴散電流

i eD A dn x dx eD A n x eD A x n v V C n BE n BE B B n BE B B BE t = = − −

L

NM

O

QP

= −F

HG

I

KJ

( ) ( ) exp 0 0 0 0 (2.29) 其中ABE是 B-E 接面的截面積,nB0是基極中的熱平衡電子濃度,而Vt是熱 電壓。電子的擴散是在+x的方向上,因此傳統的電流方向是在− x的方向 上。如果只考慮大小,(2.29)可寫成 i I v V C S BE t = expF

HG

I

KJ

(2.30) 由(2.30)可知,集極電流是由基極與射極間的跨壓來決定的。 圖 2.19 順向偏壓的 NPN 雙極性電晶體中少數載子分佈及基本電流 圖 2.19 中所顯示的射極電流分量之一iE1乃是由射極注入基極中的電 子流動所造成的。因此,這個電流值會等於(2.30)的集極電流。 射極電流 由於基極-射極接面是順偏,因此基極中的多數載子電洞會被注入跨越 B-E 接面,進入射極中,既圖 2.19 中所指的iE2。由於iE2是一個順向偏壓 的 PN 接面電流,因此可以表示為i I v V E S BE t 2 = 2

F

HG

I

KJ

exp (2.31) 其中IS2包含在射極中的少數載子電洞的參數。射極的總電流是這兩個 分量的總和, i i i i i I v V E E E C E SE BE t = 1+ 2 = + 2 = expF

HG

I

KJ

(2.32) 由於(2.32)中所有電流分量都是exp v V BE tF

HG

I

KJ

的函數,因此可推知集極電流對射 極電流的比值是一個常數,可以寫為 i i C E =α (2.33)其中α稱為共基極電流增益(common-base current gain)。

從以上的推導可知,當 B-C 接面為反向偏壓時,則集極電流與基極-射極電壓有關,而與基極-集極電壓無關。 基極電流 如圖 2.19 所示,射極電流的分量iE2是一個 B-E 接面的電流,因此這個 電流也是iBa的一個基極電流分量。這個基極電流分量是與exp(vBE /Vt)成正 比的。 之前我們假設在基極中少數載子電子與多數載子電洞是沒有復合的理 想狀況。實際上,基極中還是有某些復合。由於基極中的多數載子電洞經 復合而消失,因此必須由基極端流入正電荷補充。這個電流在圖 2.19 中被 標示為iBb。單位時間在基極中復合的電洞數目與基極中的少數載子數目是 直接相關的。因此,電流iBb也是正比於exp(vBE/Vt)。基極總電流是iBa與iBb 的總和,而且是正比於exp(vBE /Vt)。 由於集極電流與基極電流都是正比於exp(vBE /Vt),因此集極電流對基

i i

C B

=β (2.34)

其中β 稱為共射極電流增益(common-emitter current gain)。

2.5.2 操作模式 圖 2.20 顯示在一個簡單電路中的 NPN 電晶體。在這樣的電路中,電 晶體可能會被偏壓至三種操作模式中的一種。如果 B-E 接面的電壓是零或 是反向偏壓,則射極的多數載子電子無法注入基極中。此時,B-C 接面也 是反向偏壓;因此射極與集極電流均為零。這種情況稱為截止(cuteoff)。 圖 2.20 在共射極電路中的一個 NPN 雙極性電晶體 當 B-E 接面變成順向偏壓時,將會有射極電流產生,而注入到基極中 的電子會造成集極電流。環繞集極至射極的迴路依 KVL 可寫出 VCC = I RC C−VBC+VBE =VR −VBC +VBE (2.35) 如果VCC足夠大,而且VR夠小的話,則VBC p 0,表示 B-C 接面是反向偏壓, 電晶體操作在順向主動區域。

當順向偏壓 B-E 接面電壓增加時,集極電流以及VR也將因此增加。VR 的增加意謂著反向偏壓的 C-B 接面電壓或VCB 會降低。當集極電流足夠 大,使VR與VCC的組合會在 B-C 接面產生零電壓。若集極電流再增加,使VR 也增加,會導致 B-C 接面順偏。此操作模式稱為飽和(saturation)。在飽和 模式下操作時,B-E 與 B-C 接面兩者都是順向偏壓,而集極電流不再受到 B-E 接面電壓的控制。 繞著 C-E 迴路依 KVL 可寫出 VCE =VCC−I RC C (2.36) (2.36)顯示集極電流與集極-射極電壓之間呈一個線性關係。這個線性關係 稱為一條負載線(load line),如圖 2.21 所示。附加在電晶體特性上的負載線 可被使用來觀察電晶體的偏壓狀況及操作模式。 圖 2.21 雙極性電晶體的共射極電流-電壓特性及負載線 雙極性電晶體的第四種模式為反向主動(inverse active),它是發生在當 B-E 接面為反向偏壓,而 B-C 接面為順向偏壓時。在這種情況下,電晶體 是被顛倒操作的,而射極與集極的角色互換。由於電晶體並不是對稱元 件;因此反向主動特性與順向主動特性並不相同。

2.6 溫度效應

2.6.1 本徵載子濃度

圖 2.22 是溫度與載子濃度的關係圖[20]。從圖中可知對矽基板而言, 當溫度在 150K 到 450K,載子濃度約等於掺雜濃度。而在 100K 以下,由 於溫度較低,載子沒有足夠的能量脫離原子的吸引,因此載子濃度低於掺 雜濃度。當溫度高於 450K 時,本徵載子濃度(intrinsic carrier concentration) 大幅增加,因此載子濃度會大於掺雜濃度。隨著溫度增加,本徵載子濃度 增加,也造成理想反向飽合電流的增加。

2.6.2 載子遷移率 當半導體晶體中的原子,在高於絕對零度時,會具有一定大小的熱能, 使原子會相對其在晶體中的晶格位置作隨機的振動。這種晶格振動會導致 完美週期位勢函數的擾動。在一個固體之中的完美週期性位勢使電子得以 不受阻礙地,或者不受到散射地,移動通過這個晶體。但是熱振動會造成 位勢函數的擾動,並且引發電子或電洞與振動晶格原子之間的交互作用, 此作用稱晶格散射(lattice scattering)。 由於晶格散射是與原子的熱運動相關的,因此散射發生的速率是溫度 的一個函數。如果我們使用µL來代表只有晶格散射存在時所觀察到的遷移 率,則散射理論說明由一階近似 µL α T−3 2/ (2.37) 由於晶格散射會造成遷移率隨溫度的升高而降低。直觀而言,可以預期當 溫度升高時,晶格振動也會增加,意味散射事件發生的機率也會增加,並 因而使遷移率降低。 圖 2.23 顯示矽之中的電子與電洞的遷移率與溫度之間的依存關係。在 輕掺雜的半導體之中,晶格散射會主控載子遷移率。遷移率的溫度關係顯 然是與Tn成正比。圖中的插圖顯示參數 n 並不等於由一階散射理論所預測 的 3/2。然而,遷移率的確會隨著溫度的升高而降低。

(a) 電子載子 (b) 電洞載子 圖 2.23 在各種掺雜濃度的矽中,載子遷移率與溫度關係圖

第三章 研究方法

3.1 軟體模擬規劃

本論文在實作上是模仿業界的 100V 高壓製程,因此先用製程模擬軟 體(TSUPREM4)[21]模擬目前業界所使用的高壓製程,以取得製程的各項參 數,如高低壓元件源極、汲極的掺雜濃度、深度,阱區的掺雜濃度、深度, 及磊晶層的掺雜濃度、深度等。 使用元件模擬軟體(MEDICI)[22]搭配由 TSUPREM4 得到的製程參 數,建構高低壓元件整合的模型。本論文的隔離設計採用 N 型保護環及 P 型保護環設計隔離結構,並做進一步模擬分析各參數的影響。 在高低壓整合及高壓整合方面,則選擇三種常用的高功率元件, LDMOS,LIGBT,SA-LIGBT,進行模擬,如圖 3.1~3.3。對每個元件的操 作原理及可能產生漏電流的情況進行模擬分析。當導通電流增加會造成溫 度上升,會使理想反向飽合電流增加及載子遷移率下降。為了釐清各項變 因的影響,因此調變佈局參數同時亦分別模擬溫度在 300K 及 400K 的情況。N+ P-Sink Vbias Anode Gate Cathode N+ N-Buffer P-Base CMOS Structure LDMOS P well P+ N+ Vdd P+ N+ N well P-Sub N-Epi N-Epi (a)LDMOS 與低壓電路 P-Sub P-Base Gate Cathode N+ P-Sink P-Base Gate Cathode N+ P-Sink LDMOS N+ Vbias Anode N-Buffer N-Epi LDMOS N+ Vbias Anode N-Buffer N-Epi (b) LDMOS 與 LDMOS 圖 3.1 LDMOS 整合示意圖 P+ P-Sink Vbias Anode Gate Cathode N+ N-Buffer P-Base CMOS Structure LIGBT P well P+ N+ Vdd P+ N+ N well P-Sub N-Epi N-Epi (a) LIGBT 與低壓電路 P-Sub P-Sink Gate Cathode N+ P-Base LIGBT P+ Vbias Anode N-Buffer N-Epi P-Sink Gate Cathode N+ P-Base LIGBT P+ Vbias Anode N-Buffer N-Epi (b) LIGBT 與 LIGBT 圖 3.2 LIGBT 整合示意圖

P+ P-Sink Vbias Anode Gate Cathode N+ N-Buffer P-Base CMOS Structure SA_LIGBT P well P+ N+ Vdd P+ N+ N well P-Sub N-Epi N-Epi N+ (a) SA-LIGBT 與低壓電路 P-Sub P-Sink Gate Cathode N+ P-Base SA_LIGBT N-Epi P+ Vbias Anode N-Buffer N+ P-Sink Gate Cathode N+ P-Base SA_LIGBT N-Epi P+ Vbias Anode N-Buffer N+ (b) SA-LIGBT 與 SA-LIGBT 圖 3.3 SA-LIGBT 整合示意圖 當高低壓元件整合在 同一晶片上工作時,由於高功率元件的電流尺度 極大,會對低壓元件及相鄰高功率元件造成衝擊,因此隔離工作必須建立 起來。 在本節我們將依據高功率元件可能的操作情況對低壓電路及相鄰高壓 元件的影響逐一說明: 1. 當高壓元件在順向偏壓的工作情況下,會有少數載子經由 P 型基板流至 低壓電路及鄰近高壓元件,造成低壓電路不正常運作(如數位訊號錯誤,類 比訊號準位漂移,低壓電路閂鎖效應等)及鄰近高壓元件誤動作等,如圖 3.4 所示。

N+/P+ P-Sink Vdd Vbias Anode Gate Cathode P well N well P+ N+ P+ N+ N+ N-Buffer P-Base CMOS

Structure High Power Device

Leakage Current N-Epi N-Epi P-Sub P+/N+ (a) 高低壓整合 Leakage Current P-Sub P-Sink Gate Cathode N+ P-Base

High Power Device

N-Epi P+/N+ N+/P+ Vbias Anode N-Buffer P-Sink Gate Cathode N+ P-Base High Power Device

N-Epi P+/N+ N+/P+ Vbias Anode N-Buffer (b) 高壓整合 圖 3.4 順向偏壓時,漏電流示意圖 2. 從導通到關閉的切換瞬間,可能因電感性負載導致陽極端(Anode)的電 壓低於陰極端(Cathode),則高壓元件的本體二極體導通。且高低壓元件均 在 P 型基板上,使低壓電路的高電位與 P 型基板或 P-sink 及陽極端的 N+ 形成寄生的 NPN 電晶體 Q3,如圖 3.5 所示。當漏電流過大,可能會造成 高壓元件的誤動作或低壓電路的準位漂移,甚至使低壓電路產生閂鎖效 應。

P-Sink Vbias Anode Gate Cathode P well N well RNepi RNW Q2 Q3 P+ N+ N+ N-Buffer P-Base CMOS

Structure High Power Device

RPWP+ N+Q1 Vdd RPsub1 RPsub2 RPsub3 N-Epi N-Epi P-Sub RPsink N+/P+ P+/N+ (a) 高低壓整合 Q3 RPsub1 RPsub2 P-Sub P-Sink Gate Cathode N+ P-Base

High Power Device

N-Epi RPsink Anode Vbias N-Buffer N+/P+ P-Sink Gate Cathode N+ P-Base High Power Device

N-Epi RPsink Anode Vbias N-Buffer N+/P+ RPsub3 P+/N+ P+/N+ (b) 高壓整合 圖 3.5 反向偏壓時,寄生等效電路圖 在不調變製程的情況下,我們以改變佈局的方式來減少上述兩項影響 造成漏電流因素,我們擬定了以下步驟來分析各項佈局參數對隔離效果的 影響。步驟分述如下: 1. 在高壓整合方面,先改變元件與元件間 N 型磊晶層的偏壓模擬其對漏 電流的影響,如圖 3.6 所示。高低壓整合方面,若將 N 型磊晶層偏壓在低 壓電路的高電位端,如圖 3.7,當低壓電路的高電位端與 N 型磊晶層之間 有電位降時,會造成無謂的漏電流,因此不將其列入討論範圍。

P-Sub P-Sink Gate Cathode N+ P-Base

High Power Device

N-Epi N+/P+ Vbias Anode N-Buffer P+/N+ P-Sink Gate Cathode N+ P-Base High Power Device

N-Epi N+/P+ Vbias Anode N-Buffer P+/N+ N-Epi Vbias 圖 3.6 高壓整合中,改變元件間 N 型磊晶層偏壓示意圖 N+/P+ P-Sink Vbias Anode Gate Cathode P well N well N+ N-Buffer P-Base CMOS

Structure High Power Device

N-Epi N-Epi P-Sub P+/N+ Vdd P+ N+ P+ N+ Vbias 圖 3.7 高低壓整合中,改變高低壓元件間 N 型磊晶層偏壓示意圖 2. 高壓元件工作在順向偏壓或反向偏壓,且高壓元件間的 N 型磊晶層偏 壓在使漏電流較小的情況下,調整 P-sink 寬度及高壓元件與低壓電路及鄰 近高壓元件的距離,如圖 3.8 所示,以模擬這兩個參數對漏電流的影響。 N+/P+ P-Sink Vbias Anode Gate Cathode P well N well N+ N-Buffer P-Base CMOS

Structure High Power Device

N-Epi N-Epi P-Sub P+/N+ Vdd P+ N+ P+ N+ D LPsink (a) 高低壓整合

P-Sub P-Sink Gate Cathode N+ P-Base

High Power Device

N-Epi N+/P+ Vbias Anode N-Buffer P+/N+ P-Sink Gate Cathode N+ P-Base High Power Device

N-Epi N+/P+ Vbias Anode N-Buffer P+/N+ N-Epi Vbias LPsink LPsink Dis (b) 高壓整合 圖 3.8 調變佈局參數示意圖 3. 加入 N 型保護環及 P 型保護環作為隔離結構,如圖 3.9 所示。高壓元件 順向偏壓及陽極反向偏壓時,依表 3.1 模擬比較 N 型保護環及 P 型保護環, 在何種偏壓下可有效地隔離漏電流。 P-Sink Vdd Vbias Anode Gate Cathode P well N well P+ N+ P+ N+ N+ N-Buffer P-Base P+ Ring N+ Ring VNring VPring

LPring LNring LPsink N-Epi N-Epi

P-Sub CMOS

Structure

N+/P+ P+/N+

High Power Device

(a)高低壓整合 P+ Ring VNring VPring LPring P-Sub P-Sink Vbias Anode Gate Cathode N+ N-Buffer P-Base N+ Ring

LNring LPsink N-Epi

N+/P+ P+/N+

High Power Device

P-Sink Vbias

Anode Gate Cathode

N+ N-Buffer P-Base N+ Ring LNring LPsink N-Epi N+/P+ P+/N+

High Power Device VNring

(b)高壓整合

表 3.1 隔離結構各種偏壓情況 N 型保護環 P 型保護環 第一種偏壓情況 浮接 浮接 第二種偏壓情況 浮接 接地端 第三種偏壓情況 低壓電源端 浮接 第四種偏壓情況 低壓電源端 接地端 4. 在隔離效果較佳的偏壓下調整佈局尺寸。調整 P-sink 寬度、N 型保護環 寬度及 P 型保護環寬度,如圖 3.9 所示,透過模擬得知改變參數時漏電流 減小的趨勢。並比較在相同面積下,如何設計能有效的達到隔離設計。 5. 最後在高低壓整合方面,比較雙組隔離結構在不同偏壓下對漏電流的影 響。並在相同面積下,比較單組隔離結構或雙組隔離結構何種設計能達到 較佳的隔離效果,如下圖 3.10。 P-Sink Vbias Anode Gate Cathode N+ N-Buffer P-Base

High Power Device

P-Sub N-Epi P+ Ring N+ Ring VNring VPring Isolation Structure Vdd P well N well P+ N+ P+ N+ CMOS Structure N-Epi N+/P+ P+/N+ P+ Ring N+ Ring VNring VPring Isolation Structure 圖 3.10 雙組隔離結構截面示意圖

利用Tsuprem4 模擬,取得製程 Profile 將高低壓元件結 構及Profile,利用 Medici繪製網格 單載子元件 雙載子元件 改變佈局參數(Psink 寬度及元件間距離), 量測漏電流情況 加入隔離結構,模擬隔離結構在何 種偏壓下(N型保護環偏壓在低壓 電路高電位或浮接,P型保護環偏 壓在接地端或浮接),隔離效果較佳 依據各項變因 所得結果,可以 得到較佳隔離 佈局參數設計 在隔離效果較佳的偏壓下, 調整佈局參數(Psink,N型保 護環及P型保護環等寬度), 觀察漏電流改變趨勢 此元件為單 載子元件或 雙載子元件 是 否 否 是 順偏操作下, 量測漏電流 反偏操作下,本 體二極體是否 會導通 模擬反偏時,陽 極端PN接面的 崩潰電壓 改變元件間N 型磊晶層偏壓, 比較隔離效果 高低壓整合 或高壓整合 高低壓整合 高壓整合 高低壓整合 或高壓整合 正反偏操作是 否均模擬 高壓整合 比較單組隔離結 構與雙組隔離結 構的隔離效果 高低壓整合

3.2 實作驗證規劃

在實作驗證的規劃上,製程方面是模仿業界所使用的 100V 高壓製程。 要將高低壓元件整合在同一顆 IC 中,必須使用較多的光罩數目及製程步 驟,相對地使製作的難度提高,若能透過業界製程的幫助則有助於研究的 進展。 本研究的量測重點,在於低壓電路及相鄰高壓元件的漏電流,包括高 壓元件正向偏壓導通及逆向偏壓本體二極體導通時,所產生的漏電流。使 用的量測儀器為惠普 HP4155A。HP4155A 是一台模組化直流電源及直流 量測的儀器。它可依使用者需求,再待測的元件上,送出經由程式定義的 電流或電壓,並進行量測。HP4155A 將量測的結果存放在內建的暫存器 中。使用者可利用 PC 將這些數據取回做處理。 在量測漏電流前,需對元件本身的特性做量測,以得知高壓元件在正 向偏壓導通時,所能承受的最大的電流,及反向偏壓時本體二極體的導通 特性。外加偏壓在不損毀高壓元件的情況下,量測低壓電路及相鄰高壓元 件的漏電流。將所量得的漏電流與導通電流做正常化(normalize),比較量 測所得與模擬結果的趨勢是否相同,及其誤差。第四章 模擬結果與討論

本論文高低壓元件整合及高壓元件整合的漏電流模擬是採用 TMA 公 司的 MEDICI 軟體,為了方便更改佈局參數,先定義通用的高低壓整合及 高壓整合結構,如圖 4.1 及表 4.1 所示,表 4.1 中的參數是由 TSUPREM4 模仿業界所使用的 100V 高壓製程所得。 N+/P+ Vbias Anode Gate Cathode P well N well N+ CMOSStructure High Power Device

N-Epi P-Sub P+/N+ Vdd P+ N+ P+ N+ Dis

LPsink LPbase LEpi LNbuffer LCh LN DEpi DPbase LPplus LG ate DN D Nbuffer DPwell DNwell LPwell LNwell DPplus (a)高低壓整合 P-Sub Dis N+/P+ Vbias Anode Gate Cathode N+

High Power Device

P+/N+

LPsink LPbase LEpi LNbuffer

LCh LN D Epi DPbase LPplus LGate DN D Nbuffer N+/P+ Vbias

Anode Gate Cathode

N+

High Power Device

P+/N+ LPsink LEpi LPbase LNbuffer LCh LN DEpi DPbase LPplus LGate DN DNbuffer DPplus Vbias (b)高壓整合 圖 4.1 MEDICI 結構圖

表 4.1 LIGBT 結構參數表

參數名稱 定義符號 參數值

基板濃度 CPSUB 1.2E15(atom/cm3)

磊晶層濃度 CEPI 3E15(atom/cm3)

P-Sinker 濃度 CPSINK 1E18(atom/cm3)

P 阱(P 型基極)濃度 CPWELL 1E17(atom/cm3) N 阱(N 型緩衝層)濃度 CNWELL 1E17(atom/cm3) P+濃度 CPPLUS 1E19(atom/cm3) N+濃度 CN 3E18(atom/cm3) 磊晶層厚度 DEPI 10( µm) P-Sinker 深度 DPSINK 10( µm) P 阱(P 基極)深度 DPWELL 3.5( µm) N 阱(N 緩衝層)深度 DNWELL 3.5( µm) P+深度 DPPLUS 0.6( µm) N+深度 DN 0.6( µm) N 型漂移區寬度 LEPI 15( µm) P-Sinker 寬度 LPSINK 10( µm) P 型基極寬度 LPBASE 3( µm) N 型緩衝層寬度 LNBUFF 15( µm)(註 1) P+陽極寬度 LPPLUS 13( µm)(註 1) 通道寬度 LCH 2( µm) 閘極寬度 LGATE 3( µm) P 型集極寬度 LPPLUS 12( µm) N 型源極寬度 LN 2( µm) 元件間距離 DIS 10( µm)

註 1:LDMOS 時,原 P+陽極改為 N+。SA-LIGBT 時,N 型緩衝層寬度為 50 µm,P+陽極寬度為 42 µm,最末端 N+陽極為 6 µm。 Pwell Nwell N-epi 接地 高電位端 P+ P+ N+ N+ (a)CMOS 低壓電路 N -epi N -buffer N + P-sink P-base N + C athode Anode P-sub (b)LDMOS N -epi N -buffer P+ P-sink P-base N + C athode Anode P-sub (c)LIGBT N-epi N-buffer P-sink P-base N+ Cathode Anode P-sub P+ N+ (d)SA-LIGBT 圖 4.2 MEDICI 結構模擬圖

在圖 4.2 中,分別是 CMOS 低壓電路、LDMOS、LIGBT 及 SA-LIGBT 等 MEDICI 所繪製的結構圖。之後的模擬均是以這四個結構圖組合進行漏 電流模擬。 由於所模擬的高壓元件崩潰電壓約在 100V,因此在模擬高壓整合時將 相鄰高壓元件陽極端偏壓在 80V,陰極端接地。在高低壓整合模擬中,低 壓電路高電位偏壓在 5V,低電位接地。 將順向偏壓及反向偏壓分別討論,在順向及反向偏壓中再分高低壓整 合及高壓整合,依第三章所提的步驟依序模擬各項參數對漏電流的影響, 以期在不調變製程的情況下,盡可能地完整考慮能防制漏電流的變因。

4.1 順向偏壓

因為 LDMOS 為單載子元件,在導通的情況下,載子只流經閘極下方 的通道。不論在高低壓整合或高壓整合,當 LDMOS 導通時不會產生漏電 流,如圖 4.3 所示。

CMOS Structure LDMOS

(a) 高低壓整合

Main LDMOS Adjacent LDMOS

(b) 高壓整合

LIGBT,SA-LIGBT 為雙載子元件,有少數載子從陽極經 P 型基板流 向陰極,但低壓電路 P 阱與 P 型基板由於 N 型磊晶層的隔離,且空乏區沒 有發生穿透現象(punch-through),因此對低壓電路並不會有明顯的漏電 流,如圖 4.4 所示。

CMOS Structure LIGBT

(a) LIGBT

C MOS Structure SA-LIGB T

(b) SA-LIGBT

4.1.1 高壓整合

LIGBT,SA-LIGBT 為雙載子元件,其 P-sink 與 P 型基板相接,因此 當高壓元件整合,其一高壓元件導通時,從該高壓元件陽極流出的電洞載 子中部份會經由 P 型基板越至鄰近高壓元件的陰極端,如圖 4.5 所示。從 圖 4.5 的等效電路圖可知當 LIGBT,SA-LIGBT 導通時,漏電流的主要成 份為電洞。以下為各種隔離方法的分析與討論:Adjacent LIGB T Main LIGB T Anode1 C athode1 C athode Anode

流 密漸大

(電洞流)

(電 子流)

C ath ode Ano de Gate PNP PNP NMOS C atho de1 RP- su b (a) LIGBT

Adjacent SA-LIGB T Main SA-LIGBT Anode1 Cathode1 Cathode Anode

(電子流) (電洞流) C athode Anode Gate PNP PNP NMOS C athode1 RNb u f f er RP- su b

1. 改變元件間 N 型磊晶層的偏壓:在高壓整合中,可發現元件與元件間 N 型磊晶層偏壓在 5V 比浮接要略好一點,但漏電電流值的差異極微,如圖 4.6 所示,圖中縱軸 I(CATHODE1)為相鄰高壓元件陰極端的電流流密,橫 軸 I(ANODE)為主要高壓元件陽極端的電流流密。當元件間 N 型磊晶層偏 5V 可使 P 型基板的空乏區較大,如圖 4.7,使圖(b)中RP sub− 略增,使漏電 流減少。漏電電流值的差異微小是因元件間 N 型磊晶層偏壓對 P 型基板的 阻值影響極微,所以對漏電流的影響差異很小。 (a) LIGBT (b) SA-LIGBT 圖 4.6 高壓整合,元件間 N 型磊晶層不同偏壓比較

80V 0V 0V 3.43V

N-epi P-sink N-epi P-sink N-epi

P-sub C athode C athode1 RP- su b RP- sin k 1 RP- sin k Leakage C urrent(Hole) (a)元件間 N 型磊晶層浮接 80V 0V 5V 0V 3.43V

N-epi P-sink N-epi P-sink N-epi

P-sub 低電位通道區較(a)小 C athode RP- su b RP- sin k Leakage C urrent(Hole) C athode1 (b)元件間 N 型磊晶層偏壓 5V 圖 4.7 LIGBT 高壓整合,元件間 N 型磊晶層不同偏壓電位圖及等效電路 圖 2. 調變 P-sink 寬度及元件間距離:從圖 4.8 及圖 4.9 可知,當 P-sink 寬度 及元件間距離增加時,可使漏電流減少。增加 P-sink 寬度減少漏電流的幅 度較大,因為當 P-sink 寬度增加時,可以降低 P-sink 的阻值,吸收較多的 電洞。圖中 leakage_300 及 leakage_400 分別表示溫度在 300K 及 400K 的 I(Cathode1)/I(Anode)。在不同溫度對 LIGBT,SA-LIGBT 的漏電流影響不 同,主要是由於當溫度上升時,載子遷移率降低,使圖 4.7 中 RP-sub阻值增 加,造成 LIGBT 的漏電流減少;溫度上升時,雖然 SA-LIGBT 的基板阻 值亦會增加,但因溫度上升,陽極端的二極體較易導通,電流中電洞的成 份大幅增加,造成漏電流增加。

0.0000E+00 1.0000E-02 2.0000E-02 3.0000E-02 4.0000E-02 5.0000E-02 6.0000E-02 0 5 10 15 20 25 30 35 40 45 50 55 P-sink(um) I( ca tho de 1) /I (a nod e leakage_300 leakage_400 (a) LIGBT 0.0000E+00 5.0000E-03 1.0000E-02 1.5000E-02 2.0000E-02 2.5000E-02 3.0000E-02 3.5000E-02 4.0000E-02 0 5 10 15 20 25 30 35 40 45 50 55 P-sink(um) I( ca tho de 1) /I (a nod e leakage_300 leakage_400 (b) SA-LIGBT 圖 4.8 高壓整合,P-sink 寬度與漏電流關係圖

0.0000E+00 1.0000E-02 2.0000E-02 3.0000E-02 4.0000E-02 5.0000E-02 6.0000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Distance(um) I( ca tho de 1) /I (a nod e leakage_300 leakage_400 (a) LIGBT 0.0000E+00 5.0000E-03 1.0000E-02 1.5000E-02 2.0000E-02 2.5000E-02 3.0000E-02 3.5000E-02 4.0000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Distance(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (b) SA-LIGBT 圖 4.9 高壓整合,元件間距離與漏電流關係圖 3. 改變 N 型保護環及 P 型保護環偏壓:隔離結構中 N 型保護環浮接,且 P 型保護環偏壓在接地端效果最佳,如圖 4.10 所示,圖中縱軸 I(Cathode1) 為相鄰高壓元件陰極端的電流流密,橫軸 I(Anode)為主要高壓元件陽極端 的電流流密。因為漏電流的主要成份為電洞,將 P 型保護環偏壓在接地端

板的低電位通道退化,但由於其影響圖中的 RP-sub及 RP-sub1極微而影響 RPring 較大,使 P 型保護環吸收較少漏電流,則流至鄰近高壓元件陰極端的漏電 流略增。由表 4.2 可知,高壓整合且順向偏壓下,P 型保護環的偏壓影響 較大。 (a) LIGBT (b) SA-LIGBT 圖 4.10 高壓整合,隔離結構不同偏壓下,陽極電流與漏電流關係圖

Anode1 Cathode1 Cathode Anode Nring1 Nring

Pring

Main LIGBT

Adjacent LIGBT Cathode1 Cathode

RP-sub1

RP-sink1 RP-sink

Leakage Current(Hole) RP-sub

(a)N 型保護環浮接,P 型保護環浮接 Anode1 C athode1 C athode Anode

Nring1 Nring Pring

Main LIGB T

Adjacent LIGB T Cathode1 Cathode

RP-sub1 RP-sink1 RP-sink Leakage Current(Hole) RP-sub Pring RP-ring (b)N 型保護環浮接,P 型保護環接地 圖 4.11 高壓整合 LIGBT 含隔離結構,P 型保護環不同偏壓電流流密及等 效電路圖

N-epi1 P-sink1 Nring1 Pring Nring P-sink N-epi

P-sub 80V 0V 0V 0V 3.43V Cathode Cathode1 RP-sub1 RP-sink1 RP-sink Leakage Current(Hole) RP-sub Pring RP-ring (a)N 型保護環浮接,P 型保護環接地

N-epi1 P-sink1 Nring1 Pring Nring P-sink N-epi

P-sub 80V 0V 5V 0V 5V 0V 3.43V 低電位通道較退化 Cathode Cathode1 RP-sub1 RP-sink1 RP-sink Leakage Current(Hole) RP-sub Pring RP-ring (b)N 型保護環偏壓在 5V,P 型保護環接地 圖 4.12 高壓整合 LIGBT 含隔離結構,N 型保護環不同偏壓電位圖及等效

表 4.2 不同偏壓的漏電流比較 (a)LIGBT N 型保護環 P 型保護環 I(Cathode1)/I(Anode) 浮接 浮接 3.7438E-02 浮接 接地 1.6695E-02 5V 浮接 3.7923E-02 5V 接地 1.8131E-02 (b)SA-LIGBT N 型保護環 P 型保護環 I(Cathode1)/I(Anode) 浮接 浮接 2.4852E-02 浮接 接地 1.0805E-02 5V 浮接 2.5626E-02 5V 接地 1.1740E-02 4. 調變 P-sink、N 型保護環及 P 型保護環寬度:從圖 4.13~圖 4.15 可知, 不論增加 P-sink、N 型保護環或 P 型保護環均能大幅減少漏電流。P-sink 及 P 型保護環寬度增加可吸收較多基板中電洞載子,而 N 型保護環增加元 件間距離,減少漏電流。圖中 leakage_300 及 leakage_400 分別表示溫度在 300K 及 400K 的 I(Cathode1)/I(Anode)。在相同面積下,使用隔離結構比沒 有使用的隔離效果佳,其中又以增加 P 型保護環寬度所得到的效益最大, 因為當 P 型保護環寬度增加時,圖 4.12 中 RPring阻值下降,RP-sub1阻值上 升,有助於吸收 P 型基板中電洞,減少漏電流。其餘依序分別為 N 型保護 環寬度,P-sink 寬度(含隔離結構),P-sink 寬度,元件間距離,如圖 4.16 所示,圖中縱軸 I(Cathode1)為相鄰高壓元件陰極端的電流流密,橫軸 I(Anode)為主要高壓元件陽極端的電流流密。

0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 1.6000E-02 1.8000E-02 0 5 10 15 20 25 30 35 40 45 50 55 P-sink(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (a) LIGBT 0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 0 5 10 15 20 25 30 35 40 45 50 55 P-sink(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (b) SA- LIGBT 圖 4.13 高壓整合含隔離結構,P-sink 寬度與漏電流關係圖

0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 1.6000E-02 1.8000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Nring(um) I( ca tho de 1) /I (a nod e leakage_300 leakage_400 (a) LIGBT 0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Nring(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (b) SA-LIGBT 圖 4.14 高壓整合含隔離結構,N 型保護環寬度與漏電流關係圖

0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 1.6000E-02 1.8000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Pring(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (a) LIGBT 0.0000E+00 2.0000E-03 4.0000E-03 6.0000E-03 8.0000E-03 1.0000E-02 1.2000E-02 1.4000E-02 0 5 10 15 20 25 30 35 40 45 50 55 Pring(um) I(c at ho de 1)/ I(a no de leakage_300 leakage_400 (b) SA-LIGBT 圖 4.15 高壓整合含隔離結構,P 型保護環寬度與漏電流關係圖

(a) LIGBT

(b) SA-LIGBT

圖 4.16 相同面積下,高壓整合,不同佈局參數隔離效果比較 註:PSL 表 P-sink 寬度,D 表元件間距離,NL 表 N 型保護環寬度,PL 表 P 型保護環寬度

![圖 2.22 是溫度與載子濃度的關係圖[20]。從圖中可知對矽基板而言, 當溫度在 150K 到 450K,載子濃度約等於掺雜濃度。而在 100K 以下,由 於溫度較低,載子沒有足夠的能量脫離原子的吸引,因此載子濃度低於掺 雜濃度。當溫度高於 450K 時,本徵載子濃度(intrinsic carrier concentration) 大幅增加,因此載子濃度會大於掺雜濃度。隨著溫度增加,本徵載子濃度 增加,也造成理想反向飽合電流的增加。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8260357.172127/42.892.187.711.549.1068/以下由低載子原子吸引因此載子濃度低於雜濃度當徵載子增加徵載子.webp)