國 立 交 通 大 學

電機學院 電信學程

碩

士

論

文

應用於超寬頻之電容回授匹配與

電流再利用之超寬頻低雜訊放大器

An Ultra-Wideband LNA with capacitor feedback

and Current-Reused Technique for 3.1 to 10.6GHz

研 究 生:曾 智 群

指導教授:周復芳 博士

應用於超寬頻之電容回授匹配與

電流再利用之低雜訊放大器

An Ultra-Wideband LNA with capacitor feedback

and Current-Reused Technique for 3.1 to 10.6GHz

研 究 生:曾智群

Student:Chih-Chun Tseng

指導教授:周復芳 博士

Advisor:Dr.christina F.Jou

電機學院

電信學程

碩 士 論 文

A Thesis

Submitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in Communication Engineering

應用於超寬頻之電容回授匹配與

電流再利用之超寬頻低雜訊放大器

研究生:曾智群

指導教授:周復芳 博士

國立交通大學電機學院電信學程碩士班

摘

要

本篇論文主要是探討超寬頻低雜訊放大器之設計與分析。在第一級部

分,為了達到寬頻的輸入匹配,我們採用電容回授的方式,分別對高頻

及低頻作輸入匹配,及利用電感(

L

S)、電容(

C

gd)回授來達成輸入匹配;

接著第二級部分,利用疊接方式來達到電流重複使用,以降低功率消

耗,為了達到寬頻的增益,使用並串連尖峰電感(shunt-series peaking)

的頻寬延伸技術來完成寬頻增益的目的;最後我們採用一個LC串聯電路

方式,來達到輸出匹配。電路採用 TSMC 0.18μm 1P6M CMOS 製程實現,

在此架構電路實際量測結果如下:在供應電壓1.5V下,頻寬為3.1 ~ 10.6

GHz,輸入反射係數小於-10.07以下,輸出反射係數小於-15.2 dB以下,

平均順向增益大於6.66 dB,逆向隔離小於-28.25 dB以下,雜訊指數為

3.13~7.05 dB,input P1dB為-16dBm,最小值為IIP3為-10dBm,晶片消

耗功率為26.7mW.

An Ultra-Wideband LNA with capacitor feedback

and Current-Reused Technique for 3.1 to 10.6GHz

Student

:Chih-Chun

Tseng

Advisor

:Dr.Christina F. Jou

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

Abstract

T

his thesis discusses the design and analysis of an ultra wideband

low-noise amplifier. The first stage employees the capacitive feedback

with the source degenerated inductive feedback to achieve input

wideband matching, the second stage adopts current-reused cascaded

common-source structure to lower the power consumption. To obtain flat

gain over a wide bandwidth, the shunt-series peaking inductor is used.

Besides, the output impedance matching was achieved with the series

L-C network. To demonstrate the feasibility of the LNA, a 3.1 ~ 10.6

GHz LNA was designed and fabricated using the TSMC standard 0.18μm

1P6M CMOS process. The measurement results of the UWB LNA have

flat gain of 6.66 dB, input return loss smaller than -10.7dB,output return

loss small than -10.07 dB, good isolation of -28.25 dB, superior noise

figure of 3.13~7.05 dB, P1dB of -16 dBm, IIP3 of -10dBm with the

致謝

在這三年來的研究所生活中,特別要感謝我的指導教授「周復芳」博

士,感謝老師不僅僅在專業領域上的督促與訓練外,並且也從老師身

上學習到待人處世的態度、誠懇、謙遜與負責。也感謝口試委員胡政

吉博士與吳俊緯博士在口試時,對本論文提出的指導與寶貴的建議,

在此也致上深深的感謝。

另外,在晶片設計過程中,特別要感謝實驗室學長匯儀、宜星、

昭維、宗廷、玠瑝的幫忙與協助,同時也感謝冠儀、漢宗、與傑翔在

生活上及研究上的幫忙以及學弟政廷、柏儒與學妹珮玲你們的關心與

幫忙;感謝各位在這些日子的陪伴;也謝謝玠瑝與政廷及國家奈米實

驗室射頻量測實驗室全體同仁不辭辛苦地大力幫忙才得以把複雜的

量測工作完成。

最感謝就是我的老婆蕙甄,就是有你全心全力支持,讓我可以在

這三年無負擔的順利完成學業,同時感謝我的父母與家人,因為有你

們的照顧和支持,讓我能心無旁騖的完成學位。最後,僅把此論文的

榮耀獻給我的老婆、父母與以及身邊所有關懷我的朋友們。

于風城 2010.06

目錄

中文摘要………I 英文摘要………II 致謝………III 目錄………IV 表目錄………VI 圖目錄………VII 第一章 緒論 ………1 1.1 動機………1 1.2 論文架構 ……… 2 第二章 寬頻放大器相關技 ………3 2.1 超寬頻低雜訊放大器之設計簡介………3 2.2 寬頻低雜訊放大器介紹與比 ……… 32.3 低雜訊放大器(Low noise Amplifier)參數介紹 ………9

第三章 應用於超寬頻之電容回授匹配與電流再利用之低雜訊放大器…………11 3.1 簡介 ………12 3.2 寬頻輸入匹配級 ………13 3.3 電流重複利用架構 ………18 3.4 電流在利用放大級 ………19 3.5 電流再利用放大及原理 ………20 3.6 中間級串聯共振架構 ………22

4.3 結論 ………36 4.4 未來研究方向 ………37 參考文獻………39

表目錄

表 2.1 常見之寬頻低雜訊放大器比較表………8 表 4.1 表示模擬結果與量測參數值之比較……… 33 表 4.2 在相同技術下參數比較表……… 35 表 4.3 與其他技術參數比較表……… 36 表 4.4 以 PMOS 替代原負載電阻 RL 後之比較……… 37圖目錄

圖 1.1 UWB 的功率限制 ……… 1 圖 2.1 共閘極放大器 ……… 3 圖 2.2 常見的散佈式放大器架構 ……… 4 圖 2.3 cascade 結合散佈式之架構 ………5 圖 2.4 回授式放大器架 ……… 7 圖 2.5 回授式放大器輸入端等效電路圖 ……… 7 圖 2.6 Full-band Cascoded 電阻回授式放大器架………7 圖 2.7 輸入濾波器匹配放大器 ……… 8 圖 2.8 單級放大器之雜訊指數示意圖 ……… 9 圖2.9 1dB增益壓縮點示意圖……… 10 圖2.10 三階非線性現象示意圖………10 圖 2.11 三階截斷點(IP3)示意圖……… 11 圖 3.1 電容匹配與電流再使用之超寬頻低雜訊放大器之設計……… 12 圖3.2 寬頻輸入匹配級 ………13 圖3.3.1第一級放大器小信號等效電路………13 圖3.3.2 低頻小信號等效電路 ………14 圖3.3.3 第一級放大器在低頻響應下之模擬 ………14 圖3.3.4 高頻小信號等效電路 ………15 圖3.3.5 先將相依電流源g V 轉變為相依電壓源後之等效電路圖………16 m gs 圖3.3.6 第一級放大器在高頻響應下之模擬圖……… 17 圖 3.4 S11 寬頻帶輸入匹配模擬結果 ………17 圖 3.5.1 Current-reused topology………18圖 3.5.2 Current-reused With a series inter-stage resonance ………18

圖 3.6 電流在利用放大級……… 19 圖 3.7 簡易的第一級小信號電路圖……… 20 圖 3.8 電感 L4 對增益平坦度的影響 ……… 21 圖 3.9 電感 C3 對增益的影響………21 圖3.10 第二級放大器電路之小訊號模型………22 圖 3.11 電晶體 M3 尺寸對增益的影響 ………22 圖 3.12 電感 L5對增益的影響………23 圖 4.1 電容回授匹配與電流再利用之低雜訊放大器佈局圖……… 25 圖 4.2 參數變異範圍………25 圖 4.3.1 S11輸入阻抗之比較結果 ……… 26 圖 4.3.2 S22輸出阻抗之比較結果……… 26 圖 4.3.3 S12之比較結果……… 27 圖 4.3.4 S21之比較結果……… 27 圖 4.3.5 NF 之比較結果………27 圖4.3.6 穩定度模擬結果 ………28 圖4.3.7 P1dB在3.0GHz下之比較結果……… 29 圖4.3.8 P1dB在5.0GHz下之比較結果……… 29 圖4.3.9 P1dB在7.0GHz下之比較結果……… 30 圖4.3.10 P1dB在10.6GHz下之比較結果……… 30 圖4.3.11 IIP3在3.0GHz下之比較結果……… 31 圖4.3.12 IIP3在5.0GHz下之比較結果……… 31 圖4.3.13 IIP3在7.0GHz下之比較結果……… 32

第一章 緒論

1.1 動機[1][2]

隨著無線通訊發展,通訊傳輸從聲音、數據、影像到現今的多媒體應用,對 於無線通訊高資料量及低耗電的特性需求,已成為現今無線通訊系統之主要訴 求。因此短距離、低功率的超寬頻(Ultra-wideband, UWB)無線電技術被提出。 超寬頻技術使用在3.1 ~ 10.6 GHz的頻段,利用脈衝訊號方式表示0跟1來傳 輸資料,此脈衝訊號寬度約為1ns、發射功率約為10nW/Hz。相較於傳統無線通訊 技術,如802.11g、GSM、Bluetooth等,皆是利用載波方式在特定之頻帶傳送訊 號,因此在傳輸本質上,UWB的寬頻帶、脈衝訊號,與其他傳統無線通訊的窄頻 帶、連續性載波截然不同,明顯佔有優勢。其具有高傳輸速率、低耗電量、低成 本、干擾性低等特性,將成為極具競爭力的短距離無線傳輸技術。 UWB 由於資料傳輸率之優勢,各國已陸續開放其使用頻帶,但由於其所使 用之頻段跨越其他通訊已使用之頻段,為避免干擾其他通訊設備,必須限制其 發射功率(-41.3 dBm/MHz)使用,美國聯邦電信委員會(FCC)已訂出使用之功率 限制,如圖 1.1 所示。 圖 1.1 UWB FCC 輻射功率限制圖[1]1.2 論文架構

本論文使用 TSMC 0.18μm 1P6M CMOS 製程來實現所設計的超寬頻低雜訊 放大器電路,內容共分成三個章節。第一章為緒論,主要介紹超寬頻背景與特 性做簡單之介紹,最後探討論文之主體架構。第二章為探討寬頻放大器相關技 術並比較其優缺點。第三章是介紹利用電容匹配回授架構來達到寬頻輸入匹配 網路,並且搭配使用電流重複利用的技巧,設計低功率的低雜訊放大器。第四 章為針對電路 Post-simulation 與量測結果進行討論、比較與結論,並說明未 來研究的目標。第二章 寬頻放大器相關技術

2.1 超寬頻低雜訊放大器之設計簡介 由於低雜訊放大器為接收機的第一級放大,幾乎決定整個接收系統的雜音 指數,並且第一級的放大器增益越大,對後級元件所產生的雜訊抑制能力也越 好,通常低雜訊放大器前級一般為天線或濾波器,輸入端阻抗需匹配到 50 歐 姆。對於應用在超寬頻的低雜訊放大器,輸入阻抗匹配與增益必須涵蓋 3.1~ 10.6GHz。常見之參考文獻中,超寬頻低雜訊放大器可分為四種架構:共閘極 (common gate)架構、分散式(distributed)架構、回授式(feed back)架構及輸 入帶通濾波器匹配(input band-pass filter matching)架構。以下將分別說明。2.2 寬頻低雜訊放大器介紹與比較 (a).共閘極架構(common gate) [3] 共閘極放大器架構本身就有著寬頻的特性以及良好的線性度。如圖 2.1 所示,透過小訊號分析可得輸入阻抗為:Zin =1/(gm + jωCgs) ,其中 Cgs為電 晶體 M1之寄生電容;在低頻時輸入阻抗近似於 Zin ≈1/gm ,因此可達寬頻阻抗 匹配。然而應用於較高的頻率時,Cgs將開始影響輸入阻抗特性,此時可以利用 電感方式諧振掉電容效應,達到寬頻的操作。一般而言,在設定電晶體偏壓時, 主要是讓 gm=20mS。此架構雖然容易實現輸入阻抗匹配,但是共閘極放大器在雜 訊方面表現不佳,雜訊指數在製程下有最低限制(NF ≥ 2.2)。 圖 2.1 共閘極放大器

(b).分佈式放大器(distributed Amplifier)[4] 傳統分散式放大器,如下圖2.2所示。其架構為每一級電晶體寄生電容與電 感等效成一有限長傳輸線,並透過電晶體互相耦合閘極端和汲極端的等效傳輸 線,放大輸入訊號。因為電晶體的寄生電容屬於傳輸線的一部份,不會影響放大 器的增益和頻寬的乘積,所以此類放大器有較大的頻寬操作。分散式放大器通常 具有寬頻帶的特性,但因架構為多級的放大器,所以會產生相當大的功率消耗, 因此,並不合適用於低消耗功率方面的應用。在[4]論文研究參考中功率消耗為 7mW,但是在2.7~9.1GHz 的頻寬中增益只有10dBm。而如下圖2.3所示,在[5]論 文研究使用中,結合了cascade 架構與散佈式架構兩者的優點,得到很好的增益 及雜訊指數,其電路整體的增益可達到18dBm,但電路較佔面積且功率消耗高達 54mW。 以傳統的散佈式架構來說,雖具有寬頻增益的特性,但因為電感做為主要元 件使得整個電路的尺寸略顯龐大,使用了cascade 的架構雖然可以克服低增益響 應的缺點,但卻使得整體電路的尺寸更為龐大,且消耗更大的功率。 圖2.2 常見的散佈式放大器架構[4]

(c).回授式放大器(feed-back Amplifier) 利用回授電路可以延伸電路的頻寬,以及提供好的輸入阻抗匹配,並增進電 路的穩定性,卻必須犧牲增益去換取最佳化頻率響應。為了獲得較小雜訊和較大 增益,需增加電晶體尺寸或回授電阻RF,也因此造成功率消耗增加。雖然回授式 放大器能提供好的輸入阻抗匹配,但可能因為輸入寄生電容而限制於低頻部份。 如圖2.4所示[6] 為回授式放大器架構,主要是控制調整等效回授電阻,來 達到寬頻的效果。如圖2.5所示為輸入端小訊號等效電路,其中RfM為Rf的米勒等 效輸入電阻,可以表示成RfM = Rf (1− Av ),Av 表示放大器開迴路電壓增益。 透過小訊號分析可以得知,輸入阻抗由ωTLs決定,因此回授電阻(Rf)用來降低諧 振放大器輸入端網路的Q 值,其Q 值可以近似如下: 2 0 0 1 ( ) f g s T s gs M Q L R L C R ω ω ω ≈ ⎡ ⎤ + + ⎢ ⎥ ⎢ ⎥ ⎣ ⎦ g g (2.1) 從(2.1)式來考慮在-3dB 與Q 值之間的線性關係,適當選擇RfM可以達到寬頻的操 作。但是RfM電阻也會增加一些雜訊。電阻分流回授放大器的增益平坦度佳,能提 供良好的寬頻匹配,回授電阻會產生幾百歐姆去匹配訊號源電阻的50 Ω,但相 對卻會造成不小的功率消耗。

在[6]此論文研究參考中將傳統的窄頻式cascode LNA 與Resistive 並聯回 授電路相結合,雖然解決了Resistive 並聯回授且需要較大功率消耗的問題(只 消耗了12.6mW),但是整個頻寬只適用於較低頻的2GHz~4.6GHz,且增益也僅有 9.8dB。而如圖2.6,在[7]論文研究使用中,雖然頻寬增加至31.~10.6GHz,但卻 損失了雜訊指數並且功率消耗高達23.5mW。

圖2.4 回授式放大器架構

(d).輸入濾波器匹配放大器 源極電感退化式放大器是常見的低雜訊放大電路架構,它不僅有最佳的輸入 阻抗匹配,還有達到最大功率傳輸及最小雜訊的特性,但是此種方式多用在窄頻 系統使用。不過在寬頻的操作上,由於電晶體的寄生電容效應會降低操作頻寬, 因此在設計上常使用輸入濾波器匹配方式,利用電感、電容組成的寬頻架構並不 會造成過大的功率消耗,改善了原本窄頻的特性,使得電晶體輸入端在設計的頻 帶內有寬頻的效果,但是輸入端的匹配網路需要使用多個電感,使得晶片面積增 加,提高製作成本,且由於在輸入端加入太多電感,如果電感Q 值不夠高,往往 會造成雜訊上升,也會使輸入返回損耗S11表現變差。在[8]期刊中發表,利用 Chebychev 濾波器作輸入匹配,結合源極電感退化的架構如圖2.7所示。表2.1 說明以上四種常用架構之特性比較。 圖2.7 輸入濾波器匹配放大器[8] Tech. BW (GHz) S11 (dB) Gmax (dB) Min NF (dB) IIP3 (dBm) VDD (V) Power (mW) SIZE (mm) Topology [4] 0.18 2.7-9.1 <-10 10 3.8~6.9 1 0.6 7 1.57 Distributed

2.3 低雜訊放大器(Low noise Amplifier)參數介紹

一般在設計設計低雜訊放大器(Low noise Amplifier)時,一些用來定義或 描述其效能的參數應該先加以介紹。如:雜訊指數(Noise Figure) 、1dB 壓縮 點(1dB compression point)、輸入三階截取點(input third-order intercept point,IIP3)等。

1. 雜訊指數(Noise Figure)[9]

雜訊因數(noise factor)和雜訊指數(noise figure),都是用來表示接收 系統或是放大電路中雜訊之參數。放大器之雜訊指數示意圖,如圖 2.8。 雜訊因子(noise factor)定義表示為式(2.2) 。

(

,)

,@ total output noise

1 @ output noise dut to input source resistance

1 i i i i o o i i o o i a input i a a input i i i S S N N N SNR input F S GS SNR output GN N N G N N GN N N GN GN N = = = = = ≥ + + = = = + (2.2) 圖 2.8 中輸入訊號 Si及輸入雜訊 Ni ,經增益為 G 之放大電路,產生輸出信號 So 、輸出雜訊 No、輸入所增加之雜訊Na input, 。 而雜訊指數(noise figure) 定義表示為式(2.10): 10 10log NF = F(dB) (2.10) 圖 2.8 單級放大器之雜訊指數示意圖 So/No Si/Ni Gain

2. 1dB增益壓縮點(P1dB Gain Compression Point)[9] 放大器之操作區域中,輸出功率(Output Power)將正比於輸入功率(Input Power),呈現線性之增加,此線性化增加之常數一般稱為增益(Gain)。當輸 入信號超過一定功率時,輸入功率與輸出功率之線性關係將不再維持,而會進入 飽和或稱為壓縮,故定義當輸入功率增加至使得原本線性化輸出功率下降1 dB, 亦即增益下降1 dB 時,相對應之數值稱為1-dB 壓縮點(P1dB),如圖2.9所示。 圖2.9 1dB增益壓縮點示意圖

3. 第三截斷點(Third-order intercept point,IP3)[10]

在無線系統接收中,將兩個很接近(ω1、ω2)的頻率輸入至放大器時,由於 電路元件的非線性效應,產生交互調變造成許多高階諧波,其中三階交互調變 (2ω ω1− 2和2ω ω2− )的輸出是我們比較重視的,因為此諧波會落於非常接近主1 要頻率訊號ω1與ω2的兩旁,而濾波器無法濾除如此鄰近的干擾訊號,因此,會 造成主訊號的失真且會干擾其他頻道的訊號,進而增加解調位元錯誤率(Bit Error Rate,BER),造成訊號品質惡化。如圖2.10為三階非線性現象示意圖。

因此三階截斷點(IP3)為衡量電路線性度重要參數,其定義為主頻功率與三 階非線性項功率延長線的交點。如圖2.11所示,為三階截斷點(IP3)示意圖,其 中IIP3及OIP3分別為輸入及輸出的三階截斷點(input or output third-order intercept point) ,一般而言,交會點越高,或者IIP3及OIP3越大,代表線性 度越佳。

第三章

應用於超寬頻之電容回授匹配

與電流再利用之低雜訊放大器

3.1 簡介

在設計寬頻低雜訊放大器時,需考慮到的重要參數有輸入阻抗(Input matching)、雜訊指數(Noise Figure) 、P1dB 壓縮點(1dB compression point)、 輸入三階截取點(input third-order intercept point,IIP3)以及工作頻率範圍 內的增益平坦度(Gain Flatness)的特性都是必須列入設計的考量之中。

本論文研究的寬頻低雜訊放大器電路架構共有二級: 第一級為輸入匹配級 (Input matching stage),是利用電容回授方式與源級衰退電感(Source De- generated Inductor)所組成的放大器架構,來完成寬頻的輸入阻抗匹配。 第二級放大器為兩個NMOS疊接(Cascade)的共源級(Common Source)放大器架構, 且電路為共用電流(Current-Reused)方式,使能達到高增益表現且降低電路的功 率消耗,其中兩級(M2,M3) 並且分別諧振於不同的頻率,以達到超寬頻3.1 ~ 10.6

3.2 寬頻輸入匹配級(Input matching stage)[11]

此電路是利用第一級放大器輸出端的RC負載、L2、C1回授(feedback)及Lg作輸 入端匹配輸入匹配,降低輸入端的匹配網路複雜度,以達到寬頻的需求。如圖3.2 所示。電阻R2是為了防止震盪增加電路的穩定度,R1為大電阻,主要是避免RF訊 號洩漏而影響偏壓。 圖3.2 寬頻輸入匹配級 z 輸入匹配分析[12] 圖3.3.1為第一級放大器M1加上負載的完整小訊號模型等效電路。其中此負載RL 與CL即為第二級放大器之寄生電容與寄生電阻。為了分析輸入匹配網路,在此將 它分成低頻響應及高頻響應分別如圖3.3.2及圖3.3.3所示。 圖3.3.1 第一級放大器小信號等效電路在低頻響應下之輸入阻抗分析: 如圖3.3.2所示,此時負載僅為RL之效應。若將Cgd及ro忽略,且假設Cgs之阻抗 遠大於Ls之阻抗的條件下,則小信號等效電路輸入阻抗方程式可近似為: ( ) 1 s m gs 1 s m inL g gs gs gs gs L g j C L g Z j L j C C j C C

ω

ω

ω

ω

+ = + ≈ + (3.1) 圖3.3.2 低頻小信號等效電路 由(3.1)式可以得知,當相依電流gmVgs流經電感Ls時,將產生與輸入電流相同 位(In Phase)之電壓,此時可產生其值 s m gs L g C 之輸入電阻。當較小之Cgd將會增加 有效輸入電容,且當一有限值ro將會衰退gm,並且會降低由Ls所產生之輸入阻抗 的實部。因此,假設ωLS << 1/ωCgs,ωLS << RL 且流經Cgd之洩漏電流(Leakage Current)遠小於汲極電流時。則 (3.1)式之較理想的表示示為:(

)

1 1 1 1 L gd s m inL g m gs gs gs C L g Z j L g R j C C Cγ

ω

γ

ω

− ⎛ ⎞ ⎡ ⎤ = +⎜⎜ + ⎟ ⎢⎟ ⎢ + + ⎥ ⎥ ⎝ ⎠ ⎣ ⎦ (3.2) 其中 o o L S r r R j L γ ω = + + (3.3) 由方程式(3.2)可知,Z 為一個R、L、C串聯電路。圖3.3.3所示為第一級放大圖3.3.3 第一級放大器在低頻響應下之模擬圖 在高頻響應下之輸入阻抗分析: 如圖3.3.4所示,此時負載僅為CL之效應。 圖3.3.4 低頻小信號等效電路 在此先將相依電流源g V 轉變為相依電壓源m gs g r V ,如圖3.3.5所示。 m o gs freq (0.0000Hz to 15.00GHz) S (1, 1) 2 4 6 8 10 12 14 0 16 -15 -10 -5 -20 0 freq, GHz d B (S (1 ,1 ))

圖3.3.5 先將相依電流源g V 轉變為相依電壓源後之等效電路圖 m gs 其中Ya為從Cgd分之看入所形成的導納,而Zb為從Cgs分之看入之所形成的阻抗,V1、 V2及V3分別為MOS之G、D、S端點之電壓。若相依電流g V 遠大於流經Cm gs gd或Cgs之 電流時,則迴路電流ILoop可近似為: 1 1 Loop m o gs o s L I g r V r j L j C

ω

ω

− ⎡ ⎤ = ⎢ + + ⎥ ⎣ ⎦ (3.4) 因此,Cgd分之看入時所形成的導納Ya為: 1 1 2 1 1 a gd gd a a a V V Y j C j C R j L V j C ω ω ω ω − ⎛ ⎞ − = = +⎜ + + ⎟ ⎝ ⎠ (3.5) 其中 L a m gd C R g C = Ca =g r Cm o gd s L(

1)

a m o m o gd L C L g r g r C = + (3.6) 而從Cgs分之看入時所形成的阻抗Zb為: 1 1 1 1 1 1 1 1 b b gd gd b b V Z j C j Cω V V j Cω R ω j Lω − ⎛ ⎞ = = +⎜ + + ⎟ − ⎝ ⎠ (3.7) 其中: m s b g L R =因此,可由Ya及Zb的關係得知電容性負載時所形成的輸入阻抗為: 1 1 inH a b Z Y Z − ⎛ ⎞ =⎜ + ⎟ ⎝ ⎠ (3.9) 由方程式(3.9)可知,ZinH為一個R、L、C串聯再並聯電容電路。圖3.3.6所示為 第一級放大器在高頻響應下的模擬結果。 圖3.3.6 第一級放大器在高頻響應下之模擬圖 freq (0.0000Hz to 15.00GHz) S (1, 1) 2 4 6 8 10 12 14 0 16 -20 -15 -10 -5 -25 0 freq, GHz d B (S (1 ,1) ) 圖3.4 S11寬頻帶輸入匹配模擬結果 freq (0.0000Hz to 10.00GHz) S (1, 1) 1 2 3 4 5 6 7 8 9 0 10 -20 -15 -10 -5 -25 0 freq, GHz d B (S (1 ,1 ))

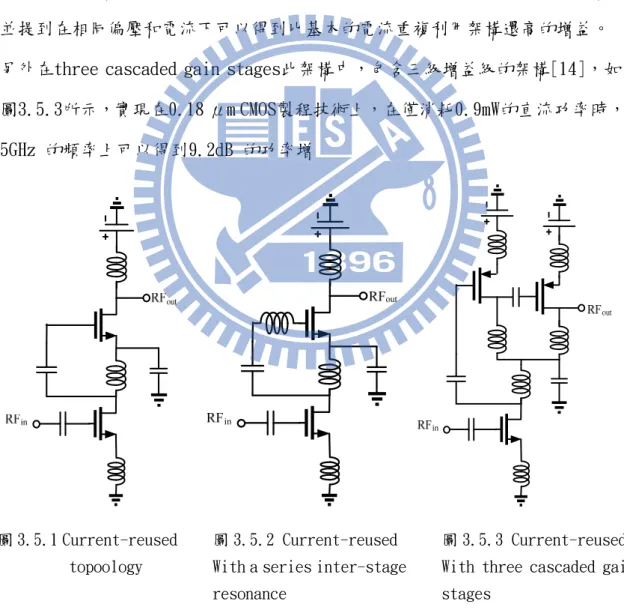

圖 3.5.1 Current-reused topoology

圖 3.5.2 Current-reused With a series inter-stage

圖 3.5.3 Current-reused With three cascaded gain

3.3 電流再利用架構

為了節省低雜訊放大器的供應電壓和消耗功率,且依舊提供足夠的增益,常 使用電流重複利用的架構, 此低功率消耗的技術是由基本Cascode、Inverter 架 構所延伸發展的,如圖3.5.1為基本的電流重複利用架構,對直流而言電路為 Cascode形式,共用一電流源可減少功率消耗,而對小訊號來說電路是Cascade 形式,擁有較大的增益。之後有人更進一步的延伸此架構,提出with a series inter-stage

resonance架構[13],如圖3.5.2所示,使用電流重複利用包含LC串聯共振架構, 並提到在相同偏壓和電流下可以得到比基本的電流重複利用架構還高的增益。 另外在three cascaded gain stages此架構中,包含三級增益級的架構[14],如 圖3.5.3所示,實現在0.18 μm CMOS製程技術上,在僅消耗0.9mW的直流功率時, 5GHz 的頻率上可以得到9.2dB 的功率增

3.4 電流再利用放大級 (Current reused amplifier stage)

第二級放大器為兩個 NMOS 共源極放大器組態疊接(Cascode)而形成的架 構,如圖 3.6 電路中所示。 此放大器利用電路中,L4為共源極放大器 M2的負載(peaking),目的為阻擋 RF 訊號流至 M3之 source 端,並使共用電流由 M3流至 M2。C3為旁路(Bypass)電 容,其功能則為提供第二級有個交流接地路徑的功能以形成 common source 放 大並避免信號耦合到第一級。C4為耦合(Coupling)電容,目的為讓 RF 訊號送至 第二级之共源放大器,並阻擋直流流入。L5用以被調整與 M3之 Cgs形成串聯諧振 (Series- Resonance)電路,達成兩組放大器間訊號之耦合,以將訊號傳遞至輸 出端。可使增益在設計的頻段達到較佳的平坦度與增益值。R5、L6則為共源極 放大器 M3的負載,目的為並聯尖峰(Shunt Peaking)之設計方式,其可提供延 伸所設計之高頻頻寬與增益平坦度。L7與 C5則是負責此電路的輸出阻抗匹配達至 50 Ohm。R4則是提供偏壓的作用,電阻值以不明顯增加 noise figure 作為

考量因素。

3.5 電流再利用放大及原理[16]

如圖 3.7 所示為簡易的第一級小信號電路圖,id2 是電晶體 M2 的小訊號汲 極電流;L4是第一級的負載電感,CL2 跟 RL2 則是它的雜散電阻跟電感;Cpar2 則 是代表著 M2 的汲極端所有的雜散電容,而 Vo2 是小訊號電壓。可得知第一級的 增益( 02 2 d v i ) 可由式(3.10)表示: 02 2 2 2 4 2 4 2 3 2 4 2 3 1 1 ( ) 1 1 1 1 1 ( ) d par par L L L L v s i sC sC sL R sL R sC sC sL R sC = = + + + + + + + (3.10) 其中,雜散電容 CL2 極小可忽略。 2 4 3 02 2 2 2 4 2 2 2 3 1 ( ) 1 L par d par par L R j L C v C i L C j C R C ω ω ω ω ω ⎛ ⎞ + ⎜ − ⎟ ⎝ ⎠ = − + + (3.11) 圖 3.7 簡易的第一級小信號電路圖 由式(3.10)與(3.11)可得知,第一級電壓增益主要取決於負載電感 L4 、汲極端 的寄生電容 Cpar2,及旁路電容 C3 。當 L4的感值增加時,低頻增益會增加,原因 是 L4為低頻段的鋒值(peaking),圖 3.8 表示為電感 L4 對增益的影響。且 C3 可使第一級共源級放大得到一個近似理想的接地,圖 3.9 表示為電容 C3 對增益0 2 4 6 8 10 12 14 Frequency (GHz) -5 0 5 10 15 20 d B (S (2 ,1 )) L4 Size=2.25 dB(S(2,1)) L4 Size=3 dB(S(2,1)) L4 Size=3.5dB(S(2,1)) 圖 3.8 電感 L4 對增益的影響 0 2 4 6 8 10 12 14 Frequency (GHz) -5 0 5 10 15 20 d B (S (2 ,1 )) C3 @ 1pF(S(2,1)) C3 @ 2pF(S(2,1)) C3 @ 3pF(S(2,1)) C3 @4pF(S(2,1)) 圖 3.9 電感 C3 對增益的影響

3.6 中間級串聯耦合(Series inter-stage Coupling)架構[17][18]

圖3.10為inter-stage resonate小訊號等效示意圖表示之。若忽略M3之Cgs下, 以M2之Drain為輸入端,到M4之Drain為輸出端所形成的小信號模型,為圖3.10所 示。 C4 L5 L4 Cgs3 gm3Vgs3 Id2 Id3 + -Vgs3 Vx Cd 圖3.10 第二級放大器電路之小訊號模型 其電流增益如(3.7)式所示: 4 3 3 2 3 4 5 4 3 1 1 1 1 d m d d gs d gs sL i g sC i sC sL sL sC sC C + = + + + + (3.12) 從(3.7)可得知,當 L4與 Cd形成高阻抗且 L5與 Cgs3形成共振時,可使增益在設計 的頻段達到較佳的平坦度與增益值。圖 3.11 與圖 3.12 表示為電晶體 M3 尺寸與 電感 L5在共振下對增益的影響。 3 6 9 12 15 18 d B (S( 2 ,1 )) M3 Size=8 dB(S(2,1))0 2 4 6 8 10 12 14 Frequency (GHz) -10 -5 0 5 10 15 20 d B (S (2 ,1 )) L5 Size=2.25 dB(S(2,1)) L5 Size=3 dB(S(2,1)) L5 Size=3.5dB(S(2,1)) 圖 3.12 電感 L5對增益的影響

第四章 電容回授匹配與電流再利用之低雜訊放大器模擬

4.1 佈局考量與電路佈局圖

在高頻元件佈局上,元件放置與走線(Metal Line)的不同,不但與面積大小 有關,更與電路特性有密切的關係,最主要是走線所產生寄生效應。導線(Trace) 之長度需越短越好,以避免產生過大的損耗及過多的寄生電感與寄生電容。走線 在轉角處時,應走45°角而避免90直角的發生,主要是因為電荷會集中在轉彎的 90°尖角處,產生尖端放電效應,嚴重影響電路特性。 走線寬度的決定,取決於通過該導線的電流密度(Current density),因此 電源線(Power line)和資料線(Data line)所需要的走線寬度自然也就不同,金 屬導線層不同其密度也有所不同,Metal6~ Metal1 中,Metal6 密度最低,Metal1 則反之。盡量可能的避免長距離的平行線出現,以防止串音(Crosstalk)現象發 生。直流導線上需加上旁路電容,以避免導線產生電感效應。使用的MOS 電晶體、 電感、電容、電阻,均有內建一圈保護環(Guard-Ring)將元件包圍起來,可有效 防止元件與元件或走線之間的訊號干擾。在完成佈局及電路模擬後,須執行設計規則檢查(Design Rule Check; DRC) 和佈局與線路比對(Layout versus schematic; LVS)驗證無誤後即完成佈局。在 完成佈局後晶片尺寸為0.95*0.77 mm2 ,如圖4.1所示。 圖4.1 電容回授匹配與電流再利用之低雜訊放大器佈局圖

4.2 模擬結果

在電路設計階段,電晶體的特性參數會隨製程的變異因素(process corner) 會產生漂移。依據特性漂移的範圍訂定電晶體的參數變異範圍,NMOS 及PMOS 分 別定義三組參數(slow, typical, fast),電路的模擬應考慮參數的變動corners simulation (SS,,TT,,FF),以供模擬實際下線結果參考,如圖4.2所示此論文電路模擬結果與量測之比較分別如下列各圖所示,並將其結果參數值列於 表4.1,此外將其結果參數值與其他論文之比較列於表4.2與表4.3。 圖 4.3.1 S11輸入阻抗之比較結果 -35 -30 -25 -20 -15 -10 -5 0 dB(S(2,2)) Sim_dB(S(2,2))

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Frequency (GHz)

-130 -120 -110 -100 -90 -80 -70 -60 -50 -40 -30 -20 freq Sim_dB(S(1,2)) 圖 4.3.3 S12之比較結果 0 2 4 6 8 10 12 14Frequency (GHz)

-20 -15 -10 -5 0 5 10 15 20 dB(S(2,1)) Sim_dB(S(2,1)) 圖 4.3.4 S21 之比較結果3 4 5 6 7 8 9 10 11 12 Frequency (GHz) 0 1 2 3 4 5 6 7 8 9 10 N F (d B ) Sim_NF (dB) NF (dB) 圖 4.3.5 NF之比較結果

圖4.3.7 P1dB在3.0GHz下之比較結果

圖4.3.11 IIP3在3.0GHz下之比較結果

Frequency 3.1~10.6GHz

Conner Post-sim Measured

S11(dB) < -10.7 < -10.07 S22(dB) < -10.6 < -15.2 S12(dB) < -29.7 < -28.25 S21(dB) < -10.6 < 6.66 N.F.(dB) 3.41~4.55 3.13~7.05 3.1GHz -8.1 -10 5.0GHz -5.1 -7 7.0GHz -5.0 -1.8 IIP3(dBm) 10.6GHz -2.2 4 3.1GHz -19.5 -16 5.0GHz -19.0 -11.2 7.0GHz -18.5 -9.5 P1dB(dBm) 10.6GHz -16.25 -5 Power (mW@1.5V) 25.485 26.7 表4.1 表示模擬結果與量測參數值之比較

一、 相關研究比較:

[19] [20] [21] Post-Sim Measure

Technology 0.13μm CMOS 0.18μm CMOS 0.18μm CMOS 0.18μm CMOS 0.18μm CMOS

Topology Current-reuse Current-reuse Current-reuse

Feedback+ Current-reuse Feedback+ Current-reuse RF(GHz) 3.1–10.6 3.1–10.6 3.1–10.6 3.1–10.6 3.1–10.6 S11(dB) < -17.5 < -8.7 <-8.6 < -10.7 < -10.07 S22(dB) < - 14.4 < -10.9 <-8 < -10.6 < -15.2 S21(dB) 7.92±0.23 10.0-13.1 9.5 <12.1 < 6.66 NF(dB) 2.5 - 4.56 2.7-4.9 5-5.6 3.41~4.55 3.13~7.05 P1dB(dBm) -14 * NA NA -21.5 -16 IIP3(dBm) -4 * NA NA -8.1 -1.8

[22] [23] [24] Post-Sim Measure

Technology 0.18μm CMOS 0.18μm CMOS 0.18μm CMOS 0.18μm CMOS 0.18μm CMOS

Topology Dual Feedback Cascad+ CS CG+ Cascad

Feedback+ Current-reuse Feedback+ Current-reuse RF(GHz) 3.1–10.6 3.1–10.6 2-10.1 3.1–10.6 3.1–10.6 S11(dB) -11.24 dB -9.7 to -19.9 <-9.76 < -10.7 < -10.07 S22(dB) -18.5 dB -8.4 to -22.5 NA < -10.6 < -15.2 S21(dB) 10.87 ~ 12.02 dB 11.4 ± 0.4 10.2 <12.1 < 6.66 NF(dB) 4.7 ~ 5.6 dB 4.12 ~ 5.16 3.68 3.41~4.55 3.13~7.05 P1dB(dBm) -20 -7.86* NA -21.5 -16 IIP3(dBm) -12.0 ~ -10.6 0.72* -1* -8.1 -1.8 Chip area (mm2) 0.665 0.447 NA 0.72 0.72 Power consumption (mW) 10.57 22.7 7.2 10.24 26.7 *At 6.4 GHz 表4.3 與其他技術參數比較表

4.3 結論

本論文提出3.1~10.6GHz之超寬頻低雜訊放大器的設計與製作,主要是利用 電容回授與電流再利用放大電路來完成。論文中,討論了設計觀念,模擬結果的 討論,再者設計LNA所需之放大器,分析與評估系統規範與需求,以低消耗功率 與低雜訊為目標。此晶片利用第一級放大器的輸出負載(RC Loading)及兩個電感 (Lg,LS)作匹配,減少輸入端的匹配電路,有效的降低雜訊指數,而cascade架構 提供較好的頻率響應(frequency response)與隔絕度(isolation),在第一 級放大器輸入端串上一個電感,且利用Cgd及LS回授來達到寬頻的輸入匹配。 在此架構電路實際量測結果如下:在供應電壓1.5V下,頻寬為3.1 ~ 10.6 GHz, 輸入反射係數小於-10.07以下,輸出反射係數小於-15.2dB以下,平均順向增益 大於6.66dB,逆向隔離小於-28.25dB以下,雜訊指數為3.13~7.05dB,input P1dB 為-16dBm,最小值為IIP3為-10dBm,晶片消耗功率為26.7mW。 為了電路能達到輸入阻抗50歐姆,必須在回授電容與NMOS尺寸上做取捨,此兩 種參數會使影響電路的雜訊指數、增益與消耗功率。當回授電容增大時,會使在 低頻段的增益值降低並且雜訊指數也增加,但若是增加NMOS的尺寸,雖然能改善 增益與雜訊卻增加總體的消率功率,也是此電路架構在未來需要作改善的地方。4.4 未來研究方向

在此論文架構中,輸入匹配級部份,由於在drain端使用一顆負載電阻RL,導致 消耗了部分功率,並且必須在回授電容與NMOS尺寸上做取捨,而嚴重影響到電路 的雜訊指數、增益與消耗功率。為了改善此問題,希望能使用一顆PMOS來替代電 阻RL,不僅能大大減少功率損耗且達到原有的效能,如圖5.1所示,為PMOS來替 代電阻RL。 在 per-simulation @SS 製程變異模式下,修改後與原電路架構下模擬結果 如圖 5.2.2 所示,其結果參數值列於表 5.1;可由表 5.1 得知,將原負載修改為 PMOS 後,不僅能減少功率損耗且達到原有的效能。 圖 4.4 以 PMOS 替代原負載電阻 RL 之電路 電路種類 原負載電阻電路 修改為 PMOS 之電路 Conner SS SS S11(dB) < -10 <10.7 S22(dB) < -11.18 <11.4 S21(dB) <14 <14.4 N.F.(dB) 2.022~3.53 1.76~3.47 Power (mW@1.5V) 13.4 9.63參 考 文 獻

[1] 江坤山,“寬頻無線傳輸,發射!"2005 年 12 月科學人雜誌。

[2] M. P. Wylie-Green, P. A. Ranta, J. Salokannel, “Multi-band OFDM UWB solution for IEEE 802.15.3a WPANs”, Advances in Wired and Wireless Communication, 2005 IEEE/ Sarnoff Symposium, pp.102-105, April 18-19, 2005.

[3] R.-H. Y. Behzad Razavi and K. F. Lee, "Impact of Distributed Gate Resistance on the Performance of MOS Devices,"IEEE Transaction on Circuit and Systems-I: Fundamental Theorey and Applications, vol. 41, pp. 750-754, Nov. 1994.

[4] Y. H. Yu, Y. J. Chen, Heo D, ”A 0.6 V low power UWB CMOS LNA,” IEEE Microwave and Wireless Components Letters, Vol. 17, pp.229–231, March 2007.

[5] K. H. Chen, C. K. Wang, “A 3.1-10.6GHz CMOS Cascade Two-stage Distributed Amplifier for Ultra-Wideband Application” IEEE Asia-Pacific Conference on Advanced System Integrated Circuit, pp. 296-299, August 4-5, 2004.

[6] R.-L. Wang, M.-C. Lin, C.-F. Yang, and C.-C. Lin, “A 1 V 3.1–10.6 GHz full-band

cascode UWB LNA with resistive feedback,” in Proc.IEEE EDSSC Conf., Dec. 2007, pp. 1021–1023.

[7] C. W. Kim, M. S. Kang, P. T. Anh, H. T. Kim, S. G. Lee, ”An Ultra-Wideband CMOS Low Noise Amplifier for 3-5GHz UWB system” IEEE Journal of Solid-State Circuit, Vol. 40, No. 2, pp. 544-547, Feb. 2005.

[8] A. Bevilazqua, “An Ultra-Wideband CMOS LNA for 3.1 ~ 10.6GHz Wireless Receivers, ” IEEE International Solid-State Circuits Conference, vol. 37, pp.382-383, Feb. 2004. [9] Guillermo Gonzalez, ”Microwave Transistor Amplifiers Analysis and Design”, Prentice

Hall Upper Saddle River, New Jersey, 1997.

[10] B. Razavi, “RF Microelectronics”, Prentice Hall Inc., 1998 [11] A. Maas, Nonlinear Microwave Circuits, Artech House, 1988.

[12] Po-Wei Lee, Hung-Wei Chiu, Tien-Ling Hsieh, Guo-WeiHuang and Shey-Shi Lu , ”Miniaturized Triple Band 2.4/5.2/5.7GHz Low Power SiGe Integrated Low Noise Amplifier For WLAN “.

[13] Robert Hu , “Wide-Band Matched LNA Design Using Transistor’s Intrinsic Gate–Drain Capacitor”, IEEE Transactions on Microwave Theory and Techniques, vol.54, NO. 3, MARCH 2006

[14] C. Y. Cha and S. G. Lee, “A low power, high gain LNA topology,” IEEE International Conference on Microwave and Millimeter Wave Technology Proceedings, pp.420–423, 2000.

[15] H. H. Hsieh and L. H. Lu, “Design of ultra-low-voltae RF frontends with complementary current-reused architectures,” IEEE Transactions on Microwave Theory and Techniques, Vol. 55, pp. 1445–1458, July 2007.

[16] F. Xiaohua, S.-S.Edgar, and S.-M. Jose, “A 3GHz-10GHz Common gate ultra wideband Low Noise Amplifier,” in Proc. Midwest Symposium on Circuit and Systems, vol.1, pp. 631-634, Aug. 2005.

[17] Chang-Ching Wu, Mei-Fen Chou, Wen-Shen Wuen, and Kuei-Ann Wen, “A low power CMOS low noise amplifier for ultra-wideband wireless applications, ”IEEE International Symposium on Circuits and Systems (ISCAS), vol. 5, pp.5063- 5066, May 2005.

[18] Choong-Yul Cha and Sang-Gug Lee, “A 5.2-GHz LNA in 0.35μm CMOS Utilizing Inter- Stage Series Resonanceand Optimizing the Substrate Resistance”, IEEE journal of solid- state circuits,vol.38, NO. 4, APRIL 2003

Circuits Symposium, 2008. RFIC 2008. IEEE June 17 2008-April 17 2008 Page(s):501- 504 Digital Object Identifier 10.1109/RFIC.2008.4561486

[21] Zhe-Yang Huang; Che-Cheng Huang; Yeh-Tai Hung; Meng-Ping Chen; “A CMOS current reused low-noise amplifier for ultra-wideband wireless receiver” Microwave and Millimeter Wave Technology, 2008. ICMMT 2008. International Conference on Volume 3,21-24 April 2008 Page(s):1499 – 1502 Digital Object Identifier 10.1109/ICMMT.2008. 4540731

[22] Kao, H.L.; Chin, A.; Chang, K.C.; McAlister, S.P.;” A Low-Power Current-Reuse LNA for Ultra-Wideband Wireless Receivers from 3.1 to 10.6 GHz” Silicon Monolithic Integrated Circuits in RF Systems, 2007 Topical Meeting on 10-12 Jan. 2007 Page(s): 257 - 260 Digital Object Identifier 10.1109/SMIC.2007.322807

[23] Chang-Tsung Fu; Chien-Nan Kuo; ” 3~11-GHz CMOS UWB LNA using dual feedback for broadband matching” Radio Frequency Integrated Circuits (RFIC) Symposium, 2006 IEEE 11-13 June 2006 Page(s):4 pp. - 56 Digital Object Identifier 10.1109/RFIC.20006 1651089

[24] Lee, J.-H.; Chen, C.-C.; Lin, Y.-S.;”0.18μm 3.1-10.6 GHz CMOS UWB LNA with 11.4±0.4 dB gain and 100.7± 17.4 ps group-delay ”Electronics LettersVolume 43, Issue 24, Nov. 22 2007 Page(s):1359 - 1360 Digital Object Identifier 10.1049/el:20071702 [25] Bo- Yang Chang; Jou, C.F.;”Design of a 3.1-10.6GHz low-voltage, low-power CMOS low-noise amplifier for ultra-wideband receivers ”Microwave Conference Proceedings, 2005. APMC 2005. Asia-Pacific Conference ProceedingsVolume 2, 4-7 Dec.2005 Page(s):4 pp. Digital Object Identifier 10.1109/APMC.2005.1606458

![圖 2.3 cascade 結合散佈式之架構[5]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8471136.183542/15.892.186.691.107.830/圖23cascade結合散佈式之架構5.webp)