國立交通大學

工學院半導體材料與製程設備學程

碩士論文

覆晶錫鉛銲錫以熱時效處理後之

電遷移失效時間與微結構研究

Electromigration Failure Time and Micro-structure Study in

Flip-Chip SnPb Solder Joints by Different Pre-aging Times

研究生:譚志祥

指導教授:陳智 博士

覆晶錫鉛銲錫以熱時效處理後之電遷移失效時間與微

結構研究

Electromigration Failure Time and Micro-structure Study in

Flip-Chip SnPb Solder Joints by Different Pre-aging Times

研 究 生:譚志祥 Student:Chih-hsiang Tan

指導教授:陳 智博士 Advisor:Dr. Chih Chen

國 立 交 通 大 學

工學院半導體材料與製程設備學程

碩 士 論 文

A Thesis

Master Degree Program of Semiconductor Material and Processing Equipment College of Engineering

National Chiao Tung University in Partial Fulfillment of the Requirements

for the Degree of Master

in

Program of Semiconductor Material and Processing Equipment January 2011

Hsinchu, Taiwan, Republic of China

覆晶錫鉛銲錫以熱時效處理後之電遷移失效時間與微

結構研究

研究生:譚志祥 指導教授:陳智 博士

國立交通大學

工學院半導體材料與製程設備學程

摘要高接腳密度、縮減封裝體積等優勢,讓覆晶銲錫在電子產品走向

輕、薄、短、小的趨勢中,成為高階元件的主流封裝型式。伴隨積體

電路高電流、小尺寸的設計變化,覆晶銲錫接點內的電遷移現象成為

元件可靠度的影響關鍵。在覆晶銲錫電遷移測試中,發現孔洞通常生

成於導線與銲錫凸塊界面處。研究發現其係在電子流由導線進入銲錫

時,因電子流流通面積改變,造成電流集中效應的影響。因此研究如

何讓銲錫球可以減低電流集中,進而抵抗電遷移效應是非常重要的課

題。

銲錫球中之 Under Bump Metallization(UBM)層通常是 Ni 或是

Cu,並會和 Sn 產生介金屬化合物(Intermetallic compound,簡稱 IMC),

這一層介金屬化合物,不但是銲接上去作為接合用的介面,更由於它

是高電阻的物質,我們可以藉由此性質降低電流集中效應,減少電遷

移之影響,增加銲錫球的使用壽命。

錫熔點絕對溫度的百分之九十)及不同的時效時間,是否對 IMC 層產

生變化,以此來觀察熱時效時間與電阻上升(孔洞生成)時間之關係,

並探討其原因。

Electromigration Failure Time and Micro-structure Study in Flip-Chip

SnPb Solder Joints by Different Pre-aging Times

Student: Chih-hsian Tan Advisor: Dr. Chih Chen

Degree Program of Semiconductor Material and Processing Equipment

College of Engineering

National Chiao Tung University

Abstract

Flip-chip technology has become a mainstream trend in advanced electronic packaging because of its capability of higher I/O density and smaller package size. With higher current and smaller size trends, electromigration in flip-chip solder has become an critical of reliability concern.

The effect of pre-aging on electromigration is investigated in this study using flip-chip SnPb solder joints. The solder joints were pre-aged at 170°C for 25 h, 50 h, and 100 h, and then they were subjected to electromigration tests of 1.0 A at 150°C. It was found that the average failure time increased when the joints were pre-aged for no pre-aged, 25 h, 50 h and 100 h. It is proposed that the major contributor to the prolonged failure time may be the densification of the nickel and copper under-bump metallization (UBM) and the solder due to the aging treatment. The pre-aging treatment at 170°C may stabilize the microstructure of the solder. The vacancies in the solder might be

annihilated during the heat treatment, causing a slower diffusion rate. In addition, the IMC structure became thicker after the pre-aging process. Thus, the thicker IMC structure may lead to smaller current crowding effect and slower consumption rates of the nickel and copper layers, resulting in the enhancement of electromigration

誌謝

在工作十五年後又重回學校,於工作與家庭的雙重壓力下,要求自

己來晚上上課,進行實驗,撰寫論文。我想說的是我做到了。而且重

回學校上課,也讓自己有機會再拿起書本,把許多基礎理論和工作經

驗相結合,這著實的讓我體會到”溫故知新”的真正意涵。

再者,敬邀陳智老師為論文指導教授,而陳智老師給予的題目,也

恰是自己在半導體領域工作比較沒有涉獵的後段封裝製程。也因為這

樣的論文題目,讓自己了解到半導體後段封裝製程之新技術演進與製

程技術瓶頸。真的讓自己在半導體領域有更通盤的認識。

在此,需先感謝陳智老師,謝謝你對我的包容與支持,並於Proposal、

論文口試階段時的引導與建議;也感謝張立老師、廖建能老師及吳樸

偉老師等口試委員,於Proposal計劃書與畢業論文的指導。另外也要感

謝CC Lab成員的協助。阿丸、翔耀、宗寬,謝謝你們在實驗上的技巧

傳授與分析儀器的協助。

最後,也要感謝我的父母與妻子。由於您們的全力支持與照顧家

庭,讓我沒有後顧之憂的上課、做實驗與寫論文,進而完成碩士學位。

還有我的七歲女兒,不時的給爸爸加油打氣。

目錄

摘要

... iAbstract

... iii誌謝

... iv目錄

... v表目錄 ...

vii圖目錄

... viii第一章、緒論

... 11-1 覆晶接合技術(Flip Chip) ... 1

1-2 凱文結構 (Kelvin Structure ) ... 2

1-3 文獻回顧 ... 3

1-3-1 電遷移... 3

1-3-2 覆晶銲錫接點的電遷移現象... 6

1-3-3 覆晶銲錫接點的電流聚集效應... 8

1-3-4 焦耳熱效應... 8

1-3-5 時效熱處理... 9

1-4 動機 ... 10

第二章、實驗方法、步驟與結果

... 202-1 試片結構 ... 20

2-2 實驗方法 ... 21

2-2-1 實驗電路設計及凸塊電性觀測... 22

2-2-2 銲錫凸塊破壞模式的觀測... 23

2-3 實驗結果 ... 23

第三章、結果與討論

... 373-1 熱時效後之試片觀察 ... 37

3-2 加熱通電阻值增加二倍之試片觀察 ... 38

3-3 熱時效與抵抗電遷移之討論 ... 38

第四章、結論

... 47表目錄

表 3-1 經不同熱時效處理後之 IMC 厚度 ... 40 表 3-2 不同熱時效條件之 EPMA 元素組成分析(a) No pre-aging,約 4um 之純 Ni

層(b) Pre-aging 20hrs,約 3um 之純 Ni 層... 44 表 3-3 不同熱時效條件之 EPMA 元素組成分析(a) Pre-aging 50hrs,約 3um 之純

圖目錄 圖 1-1 貝爾實驗室製造的第一個鍺電晶體[1] ... 12 圖 1-2 德州儀器 Jack Kilby 製造的首個積體電路晶棒[1] ... 12 圖 1-3 INTEL CPU 電晶體成長數量與摩爾定律趨勢圖 [2] ... 13 圖 1-4 打線接合(Wire bonding )圖示[3] ... 13 圖 1-5 覆晶接合示意圖[3] ... 14 圖 1-6 晶圓銲錫凸塊製程示意圖 [4] ... 14 圖 1-7 覆晶封裝與 FR4 基版(左圖)及 IBM C4 結構剖面示意圖(右圖) [5] ... 15 圖 1-8 Daisy chain 結構示意圖 ... 15

圖 1-9 Kelvin Resistor Structure (a) with two diffusion arms and two metal arms (b) with four diffusion arms and four metal arms [6] ... 15 圖 1-10 Blech 結構研究鋁導線的電遷移現象[9] ... 16 圖 1-11 不同長度的鋁導線通電後電遷移現象[9] ... 16 圖 1-12 鋁離子在晶格位能井承受電子(Fel)和電子風力(Fwd)示意圖;符號 V 表鋁 離子離開後的空位 [12] ... 16 圖 1-13 SnAg3.5 銲錫凸塊則在 120 ℃、3.58x104 A/cm2 電遷移失效 SEM 圖[19] .... 17

圖 1-14 IMC 生成圖 (a)共晶錫鉛 (b)SnAg3.8Cu0.7 UBM Ni,加熱 120°C,電流密 度 3.8x104 A/cm2 [19] ... 17 圖 1-15 (a) 銲錫凸塊內電流分佈二維模擬 (b) 銲錫凸塊剖面(x-y 面)電流密度 分佈(z 軸) 模擬示意圖[20] ... 18

圖 1-16 (a)-(d)覆晶銲錫共晶錫鉛 UBM Cu/Ni(V)/Al 電子顯微鏡電遷移破壞剖 面圖,(e) 孔洞生成與成長示意圖。條件︰加熱 125°C,電流密度 2.25x104 A/cm2 ,通電時間(a) 37 h, (b) 38 h, (c) 40 h, and (d) 43 h [20] ... 18 圖 1-17 焦耳熱效應 (a)未通電前溫度分佈(b)通電 0.59A 溫度分佈 (c) (b)圖中 所示白線溫度曲線 (d)其溫度模擬分佈[21] ... 19 圖 2-1 試片銲錫凸塊結構示意圖 ... 25 圖 2-2 試片廻路設計圖 ... 26 圖 2-3 凱文結構俯視示意圖 ... 26 圖 2-4 凱文結構剖面示意圖 ... 26 圖 2-5 實驗電路示意圖 ... 27

圖 2-6 試片研磨方冋示意圖 ... 27 圖 2-7 試片研磨後之 b3 銲錫凸塊 SEM 剖面圖 ... 28 圖 2-8 不同熱時效處理後之試片,於加熱通電後,錫鉛銲錫電阻變化率為初始電 阻二倍(Rratio= R/R0=2)對通電時間所作關係圖 ... 29 圖 2-9 不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之個別試片加熱通電時 間與不同熱時效處理時間關係圖... 30 圖 2-10 不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之平均加熱通電時間與 不同熱時效處理時間關係圖... 30 圖 2-11 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡

(SEM)×600 倍整個銲錫球影像圖(a) No pre-aging (b) Pre-aging 20hrs (c)

Pre-aging 50hrs (d) Pre-aging 100hrs... 31 圖 2-12 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡

(SEM)×1500 倍銲錫球內影像圖(a) No pre-aging (b) Pre-aging 20hrs (c)

Pre-aging 50hrs (d) Pre-aging 100hrs... 32 圖 2-13 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡

(SEM)×3000 倍 IMC 層影像圖(a) No pre-aging (b) Pre-aging 20hrs (c)

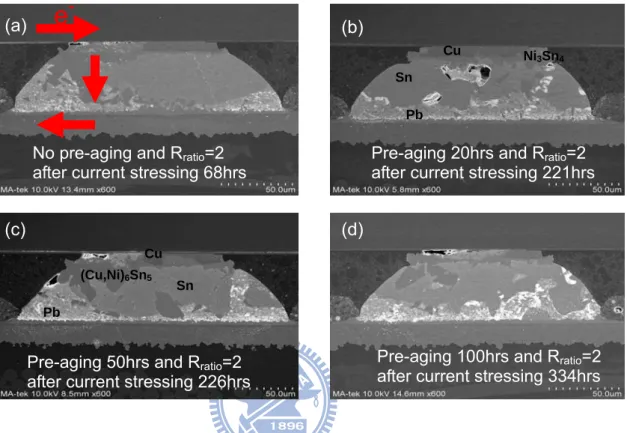

Pre-aging 50hrs (d) Pre-aging 100hrs... 33 圖 2-14 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡

(SEM)×600 倍整個銲錫球影像圖(a) No pre-aging and Rratio=2 after current

stressing 68hrs (b) Pre-aging 20hrs and Rratio=2 after current stressing

221hrs (c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs (d)

Pre-aging 100hrs and Rratio=2 after current stressing 334hrs ... 34

圖 2-15 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡 (SEM)×1500 倍銲錫球內影像圖(a) No pre-aging and Rratio=2 after current

stressing 68hrs (b) Pre-aging 20hrs and Rratio=2 after current stressing

221hrs (c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs (d)

Pre-aging 100hrs and Rratio=2 after current stressing 334hrs ... 35

圖 2-16 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡 (SEM)×3000 倍 IMC 層影像圖(a) No pre-aging and Rratio=2 after current

221hrs (c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs (d)

Pre-aging 100hrs and Rratio=2 after current stressing 334hrs ... 36

圖 3-1 為主要的電阻變化為初始電阻二倍之原因為電遷移破壞發生影像圖... 40 圖 3-2 熱時效處理時間愈久的試片,其抵抗電遷移破壞時間就愈長之關係圖... 40 圖 3-3 經 170℃,三個 pre-aging 時間處理後,IMC 厚度比較影像圖(a) No

pre-aging,IMC 厚度=0.8um (b) Pre-aging 20hrs,IMC 厚度=1.3um (c)Pre-aging 50hrs,IMC 厚度=2.4um (d) Pre-aging 100hrs,IMC 厚度=2.8um... . 41 圖 3-4 經 170℃,三個 pre-aging 時間處理後,錫鉛銲錫球之鉛相晶粒大小比較

影像圖(a) No pre-aging,鉛相晶粒大小~4.3um (b) Pre-aging 20hrs,鉛相晶 粒大小~6um (c) Pre-aging 50hrs,鉛相晶粒大小~7.5um (d) Pre-aging 100hrs, 鉛相晶粒大小~10um... .42 圖 3-5 經 170℃,二個 pre-aging 時間處理後,UBM 層之 EPMA 分析圖(a) No

pre-aging,約 4um 之純 Ni 層(b) Pre-aging 20hrs,約 3um 之純 Ni 層... 43 圖 3-6 經 170℃,二個 pre-aging 時間處理後,UBM 層之 EPMA 分析圖(a) Pre-aging

50hrs,約 3um 之純 Ni 層(b) Pre-aging 100hrs,約 2um 之純 Ni 層... 44 圖 3-7 電阻變化為初始電阻二倍之電遷移破壞發生時銲錫凸塊剖面的 SEM 影像圖

(a) No pre-aging and Rratio=2 after current stressing 68hrs (b) Pre-aging

20hrs and Rratio=2 after current stressing 221hrs (c) Pre-aging 50hrs and

Rratio=2 after current stressing 226hrs (d) Pre-aging 100hrs and Rratio=2 after

第一章 緒論

1-1 覆晶接合技術(Flip Chip)

1947年末,由AT&T 貝爾實驗室的科學家John Bardeen 和Walter Brattain 所展 示的第一個鍺電晶體(圖1-1),開啟了半導體的時代。積體電路的時代,在1958 年由德州儀器Jack Kilby 製造的首個積體電路晶棒(圖1-2)所開啟。此後伴隨著 電子產品朝向輕、薄、短、小發展的趨勢,積體電路的複雜度依摩爾定律(Moore’s Law)的驚人速度演進。1965年英特爾(Intel)創始人之一戈登摩爾,由其半導體 成長趨勢的觀察中,提出積體電路的複雜度每年會增加一倍,其後雖於1975年提 出每二年增加一倍的修正,仍可見積體電路驚人的演進趨勢。INTEL CPU內的電 晶體成長數量與摩爾定律的趨勢圖(圖1-3)。 積體電路技術不斷微縮朝高頻、高腳位數發展,傳統封裝技術,如打線接合 (Wire Bonding)封裝已無法滿足尺寸、電性上的要求。打線接合(Wire Bonding) (圖 1-4),若以50-um線寬及50-um的間距推算,僅有400 腳位/cm2;然而同樣條件下, 覆晶接合方式,則有高達25倍,10,000 腳位/cm2的高密度腳位優勢。覆晶接合(Flip Chip)圖1-5是採用銲錫凸塊(Solder Bump)作為晶片與基板連接的接合技術,將 晶面朝下藉由銲錫凸塊與基板接合,達到晶片與基版接合的方式。其除了具有提 高晶片腳位的密度之外,更可以降低雜訊的干擾、強化電性的效能、提高散熱能 力、及縮減封裝體積等優點。 圖1-6為覆晶封裝的晶圓凸塊(Wafer Bumping)製程流程。由錫鉛構成的凸塊 (Bump)或錫球排列於晶圓表面後,再植入晶片的焊墊(Bonding Pad)上方(圖1-5)。 覆晶封裝係在1960年代早期由IBM的C4製程概念開啟發展而來。所謂的C4製 程技術(controlled-collapse chip connection) [5],係將銲錫凸塊銲在晶片I/O金屬墊

上,翻覆晶片並對準於陶瓷基材上。藉由迴焊(Reflow)方式以熔融銲錫凸塊,由其 表面張力,使得已熔融銲錫凸塊在晶片與陶瓷基材產生自我對準的反應,並在二 者之間同時生成銲錫接合。該技術更因日本IBM率先採用塑膠基板取代以往的陶瓷 基板,此一材料上的重大突破,使得覆晶封裝技術往前邁向一大步。圖1-7為覆晶 封裝與FR4基版及IBM C4結構剖面示意圖。

1-2 凱文結構(Kelvin Structure )

利用雛菊花環結構(Daisy chain structure, 圖1-8)作為覆晶銲錫接點電遷移研 究中的電性觀測,其銲錫接點的破壞係以電路開路時作為定義,亦即其承受電遷 移破壞的能力。其試片設計與製作過程較為簡易,然而確會因銲錫與電路間阻抗 的特性而有所限制。銲錫接點本身的電阻(約為1 ~10 mΩ)僅佔總迴路(約為1 ~10Ω) 的極小部份,因此無法利用此一結構對於銲錫接點的變化做較為敏感、精確的觀 測;另外電路開路的狀況亦可能來自於鋁導線的破壞,如此即可能造成對於覆晶 銲錫接點電遷移破壞分析上的錯誤。 凱文結構(Kelvin structure)很早即被運用在積體電路中的電性量測方面,如 圖1-9,該法為四點探計方式量測,針對欲量測的範圍做電性的觀測時,可避除接 點電阻對電性量測的影響,其可用於較低範圍電阻 (10uΩ~1Ω) 的精確量測。因 而利用凱文結構的製備,得以精確量測單一銲錫凸塊細微電性變化。 上述對於覆晶銲錫接點電遷移研究中的電性觀測,大多都是直接定義電路開 路時為銲錫接點破壞的時間,亦即銲錫接點承受電遷移破壞的能力。 二者相較之下,以凱文結構對電性的觀測,不因銲錫接點本身的電阻僅佔總 迴路的極為小部份,而無法對銲錫接點變化做精確的觀測;同時,其可以直接觀

測覆晶銲錫接點電遷移破壞情形,而不因晶片內製作的鋁導線差異受影響。 凱文結構,能針對銲錫接點本身的變化作精確敏感的量測,在本文中,將針 對共晶錫鉛銲錫搭配 5-um銅金屬與 3-um鎳金屬墊層UBM (under-bump-metallization)的覆晶銲錫,利用凱文結構方式,用以研究其在高溫通 電下的不同條件處理後之電遷移破壞模式,即以銲錫接點本身的電阻變化作為銲 錫接點本身不同階段時期的破壞模式定義。

1-3 文獻回顧

覆晶封裝由其高密度I/O腳位的優勢,成為現今半導體產業進階製程中被廣泛 使用的封裝技術。然而其仍因電子產品的生產成本及元件操作速度的考量,邁向 微縮化的發展,伴隨而來的問題,使得覆晶銲錫凸塊面臨尺寸持續微縮及負載電 流密度提升的挑戰。 在高電流密度下,電子流由陰極流向陽極之際,可能同時也撞擊著原子,使 得原子同電子流方向移動。當原子持續由陰極流出,空孔(Void)將逐步地形成,最 終造成電路失效。陽極則因原子的擠壓,生成 hillocks 或 whisker現象,而導致電 路短路的情形。 1988年,Brandenburg 和 Yeh 的報告中,觀察到共晶錫鉛的覆晶封裝,在 150 ℃、8x103 A/cm2 的電流密度下,經過數百小時的失效情形中發現到,陰極有空孔 (Void)的形成,在凸塊陽極則發現了鉛的堆聚。[7]1-3-1 電遷移

金屬在承載一高電流密度下,所造成的質量傳送的現象稱為電遷移[8]。1861年Gerardin 由熔融錫鉛與汞鈉合金的研究中發現此一電遷移的現象。Skaupy 於 1914年提出電子風(electron wind)的觀念,來量化電遷移所造成的質量傳送。 具代表性研究電遷移現象的即為Blech結構,圖1-10為利用Blech結構研究鋁導 線的電遷移現象,陰極方向產生孔洞,而陽極方向發生凸起。[9] 圖1-11為Blech 及 Herring利用不同長度的鋁導線通電後受到電遷移破壞的情況,發現愈長的鋁導 線,在陰極方向,受到電遷移現象影嚮的鋁消耗程度愈明顯。在臨界長度下的鋁 導線,沒有明顯的鋁消耗現象,鋁導線消耗現象被解釋為背向應力的作用。對鋁 導線而言,不發生電遷移的臨界長度為10~20 -um。[10][11] 圖1-12為J. T. Yue 於1996提出鋁的電遷移模型[12],可以了解到原子在電流作 用下,會受到二種力量的影響。 電遷移模型中,高溫下部份之鋁離子會有機率躍遷至位能井之頂端,此活化 的鋁離子,基本上不受限於晶格,處於平衡狀態,即其不會離開也不會掉回位能 井內。當施加電埸時,其將會承受二個外加作用力,一者為電力 Fel,此一作用力 是因鋁離子受外加電埸作用的庫倫力,稱為靜電力;其二為電子風力(electron wind force)Fwd, 此作用力來自於鋁離子和高電流密度下電子碰撞造成動量轉移所致。 Huntington 及 Grone將電遷移力以下式表示︰[13]

(

Z Z)

eE eE Z Fem el wd * * * = + = ………...…………..(2-1) 其中 Z* 表示有效電荷(effective charge),其指當受到電遷移效應時,能夠遷移的 程度 e 表示電子電荷 E 表示電場(E=ρj,ρ為電阻率,j為電流密度)Z*el表示受擴散影響的離子常數 Z*wd表示受電子風力影響的有效價電數 電場所造成原子流動的驅動力可以分為兩部份,電場直接對擴散原子作用 力,是為靜電力;而電子與擴散原子之間的動量轉換,又可稱為電子風力。 其中靜電力以(2-2)式表示 eE Z Fel el * = … ………...………...…………. (2-2) 而電子風力可改寫成(2-3)式 eE Z Fwd wd * = ……….…...…………...…………. (2-3) 由於Fwd與電子流同一方向,而Fel和電子流呈反方向,且Fwd遠大於Fel,是以鋁 離子受電子風推擠而沿電子流方向移動,而空位(vacancy)則由電子流反方向移 動。空位和遷移的鋁離子在電遷移過程中是同時產生的。電遷移因空位的產生, 而有另一個快速移動的路徑-離子和空位交互躍遷(ion-vacancy jump process)。多 晶狀金屬薄膜中,在晶界(grain boundary)以及金屬薄膜與介電層間的界面中,提供 大量的空位所致。因此得以解釋多晶狀金屬薄膜的電遷移活化能(0.5~0.6 eV,鋁) 遠低於金屬塊體(1.48 eV,鋁)。 上述電遷移的驅動力皆存在固體原子的擴散行為,而固體裡原子的擴散通量 可以寫成如下式:[14]

∑

+ ∂ ∂ − = i i iF CM X C D J ………...…………. (2-4) 其中 D 表示擴散係數 C 表示原子濃度 M 表示原子遷移率F 表示驅動力 首項為化學式能梯度,第二項為外在力場梯度的總和。對於純金屬而言,原 子間沒有化學式能梯度的存在,所以首項為零。而 wd i i F F F = +

∑

el ,而Fwd遠大於 Fel,(2-4)式可改寫為 eE Z CMF F CM J el i wd i i * = = =∑

………...……. (2-5) 引入Nernst-Einstein 方程式,電子遷移率改寫成: kT D M = ………...…..………...…… (2-6) 將(2-6)式代入(2-5)式,可得到電遷移的通量方程式︰ eE Z kT D C F kT D C F kT D C CMF J = wd = wd = wd = el* ……….... (2-7) 其中 C 表示原子濃度 D 表示擴散係數 K 表示波茲曼常數 T 表示絕對溫度 Z*wd表示受電子風力影響的有效價電數 e 表示電子電荷 E 表示電場(E=ρj,ρ為電阻率,j為電流密度)1-3-2 覆晶銲錫接點的電遷移現象

施加一0.2A 的電流負載於一直徑50 mm的銲錫凸塊,其約受到約104 A/cm2的 電流密度。相較於晶片內的金屬銅、鋁內連導線,其電流密度約低了兩個維度等級,但確發現電遷移的現象以晶格擴散的方式發生在覆晶銲錫接點。[15][ Ref.15][ Ref.16]

一般以銲錫凸塊熔點較低或是擴散速度較快作為解釋。然而我們若以Critical Product [18]來探討其主要的原因。由Critical Product 此方程式得以一已知臨界長 度,求其在電遷移行為發生時,所需的電流密度值。發現若以相同臨界長度推算, 共晶錫鉛銲錫發生電遷移現象所需的電流密度與鋁、銅金屬內連導線相較,約少 一百倍。代表共晶錫鉛銲錫電遷移現象的發生,不需如鋁銅金屬內連導線般高的 電流密度作用。此為在104 A/cm2 的電流密度通電下,發現共晶錫鉛銲錫有電遷移 現象的主因,其公式如下: ρ ε e Z Y x jΔ = Δ* Ω ……… ………...………...….. (2-8) 其中 Y 表示為楊氏係數 Δx 表示為會發生電遷移的臨界長度 Δε表示0.2%的彈性應變 Ω 表示原子體積 Z* 有效電荷(effective charge),其指當受到電遷移效應時,能夠遷移的程度 e 表示電子電荷 ρ 表示電阻率 相較於晶片內的金屬銅、鋁內連線及共晶錫鉛銲錫特性 電阻率︰共晶錫鉛銲錫約比內連線金屬銅、鋁大十倍。

楊氏係數︰銅(69 Gpa)、鋁(110 Gpa)約為共晶錫鉛銲錫 (30 Gpa)的2 ~4倍。 有效電荷而言,共晶錫鉛銲錫約比銅、鋁大十倍。

圖1-13,係銲錫凸塊與SnAg3.5 UBM為厚膜無電鍍鎳與電鍍厚膜銅作為基板側

的墊層的電遷移破壞研究,在120℃下,進行1.5 A通電,電流密度為 3.58x104

A/cm2,結果發現到厚膜鎳UBM 快速消耗溶解及介金屬化合物(IMC)快速成長,孔 洞產生等現象。[19]

圖1-14,係共晶錫鉛與SnAg3.8Cu0.7 UBM為厚膜無電鍍鎳與電鍍厚膜銅作為基

板側的墊層的電遷移破壞研究,在120℃下,進行1.5 A通電,電流密度為 3.8x104

A/cm2,結果發現到厚膜鎳UBM 快速消耗溶解及介金屬化合物(IMC)快速成長,孔 洞產生等現象,距離鎳UBM 20-um 處更可發現介金屬化物的生成。[19]

1-3-3 覆晶銲錫接點的電流聚集效應

圖1-15(a)為覆晶封裝的銲錫凸塊內的電流分佈與凸塊內電流分佈二維模擬, 圖1-15(b)為電流密度分佈模擬圖。 [20]從中可明顯發現銲錫凸塊電流分佈並不平 均,凸塊中心的電流密度約為晶片內連導線與銲錫凸塊界面的十分之一倍。由於 覆晶封裝中的獨特銲錫接點外形,晶片內連導線與銲錫凸塊截面大小相較有百倍 大小之差,因此在電子流由晶片內連導線進入銲錫凸塊時,二者界面處將有極大 的電流密度改變﹐如此大的電流密度改變,形成了電流聚集效應。 圖1-16為覆晶銲錫共晶錫鉛,UBM為 Cu/Ni(V)/Al,電遷移破壞孔洞生成與成 長的連續過程,可以發現電遷移破壞發生在界面處[20]。孔洞生成的主因在於二者 界面處有著較大的電流密度,造成電流聚集效應的影響。1-3-4 焦耳熱效應

銲錫凸塊在通電作用下產生焦耳熱,將導致凸塊的溫度變化。圖1-17為利用紅外線顯像技術,量測置於70℃熱板、通電中的覆晶銲錫結構,其因焦耳熱效應造 成的溫升分佈及其模擬情形,其中發現主要發熱源存在於鋁導線進入銲錫處。[21]。 金屬原子,在除了在絕對零度中,其原子會於晶格平衡位置上不斷地來回振動, 當溫度愈高時,其振幅愈大,因此當電子通過金屬導體時,其所面臨的阻抗也愈 大,其阻抗將直接反應於金屬的電阻特性,稱為 TCR 效應(Temperature Coefficient of Resistance Effect)。 因此銲錫凸塊在通電作用下,所產生的焦耳熱,除了造成溫度效應外,也會 因TCR 效應而造成電路阻值的改變。 ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − = 0 1 0 0 1 1 T T R R R TCR …….………...…. (2-9) 其中 T0 表示參考溫度 T1 表示為真實溫度 R0 表示在T0下的電阻 R1 表示在T1下的電阻 如此即可利用電路阻值的變化,來校正銲錫凸塊在通電作用下所受焦耳熱造 成的溫升變化。

1-3-5 熱時效處理

S. W. Liang等人[22],研究降低電遷移之方法-減緩電流集中效應,分別以(1) Keeping the solder away from high current density region, (2) Spreading the current uniformly by adding a thin resistive layer, (3) Deceasing the passivation opening, (4)Enlarging the cross-section of Al trace 四種方法,以 Crowding ratio 作為電流聚集 效應的觀察指標,指標係以最大電流除以UBM開口處的平均電流計算。研究數據 發現與實驗驗證,此四種方向,使錫鉛銲錫因電遷移而被破壞失效時間相對愈長。 另外C.C. Chang等人,以不同條件之時效熱處理作為研究對象[23],於不同的 UBM結構,在薄膜試片中熱時效會降低銲錫球在電遷移測試當中的life time,而 在厚膜試片當中,適度的熱時效則會增加銲錫球的life time。

1-4 動機

隨著電子元件越做越小,每個銲錫球所需承受的電流密度就越大,因此研究 如何讓銲錫球可以抵抗電遷移效應是非常重要的課題。Under Bump Metallization (UBM)層通常是Ni或是Cu,並會和Sn產生介金屬化合物(Intermetallic compound,簡 稱IMC),這一層介金屬化合物,不但是銲接上去作為接合用的介面,更由於它是 高電阻的物質,我們可以藉由此性質降低電流集中效應,減少電遷移之影響,增 加銲錫球的使用壽命。 利用熱時效(Pre-aging)的方式,使用溫度170℃(約為銲錫熔點絕對溫度的百分 之九十)及不同的時效時間,是否對IMC層產生變化,以此來觀察熱時效時間與電 阻上升(孔洞生成)時間之關係。並探討其原因。相較於以往的雛菊花環結構(Daisy chain structure),對於覆晶銲錫接點電遷 移研究,凱文結構(Kelvin structure),有著對於覆晶銲錫電性變化更為敏感、精 確的量測。因而本研究將使用凱文結構的製備,作為觀察覆晶銲錫接點於不同階 段電遷移破壞情形時的研究方式。

備,用以研究高50-um、UBM: 5-um Cu /3-um Ni的覆晶共晶錫鉛銲錫,其於不同熱 時效條件處理後的抵抗電遷移破壞情形。

圖1-1 貝爾實驗室製造的第一個鍺電晶體[1]

圖1-3 INTEL CPU電晶體成長數量與摩爾定律趨勢圖 [2]

圖1-5 覆晶接合示意圖[3]

圖1-7 覆晶封裝與FR4基版(左圖)及IBM C4結構剖面示意圖(右圖) [5]

圖1-8 Daisy chain 結構示意圖

圖1-9 Kelvin Resistor Structure (a) with two diffusion arms and two metal arms (b) with four diffusion arms and four metal arms [6]

圖1-10 Blech結構研究鋁導線的電遷移現象[9]

圖1-11 不同長度的鋁導線通電後電遷移現象[9]

圖1-12 鋁離子在晶格位能井承受電子(Fel)和電子風力(Fwd)示意圖;符號V表鋁 離子離開後的空位 [12]

圖1-13 SnAg3.5 銲錫凸塊則在120 ℃、3.58x104

A/cm2電遷移失效SEM圖[19]

圖1-14 IMC生成圖 (a)共晶錫鉛 (b)SnAg3.8Cu0.7 UBM Ni,加熱120°C,電流密 度3.8x104

圖1-15 (a) 銲錫凸塊內電流分佈二維模擬 (b) 銲錫凸塊剖面(x-y面)電流密度分 佈(z 軸) 模擬示意圖[20] 圖1-16 (a)-(d)覆晶銲錫共晶錫鉛UBM Cu/Ni(V)/Al 電子顯微鏡電遷移破壞剖 面圖,(e) 孔洞生成與成長示意圖。條件︰加熱125°C,電流密度2.25x104 A/cm2 , 通電時間(a) 37 h, (b) 38 h, (c) 40 h, and (d) 43 h [20]

圖1-17 焦耳熱效應 (a)未通電前溫度分佈(b)通電0.59A 溫度分佈 (c) (b)圖中所 示白線溫度曲線 (d)其溫度模擬分佈[21]

第二章 實驗方法、步驟與結果

本實驗將利用能夠敏感、精確量測的凱文結構的覆晶共晶錫鉛銲錫試片製 備,用以其觀察抵抗電遷移破壞的情形。

實驗試片製備係為一覆晶共晶錫鉛銲錫,其銲錫凸塊高度為50-um、金屬墊層 (under-bump-metallization)為5-um Cu/3-um Ni。加以170 ℃之溫度下,進行四種時 間,(1) no pre-aging、(2) 20 hrs、(3) 50 hrs、(4) 100 hrs之時效熱處理。 實驗測試方法為在一定加熱溫度、通電電流的條件下,作為加速破壞實驗, 同時利用監測通電中的銲錫凸塊電阻值變化,作為研究該試片電遷移破壞情形不 同階段的指標。本實驗的加熱溫度條件為150℃,通電電流條件為1.0 A的一定電流。 實驗流程如下︰ 1. 電遷移破壞測試︰利用凱文結構於電遷移破壞測試期間,量測並紀錄銲錫隨 測試時間變化的電阻值,當電阻值變化達初始電阻二倍時,停止測試。 2. 試片觀察︰ (1)針對進行熱時效處理且尚未加熱通通電之試片,利用設備依一定方向將其所 需的觀察的剖面研磨、拋光後,利用光學顯微鏡及掃描式電子顯微鏡觀察、紀錄 試片的剖面狀態。 (2)將銲錫電阻值變化達初始電阻二倍時的試片,利用設備依一定方向將其所需 的觀察的剖面研磨、拋光後,利用光學顯微鏡及掃描式電子顯微鏡觀察,紀錄試 片的剖面狀態。 3. 觀察不同熱時效條件之試片與加熱通電之試片二者之剖面狀態分析,來探討 其關係。

2-1 試片結構

實驗的試片製備,係由米輯科技提供的共晶錫鉛覆晶封裝試片,其銲錫凸塊 結構如圖2-1 –晶片端的鋁導線為120-um寬、1.5-um厚、銲錫UBM (Under Bump Metallization)材料種類為Cu,厚度為 5-um/Ni,厚度為 3-um, UBM opening 為 120-um,銲錫凸塊為直徑120-um,高度 50-um的共晶錫鉛銲錫,凸塊間間距為 1-mm。 銲錫銲料係以共晶錫鉛銲錫,晶片端部份,利用電鍍將銲錫固定於UBM所在, 再於加熱爐中加熱到220℃約一分鐘;基板部份,則採用FR5基板,銅墊層直徑為 2805-um,上一層為5-um無電鍍鎳。 試片迴路設計依凱文結構方式佈局,如圖2-2(a)完整試片俯視圖,(b)凱文結構 佈局試片迴路設計圖。本研究中,將僅測試第六排(最下一排,如圖2-3 )的四顆銲 錫凸塊結構作為研究,剖面示意圖如圖2-4。

2-2 實驗方法

實驗測試方法為利用凱文結構設計,將試片置於一150℃的加熱板上,施加一 定通電電流1.0安培於電路,同時量測、紀錄銲錫凸塊及鋁導線的電阻值變化,當 電阻值變化達初始電阻二倍時,即停止加熱、通電等測試條件。其中電阻值變化 之通電時間,亦即定義為failure time。實驗電路示意圖如圖2-5。 之後再依一定方向(圖2-6)將所需觀察的試片剖面研磨、拋光後,利用光學顯微 鏡及掃描式電子顯微鏡作為試片的剖面狀態影像的觀察、紀錄,了解其不同熱時 效處理條件對抵抗電遷移破壞之影響。 實驗電路設計所使用的電源供應器與量測儀器分別為電流源Agilent E3642A 與搭配有二十個獨立頻道Agilent E34901A 模組的資料交換器(Data switch)AgilentE34970A。藉由上述二組儀器對序列阜與GPIB 控制介面通訊協定的支援,以美國 國家儀器公司開發的圖形化儀器控制軟體LabVIEW,作為實驗過程中的資料擷取 及儀器控制的工具。

2-2-1 實驗電路設計及凸塊電性觀測

圖2-3 為本文所指之凱文結構俯視圖,係僅圖2-2(b)中的最下方一排,利用此 結構觀測銲錫通電後受到電遷移影響時的即時電性變化。 結構中含有四顆銲錫凸塊,此四顆銲錫凸塊,如圖2-3 所示b1 、b2 、b3 及 b4,由一鋁導線連接四個墊層。其中鋁導線長3150-um、厚1.5-um、寬100-um,銲 錫凸塊間間距為1mm。此外,圖示之六條導線,係FR5基板與四顆銲錫凸塊連接的 銅導線,分別標示為n1 、n2 、n3 、n4 、n5 及n6 ,銅導線厚30-um、寬100-um, 其中銲錫凸塊b1 到b4 依序分別連接1、2、2及1 條的銅導線,導線分佈如圖2-3。 實驗電路設計,利用此六條銅導線不同的連接方式,可分別量測到b2 、b3 的 單顆銲錫凸塊電阻與晶片內的鋁導線電位差與電阻,如圖2-4 標註箭頭方向所示。 在本研究中,由n3 及n4 通入一1.0A 之定電流,電子流在b2 銲錫凸塊中從基板端 流向晶片端,在b3 銲錫凸塊中則呈相反方向從晶片端流向基板端。分別由n1 及 n2 量測b2 銲錫凸塊電子流向上的電位差(定義晶片端方向為向上),b3 銲錫凸塊 則由n5 及n6 量測其電子流向下的電位差,如此量測方式即可在電遷移發生的同 時量測到兩個電子流不同方向的銲錫凸塊電阻表現。同時以n1 及n6 來量測鋁導 線的電阻變化。 由於電流集中效應的影嚮,以往的研究中發現孔洞的生成大多顯示在電子流 流入銲錫凸塊的晶片端,所以本實驗電遷移現象著重在b3 銲錫凸塊電性的量測,當其電阻值變化達到設定為初始值的二倍時,即停止加熱、通電等條件,以此觀 察其電遷移破壞時間與不同熱時效條件之關係。 實驗時,將試片置於一150℃的加熱板上,將晶片面緊貼加熱板方式加熱,並 用耐熱膠帶固定,靜置試片直到試片溫度到達平衡才開始如上述方式通電量測。 電路迴路與量測的位置如圖2-5 所示,於圖2-4 中的n3 及n4 通入一定電流 1.0A,量測b3 銲錫凸塊的電阻值變化,當其變化達初始電阻二倍時後,停止通電 及加熱並取下試片。以UBM opening 直徑為 120-um,施以1.0A 之一定電流的數 值推算,其所對應電流密度為1.1x104 A/cm2。

2-2-2 銲錫凸塊破壞模式的觀測

將熱時效與實驗通電破壞後的試片依序沿圖2-6 所示方向,以不同號數的SiC 砂紙(120、600、1200、2500、4000等SiC 砂紙) 依序研磨試片,將試片研磨至銲 錫凸塊中心,同時顯現銲錫凸塊之半剖面及鋁導線,再以1-um、0.3-um、0.05-um 大 小顆粒的Al2O3作研磨拋光,之後再利用掃描式電子顯微鏡(SEM)觀察、紀錄試 片剖面狀態影像。試片研磨銲錫凸塊SEM剖面圖如圖2-7。其中,晶片端的鋁導線 為1.5-um厚、銲錫之上UBM (Under Bump Metallization)材料種類為Cu,厚度為 5-um/Ni,厚度為 3-um,銲錫凸塊為高度50-um的共晶錫鉛銲錫,銲錫之下UBM (Under Bump Metallization)材料種類為Ni,厚度為 3-um /Cu,厚度為 30-um。2-3 實驗結果

電阻變化率 Rratio定義為 R/R0 ,其中R為銲錫凸塊b3的即時量測電阻,R0為

指標定義可以修正各試片間因初始電阻值的差異,而造成結果判讀上困難之問題。 圖2-8 為不同熱時效處理後之試片,於加熱通電後,錫鉛銲錫電阻變化率為初 始電阻二倍(Rratio= R/R0=2)對時間所作關係圖; 圖2-9 為不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之個別試片加熱 通電時間與不同熱時效處理時間關係圖; 圖2-10 為不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之平均加熱通電 時間與不同熱時效處理時間關係圖; 圖2-11 ~圖2-13為不同熱時效處理後之試片,於加熱通電前的不同倍率之掃描 式電子顯微鏡(SEM)影像。 圖2-14 ~圖2-16為不同熱時效處理後之試片,於加熱通電後,錫鉛銲錫電阻變 化率為初始電阻二倍(Rratio= R/R0=2)時的掃描式電子顯微鏡(SEM)影像。

圖2-1 試片銲錫凸塊結構示意圖

Ni

5µm

Ni 3µm

Cu 5µm

Al trace 1.5µm

SnPb solder bump

Cu 30µm

Bump

Height

50 µm

120 µm

300 µm

IMC-Ni

3Sn

4e

-UBM

圖2-2 (a)完整試片俯視圖 (b)凱文結構佈局試片迴路設計圖

圖2-3 凱文結構俯視示意圖

圖2-5 實驗電路示意圖

圖2-7 試片研磨後之b3銲錫凸塊SEM剖面圖

Cross section view

n1 n2 n3 n4 n5 n6

b1 b2 b3 b4

t1 t2 t3

FR4

Silicon (Chip side)

Substrate

Al trace-1.5um UBM- Cu-5um/Ni-3umSnPb solder bump

height-50um

UBM- Ni-5um/Cu-30um圖2-8 不同熱時效處理後之試片,於加熱通電後,錫鉛銲錫電阻變化率為初始電 阻二倍(Rratio= R/R0=2)對通電時間所作關係圖

Failure time vs b3 Rratio

0 0.5 1 1.5 2 2.5 3 0 200 400 600 800 1000 Failure time (hrs) Rra tio =R /R0 #2-no pre-aging #3-no pre-aging #5-no pre-aging #6-pre-aging 20hrs #7-pre-aging 20hrs #8-pre-aging 20hrs #11-pre-aging 50hrs #12-pre-aging 50hrs #16-pre-aging 100hrs #17-pre-aging 100hrs #18-pre-aging 100hrs

圖2-9 不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之個別試片加熱通電

時間與不同熱時效處理時間關係圖;

圖2-10 不同試片電阻上升至初始電阻二倍 (Rratio= R/R0=2)之平均加熱通電時間

與不同熱時效處理時間關係圖

Failure time vs pre-aging time

0 100 200 300 400 500 600 700 800 0 10 20 30 40 50 60 70 80 90 100 110 120 Pre-aging time(hrs) F ai lur e t ime ( h rs )

Failure time vs pre-aging time

0 100 200 300 400 500 600 700 800 0 10 20 30 40 50 60 70 80 90 100 110 120 Pre-aging time (hrs) F a ilur e tim e ( hr s)

圖2-11 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡 (SEM)×600倍整個銲錫球影像圖。 (a) No pre-aging (b) Pre-aging 20hrs (c) Pre-aging 50hrs (d) Pre-aging 100hrs No pre-aging Pre-aging 20hrs Pre-aging 50hrs Pre-aging 100hrs (a) (b) (c) (d)

圖2-12 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡 (SEM)×1500倍銲錫球內影像圖。 (a) No pre-aging (b) Pre-aging 20hrs (c) Pre-aging 50hrs (d) Pre-aging 100hrs No pre-aging Pre-aging 20hrs Pre-aging 50hrs Pre-aging 100hrs (a) (b) (c) (d)

圖2-13 錫鉛銲錫不同熱時效處理後之試片,於加熱通電前的掃描式電子顯微鏡 (SEM)×3000倍IMC層影像圖。 (a) No pre-aging (b) Pre-aging 20hrs (c) Pre-aging 50hrs (d) Pre-aging 100hrs No pre-aging Pre-aging 20hrs Pre-aging 50hrs Pre-aging 100hrs 0.8 µm 2.8 µm 2.4 µm 1.3 µm (a) (b) (c) (d)

圖2-14 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡 (SEM)×600倍整個銲錫球影像圖。

(a) No pre-aging and Rratio=2 after current stressing 68hrs

(b) Pre-aging 20hrs and Rratio=2 after current stressing 221hrs

(c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs

(d) Pre-aging 100hrs and Rratio=2 after current stressing 334hrs

No pre-aging and Rratio=2

after current stressing 68hrs

Pre-aging 20hrs and Rratio=2

after current stressing 221hrs

Pre-aging 50hrs and Rratio=2

after current stressing 226hrs

Pre-aging 100hrs and Rratio=2

after current stressing 334hrs Sn Ni3Sn4 Pb Sn (Cu,Ni)6Sn5 Cu Cu Pb

e

- (a) (b) (c) (d)圖2-15 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡 (SEM)×1500倍銲錫球內影像圖。

(a) No pre-aging and Rratio=2 after current stressing 68hrs

(b) Pre-aging 20hrs and Rratio=2 after current stressing 221hrs

(c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs

(d) Pre-aging 100hrs and Rratio=2 after current stressing 334hrs

Pre-aging 20hrs and Rratio=2

after current stressing 221hrs

Pre-aging 50hrs and Rratio=2

after current stressing 224hrs

Pre-aging 100hrs and Rratio=2

after current stressing 334hrs No pre-aging and Rratio=2

after current stressing 68hrs

(a) (b)

圖2-16 錫鉛銲錫不同熱時效處理後之試片,於加熱通電後的掃描式電子顯微鏡 (SEM)×3000倍IMC層影像圖。

(a) No pre-aging and Rratio=2 after current stressing 68hrs

(b) Pre-aging 20hrs and Rratio=2 after current stressing 221hrs

(c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs

(d) Pre-aging 100hrs and Rratio=2 after current stressing 334hrs

Pre-aging 20hrs and Rratio=2

after current stressing 221hrs

Pre-aging 50hrs and Rratio=2

after current stressing 224hrs

Pre-aging 100hrs and Rratio=2

after current stressing 334hrs No pre-aging and Rratio=2

after current stressing 68hrs

(a) (b)

第三章、結果與討論 由實驗試片中的加熱通電後之銲錫凸塊b3剖面影像觀察,圖3-1為主要的電阻 變化為初始電阻二倍之原因為電遷移破壞發生。除Cu/Ni UBM消耗溶解、IMC成長、 錫鉛相重新分佈並發生相分離外,更可觀察到孔洞的生成、成長。 利用凱文結構的電性觀測方式,於加熱通電後,觀察電阻變化為初始電阻二 倍之抵抗電遷移破壞時間與熱時效預處理時間之關係。如圖3-2,我們發現,在經 過熱時效處理後之實驗試片,其抵抗電遷移破壞時間,都比未做熱時效處理之實 驗試片來的長。而且熱時效處理時間愈久的試片,其抵抗電遷移破壞時間就愈長。

3-1 熱時效後之試片觀察

對於熱時效處理時間愈久的試片,其抵抗電遷移破壞時間就愈長之現象。由 銲錫凸塊剖面的SEM影像圖觀察發現: (1) 圖3-3,經170℃,三個pre-aging時間處理後,IMC厚度比較為-100hrs (2.8um)> 50hrs (2.4um)> 20hrs (1.3um) > no pre-aging(0.8um)…如表3-1

(2) 圖3-4,經170℃,三個pre-aging時間處理後,錫鉛銲錫球之鉛相晶粒大小比較 為:

100hrs(~10um) > 50hrs(~7.5um) > 20hrs(~6um) > no pre-aging(~4.3um)

(3) 表3-2與表3-3為不同熱時效條件之EPMA元素組成分析。圖3-5與圖3-6為各種熱 時效條件之EPMA元素組成分析取樣點示意,其取樣點為經由Cu-5um/Ni-3um UBM到錫鉛銲錫球,每間隔1um取一點EPMA元素組成分析,每一試片共取十六 點。可以觀察到,經170℃及三個不同pre-aging時間處理後,錫鉛銲錫球之UBM層,

由Cu-5um/Ni-3um UBM到錫鉛銲錫球之EPMA元素組成分析發現,原UBM之純Ni 層,也因熱時效處理後變薄。其UBM之純Ni層厚度比較為:

No pre-aging condition (約EPMA的4點的純Ni層,亦即4um的純Ni層) > All pre-aging condition(約EPMA的2~3點的純Ni層,亦即2~3um的純Ni層)

3-2 加熱通電阻值增加二倍之試片觀察

於150℃,1.0安培的通電條件下,電阻變化為初始電阻二倍之原因為電遷移破 壞發生。由銲錫凸塊剖面的SEM影像圖觀察發現: (1) 圖3-7,於150℃,1.0安培的通電條件下,錫鉛銲錫球之電阻上升乃因UMB與IMC 被消耗後之孔洞生成。 (2) 圖3-7,於150℃,1.0安培的通電條件下,由於Electromigration之效應造成原錫 鉛銲錫球中之錫與鉛產生相分離。 (3) 圖3-7,於150℃,1.0安培的通電條件下,由於熱時效處理造成IMC層變厚的現 象,於加熱通電後之電遷移破壞,其UBM與IMC層被破壞橫向距離比較為: 100hrs > 50hrs > 20hrs > no pre-aging3-3 熱時效與抵抗電遷移之討論

由經熱時效處理後之銲錫凸塊剖面觀察,愈長時間之熱時效處理,其IMC厚度 是愈厚。也因此結果而造成抵抗電遷移能力增加。而IMC厚度經熱時效處理後而變 厚的原因為Ni與銲錫球的Sn反應,而型成更厚的Ni3Sn4 IMC層。此較厚的IMC層, 讓銲錫球的位置離開高電流密度區,亦即離開熱點遠一點。並且,因其高阻值之 特性,而減緩電流集中效應,增加抵抗電遷移能力。另由Cu-5um/Ni-3um UBM到錫鉛銲錫球之EPMA元素組成分析發現,原UBM 之純Ni層,也因熱時效處理後變薄。這表示原UBM中的Ni消耗並和錫鉛銲錫球中 的Sn反應生成更厚的Ni3Sn4 IMC層。此也證明經熱時效處理後,IMC厚度變厚的 原因是,原UBM層中的Ni經熱時效處理後,部分Ni消耗與錫鉛銲錫球中的Sn反應 生成更厚的Ni3Sn4 IMC層。而此此較厚的IMC層,因其高電阻率之特性,而減緩電 流集中效應,增加抵抗電遷移能力。 再由不同熱時效之試片,於加熱通電後,電阻變化為初始電阻二倍之原因為 電遷移破壞發生。其SEM剖面圖之破壞模式觀察,經過較長時間熱時效處理之試 片與未做熱時效之試片比較,UBM與IMC層被破壞的橫向距離,有做過熱時效處 理之試片,其被破壞的距離是較寬的。這可解釋為,因此較厚的IMC層,因其高電 阻率之特性,讓電流於更廣的IMC層分散,而減緩電流集中效應,以增加抵抗電遷 移能力。

170℃ Pre-aging time Chip side IMC thickness 0hr 0.8μm 20hr 1.3μm 50hr 2.4μm 100hr 2.8μm 表 3-1 經不同熱時效處理後之 IMC 厚度

圖3-1 為主要的電阻變化為初始電阻二倍之原因為電遷移破壞發生影像圖。

圖3-2 熱時效處理時間愈久的試片,其抵抗電遷移破壞時間就愈長之關係圖。

Pre-aging 20hrs and R

ratio=2

after current stressing 221hrs

Sn

Ni

3Sn

4Pb

Cu

Failure time vs pre-aging time

0 100 200 300 400 500 600 700 800 0 10 20 30 40 50 60 70 80 90 100 110 120 Pre-aging time (hrs) F a ilur e tim e ( hr s)

圖3-3 經170℃,三個pre-aging時間處理後,IMC厚度比較 (a) No pre-aging,IMC厚度=0.8um (b) Pre-aging 20hrs,IMC厚度=1.3um (c) Pre-aging 50hrs,IMC厚度=2.4um (d) Pre-aging 100hrs,IMC厚度=2.8um No pre-aging Pre-aging 20hrs Pre-aging 50hrs Pre-aging 100hrs 0.8 µm 2.8 µm 2.4 µm 1.3 µm (a) (b) (c) (d)

圖3-4 經170℃,三個pre-aging時間處理後,錫鉛銲錫球之鉛相晶粒大小比較 (a) No pre-aging,鉛相晶粒大小~4.3um (b) Pre-aging 20hrs,鉛相晶粒大小~6um (c) Pre-aging 50hrs,鉛相晶粒大小~7.5um (d) Pre-aging 100hrs,鉛相晶粒大小~10um No pre-aging Pre-aging 20hrs Pre-aging 50hrs Pre-aging 100hrs (a) (b) (c) (d)

EPMA result (Atomic ratio):

(a) no pre-aging

(b) pre-aging 20hrs

No. Sn Ni Pb Cu No. Sn Ni Pb Cu 1 0.7585 6.5548 0.6545 92.0322 1 0.2202 1.7767 0.4108 97.5923 2 0.0758 0.5686 0.1411 99.2144 2 0 0.4099 0.0554 99.5346 3 0.0256 0.3832 0.0291 99.5621 3 0.0328 0.6078 0.0315 99.3279 4 0.0425 0.4983 0.0498 99.4094 4 0.021 0.6614 0.0618 99.2558 5 0.0077 0.66 0.0159 99.3165 5 0.0286 0.8842 0.0143 99.0729 6 0.0372 0.723 0.0289 99.2108 6 0.0459 1.1975 0.0464 98.7102 7 0.0615 0.9159 0 99.0226 7 0.0917 2.0211 0.0122 97.875 8 0.0496 1.1073 0.0496 98.7935 8 0.0663 75.6127 0.0074 24.3136 9 0.0039 1.4825 0.0022 98.5114 9 0.0823 98.9147 0.0456 0.9575 10 0.0816 3.3047 0.0086 96.605 10 0.1278 99.4738 0.0104 0.388 11 0.06 84.6918 0 15.2482 11 9.2612 90.0376 0.065 0.6363 12 0.0616 98.892 0.0033 1.0432 12 61.7952 34.9681 0.6704 2.5663 13 0.0742 99.2188 0.0271 0.6799 13 94.7624 3.4224 0.3443 1.4708 14 0.1141 99.474 0.0119 0.3999 14 96.2058 2.3034 0.3534 1.1374 15 9.3701 90.1418 0.0684 0.4197 15 97.2153 1.4662 0.3209 0.9975 16 59.2018 28.8448 9.4027 2.5506 16 97.1349 1.2229 0.6608 0.9814 表 3-2 不同熱時效條件之 EPMA 元素組成分析

(a) No pre-aging,約 4um 之純 Ni 層 (b) Pre-aging 20hrs,約 3um 之純 Ni 層

SEM picture:

t 圖3-5 經170℃,二個pre-aging時間處理後,UBM層之EPMA分析圖 (a) No pre-aging,約4um之純Ni層 (b) Pre-aging 20hrs,約3um之純Ni層 (a) No pre-aging (b) Pre-aging 20hrsEPMA sampling point from Cu/Ni UBM to SnPb solder (every 1um to get 1pt and total 16pts)

1

1

16

EPMA sampling point from Cu/Ni UBM to SnPb solder (every 1um to get 1pt and total 16pts)

16 1

EPMA result (Atomic ratio):

#14(pre-aging 50hrs)

#19(pre-aging 100hrs)

No. Sn Ni Pb Cu No. Sn Ni Pb Cu 1 0.2652 2.2179 0.1298 97.3871 1 0.714 2.5619 0.3006 96.4234 2 0.0508 0.4235 0.0023 99.5234 2 0.0204 0.5003 0.0017 99.4776 3 0.0142 0.592 0 99.3938 3 0.0653 0.5174 0.0756 99.3417 4 0.097 0.6632 0.024 99.2158 4 0.0611 0.7536 0.0518 99.1335 5 0.0249 1.0012 0.0379 98.936 5 0.023 0.8411 0 99.136 6 0.0785 1.4203 0.0111 98.4901 6 0.0664 1.1373 0.0261 98.7701 7 0.0795 9.2615 0.0516 90.6074 7 0.089 2.1559 0.0304 97.7248 8 0.1535 98.031 0.0158 1.7996 8 0.0957 75.1822 0.0255 24.6966 9 0.1663 99.0704 0.0196 0.7437 9 0.1585 98.7533 0 1.0882 10 5.771 93.7855 0.0239 0.4195 10 0.2169 99.2153 0 0.5677 11 53.2059 44.1716 0.0841 2.5383 11 28.7685 70.0838 0.0331 1.1146 12 74.3104 21.7836 2.0923 1.8137 12 53.1006 44.2569 0.4847 2.1578 13 85.9416 11.4702 1.2488 1.3394 13 73.0692 22.6088 2.6253 1.6968 14 93.1687 1.5675 4.2978 0.9659 14 23.5147 5.339 69.2856 1.8608 15 64.0688 1.3698 33.3985 1.1629 15 48.9946 2.038 47.2975 1.6699 16 12.8611 1.6586 84.0479 1.4324 16 88.2185 1.1155 9.6635 1.0025 表 3-3 不同熱時效條件之 EPMA 元素組成分析(a) Pre-aging 50hrs,約 3um 之純 Ni 層(b) Pre-aging 100hrs,約 2um 之純 Ni 層

SEM picture:

圖3-6 經170℃,二個pre-aging時間處理後,IMC層之EPMA分析圖 (a) Pre-aging 50hrs,約3um之純Ni層

(b) Pre-aging 100hrs,約2um之純Ni層

(a) Pre-aging 50hrs

(b) Pre-aging 100hrs 1

16

EPMA sampling point from Cu/Ni UBM to SnPb solder (every 1um to get 1pt and total 16pts)

1

16

EPMA sampling point from Cu/Ni UBM to SnPb solder (every 1um to get 1pt and total 16pts)

圖 3-7 電阻變化為初始電阻二倍之電遷移破壞發生時銲錫凸塊剖面的 SEM 影像圖

(a) No pre-aging and Rratio=2 after current stressing 68hrs

(b) Pre-aging 20hrs and Rratio=2 after current stressing 221hrs

(c) Pre-aging 50hrs and Rratio=2 after current stressing 226hrs

(d) Pre-aging 100hrs and Rratio=2 after current stressing 334hrs

No pre-aging and Rratio=2

after current stressing 68hrs Pre-aging 20hrs and Rafter current stressing 221hrs ratio=2

Pre-aging 50hrs and Rratio=2

after current stressing 226hrs

Pre-aging 100hrs and Rratio=2

after current stressing 334hrs Sn Ni3Sn4 Pb Sn (Cu,Ni)6Sn5 Cu Cu Pb

e

- (a) (b) (c) (d)第四章、結論 對於覆晶銲錫銲錫凸塊的電性觀測,凱文結構提供更為敏感精確的量測;利 用凱文結構,可針對銲錫凸塊電遷移不同階段的變化現象,可精準的定義觀察。 無通電之銲錫凸塊,受到不同熱時效時間影響,觀察到UBM中Ni 消耗溶解及 IMC的成長的關係。愈長時間之熱時效處理,其IMC厚度是愈厚。 再將經熱時效處理之試片加熱通電,發現其電阻上升為初始電阻二倍之時 間,就是抵抗電遷移能力,會因熱時效時間愈久,高電阻率之IMC層厚度愈厚,以 減緩電流集中效應,而抵抗電遷移能力會愈強。 故為增加銲錫凸塊之抵抗電遷移能力,若於在元件使用前,可以作一步驟之 時效熱處理,來增加元件的抗電遷移 life time。至於,是否更長之熱時效時間(超 過本實驗之最長熱時效時間100hrs) ,是否會持續增加元件的抗電遷移 life time, 則有待之後進行類似實驗或以模擬建立來做進一步的確認。

第五章、參考文獻

1. Hong Xiao, Introduction to Semiconductor Manufacturing Technology, 2001. 2. Simon M Sze, Semiconductor Devices Physics and Technology, 2nd ed. 2002. 3. R.J. Wassink, Soldering in Electronics, Electrochemical Pub. Ltd., p.99, (1984). 4. http://www.chipbond.com.tw

5. V. B. Fiks, Soviet Physics – Solid State, Vol. 1, pp. 14-28, 1959.

6. W. M. Loh, K. Saraswat, and R. W. Dutton, IEEE Electron Device Lett. EDL-6, 105 (1985).

7. S. Brandenburg and S. Yeh, Proceedings of Surface Mount International

Conference and Exhibition, SM198, 4.San Jose, CA, Aug. 23-27, 1998(Edina, MN: SMTA, 1998), p. 337.

8. J. R. Black, IEEE Trans. On Electron Devices, ED-16, No4,p338, 1969. 9. H. B. Huntington and A.R. Grone, “Current-Induced Masker Motion in Gold

Wires,” J. Phy. & Chem. Solids, 20, 76 (1961). 10. I. A. Blech, J. Appl. Phys. 47, 1203 (1976).

11. I. A. Blech and C. Herring, Appl. Phys. Lett. 29, 131 (1976).

12. C. Y. Chang, S. M. Sze, ULSI Technology, the McGRAW-HILL, P. 663, 1996. 13. K. N. Tu, J. Appl. Phys., Vol. 94, No. 9, P.5456 (2003).

14. K. N. Tu, J. W. Mayer and L.C. Feldman, “Electronic Thin Film Science,”Macmillan, New York 1992.

15. S. Brandenburg and S. Yeh, in Proceedings of the Surface Mount International Conference and Exhibition, SMI98, San Jose, CA, August (1998),pp. 337–344. 16. C. Y. Liu, C. Chen, C. N. Liao, and K. N. Tu, Appl. Phys. Lett. 75, 58 (1999). 17. C. Y. Liu, C. Chen, and K. N. Tu, J. Appl. Phys. 88, 5703 (2000).

18. K. N. Tu, J. Appl. Phys. Vol. 94, Issue 9, pp. 5451-5473 (2003).

19. T. Y. Lee, and K. N. Tu, Electromigration of eutectic SnPb and SnAg3.8Cu0.7 flip chip solder bumps and under-bump metallization, JAP, Vol. 90, N. 9, 2001.

20. E. C. C. Yeh, W. J. Choi, and K. N. Tu, P. Elenius, and H. Balkan, Appl. Phys. Lett. 80, 580 (2002).

21. S. H. Chiu, T. L. Shao, and Chih Chen, Infrared microscopy of hot spots induced by Joule heating in Flip-chip SnAg solder joints under accelerated electromigration, APL 88, 022110, 2006.

22. T. L. Shao, S. W. Liang, T. C. Lin, and Chih Chen, Three-dimensional simulation on current-density distribution in flip-chip solder joints under electric current stressing, JAP 98, 044509, 2005.

23. S.W. Liang, Y.W. Chang, and Chih Chen, Three-Dimensional Thermoelectrical Simulation in Flip-Chip Solder Joints with Thick Underbump Metallizations during Accelerated Electromigration Testing, JEM, Vol. 36, No. 2, 2007.