行政院國家科學委員會專題研究計畫 成果報告

60 GHz 高速無線區域網路前瞻性技術研究--子計畫二:高速

多天線分頻正交多工通信基頻收發機之設計與製作(3/3)

研究成果報告(完整版)

計 畫 類 別 : 整合型 計 畫 編 號 : NSC 95-2219-E-002-004- 執 行 期 間 : 95 年 08 月 01 日至 96 年 07 月 31 日 執 行 單 位 : 國立臺灣大學電機工程學系暨研究所 計 畫 主 持 人 : 闕志達 計畫參與人員: 碩士班研究生-兼任助理:游景皓、游宗翰 處 理 方 式 : 本計畫可公開查詢中 華 民 國 96 年 11 月 01 日

行政院國家科學委員會專題研究計畫成果報告

60 GHz

高速無線區域網路前瞻性技術研究—子計畫二:高速多天線分

頻正交多工通信基頻收發機之設計與製作 (3/3)

計畫編號: 95-2219-E-002-004

執行期限: 95/08/01 ~96/07/31

主持人: 闕志達 教授 國立台灣大學電子工程學研究所

計畫參與人員: 游景皓 游宗翰 國立台灣大學電子工程學研究

所

一﹑摘要:

在本年度中,依照之前已設計完成的適 用於 60 GHz 無線區域網路的基頻系統設 計、送發機架構及相對應的基頻接收機,來 進行基頻接收機之硬體設計與實現。此系統 採用 MIMO OFDM 技術。目前整個系統包括傳 送機、通道與接收機的軟體架構已完成,另 外整個基頻接機的硬體架構也已經設計完 畢,在硬體架構中有考慮到如何讓整個硬體 架構達到較小及低功率之表現。 關鍵詞:多輸入多輸出技術,正交分頻 多工調變,高速率無線區域網路,基頻收發 機。Abstract

In this year, we have completed system hardware design of a baseband receiver system for a high-rate 60-GHz wireless LAN based on the transceiver design before. Also the hardware architecture and simulation platform are established. This baseband processing adopts MIMO OFDM technique, which can be more robust to channel effects in the band that the WLAN will operate. In addition, we take some hardware design skill into consideration. In this way, we can make the hardware architecture less area and lower power consumption.

Keywords: MIMO, OFDM, WLAN, Baseband receiver

二、計畫緣由與目的:

本計畫之主要目的在於搭配本研究團 隊中的無線通訊系統設計、射頻/類比電路技 術、通訊訊號處理、媒體存取協定與多重存 取等有關專長的研究人力,以達到高速率無 線傳輸應用為目標,進行 60-GHz 之無線區域 網路系統中的相關前瞻技術。本計畫在這整 合型計畫中的任務著重於基頻訊號處理、低 功率基頻接收電路設計技術、多輸入多輸出 接收機設計與系統硬體架構實現等等。最後 並進行基頻模組的整合,並對所建構的模組 進行實際測試。在本年度之前已經達成下列 幾項工作內容 (1) 傳送機的架構及模擬驗證 (2) 60 GHz多路徑通道模型的模擬 (3) 接收機的架構及表現 而本年度即是將已設計完成的接收機 進行硬體實現,並進行 FPGA 驗證功能,已 達成下列幾項工作內容 (1) 60GHz基頻接收機的硬體架構 (2) 系統模擬結果 (3) FPGA驗證(尚在進行中)三﹑方法及結果:

接收機硬體架構介紹、硬體電路設計與化簡 及模擬結果a.

接收機硬體架構 在此介紹傳送機的基本硬體架構,如圖 1所示。PART1(圖 1(a))部分為時域的信號處理,是作初始同步(符元邊界)以及 CFO 偵測,而 PART2(圖 1(b))主要是作 256 點的 FFT 運算以 及 SCO 補償、以及 JWLS Tracking Loop。 PART3(圖 1(c)) 則是頻域的信號處理,主要是 做 MIMO Channel Estimation 以 及 VBLAST Equalizer及 Slicer 等。接下來將針對硬體架構 中比較重要的部份來做說明及其電路設計架 構圖。

a.1 延遲相關器(Delay correlator)

由於每個訊框的一開始會傳送重覆的 64點短前置碼,接收機將利用這些短前置碼 資料重覆的特性以延遲相關器來估測訊框的 起始位置,其公式如(式 1)下:

∑

=− + + + = 1 0 * ) ( ) ( ) ( L k L k m r k m r m c (式 1) 。由於整個初始同步的動作需要兩個訊框的 時間才能完成,所以在搜尋第二個訊框的起 始位置時,為配合分數載波頻率飄移的的重 估,我們改採用延遲長度為 128 的延遲相關 器來實現,且考量到延遲長度為 64 和 128 的 兩套延遲相關器不會同時用到,所以可以合 併起來,其硬體架構如圖 2。另外倘若系統 的 LP 是採取新的 LP 格式傳送,那麼我們的 延遲相關器將擴展到長度 256。而我們在求 之後的分數或者是整數載波頻率飄移估測 時,還需要先求取延遲相關器輸出振幅的最 大值及一半最大值,其電路架構如圖 3。a.2 分數載波頻率飄移估測(Fractional Part

CFO Acquisition) 我們可以利用當延遲相關器的輸出有最 大值時的輸出相位,即可測出分數載波頻率 的飄移,其架構如圖 4。而在求得分數載波 頻率飄移前的延遲相關器的輸出相位則是用 CORDIC之法來達成,其架構如圖 5。

a.3 整數載波頻率飄移估測(Integer Part CFO

Acquisition)

由於在 40ppm 的 CFO 最大值,會產生

integer CFO的問題,所以在此我們將會用到 3 套 Correlator Bank 來計算相關性,然後看哪一 個 Correlator Bank 最大,再來判斷出現在 CFO 比較靠近-4,0,4 個 subcarrier spacing 三者中的 哪一個,如圖 6。圖 6.表示當 CFO 介於-2~+2 subcarrier spacing時,會被 Fractional CFO 補償 到 0,如果 CFO 大於 2 subcarrier spacing or 小 於-2 subcarrier spacing,會分別被補償到+4 subcarrier spacing and -4 subcarrier spacing,而圖 6 中的藍色粗線是表示系統會遭遇之最嚴重 的 CFO 範圍:-3.84~+3.84 個 subcarrier spacing。 接著就可以利用 3 套 Correlator Bank 來判斷出 Integer CFO是-4,0,+4 個 subcarrier spacing 三者 中的那一個。其 Correlator Bank 架構圖如圖 7 所示。 a.4快速傅利葉轉換(FFT) 在時域方面將載波頻率補償回來後,即 需 256 點 FFT 來將值轉換到頻域上來進行其 它效應的估測。在本硬體架構中的快速傅立 葉轉換如圖 8,其中的 PE 之架構如圖 9,設 計之 FFT 是運用兩級 Radix 2/4/8 Unit 及一級的 Radix-22 Unit single path delay feedback的架構 來實現 256 點 FFT,以減少複數乘法器及暫 存器的數目,且這兩種結合的好處為只要使 用兩個 Twiddle Factor 的複數乘法器,可加速 電路的運作。

a.5 SCO反旋轉器(SCO De-rotator)

在同步追蹤迴路中,取樣點在時域上位 置的偏移相當於在頻域上發生相位的旋轉, 所以我們只要算出在頻域上每個次載波所需 要調整的相位旋轉量,再做相位旋轉的動作 即可。而此模組依據累加之取樣時脈偏移估 計值,在頻域進行相位反旋轉,以補償取樣 時間偏移,其電路架構如圖 10。

a.6 聯合加權最小方差估計器(Joint Weight

Least Square Estimation, JWLSE)

Rotation DIgital Computer, CORDIC)擷取出領航 碼之振幅及相位,並使用 JWLSE 演算法,利 用相鄰 OFDM Symbol 之領航碼在時間上的相 位旋轉差異量,來進行殘餘載波頻率偏移以 及取樣時脈偏移估測,其精神即是權重的概 念,能量高者權重高,使估測值更為準確, 而其電路架構如圖 11。

a.7 多輸入多輸出通道估計(MIMO Channel

Estimation)

其電路架構如圖 12,此處利用經過 SCO De-rotator後的訊號來當輸入,並且搭配內部 central control電路所計算的 sample counter 來 取出 Long preamble 的值,如此一來即可得到 四種通道(2x2)的 Channel Gain 值,並配合 平均及頻域濾波技巧,消除雜訊干擾。

a.8相位反旋轉器(Phase De-rotator) 相位雜訊或追蹤迴路收斂過程在各次載 波所造成的 Phase Error 可藉由偵測領航碼的 相位取得,接下來再將 SCO De-rotator 出來的 訊號相乘其相位來作反旋轉補償,其電路架 構如圖 13。 a.9 縱 向 - 貝 爾 實 驗 室 多 層 空 時 等 化 器 (VBLAST Equalizer) 在 Basic-MIMO 模式下,利用通道估計的 結果,對輸入訊號作 VBLAST 等化,其演算 法的重點在於解碼時需要比較兩條天線信號 的能量,從具有較大接收信號能量的路徑開 始解碼。其電路架構如圖 14。

b.

硬體電路設計與化簡 在硬體設計上有許多考量,例如面積、 延遲時間(latency)等,接下來將介紹一些 常用的電路架構及其方法。 b.1 複數乘法器(Complex Multiplier) 兩個複數乘法器相乘的結果為下列式 2: ) ( ) ( ) )( (a+ jb c+ jd = ac−bd + j bc+ad (式 2) 原則上只需要 4 個實數乘法器及 2 個加法器 來實現,如圖 15(a)所示,但若將式 2 改寫成 式 3: )] ( ) ( [ )] ( ) ( [ ) )( ( d c b b a d j d c b b a c jd c jb a − + + + − + − = + + (式 3) 因為 b(c-d)可以共用,所以最後只需要 3 個實 數乘法器與 5 個加法器來實現即可,如圖 15(b),如此以來所需要的硬體面積將會減少。 b.2 延遲線(Delayline) 當本系統在運作時,常常需要將資料暫 存起來,等待控制訊號或是其他輸入信號的 結果產生後,再依序將資料讀取出來做運 算,在硬體架構中我們將採取兩種方法搭配 使用,法 1 為利用位移暫存器(shift register)之 法來做,如圖 16(a)所示,運用於延遲點數很 小時,如 32 點、64 點等,由於每次 clock 一 來,所有暫存器裡的資料都必需往右位移到 下一個暫存器,如此會消耗大量的 power,但 在延數點數夠小時,所需要的面積將小於法 2;而法 2 則是利用 dual port 的 RAM,如圖 16(b) 所示,藉由控制寫入位址,將資料依序存在 不同的位址,接著再控制讀取位址,將先前 存入的資料讀取出來即可,這樣每次 clock 一來,RAM 只做一次存取的動作,可以減少 功率,當延遲點數夠大時,其實現 RAM 的硬 體面積將比用位移暫存器要小很多,但若在 延遲點數較小時,RAM 所需的面積就變的較 大。 b.3 正餘弦產生器(Sin-Cos Generator) 在 FFT、CFO 和 SCO 的補償電路中,都 需要將資料做相位旋轉的動作,因此需要一 正餘弦產生器,如(式 4)。若正餘弦產生器的 輸 入 為 一 角 度 θ , 則 輸 出 cos(2πθ 與) ) 2 sin( πθ 之值,以供後續的電路利用,將資 料做相位的旋轉。)) 2 sin( ) 2 )(cos( ( ) (a+ jb ⋅ej2πθ = a+ jb πθ + j πθ (式 4) 而本系統所採用的方法為分段線性近似的方 法來產生正餘弦值,其近似公式如下: ≤ ≤ + ≤ ≤ ≈ = 8 1 16 1 , 128 9 8 41 16 1 0 , 4 25 2 sin θ θ θ θ πθ A (式 5) − ≤ ≤ − ≤ ≤ − ≤ ≤ − ≈ = else A A A A A A A B , 4 3 4 5 2 1 4 1 , 8 3 16 17 4 1 8 1 , 16 3 64 65 8 1 0 , 16 1 1 2 cos πθ (式 6) 此法的電路圖如圖 17,我們只需要用位移與 相加的方法即可算出sin(2πθ 與) cos(2πθ 的) 值,其法有別於傳統法利用查表的方法,當θ 的解析度愈高時,傳統法需要的耗費的硬體 面積也愈多,而分段線性近似法只會小幅度 的增加,另外論近似結果,分段線性近似法 還算不錯,所以相較之下,本系統即採用分 段線性似法來實現正餘弦產生器。 b.4 除法器(Divider) 本系統中需要用到實數除法器和複數除 法器,而複數除法器的實現公式如式 7 2 2 2 2 1 b a b j b a a bj a + − + + = + (式 7) 我們只要先利用兩個乘法器、兩個加法器及 兩個除法器即可達成。至於實數除法器的實 現電路如圖 18,本法是引用長除法的概念, 使用疊代的方法來實現。

c.

系統模擬結果 接下來將介紹一些在我們系統中對一些 效應是否正確改善的模擬結果,另外再來待 我們系統全部的硬體模擬功能都能正確達到 後,將上 FPGA 板上進行驗證。c.1 Carrier Frequency Offset (CFO)補償

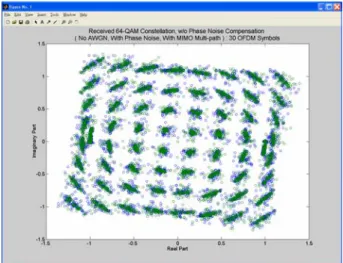

在本系統中,我們有利用 Delay Correlator 與 Correlator Bank 來分別偵測 Fractional & Integer CFO,並用加以補償,我們分兩個部 份來做模擬結果,第 1 個是假設 Phase Offset 為 0 , CFO=10ppm 的 情 況 下 , 其 星 座 圖 (64QAM)如圖 19 所示,可以看出來完全消 除 CFO 的效應;第 2 個是當加入相位雜訊以 後,CFO=40ppm(有 Integer CFO),沒有補償 前的模擬(64QAM)如圖 20,接著將 CFO 補 償區塊打開後的模擬(64QAM)如圖 21,由 此可知我們所設計之 CFO 補償迴路的確發揮 了其正確的作用。 c.2 Phase Noise補償 在本系統架構中 PART3 中的 Phase De-rotator關掉的時候,星座圖(64QAM)被 旋轉的效應如圖 22,如果我們把 Phase De-rotator打開,星點擴散的情況將大大改 善,如圖 23,所以這表示我們所設計的 Phase De-rotator能夠正確的對相位雜訊進行補償。

c.3 Sampling Clock Offset (SCO)補償

在本系統架構中是採用在頻域作補償的 動作,當尚未作 SCO 補償時的模擬如圖 24 (64QAM),從這張圖可發現系統完全變亂 掉,此時我們將 SCO 的 Frequency Domain De-rorator打開後再跑的模擬如圖 25,從此圖 可以看出我們所設計之 Frequency Domain De-rorator對於 SCO 的補償有很大的幫助。

c.4 Residual CFO補償

在本系統架構中加上一迴路濾波器 (Loop Filter)搭配 JWLS Block 所計算出的兩 兩 OFDM symbol 之間 pilot 的相位差,來補償 一開始估測出的 CFO 不夠精準的情況。當我 們先不要打開 Loop Filter,表示沒有補償 Residual CFO的模擬(64QAM)如圖 26,接著 打開 Loop Filter 所跑的模擬如圖 27,我們可 以發現 Loop Filter 可以正確的將 Residual CFO

補償回來。

c.5 I/Q Imbalance補償

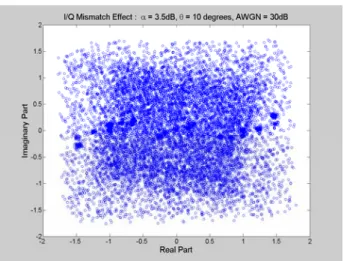

在本系統架構中使用幾個 OFDM Symbol 來當作 training symbol,好來提高估計 I/Q Imbalance的準確度,倘若尚未補償 I/Q Mismatch的模擬(64QAM)如圖 28,接下來 圖 29 是經過補償過後的模擬,由這兩張圖比 較可得知,在補償方面有很大的效果。

四、結論

本 計劃 在第 三年度 中已 完成 了 MIMO OFDM 基頻接收機的硬體架構設計與其模 擬,在軟體模擬結果方面與規格相符,關於 基頻接收機硬體方面已經都設計完成,目前 的硬體模擬驗證階段已經在進行中,驗證階 段到全系統的 PART2 部份,將加快腳步在短 時間內把硬體模擬驗證完成,另外也同時在 尋找合適的 ADC 模組與 FPGA 模組,待硬體 模擬驗證完成後,將進行 FPGA 驗證。五、參考文獻:

[1]www.ist-broadway.org/documents/deliverables/broadway-w p3-d7R3_annex1.pdf[2] Takeshi Manabe, “Effects of Antenna Directivity and Polarization on Indoor Multi-path Propagation Characteristics at 60GHz”, IEEE Journal On Selected Areas In Communications, April, 1996

[3] IEEE 802.11a Physical Layer standard

[4] Roberto Corvaja and Silvano Pupolin , “Phase Noise Limits in OFDM Systems”

[5] Ali Behravan, “System Implications in Designing a 60GHz WLAN RF Front-end”

[6] Richard van Nee and Prasad, OFDM for Wireless

Multimedia Communications.

六、圖表:

圖 1(a):接收機架構圖

圖 1(b):接收機架構圖

圖 2:延遲相關器電路圖

圖 3:尋找延遲相關器輸出振幅的最大值及一半最大 值的電路圖

圖 4:分數載波頻率飄移估測電路

圖 5:CORDIC 電路示意圖

圖 6:經 Fractional CFO 補償後,三種可能的 Integer CFO

數值

圖 7:用來估計 Integer CFO 的 Correlator Bank 架構圖

圖 8:256 點 FFT 架構圖

圖 9:PE 電路圖

圖 11:JWLS 方塊架構圖

圖 12:Channel Estimation 方塊架構圖

圖 13:相位調整電路圖

圖 14:VBLAST 電路運作示意圖

圖 15: 複數乘法器

圖 16: 延遲線電路圖 (a)Shift register (b)dual port RAM

圖 17: 正餘弦產生器電路圖

圖 19:CFO=10ppm 的星座圖(無相位雜訊) 圖 20:CFO=40ppm 的星座圖(沒有補償) 圖 21:CFO=40ppm 的星座圖(補償後) 圖 22:沒有補償相位雜訊之星座圖 圖 23:有補償相位雜訊之星座圖 圖 24:沒有補償 SCO(40ppm)之星座圖

圖 25:有補償 SCO(40ppm)之星座圖

圖 26:Residual CFO 造成的星座圖效應

圖 27:Residual CFO 補償後的星座圖

圖 28:沒有補償 I/Q Imbalance 的星座圖