國 立 交 通 大 學

電機學院 電信學程

碩

士

論

文

切換式穩壓器的電磁干擾研究

The Research of the Switching Regulator EMI

研 究 生:黃新凱

指導教授:吳霖堃 博士

切換式穩壓器的電磁干擾研究

The Research of the

Switching Regulator

EMI

研 究 生:黃新凱 Student:Hsin-Kai Huang 指導教授:吳霖堃 博士 Advisor:Dr. Lin-Kun Wu 國 立 交 通 大 學

電機學院 電信學程

碩 士 論 文 A ThesisSubmitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in

Communication Engineering December 2013

Hsinchu, Taiwan, Republic of China

i

切換式穩壓器的電磁干擾研究

研究生:黃新凱 指導教授:吳霖堃 博士

國立交通大學 電機學院 電信學程 碩士班

摘 要

本論文選用“致新科技"公司,型號 G5684 的 Step Down DC-to-DC converter IC 為例,探討改變切換頻率對輸出電壓漣波(Ripple)和電 磁干擾(Electromagnetic Interference, EMI)問題的影響。

由 Switching Regulator 的結構原理可知,輸出電壓漣波與頻率 的平方成反比,提高切換頻率可降低漣波,電感亦可選用較低的電感 值,而使印刷電路板(Printed circuit board, PCB)的使用面積下降。 但是副作用就是其內部結構造成 PWM 週期切換時不是一完美的方波, 在 high-low 急遽變化的地方,波形會產生震鈴(Ringing),此 ringing 會疊加在輸出電壓波形上,造成雜訊干擾,實際量測 EMI,結果隨著 頻率升高而變糟。研究結果顯示,在輸出電壓端加上可抑制 ringing 雜訊的 ferrite bead 可達到抑制 EMI 的效果。

ii

The Research of the Switching Frequency EMI

Student: Hsin-Kai Huang Advisor:Dr. Lin-Kun Wu

Degree Program of Electrical and Computer Engineering National Chiao Tung University

Abstract

In this paper, we used the GMT model G5684 Step Down DC-to-DC IC to explore the effect of changing the switching frequency on the output voltage ripple and electromagnetic interference (EMI).

From the structural principle of switching regulator, we can see that the output voltage ripple is inversely proportional to the square of the frequency. Increasing the switching frequency reduces ripple and allows the use of lower-valued inductor which occupies smaller area on the printed circuit board (PCB). But the side effect is when the wave changes rapidly in the high-low transition, ringing occurs. The ringing will be superimposed on the output voltage waveform, causing noise interference. When we test EMI, the result becomes worse as the frequency increases. The result shows that adding ferrite bead on the output voltage terminal can suppress EMI associated with the ringing noise.

iii

誌 謝

工作之後重回校園是我的心願,在這段時間當中受到師長、同 學、公司主管以及同事的鼓勵和支持,讓我收穫良多。 感謝我的論文指導教授-吳霖堃教授,不厭其煩、深入淺出及耐 心的教導,其次,要感謝同事和朋友們在這段時間的支援與協助,還 有太太的包容與鼓勵,讓我可以順利完成學業。iv

目 錄

中文摘要 ... i 英文摘要 ... ii 誌 謝 ... iii 目 錄 ... iv 圖 目 錄 ... vi 表 目 錄 ... vii 第一章 簡介 ... 1 第二章 降壓型電源轉換器原理介紹 ... 3 2.1 直流-直流降壓型轉換器簡介 ... 3 2.1.1 線性穩壓器 ... 3 2.1.2 切換式穩壓器 ... 52.2 降壓型切換式電壓轉換器(Buck Converter or Step-Down Converter)原理... 6

2.2.1 概述 ... 6 2.2.2 降壓型電源轉換器工作原理 ... 7 2.3 降壓型電源轉換器的元件選擇 ... 13 2.3.1 輸出電容 ... 13 2.3.2 輸出電感 ... 14 2.3.3 切換開關 ... 14 2.3.4 箝制整流器 ... 15 2.4 降壓型電源轉換器的 EMI 干擾 ... 16 第三章 實驗方法與結果分析 ... 18 3.1 實驗電路與佈局 ... 18 3.1.1 Step-Down DC-DC Converter ... 18 3.1.2 實驗電路解析 ... 20 3.2 Step-Down DC-DC 切換頻率對 Ripple 的影響 ... 22 3.3 增加消除高頻雜訊的電感對 EMI 的影響 ... 31 3.3.1 改變切換頻率對 EMI 量測結果的影響 ... 31

v

第四章 結論 ... 49

vi

圖 目 錄

圖 2-1 LINEAR REGULATOR線性穩壓器示意圖 ... 4 圖 2-2 SWITCHING REGULATOR切換式穩壓器示意圖 ... 5 圖 2-3 降壓型電源轉換器 ... 8 圖 2-4 ON STATE ... 9 圖 2-5 OFF STATE ... 10 圖 2-6 降壓型電源轉換器主要電壓電流波形 ... 10 圖 2-7 漣波(RIPPLE)和雜訊(NOISE) ... 17 圖 3-1 DC-DC 規格簡介 ... 19 圖 3-2 G5684 IC 腳位配置圖 ... 19 圖 3-3 實驗電路 ... 20 圖 3-4 輸出電壓和 SWITCH PIN輸出波形,FSW=300KHZ,L=4.7ΜH ... 23 圖 3-5 輸出電壓漣波波形,FSW=300KHZ,L=4.7ΜH ... 24 圖 3-6 輸出電壓和 SWITCH PIN輸出波形,FSW=1000KHZ, L=1.5ΜH ... 24 圖 3-7 輸出電壓漣波波形,FSW=1000KHZ,L=1.5ΜH ... 25 圖 3-8 FSW=300KHZ上升邊緣的RINGING ... 27 圖 3-9 FSW=300KHZ下降邊緣的RINGING ... 27 圖 3-10 FSW=300KHZ RINGING的 FFT 結果 ... 28 圖 3-11 FSW=1000KHZ上升邊緣的RINGING ... 28 圖 3-12 FSW=1000KHZ下降邊緣的RINGING ... 29 圖 3-13 FSW=1000KHZ RINGING的 FFT 結果 ... 29 圖 3-14 RISING RINGING的 FFT 結果 ... 30 圖 3-15 FALLING RINGING的 FFT 結果 ... 30 圖 3-16 FSW=300KHZ,L=4.7ΜH,EMI 垂直極化量測結果 ... 33 圖 3-17 FSW=300KHZ,L=4.7ΜH,EMI 水平極化量測結果 ... 34 圖 3-18 FSW=1000KHZ,L=1.5ΜH,EMI 垂直極化量測結果 ... 35 圖 3-19 FSW=1000KHZ,L=1.5ΜH,EMI 水平極化量測結果 ... 36 圖 3-20 FERRITE BEAD的阻抗特性圖 ... 38 圖 3-21 電壓輸出端加入BEAD後的前後波形比較 ... 39 圖 3-22 FSW=1000KHZ,L=1.5ΜH,電壓輸出端 ... 40 圖 3-23 FSW=1000KHZ,L=1.5ΜH,電壓輸出端 ... 41 圖 3-24 FSW=1000KHZ,L=1.5ΜH,電壓輸出端距離 5CM處 ... 42 圖 3-25 FSW=1000KHZ,L=1.5ΜH,電壓輸出端距離 5CM處 ... 43 圖 3-26 FSW=1000KHZ,L=1.5ΜH,負載端 ... 44 圖 3-27 FSW=1000KHZ,L=1.5ΜH,負載端 ... 45vii

表 目 錄

表 3-1 各腳位功能概述 ... 20 表 3-2 輸出電壓的建議搭配阻值 ... 21 表 3-3 切換頻率和電感建議值 ... 22 表 3-4 FERRITE BEAD的電子特性 ... 37 表 3-5 不同 BEAD擺放位置的垂直極化量測值比較表 ... 47 表 3-6 不同 BEAD擺放位置的水平極化量測值比較表 ... 481

第一章

簡介

由於電力公司所送出的是交流電源,而現今電子產品大多使用直 流電源,幾乎每個電子產品,如筆記型電腦、平板電腦、液晶電視、 智慧型手機等電子設備,都會使用到交流-直流電源轉換器(AC-DC converter),將交流高壓市電轉換為低電壓的直流電源,如:12V、19V。 但隨著電子技術的進步,電子產品朝向高速化與輕、薄、短、小 發展,積體電路(Integrated Circuit, IC)也隨著製程技術提升,運 作頻率愈來愈快,工作電壓則愈來愈低,從以往的 5V 和 3.3V,核心 工作電壓已降到 1.2V。要達到 IC 的工作電壓只單靠 AC-DC converter 無法達到,因此需使用直流-直流電源轉換器(DC-DC converter)將電 壓降至 IC 所需的工作電壓。愈低的工作電壓代表 IC 對雜訊的耐受度要求愈嚴格。加上現今電 子產品強調輕薄化,造成印刷電路板((Printed circuit board, PCB) 的面積減小,電路密度愈來愈高,零件選用也只能朝向微小化進行, 敏感性電路受周圍電路干擾的機會則是大大的增加,所以電子產品除 了滿足功能性的需求外,一方面要避免產生過高的電磁輻射,造成系 統內部電路之間彼此干擾或干擾到周圍其他系統的正常運作,另一方

2 面也要提升本身抵抗外來干擾的能力。電子產品同時滿足這兩項條 件,我們稱之為合乎電磁相容性(Electromagnetic Compatibility, EMC)。 電源系統是產生電磁干擾與傳播電磁干擾的一個重要機制。配合 現今電子產品對輕薄和省電的要求,電源系統一般使用交換式的 DC-DC converter,也就是切換式穩壓器(Switching Regulator)。它 可調節操作頻率,進而縮小元件使用面積,並具有高轉換效率的優點。 但因為是切換式元件,本身電路結構會產生漣波和雜訊,如何降低漣 波增加電壓穩定性和避免所產生的雜訊干擾後方電路是一重要課題。 一般來說,避免電磁輻射干擾的對策愈靠近輻射源,所需的控制 成本越小,得到的效果也最大[1][2]。對產品開發流程來說,在研發 設計階段就應該考慮電磁輻射干擾的問題,此階段發現與解決電磁輻 射干擾問題時,可用的對策最多、成本較低、隱密性高、影響製作的 流暢性最低且對計畫時程影響最小。 本 論 文 針 對 現 今 常 用 的 降 壓 型 轉 換 器 (Buck converter or Step-down converter)進行漣波和雜訊的討論。第一章為簡介;第二 章介紹降壓型轉換器的工作原理和元件選用;第三章針對降低漣波和 雜訊所做實驗數據進行分析;最後第四章做結論。

3

第二章

降壓型電源轉換器原理介紹

2.1 直流-直流降壓型轉換器簡介

電壓轉換的方式依照電路結構與操作方式大致可分為兩類:線性 穩壓器(Linear Regulator)與切換式穩壓器(Switching Regulator)。

2.1.1 線性穩壓器[3][4][5] 線性穩壓器運用在輸入電壓高於輸出電壓的情況下,提供輸出端 一恆定的直流輸出電壓。此架構使用錯誤放大器,正向端連接參考電 壓(

V

ref),反向端連接輸出端經分壓電阻後的電壓,以此調節電晶體的 導通變化。電晶體如同可變電阻,連續地調整以保持恆定的輸出電壓。 輸出電壓與參考電壓有關,可藉由選擇回授電阻的阻值來決定輸出電 壓,可由下式得出: ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ + × = 2 1 1 R R V Vout ref (2-1)4 圖 2-1 Linear Regulator 線性穩壓器示意圖 線性穩壓器電路架構簡單不需用到電感,較容易做成積體電路, 不需要複雜的控制訊號,成本較低,外圍零件少,對於固定電壓輸出 的場合,外圍只需 2~3 個很小的電容即可構成整個電路,可有效降低 電路板所需面積。由於沒有開關時大的電流變化所引發的電磁干擾, 適合用於對雜訊較敏感的電路供電。但缺點是只能作降壓的轉換,而 因電晶體的作用如同電阻,所以部分功率會消耗在電晶體上,使得轉 換效能差,這也是線性穩壓器工作時易發熱的主要原因。

5 2.1.2 切換式穩壓器[3][4][5] 切換式穩壓器結構上比起線性穩壓器較為複雜,最基本的切換穩 壓器結構須一個電晶體做為開關,一個二極體,一個電感器和一個電 容器作為電能儲存元件。透過控制電晶體開關模式的不同可分為兩 類:一種為固定工作頻率,調整電晶體導通時間長短,改變工作週期 (Duty Cycle),也就是電晶體導通時間和切換時間的比值,稱為脈衝 寬度調變(Pulse Width Modulation ,PWM);另一種為固定導通關閉時 間,也就是工作週期固定,而調變訊號頻率快慢,稱為脈衝頻率調變 (Pulse Frequency Modulation ,PFM)。

6 不同於只能降壓的線性穩壓器,切換式穩壓器可以升壓、降壓、 降升壓或將輸入電壓反相。因具有較高的電源轉換效率,可將散熱問 題減至最低,降低能源損耗。但是由於切換式電源是以週期性的切換 開關來達到穩定的輸出,因此會在輸出端產生漣波疊加在直流輸出電 壓,而對系統產生不必要的干擾。對於較敏感的系統,此類穩壓器就 不適用。

2.2 降壓型切換式電壓轉換器(Buck Converter or Step-Down

Converter)原理

2.2.1 概述

切換式穩壓器應用於直流-直流轉換器中可分為四種結構,Buck or Step-down regulator 降壓型穩壓器; Boost or Step-up regulator 升壓型穩壓器;flyback or buck- boost regulator 反激式或降升壓 型穩壓器和 Cuk 型穩壓器。藉由功率電晶體的開關切換動作將輸入端 的能量轉移至輸出端的電感和電容等儲能元件,以提供負載所需能量。

7 的穩定電壓(通常為 1.2V 到 5V)的電壓源,因其結構簡單、成本低、 高可靠度、高轉換效率而被廣泛用於現今多數電子產品的內部。 以下就降壓型電源轉換器的工作原理做簡單說明。 2.2.2 降壓型電源轉換器工作原理[6] 降壓型電源轉換器利用脈衝寬度調變(PWM)機制來控制導通元 件,此技術會改變工作週期(Duty Cycle),也就是電晶體導通時間和 截止時間的比值,再配合電感的電力儲存能力,讓輸出電壓在有限的 輸入電壓和負載電流範圍內保持固定。圖 2-3 是一組簡單的降壓型電 源轉換器結構圖,Q 是一顆 MOSFET 的功率開關,配合 PWM 訊號控制電 晶體的導通與否。二極體 D 通常稱為箝制二極體(catch diode)或飛輪 二極體(flywheel diode),將輸入直流電壓

V

in切換成具有V

in和 0 兩 種狀態之高頻脈動直流。輸出電感 L 與輸出電容 C 組成低通濾波器產 生直流電壓輸出。8 圖 2-3 降壓型電源轉換器 降壓型電源轉換器電路工作原理可分成 ON/OFF 兩種模式,ON 狀 態的持續時間為

D×T=T

on,其中D

為電晶體工作週期,介於 0~1 之間, T 為電晶體的切換週期。OFF 狀態的持續時間被稱為T

off。在每個開關 週期的模式下只有 ON/OFF 狀態,T

off等於(1-D)×T

。(1-D)

有時也被稱 為D'

,由於D

介於 0~1 之間,此電路的輸出電壓 Vout必會較輸入電壓 Vin來得小,故可達到降壓的功能。 ON stage(0 <t<DT

) 當電晶體 Q 導通時,二極體 D 的陰極電壓約等於輸入電壓V

in,二 極體逆偏形成斷路,輸入電壓經 Q 對電感 L 充電並供應電壓至電容 C 及負載 R,此時電感電壓V

L=V

in-V

out,由於輸出直流電壓V

out必然低於V

in,故此時的V

L 為一正電壓,L 便儲存能量,因此輸出電感電流i

L 線性上升。此時其輸入電壓源傳送能量給 L 與負載 R。流經功率開關9 之電流

i

在此工作模式下等於輸出電感電流i

L。 圖 2-4 ON State OFF stage (DT< t < T

) 當電晶體 Q 截止時,電感 L 的電壓極性反轉,使二極體 D 順偏導 通,電容 C 及電感 L 均對負載 R 放電,此時 L 的跨壓V

L等於-V

out,電 感 L 便釋放能量,因此i

L線性下降。此時其負載 R 的能量由電感 L 提 供。流經二極體 D 之電流i

D 在此工作模式下等於輸出電感電流i

L。10 圖 2-5 OFF State 下圖 2-6 列出主要電壓電流波形 (a) (b) (c) (d) 圖 2-6 降壓型電源轉換器主要電壓電流波形

11

當 ON stage 電感電壓

V

L=V

in-V

out;OFF stage 電感電壓V

L=-V

out,由式(2-2)[7]: dt di L VL= × L (2-2) 可得到

i

L上升斜率和下降斜率如下: 上升斜率: L V V L V dt di iL L L in out − = = = + Δ ( ) (2-3) 下降斜率: L V L V dt di iL L L out − = = = − Δ ( ) (2-4) 在穩態條件下,Δi

L(+)在 ON state 下的電流增加量和Δi

L(-)在 OFF state 下的電流減少量是相等的,所以可由下式(2-5)計算出電感的漣 波電流變化量,Δi

L。 = = Δ∫

V dt L iL DT L 1 0 L(Vin−Vout)×DT 1 (2-5) 由Δi

L,可得出i

L,max和i

L,min如下: 2 max L L L, i I i = +Δ (2-6) 2 min , L L L i I i = −Δ (2-7) 在V

out的總變化,Δv

out,是峰值對峰值的輸出漣波,當輸出電容的電 壓在最大值和最小值之間改變期間,電容上的電荷變化是由q

=C(Δv

out) 決定,其中q

是電流波形通過零點之間的積分結果,即圖 2-6(c)的綠 色面積部份[8]: sw L L f i i T q × Δ = Δ × × = 8 2 2 2 1 (2-8) 由q

=C(Δv

out)可得:12 C f i v sw L out × × Δ = Δ 8 (2-9) 其中Δ

v

out:輸出電容的漣波電壓 Δi

L:輸出電感的漣波電流f

sw:切換頻率 C:輸出電容容值 將Δi

L用式(2-5)帶入式(2-9),可得: 2 8 ) ( 8 ) ( sw out in sw out in out f C L D V V L C f DT V V v × × × − = × × × × − = Δ (2-10) 電感感值須根據漣波電流要求才能決定,設計人員通常需要漣波 電流小於 20%的平均電感電流。如式(2-5)所示,較高的V

in或V

out也 會增加漣波電流。由於核心飽和會導致電感產生功耗,因此電感必須 在不造成核心飽和的情形下承受峰值開關電流。在降壓型穩壓器中, 電感的感值通常使用 2.2μH 至 10μH。隨著電感的電流上升或下降, 輸出電容提供立即地電流變化以配合負載電流的改變。一個小感值電 感可快速地抬升電流來降低輸出電容所需的容值,提高輸出電流迴轉 率,這可改善轉換器的負載暫態響應能力,但也導致較大的輸出電壓 漣波。大感值電感則會降低漣波電流並減少電感的磁滯功耗。 由式(2-5)和(2-10)可知,Δi

L與 PWM 切換頻率成反比,Δv

out與 PWM 切換頻率的平方成反比,輸出電感感值和輸出電容容值各有考量 的選擇因素,提高切換頻率對降低Δi

L和Δv

out是一簡單的策略。13 2.3 降壓型電源轉換器的元件選擇 本節主要討論降壓型電源轉換器的組成元件的功能。各元件通常 必須滿足規格書中最小的性能要求。本節主要介紹輸出電容、輸出電 感、切換開關 Q 和箝制二極體 D。 2.3.1 輸出電容[6] 在切換式電源轉換器中,輸出電容的功能主要是儲能,由於施加 的電壓能量被存儲在電容器的電場。因此,電容的功能,是試圖保持 一個恆定的電壓。 降壓型電源轉換器的輸出電容值選擇限制是根據輸出電壓的漣波 規範。由於輸出電感的漣波電流通常是已經確定的,該電容的等效串 聯阻抗決定了輸出電壓的漣波大小。電容的等效電路是由等效串聯電 阻(ESR),等效串聯電感(ESL),和電容 C 組成。下面給出了輸出電容 選擇的指導方針。 對於連續的電感電流操作模式,(2-9)式顯示電感的電流漣波Δ

i

L,切換頻率f

sw,和輸出電壓漣波Δv

out,決定所需之電容容值。假定 所有的輸出電壓漣波皆是由電容的容值所產生,則所需電容之最小值14 可由下式表示。 out sw L v f i C Δ × × Δ ≥ 8 (2-11) 假設有足夠的電容容值,則由於容值所產生的漣波可忽略不計, 所 以 依 據 輸 出 電 壓 漣 波 要 求 來 選 擇 輸 出 電 容 器 的 等 效 串 聯 電 阻 (ESR)。其選擇公式如下: ESR i vout =ΔL× Δ (2-12) 2.3.2 輸出電感[6] 在切換式電源轉換器中,輸出電感的功能主要是儲能,能量被儲 存在流動的電流所產生的磁場中。因此,電感的功能是試圖保持恆定 電流和限制電流流動的變化率。 除了電感感值,其他重要的因素要考慮選擇電感的最大直流或峰 值電流和最大工作頻率。電感的額定直流電流在使用時是很重要的, 確保電感不會過熱或飽和。確保電感操作於其最大頻率等級下使其鐵 心的損耗不超標而造成過熱或過飽和。 2.3.3 切換開關[6]

15 切換開關的功能是控制從輸入功率源的輸出電壓的能量流。在降 壓系統中,當切換開關(圖 2-3 中的 Q)開啟時連接輸入至輸出濾波器, 關閉時斷開輸入至輸出濾波器。切換開關開啟時必須引導輸出電感中 的電流,關閉時隔離整個輸入電壓。此外,切換開關必須快速地切換, 避免過多的功耗產生。 切換開關是一個功率 MOSFET。其他功率元件也可使用,但在驅動 電路的情況下,MOSFET 在成本和性能方面是最好的選擇。選擇時應考 慮選擇適合的 MOSFET 的最大汲源極崩潰電壓,V(BR)DSS和最大汲極電 流,

i

D(max)。 MOSFET 的 V(BR)DSS額定值應大於最大的輸入電壓和預留瞬變 和尖峰的電壓量。i

D(max)選擇至少兩倍於最大功率輸出電流。 2.3.4 箝制整流器[6] 當切換開關關閉時,箝制整流器提供了一條路徑給電感電流。選 擇整流器的重要標準包括:快速開關,崩潰電壓,額定電流,低正向 壓降最大限度地降低功耗和合適的封裝。一個低電壓輸出的肖特基整 流器通常是最好的選擇。崩潰電壓必須大於輸入電壓的最大值,並對 瞬變和尖峰電壓的反應增加些餘量。電流額定值應至少兩倍於輸出電 流。發生在從導通到非導通狀態轉換間的開關損耗和傳導損耗相比是16 非常小的,並通常被忽略。 2.4 降壓型電源轉換器的 EMI 干擾 在現今電子設備中,DC-DC converter IC 是電源電路不可缺少的 部份。由於電壓和電流波形的非線性性質,導致切換式電源轉換器在 其操作期間會產生一些漣波和雜訊。這種切換動作就變成了一種雜訊 源,這種雜訊可泄漏至直流電源線,且透過 AC 電源線發射出去。 同時,隨著電子設備功能的增多,所需半導體 IC 的種類也隨之 增多,如具有更高處理性能和大容量記憶體的微處理器。同時,隨著 處理量的增加和數據處理速度的提高,電路要求有更高速率的 IC 處理 晶片。當 IC 運作時,大量寬頻雜訊就隨之產生,並透過 AC 電源線發 射出去。 切換式電源轉換器的輸出雜訊會由兩種成分所組成,漣波和雜 訊。漣波的存在是因切換轉換器的操作週期的一部分期間,能量從輸 入端轉移到輸出端,此時輸出電壓略有增加。當無能量轉移到輸出端 的時間間隔期間,負載電流由輸出電容和電感中儲存的能量所提供, 當能量被耗盡輸出電壓略有降低。漣波是低頻成分,發生在切換轉換 器的工作頻率,或它們的某個倍數。

17 雜訊是由很多變數產生,比起漣波很難預測。它是發生在切換式 轉換器內部

di/dt

的大變化,導致寄生電感的振盪造成。雜訊的頻率 比起漣波是高的多,最多可以到幾十 MHz 甚至高過 100MHz。雜訊發生 在切換式轉換器中動作的時間,因此,雜訊要被疊加在漣波波形之上 [9],如圖 2-7。 圖 2-7 漣波(Ripple)和雜訊(Noise)18

第三章

實驗方法與結果分析

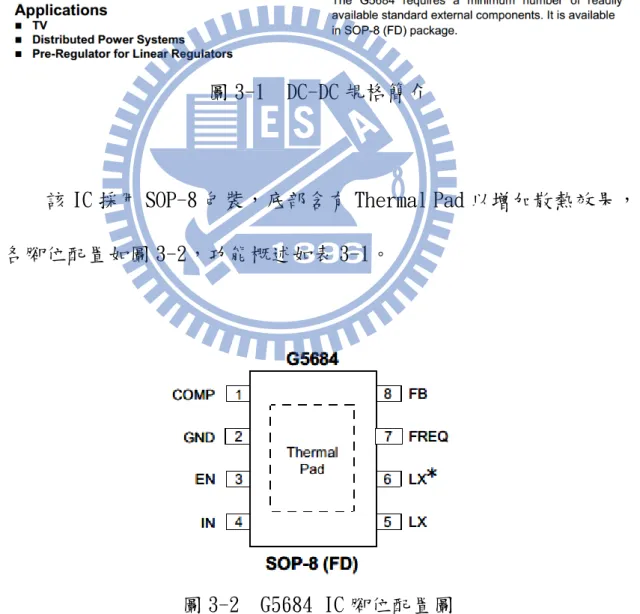

3.1 實驗電路與佈局 由上章節得知,切換式電壓轉換器在輸出端會產生漣波和雜訊, 如何抑制漣波使其符合 IC 電壓規格並降低雜訊對系統的影響是一重 要課題。本論文主要探討 Step Down DC-DC 的切換頻率對其輸出電壓 的影響。 3.1.1 Step-Down DC-DC Converter 要探討頻率對輸出電壓的影響,我們選用工作週期固定但切換頻 率可調整的 PFM 模式的 DC-DC Controller,此次實驗使用“致新科 技"公司所生產,型號 G5684 的 IC,該 IC 可提供 4A 的輸出電流, 3V~5.5V 的輸入電壓,可調整的輸出電壓,PWM 工作週期固定,切換頻 率範圍可從 300kHz 到 1.4MHz,圖 3-1 為規格書簡介。19

圖 3-1 DC-DC 規格簡介

該 IC 採用 SOP-8 包裝,底部含有 Thermal Pad 以增加散熱效果, 各腳位配置如圖 3-2,功能概述如表 3-1。

20

表 3-1 各腳位功能概述

3.1.2 實驗電路解析

實驗電路如圖 3-3,使用 Switching power supply 將交流市電轉

換成直流 5V 電壓,提供給 G5684 IC。EN 腳位可容許 VIN+0.3V 的最大

電壓,此腳位直接與輸入電壓 5V 共用,不另作分壓處理。COMP 腳位 是補償電路的 RC 結構,FREQ 腳位依搭配電阻調整切換頻率。

21

輸出電壓依電壓轉換公式(3-1),計算出輸出電壓所需搭配的電阻 R1 和 R2 阻值。輸出端依規格書建議放置兩顆 22μF 積層陶瓷電容 (Multi-layer Ceramic Capacitor, MLCC)做穩壓。

⎟ ⎠ ⎞ ⎜ ⎝ ⎛ + × = 2 1 1 8 . 0 R R Vout (3-1) 表 3-2 列出 R1、R2 的建議值。表 3-3 列出 FREQ 腳位選擇切換頻率所 需搭配的電阻值和對應的電感感值。 VOUT (V) R1(kΩ) R2(kΩ) 1.1 7.5 20 1.2 10 20 1.5 13 15 1.8 30 24 2.5 51 24 3.3 75 24 表 3-2 輸出電壓的建議搭配阻值

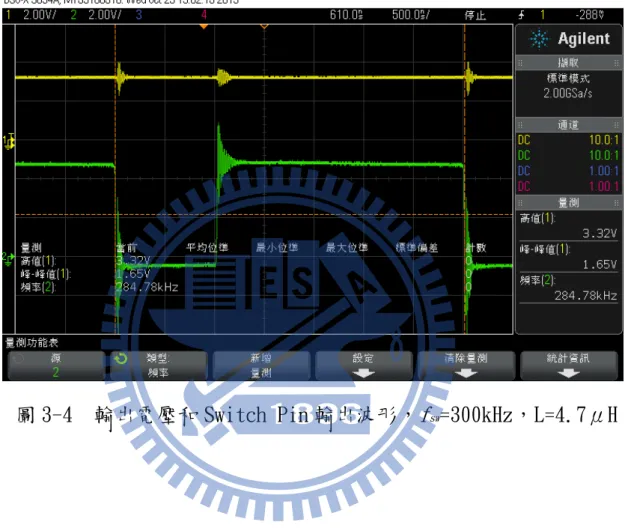

22 VOUT (V) L (µH) FSW (kHz) COUT (µF) 3.3 4.7 300 22//22 MLCC 3.3 2.2 600 22//22 MLCC 3.3 1.5 1000 22//22 MLCC 3.3 1 1400 22//22 MLCC 表 3-3 切換頻率和電感建議值 3.2 Step-Down DC-DC 切換頻率對 Ripple 的影響 由式(2-10)可知,Δ

v

out與切換頻率的平方成反比,所以我們可改 變電路上 FREQ 腳位阻值和規格書所建議的電感感值來驗證。輸出電壓 和漣波量測實驗電路 C31 位置,切換頻率可由量測 IC Pin5,6 switch pin 的輸出得到,結果如下:圖 3-4 是切換頻率 300kHz,電感感值 4.7μH 的輸出電壓和 Switch Pin 輸出波形;圖 3-5 是切換頻率 300kHz 時的輸出電壓漣波;圖 3-6 是切換頻率 1000kHz,電感感值 1.5μH 的 輸出電壓和 Switch Pin 輸出波形;圖 3-7 是切換頻率 1000kHz 時的輸 出電壓漣波。 圖 3-4 和 3-6 的輸出電壓是 DC 準位,圖 3-5 和圖 3-7 的輸出電壓23

漣波是量測該點 AC 訊號,可發現兩者都會受震鈴(Ringing)影響,皆 有疊加的雜訊在其輸出端出現。

24

圖 3-5 輸出電壓漣波波形,

f

sw=300kHz,L=4.7μH25 圖 3-7 輸出電壓漣波波形,

f

sw=1000kHz,L=1.5μH Step-Down DC-DC Converter 加快切換頻率可選用小電感感值, 相對地縮小電源系統佔用 PCB 的面積,由圖 3-5:峰-峰值為 29mV 和 圖 3-7:峰-峰值為 14mV,可看出輸出電壓漣波確實隨著切換頻率提高 而減小。 在現今電子行動裝置崛起,走向輕薄化發展的時候,此應用看似 切合需求,但觀察圖 3-4 和 3-6,可發現切換頻率在高低位準急遽變 化處會產生 ringing,這是由於di/dt

的大變化導致包含 IC 內部電路 和走線,與外部 PCB 電路零件和走線的寄生電容與寄生電感形成等效 的 RLC 迴路,所產生固定的共振頻率[10]。由上圖可明顯看出,此共 振頻率會疊加在輸出電壓和漣波波形上,隨著切換頻率提高疊加的次26 數也隨之增多,當此雜訊隨電源進入系統各處會導致不必要的電磁輻 射干擾。 圖 3-8 為

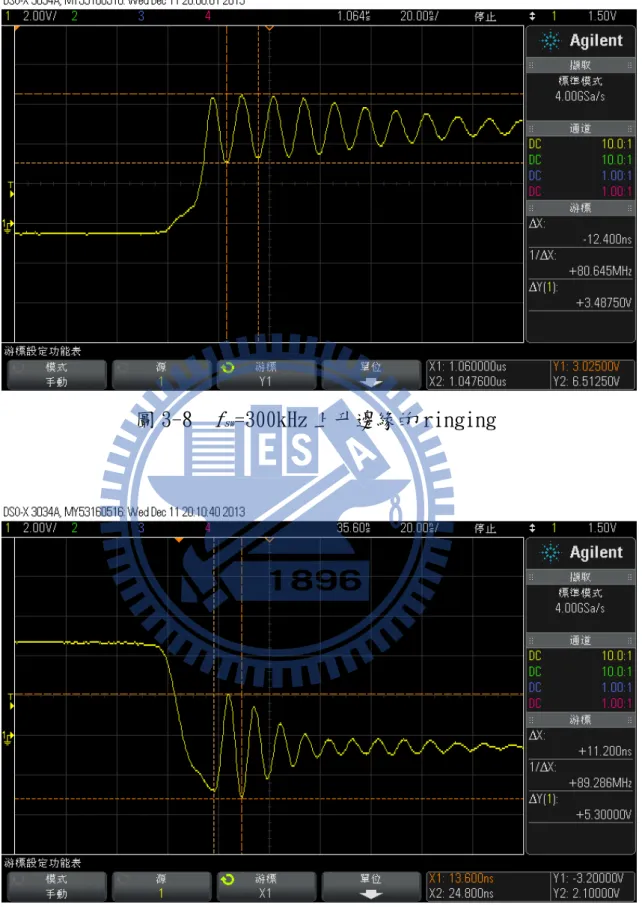

f

sw=300kHz 時,上升邊緣的 ringing 展開波形;圖 3-9 為f

sw=300kHz 時,下降邊緣的 ringing 展開波形;圖 3-11 為f

sw=1000kHz 時,上升邊緣的 ringing 展開波形;圖 3-12 為f

sw=1000kHz 時,下降 邊緣的 ringing 展開波形。四個 ringing 的震盪頻率約在 85MHz,振 幅也未有明顯變化,可證實切換頻率f

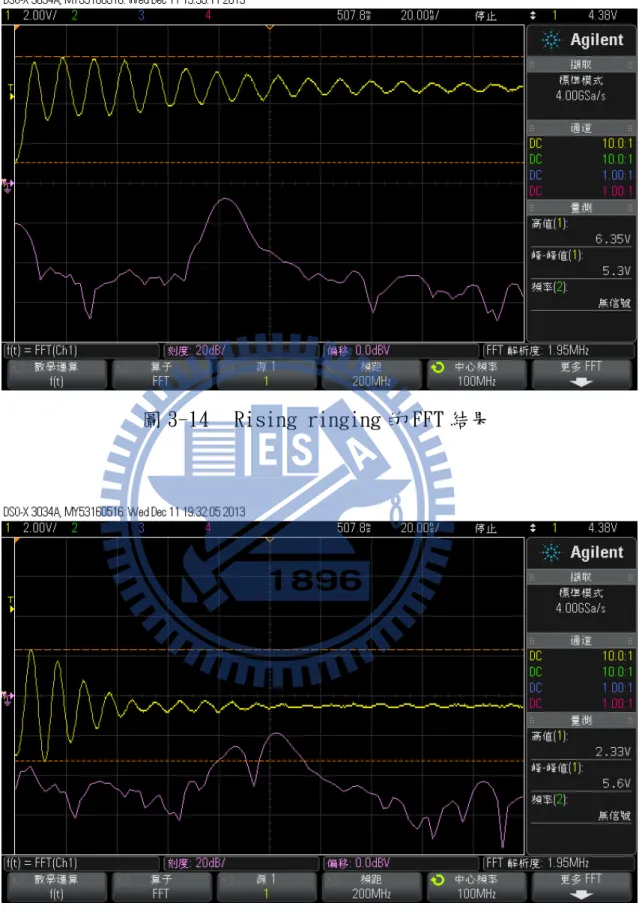

sw對 ringing 並無影響,只與上 段提到的因素有關。進而觀察圖 3-10 和 3-13,將該波形做 FFT 後, 可發現在中心頻率為 100MHz,頻距為 200MHz 的圖形中,在頻率約 80MHz 處之前的頻段,dB 值比其他頻率點都高。進一步觀察圖 3-14 rising 和圖 3-15 falling 的個別的頻譜分佈,兩者並非完全相同,rising 的頻譜分佈在 85MHz 附近達到最高,falling 的頻譜分佈在 105MHz 附 近達到最高,85MHz 附近次高,此兩頻率點在 EMI 測試時必會出現。 隨著切換頻率提高,固定時間內的 ringing 震盪次數變多,造成 FFT 後的波形可明顯看出更多雜訊疊加。我們可推測在實際量測 EMI 結果 時,此電源雜訊在此頻段所造成的干擾必會高於其他頻段,甚至產生 驗證超出 EMI 標準的情況。27

圖 3-8

f

sw=300kHz 上升邊緣的 ringing28

圖 3-10

f

sw=300kHz ringing 的 FFT 結果29

圖 3-12

f

sw=1000kHz 下降邊緣的 ringing30

圖 3-14 Rising ringing 的 FFT 結果

31 Ringing 為阻尼震盪波形,且週期性的發生於波形切換瞬間,故 能分佈頻寬甚廣,個別譜線寬度亦較大。與時脈訊號所產生頻譜不同, 時脈訊號為一週期性函數,經由 FFT 後的結果是多個脈衝分布,以主 頻強度最大,倍頻上升,強度依序減輕,通常針對主頻做壓抑,其他 倍頻也會跟著下降。 3.3 增加消除高頻雜訊的電感對 EMI 的影響 上節說明了調高切換頻率所帶來的優點,並點出實際上系統層面 會面臨的問題,如何抑制雜訊進入系統造成干擾是一重要課題。當電 源雜訊進入系統產生不必要的電磁輻射干擾時,如果未在研發設計階 段就加入相對應的對策,一般採用圍堵的方式防止電磁輻射,加導電 泡棉、貼銅箔等方法,如不幸需修改 layout,所造成成本上升和時程 延誤更是得不償失。 3.3.1 改變切換頻率對 EMI 量測結果的影響 圖 3-16 和圖 3-17 分別是切換頻率 300kHz,電感感值 4.7μH 的

32 垂直和水平極化 EMI 量測結果。圖 3-18 和圖 3-19 分別是切換頻率 1000kHz,電感感值 1.5μH 的垂直和水平極化 EMI 量測結果。比較兩 組 EMI 數據可發現,隨著切換頻率提高,如同圖 3-10 和 3-13 FFT 的 頻譜分佈,ringing 頻率(85MHz 左右)所測得的結果都是最糟的, 100MHz 前的頻段形成很多的脈衝,垂直極化的許多頻率甚至超過標準 甚多,雜訊造成的電磁輻射結果增強很多,如何減輕此現象是本節所 要討論的重點。 一般 DC-DC Converter 輸出端的電感和電容是作為儲能功用,對 高頻雜訊幾乎沒有阻擋的作用。為了降低高頻雜訊,我們可加上一 Ferrite Bead,並改變擺放位置來觀察實際量測結果。

33

34

35

36

37

3.3.2 Ferrite Bead 擺放位置對 EMI 量測結果的影響

現今消除 EMI 干擾的元件多應用鐵氧體磁珠(Ferrite Bead),它 是一種抗干擾組件,廉價、易用,濾除高頻雜訊效果顯著。我們選用 “奇力新電子"公司的 Ferrite Bead,型號:PBY201209T-600Y-N, 表 3-4 為該顆 Bead 的電子特性,圖 3-20 為該顆 Bead 的阻抗特性圖。

38 圖 3-20 Ferrite Bead 的阻抗特性圖 圖 3-20 顯示了 ZRX 的特性曲線,15MHz 以下的響應是電感性的, Z 和 X 是幾乎相等的。在此區域內,Bead 是一個非常高 Q 值電感;X 和 R 在大約 50MHz 處交叉,在這個頻率,儲存的能量和消耗的能量可 互相匹配。從 50MHz 以上至 750MHz 處的峰值阻抗,感抗下降到零,此 時阻抗變得完全是電阻性的。從峰值阻抗在 750MHz 到之後的頻率, Bead 變為電容導納。 圖 3-21 為電壓輸出端在加入 bead 後,bead 前後的波形比較圖。 channel 1 為 bead 後的結果;channel 2 為 bead 前的結果,比較其峰 -峰值的結果有下降,可推測在加入 bead 後確實可降低 ringing 所造 成的干擾。以下圖 3-22 至圖 3-27 為加入 bead 的 EMI 測量結果,我們

39

分別改變 bead 的位置,由電壓輸出端、距離電壓輸出端 5 公分處、負 載端,三個位置觀察其 EMI 測量結果。

40

圖 3-22

f

sw=1000kHz,L=1.5μH,電壓輸出端41

圖 3-23

f

sw=1000kHz,L=1.5μH,電壓輸出端42

圖 3-24

f

sw=1000kHz,L=1.5μH,電壓輸出端距離 5cm 處43

圖 3-25

f

sw=1000kHz,L=1.5μH,電壓輸出端距離 5cm 處44

圖 3-26

f

sw=1000kHz,L=1.5μH,負載端45

圖 3-27

f

sw=1000kHz,L=1.5μH,負載端46 比較上圖結果可發現,當 bead 愈接近輸出電壓位置,電磁輻射量 測結果的基底在高頻端有被壓抑下來的現象,表 3-5 和 3-6 取 100MHz 前後幾個表現較差的頻率點與未加 bead 的結果做比較,加了 bead 的 結果比起未加的 bead 的結果皆有改善,加在電壓輸出端的結果在某幾 個頻率點下比起負載端有更好的表現。由此可知,隨著切換頻率提高 所 帶 來 的 雜 訊 干 擾 , 我 們 在 輸 出 電 壓 端 加 上 bead 可 有 效 抑 制 Step-Down DC-DC Converter 內部所產生雜訊干擾。

47 頻率點 (MHz) 無 Ferrite Bead 的量測 值(dB) Ferrite Bead 位置 電壓輸出端 的量測值(dB) 電壓輸出端 +5cm 的量測值 (dB) 負載端 的量測值(dB) 39.450 -3.92註 1 -8.000 -8.000 -8.950 65.100 2.910 0.380 -0.080 0.260 82.650 8.330 4.630 4.81註 2 6.820 102.225 0.760 1.230 -0.550 1.620 註 1:38.775MHz 的量測結果 註 2:84.000MHz 的量測結果 表 3-5 不同 bead 擺放位置的垂直極化量測值比較表

48 頻率點 (MHz) 無 Ferrite Bead 的量測 值(dB) Ferrite Bead 位置 電壓輸出端 的量測值(dB) 電壓輸出端 +5cm 的量測值 (dB) 負載端 的量測值(dB) 38.775 -9.7 -17.62 -17.55 -15.34 67.8 -11.07 -11.86註 2 -12.64 -11.56 82.65 -2.78 -7.57 -7.69 -4.49 102.225 -10.440註 1 -11.85 -13.84 -12.14 註 1:99.525MHz 的量測結果 註 2:68.475MHz 的量測結果 表 3-6 不同 bead 擺放位置的水平極化量測值比較表

49

第四章

結論

現今電子產品的電源系統使用 Switching Regulator 提供给系統 的低直流電壓是一種趨勢。手持裝置產品大多搭載容量有限的電池, 對 電 源 消 耗 可 謂 錙 銖 必 較 , 降 低 耗 電 量 也 就 是 延 長 待 機 時 間 。 Switching Regulator 不單具有比 Linear Regulator 較好的效率,提 高頻率也能縮小電感的體積進而縮小 PCB 的使用面積與降低電壓漣波 優勢。但經由上述實驗可以看出,提高切換頻率的同時,由於其電壓 和電流波形的非線性性質,也會引入一些雜訊的干擾。如果系統對漣 波和雜訊很敏感,在產品開發初期就應先考量到電源系統的穩定,避 免後期有不可預期的結果。 尤其現在有畫面顯示的裝置,如手機、平版、筆記型電腦等,幾 乎人手一機,如雜訊經由電源系統進入,干擾到後端訊號處理,造成 訊號解析有誤,消費者經由畫面可輕易發現品質不良,畫面抖動,水 波紋等,造成對產品甚至品牌的不信任感,影響可謂深遠。 經由本實驗,提供產品開發人員一個在初期就可應用的方法。利 用最小的 PCB 面積和花費相對低廉的方法,避免後續的 EMI 問題產生。 在 Switching Regulator 的輸出電壓端再預留一組可抑制 ringing 現50 象的 ferrite bead,比起放置在負載端得到的效果更加明顯。從源頭 進行雜訊的壓抑,避免雜訊擴散到後端系統,造成更多電磁輻射干擾, 此時所要壓抑改善此干擾問題所花費的時間和成本,是天壤之別。如 何在提升電源穩定度與避免電磁干擾的課題中,選擇適合的切換頻率 和 bead 是設計人員的一大課題與挑戰。

51

參考文獻

[1] Clayton R. Paul, Second Edition, Introduction to Electromagnetic Compatibility, John Wiley & Sons, Inc., 2006.

[2] 楊克俊 編著,陳一鋒 校訂,電磁相容原理與設計技術,全華科技 圖書,2006 年 10 月。 [3] George C. Chryssis 著,梁適安 譯,高頻交換式電源供應器原理與 設計,麥格羅希爾出版,全華發行,1995。 [4] 蘇家弘,「交換電壓調節器」,http://www.digi-mods.com/knsm071/pwm.doc [5] 林睿鵬,「DC-DC 轉換電路拓樸初探」,零組件雜誌,2006 年 5 月。

[6] Application Report SLVA057, “Understanding Buck Power Stages in Switchmode Power Supplies," TI Inc., March 1999.

[7] Inderpreet Kour, Navdeep Kaur, “Real Time Ripple Analysis of Buck DC-DC Converter," International Journal of Engineering Research and Applications, Vol. 2, Issue 3, pp.2531-2537, May-Jun 2012.

[8] Application Note AN-1144, “Measuring Output Ripple and Switching Transients in Switching Regulators," Analog Devices Inc.

[9] Application Note AN-1105, “Ripple & Noise Measurements," Excelsys Technologies Ltd., 2011.

[10]Keong W. Kam, David Pommerenke, Cheung-Wei Lam, Robert Steinfeld, “EMC Guideline for Synchronous Buck Converter Design,"

52 Symposium, pp47-52, August 2009. [11]蔡政憲,「防護線對高速數位信號在板級的電磁干擾影響探討」, 國立交通大學電機與控制學程碩士論文,2009。 [12]楊文琳,「利用去耦合電容與 RC 終端改善印刷電路板電源切換雜 訊」,國立交通大學電信工程系碩士論文,2001。