國 立 交 通 大 學

電信工程研究所

碩 士 論 文

縮小化功率放大器輸出級平面式巴倫濾波器

Miniaturized planar balun filter for power amplifier

output stage

縮小化功率放大器輸出級平面式巴倫濾波器

Miniaturized planar balun filter for power amplifier

output stage

研 究 生 : 林士峰 Student :Shih-Feng Lin

指導教授 : 張志揚 博士 Advisor : Dr. Chi-Yang Chang

國 立 交 通 大 學

電信工程研究所

碩 士 論 文

A Thesis

Submitted to Institute of Communication Engineering College of Electrical and Computer Engineering

National Chiao Tung University In Partial Fulfillment of the Requirements

For the Degree of Master of Science in

Communication Engineering July 2010

Hsinchu, Taiwan, Republic of China

縮小化功率放大器輸出級平面式巴倫濾波器

研究生 : 林士峰 指導教授 : 張志揚 博士

國 立 交 通 大 學 電 信 工 程 研 究 所

摘 要

本論文為設計一個巴倫(balance to unbalance transformer)作為功率放大 器的輸出級,對於要把一個功率放大器的平衡訊號轉換為單端訊號的輸出級裝置 來說,傳統的方法均為使用一平面電感式變壓器形式之輸出級,其中中央抽頭式 變壓器型式易有高磁場耦合,在單晶片系統上,不論是 VCO 與 PA 都會產生磁場耦 合的雜訊效應,例如互調訊號(inter-modulation signal)、注入鎖定(injection lock)、 注入牽引(injection pulling)等干擾。為了解決這樣的情況,於是我們朝著巴倫式的 輸出級作研究,以公式分析並推演出不對稱耦合線(asymmetric coupled line)所

Miniaturized planar balun filter for power amplifier

output stage

Student: Shih-Feng Lin Advisor: Dr. Chi-Yang Chang

Institute of Communication Engineering

National Chiao Tung University

Abstract

This thesis introduces a design of balun (balance to unbalance transformer) as an output of a power amplifier. A conventional power amplifier output network uses a center-tapped spiral transformer to transform the balanced signal to a single ended signal with specific impedance transformation ratio. The center-tapped spiral transformer always comes with a strong magnetic coupling with nearby spiral inductors. For the SOC (System On Chip), both VCO and power amplifier are interfered by noise from magnetic coupling, such as inter-modulation signal, injection lock, injection pulling. To solve this problem, a novel balun filter for power amplifier output network is proposed in this thesis. An analytical method is developed to calculate the width and gap of the asymmetric coupled-line with respect to balun filter specifications. A folded layout is applied to meet the smaller size. Measuring is also a critical issue in the project. The proposed balun filter can be applied to any substrate at any frequency.

Acknowledgement

誌謝

時光荏苒,兩年的時光匆匆流縱,碩士生涯雖有崎嶇至此也算圓滿結 束,對於我的指導教授張志揚博士,心中只有滿溢的感謝,老師對於研究 的專業,總是能夠在我研究遭遇困難及瓶頸時給予我最精準最又最精闢的 指導,處事踏實又懂得享受生活的人生哲學,老師給我們研究生做了一個 最好的榜樣;孟慶宗博士則是我人生中另一個貴人,從專題開始接受孟教 授的指導,著實受益良多,並且在我人生迷失方向、心急迷惘的時候,孟 教授大方且有力的幫忙我、協助我,讓我能重新回到軌道,我能從交大電 信研究所畢業,要特別感謝張教授和孟教授。同時也感謝孟教授能來作為 口試委員,還有同是口試委員的邱煥凱教授和鍾世忠教授,各位口試委員 都以精準的眼光和專業能力給了研究上的和論文上的建議,讓我的論文能 夠更加的完備,很感謝他們。 對於能成為 916 實驗室的一員我滿懷感謝,實驗室的學長姐、學弟妹 和同學們都是我不論研究上還是生活上的好夥伴,博班學長益廷、昀緯、 哲慶、建育、正憲;96 級學長姐耿宏、忠傑、如屏、殿靖;98 級學弟妹 鵬達、懿萱、維欣、宛蓉;97 級同學揚達、聖智、姵潔、德裕。有了大家 在,讓我的研究生活精彩非凡,特別感謝益廷和昀緯學長,以他們深厚的 知識與經驗許多次的為我解惑。希望大家都還能時常相聚。還要謝謝 red目錄

摘要 ... i Abstract ... ii 誌謝 ... iii 目錄 ... iv 圖目錄 ... vi 表目錄 ... viii Chapter 1 簡介 ... 1 1.1 研究動機與簡介 ... 1 1.2 文獻探討 ... 2 Chapter 2 微帶線與耦合線 ... 10 2.1 微帶線平行耦合線的特性 ... 10 2.1.1 對稱耦合線的奇模電容與偶模電容 ... 12 2.1.2 奇模電容與偶模電容與阻抗之關係 ... 15 2.2 單線與耦合線的雜散電容 ... 16 2.2.1 單條傳輸線的雜散電容 ... 17 2.2.2 耦合傳輸線的雜散電容 ... 18 Chapter 3 平面式巴倫輸出級 ... 22 3.1 簡介 ... 22 3.2 巴倫濾波器設計理論 ... 23 3.2.1 主要電路架構 ... 23 3.2.2 等效電路推演 ... 25 3.3 電路模擬結果 ... 293.4 量測與佈局 ... 38 3.5 Rogers RO4003 板材的實作 ... 40 Chapter 4 結論與未來工作 ... 46 4.1 結論 ... 46 4.2 未來工作 ... 46 參考文獻 ... 48

圖目錄

圖 1.1 (a) SiGe 功率級之輸出端變壓器匹配之等效電路。(b) SiGe 功

率級之輸出端變壓器匹配之佈局。 ... 3 圖 1.2 (a) 功率級使用自耦變壓器之輸出端等效電路。(b) 輸出端自耦 變壓器之佈局,其中各對應點請參考(a)。 ... 4 圖 1.3 [3]中之 3-3.6GHz VCO,(a)等校電路,(b)佈局圖。 ... 5 圖 1.4 [4]中之 5-5.4GHz VCO,(a)等效電路,(b)佈局圖。 ... 6 圖 1.5 (a)系統方塊圖,(b)晶片佈局圖,(c)利用磨薄基板以改善電路之 間的耦合(耦合較強時輸出頻譜出現歪斜現象)。 ... 8

圖 1.6 (a) 功率放大器與 VCO 之間的耦合現象將破壞 VCO 之頻譜 (b)功率放大器與 VCO 之間的電感磁耦現象的量測情境 (將晶片切 割以消除基板耦合,因此只剩下電磁耦合) (c) (b)圖中不同距離之下之量測結果。 ... 9 圖 2.1 一段傳輸線耦合線的交互感應區電容示意圖。 ... 11 圖 2.2 對稱耦合線的(a)偶模激發 與 (b)奇模激發之電容。 ... 13 圖 2.3 對稱耦合線的電容示意圖 (a)偶模 (b)奇模。 ... 14 圖 2.4 單條微帶傳輸線的(a)電場示意圖(b)等效電容示意圖。 ... 17 圖 2.5 (a)對稱傳輸線的交互作用區,(b)-(c)偶模激發的電場分布圖與電 容示意圖(d)-(e)奇模激發的電場分布圖與電容示意圖。 ... 18 圖 3.1 功率放大器輸出端 balun 的電路基本結構。 ... 23 圖 3.2 二階阻抗轉換濾波器之電路示意圖。 ... 24 圖 3.3 此為圖 3.2 電路之響應。 ... 24 圖 3.4 二階阻抗轉換濾波器之實際等效電路。 ... 25 圖 3.5 此為圖 3.4 之等效電路。 ... 25

圖 3.6(a)耦合線之等效情況(b)單線之等效情況(c)故非對稱耦合線相當

於 a、b 並聯。 ... 26

圖 3.7 有磁牆之對稱耦合線之等效電容分布。 ... 27

圖 3.8 等效電路 θ≠90 度時的情形。 ... 27

圖 3.9 計算諧振腔的斜率參數。 ... 28

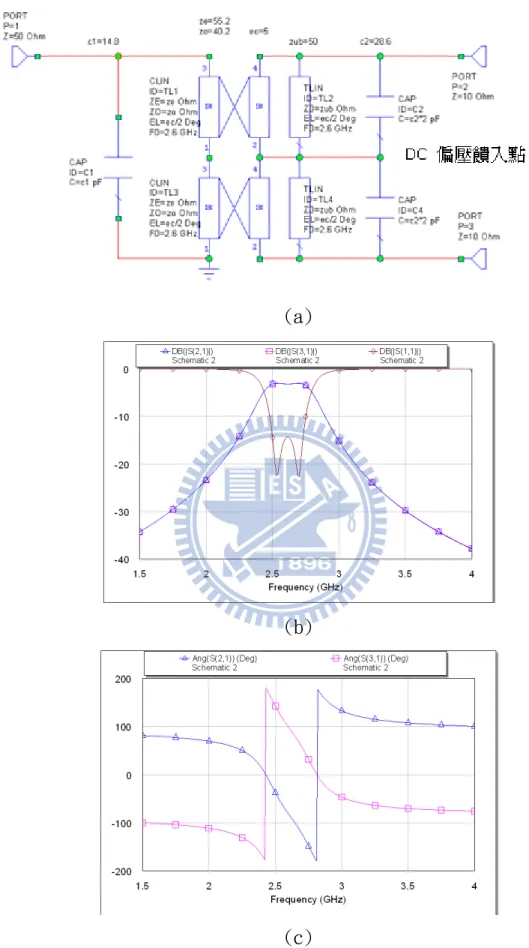

圖 3.10 此 Balun 的響應(a)DC Bias open circuit(b)Amplitude 響應(c) 相位響應。 ... 30

圖 3.11 此 Balun 的響應(a)DC Bias short circuit(b)amplitude 響應(c) 相位響應。 ... 31

圖 3.12 (a)sonnet 所模擬之 coupled line balun 之電路示意圖(b)電磁 模擬軟體輸出 SNP 檔由 ADS 匯入之電路(c)balun 之 amplitude 與相位響應。 ... 33

圖 3.13 (a) coupled line balun 使用標準 0.18μm CMOS 製程 metal 6 金屬(b)balun 的 amplitude 與相位響應。 ... 34

圖 3.14 (a)HFSS 模擬 meander coupled line balun(b)響應圖。 ... 36

圖 3.15 (a)改良的 coupled line balun(b)amplitude 與相位響應。 .. 37

圖 3.16 預想之 Balun 佈局圖。 ... 38

圖 3.17 Balun 輸出級取代傳統變壓器式輸出級。 ... 39

圖 3.18 balun 量測磁場耦合量示意圖。 ... 40

表目錄

Chapter 1

簡介

1.1 研究動機與簡介

近幾年來,CMOS 製程技術被極為有效的廣泛應用於無線通訊 IC 電路 的設計,當然尺寸的考量與成本是其中一個優勢,但它的高度整合的特性 才是最大的好處,能在相同的製程上整合各種數位與類比電路以實現『系 統單晶片(SOC)』的目標,目前技術已達到單晶片整合基頻、射頻、記憶 體、電源管理…等電路。但是在射頻/微波晶片之中,若想將功率放大器 放入晶片中,則整合上會遇到許多困難,電路間的干擾會變得非常的嚴重, 因為整個射頻接收機被整合在一起的緣故,尤其是功率放大器,它的電流 很大產生的電磁、基板干擾也大,因此對其他電路如低雜訊放大器(LNA)、 混頻器(MIXER)、尤其是壓控震盪器(VCO)等產生干擾,例如互調訊號 (inter-modulation signal) 、 注 入 鎖 定 (injection lock) 、 注 入 牽 引 (injection pulling)等干擾。現今,因為傳統 CMOS 製程技術下之功率電晶體大都是操作在低電壓與 高電流的狀況之下,因而其輸出阻抗很低。傳統常見的功率放大器輸出級

防治方法截斷基板雜訊的耦合,磁場耦合仍是沒有辦法降低。 有鑑於上面所述的理由,這個研究將著重在功率放大器輸出級平面式 中央抽頭變壓器與周邊電感之磁場互耦現象的改善。在本論文研究中,我 們將設計一種新的輸出 balun 電路,具有傳統平面式中央抽頭輸出變壓器 的所有功能,即: 阻抗匹配、DC choke、與推挽到單端之轉換等三項功能, 並且能有效改善與周邊電感(尤其是壓控振盪器諧振腔之電感)之耦合。

1.2 文獻探討

首先先討論常見的功率放大器的輸出端,即為一中央抽頭變壓器。圖 1-1,為一傳統 CMOS 或 SiGe 功率放大器輸出端之匹配網路設計[1],從圖 中可以看出它是二個渦狀電感(spiral inductor)纏繞在一起的電路。圖 1-2,則為最近有人提出的使用自耦變壓器(autotransformer)方式形成的 輸出端匹配網路[2],同樣也是數個渦狀電感纏繞在一起而成。如果觀察 圖 1-3[3]及 1-4[4],這是一個傳統 CMOS 的壓控震盪器(VCO),整個震盪 器最醒目(最佔面積)的部份也是由數個渦狀電感(spiral inductor)纏繞 在一起的電路,當將圖 1-1 或 1-2 與圖 1-3 或 1-4 兩種電路擠在同一晶片 之 上 , 無 可 避 免 的 一 定 會 產 生 極 強 的磁 場 互 耦 。 於 是 例 如 互 調 訊 號 (inter-modulation signal) 、 注 入 鎖 定 (injection lock) 、 注 入 牽 引 (injection pulling)等干擾均會出現甚而導致 VCO 失效。(a)

圖 1.1 (a) SiGe 功率級之輸出端變壓器匹配之等效電路。(b) SiGe 功 率級之輸出端變壓器匹配之佈局。

(a)

圖 1.2 (a) 功率級使用自耦變壓器之輸出端等效電路。(b) 輸出端 自耦變壓器之佈局,其中各對應點請參考(a)。

(a)

(a) (b) 圖 1-4 [4]中之 5-5.4GHz VCO,(a)等效電路,(b)佈局圖。 至於二種電路之間的相關影響,概述如下: [5]中敘述了一個 5.8GHz SiGe 收發機系統,圖 1-5(a)、(b)顯示其系 統架構圖與晶片佈局,既使在佈局上把功率放大器(測試功率為 13dBm,功

率並不算很大)與壓控震盪器放在晶片最遠的兩個角落,但其輸出頻譜仍 出現歪斜現象如圖 1-5(c)所示。

(a)

基板厚 300μm 基板厚 127μm (c) 圖 1.5 (a)系統方塊圖,(b)晶片佈局圖,(c)利用磨薄基板以改善電 路之間的耦合(耦合較強時輸出頻譜出現歪斜現象)。 另外有一篇探討有關功率放大器與 VCO 之間電感相互耦合的論文[6], 基本上作者利用量測的方法,直接量測二組電感之間的耦合,為了觀察磁 耦效應文中並將基板切開以防止基板耦合,再以量測的方式測量兩組線圈 之間不同距離下的耦合,圖 2-6 顯示其量測結果。 (a)

(b)

(c)

圖 1.6 (a) 功率放大器與 VCO 之間的耦合現象將破壞 VCO 之頻譜 (b) 功率放大器與 VCO 之間的電感磁耦現象的量測情境 (將晶片切 割以消除基板耦合,因此只剩下電磁耦合)

Chapter 2

微帶線與耦合線

在微波頻率中使用的傳輸線可簡單分為兩個分類:TEM 模(或準 TEM 模) 傳輸線與非 TEM 模傳輸線,當訊號傳導在一個微帶結構,若電磁場是分佈 在一個不均勻的金屬中,則傳輸模式為準 TEM 模。對於要測定一個對稱的 TEM 或準 TEM 模耦合傳輸線中的一些重要的特性(例如特性阻抗、相位速度) 我們可以將範圍縮小,探討耦合線模組中跟基板還有激發模態的電容即可。 而且 TEM 模(或準 TEM 模)之傳輸線的導體損耗可以由特性阻抗和一些幾何 的參數決定,本章討論的是一段微帶線對稱平行耦合線。2.1 微帶線平行耦合線的特性

傳輸線之間的耦合可以用自身電容與相互電容來解釋,因此我們首先 探討耦合傳輸線的等效電容。圖 2.1 為一段耦合傳輸線共用一段地的相關 電容示意圖,若Q 和Q 為導體 1 和導體 2 電荷量,V 和V 為導體 1 和導體 2 之電壓,其中Q 跟Q 可以用下列公式表示: Q C V C V V C C V C V (2.1) Q C V V C V C V C C V (2.2)Ground

圖 2.1 一段傳輸線耦合線的交互感應區電容示意圖。 兩條傳輸線耦合線的電容矩陣表示為: C CC CC (2.3) C 與C 是被定義為傳輸線 1 和傳輸線 2 的自身電容,電容矩陣也表 示了兩條傳輸線之間電荷與電壓的關係: Q C V C V (2.4) Q C V C V (2.5)耦合線的電感矩陣則給定為: L µ C (2.7) 其中 C 為在標準介電常數的介質中傳輸線的電容矩陣。 2.1.1 對稱耦合線的奇模電容與偶模電容 對於一段對稱的耦合線,他們之間的電容矩陣可以用偶模電容和奇模 電容來表示, 偶模激發 一段均勻的耦合傳輸線交互作用區就如圖 2.2(a)所示,在此情況下,圖 2.1 中的C 被分開成兩個值為2C 的電容串聯,當偶模激發時,兩條傳輸 線是相等並同相的電位(V V V ),由於幾何結構,可以很明顯的推測 出有相同電位的兩條傳輸線也會有相同的電量,(Q Q Q ),把C 用 Q /V 表示,則(2.1)式和(2.2)式可簡化為: C C Q V C (2.8) 奇模激發 在奇模激發中,兩條傳輸線有著相等但反相的電位(V V V ), 就如圖 2.2(b)所示,如果結構是對稱的,那相等但反相的電位在兩條傳輸 線上就會產生相等但反相的電量(Q Q Q ),若將C 表示成Q /V ,

則(2.1)式和(2.2)式可簡化為:

(a)

Ground

Ca

Qo'Vo

-Qo' -Vo

2Cm

P'

2Cm

P

PP'--電牆 (短路電路)Ca

(b) 圖 2.2 對稱耦合線的(a)偶模激發 與 (b)奇模激發之電容。因此當我們知道了偶模電容和奇模電容,便可利用(3.8)式和(3.10) 式求出C 、C 跟C ,電容矩陣也可以用(3.6)式求得。在偶模激發狀態中, 中間的 PP′平面為一磁牆(開路電路)就如圖 2.3(a)所示,這樣子等效可以 有效的簡化分析耦合線的問題。而在奇模中電容的等效就像是中間有一道 電牆如圖 2.3(b)所示,這讓奇模電容的測定可以簡化為中間有電牆時的傳 輸線電容的測定。

'

PP'--開路電路

(a) (b) 圖 2.3 對稱耦合線的電容示意圖 (a)偶模 (b)奇模。2.1.2 奇模電容與偶模電容與阻抗之關係 奇模與偶模的電容與阻抗的關係則是: Z 1 v C ω β C (2.11) 和 Z 1 v C ω β o (2.12) Z 和v 分別為偶模的特性阻抗和相速,而Z 和v 則為奇模的如果 傳輸線是被放置在一段介電常數為 的均勻介質中,那麼奇模與偶模的相 速就會相等,並表示為: v v c √ (2.13) 然而,如果介質並不均勻的話,奇模與偶模的相速就會有差異出現, 如果是在不均勻介質中,相速的表示為:

v c (2.15) 其中ε 和ε 為偶模與奇模的等效介電常數,可以用下列公式測定: ε C C (2.16) 和 ε C C (2.17) 這代表了我們可以用C 和C 來代替相對介電常數,上述公式可以簡 化為: Z 1 c C C (2.18) 和 Z 1 c C C (2.19)

2.2 單線與耦合線的雜散電容

至此我們討論了耦合線一般情況的電容,但很多時候,我們必需設想 更多有關組成結構電容的要素,這幫助我們了解並分析問題。例如平面傳 輸線,總電容可以被拆成平行板和雜散電容。以下討論單條傳輸線和耦合 傳輸線的情況。2.2.1 單條傳輸線的雜散電容 單條微帶傳輸線的電場分布如圖 2.4(a)所示,由於微帶線有限的寬度, 因此場的分布不僅僅是在帶狀導體之下,也會延伸到周圍的區域,這就是 所謂的「邊緣場」。由帶狀導體之下直接產生的電容,我們所稱之為「平 行板電容」,而由邊緣場所產生的電容則稱為「雜散電容」,所有電容的可 以用圖 2.4(b)來表示,並且以公式表示成: (a)

C C 2C (2.20) C W h (2.21) C 表示平行板電容,而 C 則代表了因為微帶線邊緣所產生的雜散電容, 一旦C 知道了,則可經由(2.20)式與(2.21)式知道全部電容。相反的,如 果我們知道了一條微帶線的特性阻抗和等效介電常數,則總電容 C 就可以 用(2.22)式求得,並使用(2.20)式和(2.21)式則C 也可求得。 Z cC 1 c CC 1 c C Z (2.22) 2.2.2 耦合傳輸線的雜散電容 一個交互作用區的耦合線如圖 2.5(a)所示,圖 2.5(b)則表示了一個 偶模激發的半結構電場分布,在這種情況,PP 平面的法線電場為零,因為 此時 PP 平面為一磁牆,而偶模耦合線的電容也就可以表示為如圖 2.5(c) 所示,公式則為: C C C C (2.23) 其中C 即為(2.21)式的平行板電容,如果此耦合線的兩條線並不很窄的話, 則C 可假設為與此耦合線相同線寬之單條傳輸線的雜散電容的值。 奇模激發的電場分布圖如圖 2.5(d)所示,其中 PP 平面的切線電場值 為零,因為此時 PP 平面為一電牆,而公式為: C C C C (2.24)

(c)

(e) 圖 2.5 (a)對稱傳輸線的交互作用區,(b)-(c)偶模激發的電場分布圖與電 容示意圖(d)-(e)奇模激發的電場分布圖與電容示意圖。 其中C 代表了耦合線內側邊緣的雜散電容,當兩條導線中間的空間很小時 (S/2 跟基板厚度 h 比較起來相對很小時),內側邊緣的電場都終止於 PP 平 面,這種情況可以用圖 2.5(e)表示,公式則寫為: C C C C C C C C (2.25) 而C 雜散電容由兩個並聯電容所組成C 、C :

Chapter 3

平面式巴倫輸出級

3.1 簡介

對於在系統單晶片(System on chip)中,功率放大器與壓控震盪器的 感應線之間的磁場耦合所造成的雜訊效應,在第一章中有詳細描述,並且 提供一些目前的解決方案。其中包括如[5]將基板磨薄,並且把功率放大 器與壓控震佈局在系統單晶片中最遠的兩個角落;又如[6]的將基板裁切 出來去分析跟解決。 在本章節將介紹,不同於在基板解決磁場耦合的雜訊效應,而從更根 本的—兩個渦狀纏繞電感式輸出級的結構去著手改善,考慮原本的電感式 輸出級響應,要有阻抗匹配以及推挽至單端的功能,而其中推挽至單端很 直觀的就讓人想到巴倫(balun—balance to unbalance transformer), 所以基本架構就從平面式耦合線巴倫濾波器出發,任何電路在晶片裡,有 一項考慮因素變的特別的重要,就是尺寸大小,尤其想要把微波電路安置 在標準 0.18μm CMOS 製程是更是一項具挑戰性的研究。 理論上若能使用縮小化功率放大器輸出級平面式巴倫濾波器來取代 傳統電感式變壓器輸出級,由於耦合線巴倫濾波器並無纏繞線圈,所以並 不會產生太大的磁場耦合,也就可以解決晶片系統中因為磁場耦合而造成 的雜訊效應,若能再更進一步縮小化,讓平面式巴倫輸出級較傳統變壓器 輸出級的尺寸更小,就能再讓晶片能更有效的利用空間,以節省晶片的面 積成本。3.2 巴倫濾波器設計理論

對於我們設計的巴倫濾波器輸出級,設計規格如表 3.1: 1 頻率 2.5-2.7GHz 2 損耗 <2dB 3 相位不平衡 5 度 4 尺寸 <700μm x 1000μm 表 3.2 巴倫濾波器輸出級之設計規格。 3.2.1 主要電路架構 新的電路架構取代傳統中央抽頭變壓器方式的功率大器輸出端 的匹配電路,主要電路架構如圖 3.1 所示。 圖 3.1 功率放大器輸出端 balun 的電路基本結構。階阻抗轉換濾波器的等效電路。可以看出接地點雖不同但其模擬結果與將 來平衡式結構(圖 3.10,3.11)相去不遠。是一個簡單、易懂的初始設計。

按照濾波器理論,因為埠阻抗一邊是 50Ω、一邊是 20Ω,因此中間的 耦合線應該是非對稱耦合線(asymmetric coupled line),這樣才能達到 理想匹配。我們將會推演發展出這個濾波器的等效電路模型,以利爾後類 似電路的設計。

圖 3.2 二階阻抗轉換濾波器之電路示意圖。 初步模擬的濾波器響應圖,如圖 2-3 所示

圖 3.2 的不對稱耦合線(asymmetric coupled line)可以用圖 3.4 的電 路來實現,將耦合線中阻抗較低、線寬較寬的一邊,等效為一對稱耦合線 並聯另一段傳輸線。 圖 3.4 二階阻抗轉換濾波器之實際等效電路。 3.2.2 等效電路推演 圖 3.4 又 可 利 用 耦 合 傳 輸 線 理 論 進 一 步 形 成 含 導 納 反 轉 器 (susceptance inverter)之電路,因此可以發展出濾波器合成之理論,將 來能夠極快速的將電路初始架構計算出來。

Y Y Jtanθ (3.1) Y Y Jtanθ (3.2) 圖 3.5 之中兩個電長度為θ,特徵導納為 Y0之短路傳輸線中間夾一個 值為 J 的導納反轉器,可以等效成圖 3.4 中之對稱傳輸線,圖 3.5 為一個 二階濾波器,一旦濾波器的規格確定則可以經由計算得到其中的參數數值 ,再轉換成圖 3.4 的電路。 (a) (b) (c) 圖 3.6(a)耦合線之等效情況(b)單線之等效情況(c)故非對稱耦合線 相當於 a、b 並聯。

從圖 3.6 可以推演出,若以磁牆將非對稱耦合線中阻抗較低的一條切 開,則相當於一個對稱耦合線並聯一段傳輸線,使得等效電路成立。加入 磁牆的對稱耦合線,其中等效電容的分布如圖 3.7。 圖 2-7 有磁牆之對稱耦合線之等效電容分布。 其中C 、C′表平板電容,C 表微帶線邊緣雜散電容,C 表二微帶線之 間的 Gap capacitance,以這四種有磁牆的對稱耦合線之等效電容,可以 寫出以下公式: Y ε ε 120π C C (3.3) Y ε ε 120π C C 2C (3.4)

Θ=90 度時,Y 以及Y 發散。其中ε 和ε 為偶模與奇模的等效介 電常數。藉由 ABCD 矩陣的相等,可以求出圖 3.8 的公式,再代入圖 3.5 之等效電路,由給定的頻寬與 return loss level 可以計算出圖 2-5 中各 電路元件的電性參數,再經由YOO Y J tan θ(3.1);Y Y

J tan θ(3.2)二式可計算出奇模與偶模導納。 圖 3.9 計算諧振腔的斜率參數。 θ β l at ω ω ; β ω v (3.5) Y jωC jY cot θ jB (3.6) Y | jω C jY cot θ 0 (3.7) b ω 2 dB dω ω C 2 Y θ 2 csc θ (3.8) (3.8)式的 b 為 susceptance slope parameter。

由諧振腔的斜率參數,給定濾波器的比例頻寬 w,可以計算求出低通 濾波器雛型的參數值:g0,g1,g2,g3。

1 50 J b w g g 50 (3.9) 由上式計算出 b1 再經圖 2-9 的(1)(2)可得 Y 與 C。 1 20 J L b w g g 20 (3.10) 由上式計算出 b2 再經圖 2-9 的(1)(2)可得 Y 與 C。 J b b g g w (3.11) 由上式可以計算出 J 進而得Y , Y ,得知了Y , Y 後即可求出Z , Z , 有了Z , Z 後,即可推出在不同板材上,不對稱耦合線的各項參數,並在 模擬軟體上進行理想狀態的模擬。

3.3 電路模擬結果

(a)

(b)

(c)

圖 3.10 此 Balun 的響應(a)DC Bias open circuit(b)Amplitude 響應 (c)相位響應。

(a)

比對圖 3.10 與圖 3.11 可以發現不論 DC 偏壓饋入點是短路或開路,這 個 balun 變壓器的輸出均不受影響,無論是振幅的平衡度與相位差均有幾 近理想的表現。同時其耦合線的電長度(electrical length)只有 5o ,小 型化的效果相當好,也因此可應用在 CMOS 製程中節省成本。 在作過理想狀態的模擬後,我們就開始著手進行標準 0.18μm CMOS 製程下的尺寸設計與電磁模擬,基於縮小尺寸原則我們先以較窄較細的 coupled line 來做嘗試,結果如下: (a) (b) S4P SNP6

File="C:\Documents and Settings\lab916-105\My Documents\我 已 接 收 的 檔 案 \9-4-16simplosles.s4p"

4 1 2

3Re f S4P

SNP5

File="C:\Documents and Settings\lab916-105\My Documents\我 已 接 收 的 檔 案 \9-4-16simplosles.s4p"

4 1 2 3Ref VAR VAR1 c2=10.7 {t} c1=8 {t} EqnVar Term Term3 Z=10 Ohm Num=3 Term Term2 Z=10 Ohm Num=2 Term Term1 Z=50 Ohm Num=1 S_Param SP1 Step=0.01 GHz Stop=4 GHz Start=0.1 GHz S-PARAMETERS C C3 C=c2 pF C C1 C=c1 pF

(C)

圖 3.12 (a)sonnet 所模擬之 coupled line balun 之電路示意圖(b) 電磁模擬軟體輸出 SNP 檔由 ADS 匯入之電路(c)balun 之 amplitude 與相位

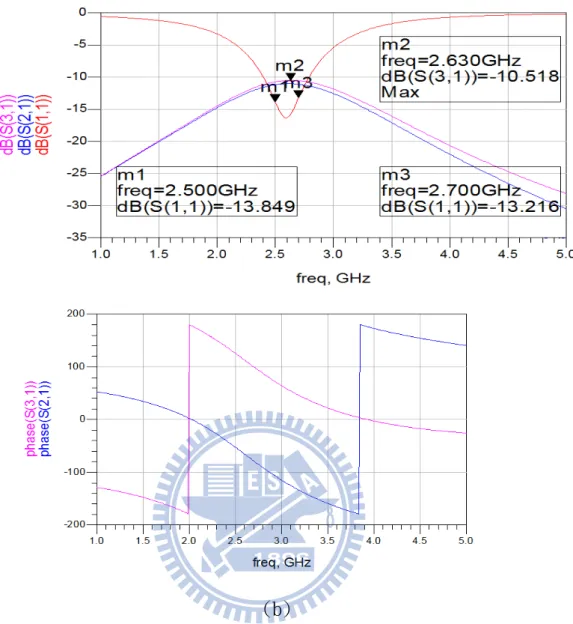

響應。 0.5 1.0 1.5 2.0 2.5 3.0 3.5 0.0 4.0 -50 -40 -30 -20 -10 -60 0 freq, GHz dB (S (1 ,1 )) m2 dB (S (2 ,1 )) m1 dB (S (3 ,1 )) m1 freq= dB(S(2,1))=-3.137 Max 2.770GHz m2 freq= dB(S(1,1))=-16.6922.630GHz 0.5 1.0 1.5 2.0 2.5 3.0 3.5 0.0 4.0 -100 0 100 -200 200 freq, GHz phas e( S( 2, 1) ) phas e( S( 3, 1) )

(a)

(b)

圖 3.13 (a) coupled line balun 使用標準 0.18μm CMOS 製程 metal 6 金屬(b)balun 的 amplitude 與相位響應。 0.5 1.0 1.5 2.0 2.5 3.0 3.5 0.0 4.0 -50 -40 -30 -20 -10 -60 0 freq, GHz dB (S (1 ,1 )) m2 dB (S (2 ,1 )) m1 dB (S (3 ,1 )) m2 freq= dB(S(1,1))=-7.5282.630GHz m1 freq= dB(S(2,1))=-9.268 Max 2.490GHz 0.5 1.0 1.5 2.0 2.5 3.0 3.5 0.0 4.0 -100 0 100 -200 200 freq, GHz ph as e( S (2 ,1) ) ph as e( S (3 ,1) )

在 Lossless 的金屬中,四個 port 都以 de-embedded 的方式從 Box 拉 至參考平面,Balun 的響應良好,不但頻寬、loss 都有達到甚至超出目標 ,相位也是一直維持 differential 的 180°相位差;但在加入了屬於標準 0.18μm CMOS 製程中 Metal 6 金屬的 loss 後,Balun 的響應開始走樣, 不但 loss 極高(高出單純因金屬非完美所造成的 loss),連原本預期的 two dips 也變成 one dip。原本預想加入的 meander 方式,不但可以縮小面積 ,又可增加 couple 量,也在 ansoft HFSS 上模擬,響應也如 sonnet 上有 loss 之 metal 6 的 balun 的響應。

(b)

圖 3.14 (a)HFSS 模擬 meander coupled line balun(b)響應圖。

為了解決此問題,我們考慮了一些因素與解決方法,也將這套理論, 推演實作在標準 0.18μm CMOS 製程以外的板材(pcb 板、ceramic 板)上, 但在其他板材上即使加上金屬 loss 也不會如標準 0.18μm CMOS 製程中加 上 metal 6 金屬 loss 那樣變化巨大,因此,可以推測出原因為 Balun 中 coupled line 的線寬太細,與基板厚度太接近,因此金屬線的毆姆耗損太 大,於是在改良之後,我們將 coupled line 尺寸調整成較寬,可以看到 如圖 的模擬,既使加上標準 0.18μm CMOS 製程 metal 6 的金屬 loss,仍 然是維持一個如預期的響應:

(a) 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 0.0 5.0 -40 -30 -20 -10 -50 0 freq, GHz dB(S( 1 ,1 )) m1 dB(S( 2 ,1 )) m2 dB(S( 3 ,1 )) m1 freq= dB(S(1,1))=-15.2332.540GHz m2 freq= dB(S(2,1))=-3.9712.650GHz 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 0.0 5.0 -100 0 100 -200 200 p has e( S (2 ,1) ) p has e (S( 3,1 ))

3.4 量測與佈局

若考慮到 balun 的佈局,由於此 coupled line balun 為不對稱 的 coupled line,故 meander 過後,細線與粗線哪一條在內哪一條在外也 是需要斟酌的;此 balun 是連接在 PA 後端的輸出級裝置,與 PA 相接的 Port 即為兩個 10Ω的 differential port,故我們將兩端是 10Ωport 的線也 就是較粗的線放內側(如圖 2-16),並以 meander 的程度來控制,控制兩個 10Ωport 最後的距離,會跟兩 PA 的兩個 differential 輸出同距,即可在 之在要接上 PA 的實際應用中,省去許多麻煩。 圖 3.16 預想之 Balun 佈局圖。 再考慮到此 balun 出來之後的量測,需著重在此 balun 比傳統平面變 壓器形式輸出級較低的磁場耦合的重點,如圖 2-16 所示 Balun 所取代的 傳統變壓器輸出級,不但效能符合預期要求,磁通量(magnetic flux)也 較傳統的輸出級低。

CMOS Power Cell

NCTU Balun with low Magnetic coupling

OUT

CMOS PA

圖 3.17 Balun 輸出級取代傳統變壓器式輸出級。

為了要比較磁場耦合量,在量測時我們將兩個 10Ω也就是接到 Power Amplifier 輸出的 port,接上 20Ω的電阻來將之 terminal,測試訊號將 從 50Ω端輸入作為 port 1,並在周圍不限定某處,擺放一個傳統平面式 變壓器輸出級 chip,它的輸出視為 port 2,依此量測 S21,即可看 Balun 式輸出級的磁場耦合量。從 chip 要拉出接電阻,或是接下針的 pad,都是 以打線的方式拉出,接上電阻或 ceramic 板的 cpw 下針電路。

圖 3.18 balun 量測磁場耦合量示意圖。

3.5 Rogers RO4003 板材的實作

為了印證縮小化功率放大器輸出級平面式巴倫濾波器理論,因此我們 在 RO4003 板子上實作,以期達到在各種板材上都能實現縮小化輸出級平 面式巴倫濾波器,電路佈局如圖 3.19:

44 20 14 15 30 40 35 20 20 44 35

PORT1

PORT2

PORT3

Via

Hole

圖 3.19 在 RO4003 板材上之電路佈局。 由於縮小化巴倫濾波器能將電路縮的很小,若製作中心頻率為 2.6GHz 的巴倫濾波器,整段耦合線將會非常短,短到無法在 RO4003 板材上實現, 所以我們將中心頻調整到 550MHz,並且將兩個差動埠設計為 50Ω,這樣 整段耦合線才夠長而不至於讓拉出要接電容的傳輸線產生不希望的耦合。 當兩個差動埠(port2,port3)各為 50Ω時,仍是要使用前面所敘述的不對 稱耦合線的計算理論,因為兩個 50Ω的差動埠會其實是串聯變 100Ω,所 以我們可以看到耦合線的寬度是設計成匹配 50Ω跟 100Ω。實際電路製作 出來為圖 3.20。圖 3.20 以 RO4003 所製作之巴倫濾波器。

由圖 3.20 我們可以看出,縮小化的巴倫實作出來後,的確是非常小 尺寸的電路,既使是 550MHz 這麼低的中心頻率,也能讓整個電路壓縮成 極小的尺寸,耦合線的寬度分別為 30mils 和 14mils,gap 寬度為 15mils, 電容選用 0603 的 20pF 和 25pF,使用 SONNET 的 EM 模擬如圖 3.21。

圖 3.21 巴倫濾波器的 EM 模擬響應。 可以看出,頻寬大約有 9%,由於用的是無損耗的金屬,故損耗在一分 二的正常損耗-3dB,相位除了在零點(由於拉傳輸線至埠 1,電感性的傳輸 線與電容共振而產生)附近有點亂掉,在通帶中則是維持完美的 180 度相 m1 freq= dB(S(1,1))=-2.999530.0MHz m2 freq= dB(S(1,1))=-3.468580.0MHz 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 0.1 1.0 -40 -30 -20 -10 0 -50 10 freq, GHz d B (S (1 ,1 )) m1m2 d B (S (2 ,1 )) d B (S (3 ,1 )) m1 freq= dB(S(1,1))=-2.999530.0MHz m2 freq= dB(S(1,1))=-3.468580.0MHz 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 0.1 1.0 -100 0 100 -200 200 freq, GHz p h a se (S (2 ,1 )) p h a se (S (3 ,1 ))

圖 3.22 實際製作電路量測之響應。

這組電路是使用 Agilent E5071B 4-port network analyzer 量測,

由於我們可以看到通帶的中心頻率是正確的落在 550MHz,S11 也看的出有 兩段下沉,但因為損耗較大,似乎快連成一個下沉了,S21 和 S31 幾乎是

相同的,相位也都在通帶中有很好的相差 180 度的表現,在零點處也如預 期有點混亂,只是損耗較大,比原本一定會有的-3dB 又再多了-3dB,除了 金屬本身的損耗,頻寬變小也是損耗增加的原因,原本 9%的頻寬變到約 6%,估計是由電容值不準確所造成的誤差,電容本身就會有的±數百分比 的誤差加上頻率影響,造成電容值不準確,以致頻寬變窄,損耗增加。

Chapter 4

結論與未來工作

4.1 結論

綜觀目前對於單系統晶片的電感型式輸出級磁場耦合極高導致雜訊之 解決方法,大多沒有完善的解決,而只是力求將之降低。而縮小化功率放 大器輸出級平面式巴倫濾波器的目標是從根本原因做起,改善幅度應該是 超越先前的解決方法,目前使用理論製作出的電路還可以符合設計規格, 但未來仍有許多改進方向可以繼續前進,以期求更乾淨的完全消除磁場耦 合效應所造成的雜訊。在 RO4003 板材上所製作的巴倫濾波器可以看出, 雖然對電容值比較敏感,但實際響應是可以達到,若能更準確的掌握電容 值,絕對可以製作出更好響應的巴倫濾波器來取代傳統渦狀電感式變壓器 輸出級。4.2 未來工作

在製作縮小化功率放大器輸出級平面式巴倫濾波器時,有些方針可以 作為未來改進的方向。首先是縮小化是永遠嫌不夠的,在晶片製程中寸土 寸金,若能愈做愈小的確是對經濟效應的一大改善;再來是電容的敏感度, 這或許要從基礎結構下手,但若能讓電路敏感度下降,則製作上必定可以更加簡易,更好掌握;在試過微帶線的巴倫製作後,共平面波導(Coplanar Waveguide)的製作方式也許更適合在晶片上製作微波電路,因為最上層的 metal 6 比起下層的 metal 1 到 metal 5 有著更好的導電度;最後則是當 真的要在單系統晶片(SOC)上銜接功率放大器,也是要做一些接軌和佈局 的考量。

參考文獻

[1] H. Seol, C. Park, D. H. Lee, M. P. and S. Hong, “A 2.4-GHz HBT power

amplifier using an on-chip transformer as an output matching network,” in

2008 International Microwave Symposium Digest, IEEE MTT-S, pp. 875–878,

June 2008.

[2] V. A. Solomko and P. Weger, “A fully integrated 3.3–3.8-GHz power amplifier

with autotransformer balun,” IEEE Trans. Microw. Theory Tech., vol. 57, no.

11, pp. 2160–2172, Nov. 2009.

[3] M. -D. Wei, S. -F. Chang, and S. -W. Huang, “An amplitude-balanced

current-reused CMOS VCO using spontaneous transconductance match technique,” IEEE Wireless and Component Letters, vol. 19, no. 6, pp. 395–397,

June 2009.

[4] J. -A. Hou and Y. -H. Wang, “A 5 GHz differential colpitts CMOS VCO using

the bottom PMOS cross-coupled current source,” IEEE Wireless and

Component Letters, vol. 19, no. 6, pp. 401–403, Oct. 2009.

[5] S. Shinjo, K. Tsutsumi, K. Nakajima, H.-O. Ueda, K. Mori, M. Hieda, J. Koide, M. Inoue, and N. Suematsu, “5.8GHz ETC SiGe-MMIC transceiver having

improved PA-VCO isolation with thin silicon substrate,” in 2006

International Microwave Symposium Digest, IEEE MTT-S, pp. 2039–2042, June

2006.

[6] S. Bronckers, G. Vandersteen, L. De Locht, M. Libois, G. Van der Plas, and Y. Rolain, ”Experimental analysis of the coupling mechanisms between a 4

GHz PPA and a 5–7 GHz LC-VCO,” IEEE Trans. on Instrumrntation and

Park, Dal Ahn, Nam-Kee Kang, Chan Sei Yoo, and Jae-Bong Lim, “A design of

the ceramic chip balun using the multilayer configuration,” IEEE Trans.

Microw. Theory Tech., vol. 49, no. 1,Jan 2001.

[7] B. Preetham Kumar, G. R. Branner and Donald G. Thomas,Jr, “A reduced size

planar balun structure for wireless microwave and RF applications,” in Proc.

Of the 38th Midwest Symposium on Circuits and Systems.pp. 526-529, August

1995.

[8] Ching-Wen Tang, Jyh-Wen Sheen, and Chi-Yang Chang, “Chip-type

LTCC-MLC balun using the stepped impedance method,” IEEE Trans.

Microw. Theory Tech., vol. 49, no. 12,Dec 2001.

[9] Shih-Ming Wang,Chin-Hsiung Chen, Chi-Yang Chang , “A study of

meandered microstrip coupler with high directivity”, in Microwave

Symposium Digest, 2003 IEEE MTT-S International, Vol. 1, 2003

[10] S. Shinjo, K. Tsutsumi, K. Nakajima, H.-O. Ueda, K. Mori, M. Hieda, J. Koide, M. Inoue, and N. Suematsu, “5.8GHz ETC SiGe-MMIC transceiver having

improved PA-VCO isolation with thin silicon substrate,” in 2006

International Microwave Symposium Digest, IEEE MTT-S, pp. 2039–2042, June

2006.

[11] S. Bronckers, G. Vandersteen, L. De Locht, M. Libois, G. Van der Plas, and Y. Rolain, ”Experimental analysis of the coupling mechanisms between a 4

![圖 1.3 [3]中之 3-3.6GHz VCO,(a)等校電路,(b)佈局圖。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8645722.193552/15.892.201.701.119.908/圖133中之336GHzVCOa等校電路b佈局圖.webp)