使用H∞和H2迴授控制法設計之全數位式耳機主動式噪音消除系統

70

0

0

全文

(2) 使用H∞和H2迴授控制法設計之全數位式耳機 主動式噪音消除系統 A Full-digital Active Noise Cancellation Headset Using H∞ and H2 Feedback Control Methods Student:Chiun-Wen, Chang. 研 究 生:張 瓊 文 博士. Advisor:Prof. Jwu-Sheng, Hu. 蕭 得 聖 博士. Prof. Te-Sheng, Hsiao. 指導教授:胡 竹 生. 國立交通大學 電機與控制工程學系 碩 士 論 文 A Thesis Submitted to Institute of Electrical and Control Engineering College of Electrical Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Master in Electrical and Control Engineering July 2008 Hsinchu, Taiwan, Republic of China. 中 華 民 國 九 十 七 年 七 月.

(3) 使用H∞和H2迴授控制法設計之全數位式耳機 主動式噪音消除系統 研究生:張. 瓊. 文. 指導教授:胡. 竹. 生. 博士. 蕭. 得. 聖. 博士. 國立交通大學電機與控制工程研究所碩士班. 摘. 要. 本論文為設計並實現主動式噪音消除耳機的全數位式迴授控制器,藉由以 強健控制中H2/H∞設計理論訂定限制條件,透過MATLAB最佳化工具模擬運算得 到符合設計的最佳化迴授控制器。此控制器結合播放聲音的數位式Sigma-Delta Modulator class-D音頻放大器以及數位麥克風,故本控制器以數位濾波器方式實 現,次一系統以verilog撰寫在FPGA內,由於此全數位系統皆實現於FPGA內部 且經驗證,故未來可以用IC模式應用在頭戴式耳機的主動式噪音消除。. i.

(4) A Full-digital Active Noise Cancellation Headset Using H∞ and H2 Feedback Control Methods. Student: Chiun-Wen Chang. Advisor: Prof. Jwu-Sheng Hu Prof. Te-Sheng Hsiao. Institute of Electrical and Control Engineering National Chiao-Tung University. ABSTRACT This thesis designs a digital feedback controller for active noise cancellation (ANC) headphones using constrained optimization problem with H2 performance criterion and H2/H∞ constraints. The optimal controller is obtained by using sequential quadratic programming tools in MATLAB. The controller for ANC is combined with digital sigma-delta modulator for class-D audio amplification and digital micorphone. Therefore the whole ANC functions are realized on an FPGA using Verilog language. Because of all the full-digital system implemented, the result can be easily customized to produce a integrated circuit (IC) .. ii.

(5) 誌. 謝. 終於還是順利走完了碩士的路程,雖然中間波折不斷幸好除了自己努力不懈還有 其他人鼎力協助最終還是完成了。 要感謝的人真的很多,首先要感謝的當然是各位撥空參加的口試委員白明憲老師 和董蘭榮老師,因為有老師的指導讓我知道自己還有哪些地方需要加強,有你們的到 來與審核才讓我順利通過考驗。 再來最應該感謝是胡竹生老師,感謝老師這兩年來的指教。在兩年研究的過程當 中常常遇到瓶頸亦或迷失,幸好老師總是指引我正確的方向,讓我可以即時轉回正確 的道路,真的由衷地謝謝老師的教導。 接下來要感謝在實驗室的學長學姊以及同學們,剛從大學畢業的我其實在各方面 的基礎都很薄弱,謝謝你們不厭其煩的從頭教起,能讓我從零成長到現在都是大家的 功勞。尤其要謝謝鏗元的幫忙,沒有妳相信今天畢業的路離我依然很遙遠。這兩年妳 除了是我的老師也是很重要的朋友,短短兩年開心的生活有很大一部分是妳帶來的。 另外還要感謝實驗室的各位夥伴,博士班學長:實做相當強悍而且歷練足夠的立 偉、學問滿溢又很幽默的宗敏、超級天才而且很愛電影的劉大、強到不行的萬能興哥、 正直老實而且脾氣超好又是引領我進到這個實驗室的妞、程式超強的大師兄;大我一 屆的學長:隊長 PLE、程式天才 Alphar、超級 high 咖弘齡;一起奮鬥的同學:永遠的 第一名阿吉、城應該已經攻下的大哥 HCY、擁有活動長宿命的 GUM、很愛打排球又 是老師愛將的 PAPA、老是愛欺負我的俊宇、甩尾一流的唐哥;實驗室的學弟:轉系 成功而且很有志向的肉鬆、愛耍色的 LUNDY、英文溜到不行的嘟嘟、可以扛起大哥 的 JUDO;當然還有大小事都包辦的實驗室助理淑伶;感謝大家陪我度過這一段難忘 的日子,謝謝你們的支持與幫助,能認識你們我真的很幸運。 研究所兩年我學到了很多,得到過去沒有而且缺乏的東西,雖然同時失去了一些 東西,但我相信我得到的遠比我失去的多。現在我終於在人生中學生生涯的終點,但 iii.

(6) 是我的學習永遠不會結束。站在人生的轉捩點我不知道下一步是什麼?我又將會在哪 裡持續我的旅程?不過我知道我依然會持續奮鬥下去,一步一步地往上爬。. iv.

(7) 目. 錄. 摘 要.............................................................................................................................i ABSTRACT..................................................................................................................ii 誌 謝...........................................................................................................................iii 目 錄............................................................................................................................ v 表 列..........................................................................................................................vii 圖 列.........................................................................................................................viii 第一章 緒論................................................................................................................ 1 1.1 研究動機............................................................................................................ 1 1.2 相關文獻及歷史發展回顧................................................................................ 2 1.3 論文主旨和架構與貢獻.................................................................................... 4 1.4 章節概要............................................................................................................ 5 第二章 理論和系統簡介............................................................................................ 6 2.1 SIGMA-DELTA MODULATION (SDM)................................................................. 6 2.1.1 SDM之發展由來........................................................................................ 6 2.1.2 SDM之概念與系統效果............................................................................ 9 2.2 H∞強健控制理論簡介..................................................................................... 10 2.3 系統簡介說明.................................................................................................. 12 2.3.1 架構簡介 .................................................................................................. 12 2.3.2 控制器設計限制 ...................................................................................... 13 第三章 迴授控制器的設計...................................................................................... 14 3.1 設計條件說明.................................................................................................. 14 3.1.1 問題描述 .................................................................................................. 14 3.1.2 條件設定說明 .......................................................................................... 15 3.2 條件求解.......................................................................................................... 18 3.2.1 設計條件轉換 .......................................................................................... 18 3.2.2 求解條件 .................................................................................................. 19 3.3 ANC頭戴式耳機的迴授控制器設計 ............................................................. 20 3.3.1 錄音平台簡介 .......................................................................................... 20 3.3.2 頻寬和權重函數的選擇 .......................................................................... 21 第四章 迴授控制器設計實例分析與模擬.............................................................. 23 4.1 受控體的定義.................................................................................................. 23 4.2 MATLAB模擬................................................................................................. 24 4.2.1 數位控制器模擬 ...................................................................................... 24 4.2.2 雜訊抑制效果模擬 .................................................................................. 28 v.

(8) 4.3 數種IIR濾波器之實現架構討論 .................................................................... 30 第五章 硬體架構與實現.......................................................................................... 33 5.1 USB介面 .......................................................................................................... 35 5.1.1 硬體介紹:EZ-USB FX .......................................................................... 36 5.1.2 軟體介紹:KeilμVision2 and EZ-USB Control Panel.......................... 36 5.2 USB1.1 5.1 聲道音效控制器 .......................................................................... 38 5.2.1 硬體介紹:SONIX SN11116.................................................................. 38 5.2.2 I2S (Inter-IC Sound)介面......................................................................... 40 5.3 FPGA核心實現 ............................................................................................... 41 5.3.1 硬體介紹:CycloneII EP2C35F484C6 Emulation Board ...................... 41 5.3.2 軟體介紹:Quartus.................................................................................. 43 5.3.3 FPGA實作 ................................................................................................ 43 5.4 數位麥克風...................................................................................................... 46 第六章 效能量測與比較.......................................................................................... 47 6.1 單頻雜訊抑制效果量測.................................................................................. 47 6.1.1 不同頻率點的雜訊抑制效果量測 .......................................................... 47 6.1.2 耳機不同配戴法的雜訊抑制效果量測 .................................................. 49 6.2 非單頻雜訊抑制效果量測.............................................................................. 52 第七章 結論.............................................................................................................. 55 7.1 研究成果.......................................................................................................... 55 7.2 未來展望.......................................................................................................... 56 參考文獻...................................................................................................................... 57. vi.

(9) 表 表 4.2.1 表 5.1.1 表 5.2.1 表 5.3.1. 列. 數位控制器係數(以 16 位元表示)............................................................ 26 USB四種傳輸模式比較............................................................................. 35 TYPE 2、3 參照SN11116 運作模式 ........................................................ 39 四階Σ-Δ調變器實作係數........................................................................ 44. vii.

(10) 圖 圖 1.2.1 圖 1.2.2 圖 1.3.1 圖 2.1.1 圖 2.1.2 圖 2.1.3 圖 2.1.4 圖 2.1.5 圖 2.1.6 圖 2.1.7 圖 2.2.1 圖 2.3.1 圖 3.1.1 圖 3.1.2 圖 3.2.1 圖 3.3.1 圖 3.3.2 圖 4.1.1 圖 4.2.1 圖 4.2.2 圖 4.2.3 圖 4.2.4 圖 4.2.5 圖 4.2.6 圖 4.2.7 圖 4.2.8 圖 4.3.1 圖 4.3.2 圖 4.3.3 圖 4.3.4 圖 5.1 圖 5.1.1 圖 5.1.2 圖 5.1.3 圖 5.2.1. 列. Paul Lueg主動式消音架構圖 ...................................................................... 2 Olson和May所提出的電子吸音器架構...................................................... 3 實作架構圖................................................................................................... 5 Delta Modulator 和功率放大方塊圖 .......................................................... 6 Delta Modulator操作機制 ............................................................................ 7 Delta Modulator的缺點 ................................................................................ 8 Inose Δ調變器 ............................................................................................ 8 (i)一階Σ-Δ調變器 (ii) 一階數位Σ-Δ調變器................................ 8 n階數位Σ-Δ調變器................................................................................. 9 一階與二階Σ-Δ輸出頻譜響應圖......................................................... 10 基本迴授架構............................................................................................. 11 ANC耳機 .................................................................................................... 12 典型反饋控制架構圖................................................................................. 14 另一種表示反饋控制的架構圖................................................................. 15 數位內部模式控制系統架構圖................................................................. 18 錄製受控體的平台方塊圖......................................................................... 20 用來設計控制器之受控體頻率響應......................................................... 21 量測受控體的平台方塊圖......................................................................... 23 設計出的數位控制器點對點畫出的頻率響應圖 .................................... 25 受控體近似後的數位控制器頻率響應圖 ................................................ 25 量化後的數位控制器頻率響應圖............................................................. 26 (a)受控體近似後的奈氏圖 (b)量化後的奈氏圖 ..................................... 27 (a)平常實驗室的噪音 (b)經過數位控制器的輸出 ................................. 28 (a)開迴路點對點的頻率響應圖 (b)靈敏函數S0點對點的頻率響應圖.. 28 (a)近似後開迴路頻率響應圖 (b)近似後靈敏函數S0的頻率響應圖...... 29 (a)量化後開迴路頻率響應圖 (b)量化後靈敏函數S0頻率響應圖.......... 29 第一種直接結構之信號流程圖................................................................. 31 第二種直接結構之信號流程圖................................................................. 31 串接結構之信號流程圖............................................................................. 32 並聯結構之信號流程圖............................................................................. 33 硬體實體圖.................................................................................................. 34 EZ-USB硬體圖[53] .................................................................................... 36 Keil μ Vision2 使用介面 .......................................................................... 37 EZ-USB Control Panel使用介面 ............................................................... 37 SN11116 接腳圖[48].................................................................................. 38 viii.

(11) 圖 5.2.2 圖 5.2.3 圖 5.3.1 圖 5.3.2 圖 5.3.3 圖 5.3.4 圖 5.4.1 圖 6.1.1 圖 6.1.2 圖 6.1.3 圖 6.1.4 圖 6.1.5 圖 6.1.6 圖 6.1.7 圖 6.1.8 圖 6.1.9 圖 6.2.1 圖 6.2.2 圖 6.2.3 圖 6.2.4 圖 7.1.1. SN11116 方塊圖[48].................................................................................. 39 I2S傳輸機制[19] ........................................................................................ 41 CycloneII EP2C35F484C6 Emulation Board[54] ...................................... 42 Quartus使用介面 ........................................................................................ 43 I2S Decoder硬體方塊圖[19]...................................................................... 44 FPGA內部總實現方塊圖 .......................................................................... 46 (a)數位麥克風的量測訊號架構圖 (b)數位麥克風的硬體示意圖[51]... 46 800Hz單頻正弦波當雜訊 (a)沒有數位控制器 (b)有數位控制器....... 47 耳機內部量測的噪音大小......................................................................... 48 800Hz當雜訊(另一個噪音源) (a)沒有控制器 (b)有控制器 ................. 48 耳機內部量測的噪音大小(另一個噪音源).............................................. 49 800Hz(正配戴法) (a)沒有數位控制器 (b)有數位控制器 ..................... 50 800Hz(前配戴法) (a)沒有數位控制器 (b)有數位控制器 ..................... 50 800Hz(後配戴法) (a)沒有數位控制器 (b)有數位控制器 ..................... 51 800Hz(放桌上) (a)沒有數位控制器 (b)有數位控制器 ......................... 51 不同戴法的抑制效果................................................................................. 52 街道上聲音的抑制效果:(a) Amplitude (b) dB.................................... 53 另一段街道上聲音的抑制效果:(a) Amplitude (b) dB........................ 53 有明顯脈衝頻率點街道上聲音的抑制效果:(a) Amplitude (b) dB ... 54 具人聲的街上聲音的抑制效果:(a) Amplitude (b) dB........................ 54 全數位式主動式噪音消除系統................................................................. 55. ix.

(12) 第一章 1.1. 緒論. 研究動機 科技蓬勃發展至今為人類帶來便利的生活,但是隨之而來的負面效應不僅污. 染了人類賴以維生的地球也降低人類生活的品質。現在「科技始終來自於人性」 這句話就代表近代科技發展的目標:為提高人類的生活品質不斷研究,其中一項 一直靜待解決的問題就是噪音。因為噪音並不會立即對人類造成明顯的傷害而一 直被忽略,然而事實上短暫的暴露在吵雜的環境下便會因人產生不同程度的焦慮 和不安感,增加疲倦感造成工作效率低落、學習效果不彰,進而引起暫時性聽力 障礙(Temporary Threshold Shift),而長期一直暴露在這樣的環境下來便會演變成 永久性聽力障礙(Permanent Threshold Shift)。也因此政府在民國 85 年起開始課徵 機場噪音防制稅並在民國 88 年和 89 年制訂噪音管制法以及機動車輛管制辦法, 以上均突顯噪音對人類影響的重要性。所以有效的消除噪音不再只有學術研究的 意義,對人類生活品質改善更是有進一步的幫助。 一般噪音控制的方法主要分為以下兩種:被動式(Passive)噪音抑制和主動式 (Active)噪音控制,傳統的噪音控制多屬於被動式。此種抑制方法主要是利用隔絕 或是吸音材料(Sound absorbent meterials)吸收噪音,此方法對於 500Hz 以上的噪 音有較明顯的效果。抑或從結構以及音場著手,改變噪音傳遞路徑的空間幾何形 狀使聲場阻抗(Acoustic impedance)改變而減少噪音傳遞的能量。但是被動式噪音 抑制有以下幾種缺點: z. 設計完成後的噪音消除結構於日後整修均須再花費,成本只會越來越高而耐 久性卻不確定。. 1.

(13) z. 此種方法對於 500Hz 以下的效果不彰,乃因其低頻聲波有較長的波長不容易 在傳輸的過程中損耗能量或被吸收。如果要加強其效果必需使用大量的吸音 材料而導致體積過於龐大笨重且價格高昂,除了不切實際也不符合經濟效益。. 而主動式噪音控制則是利用次音源產生噪音訊號相位相反的訊號干涉破壞噪音 來達到控制效果,主動式具有被動式所沒有的優點:較優的低頻消音效果、體積 較小價格也較便宜、不會造成管路背壓(Back Pressure)、設計具程式彈性化,這使 得主動式成為近年來研究的主流。. 1.2. 相關文獻及歷史發展回顧 主動式噪音控制(Active Noise Control)最早是在 1933 年由德國物理學家 Paul. Lueg(1898~1979)所提出兩個實現主動式消音的理論:「破壞性干涉消音原理」和 「主動式吸音原理」 ,並於 1936 年獲得美國專利[1],他提出理論的系統架構如圖 1.2.1 所示:. 圖 1.2.1 Paul Lueg 主動式消音架構圖 他認為因為數位訊號傳遞速度遠大於聲波,故聲波從偵測點到消音點的時間 足夠其架構對噪音訊號加以控制。但實際上因為聲場迴授(Acoustic Feedback)現 2.

(14) 象,消音喇叭所發出的聲波會回傳到偵測點的麥克風,使得麥克風收到的不只是 噪音還有消音喇叭發出的聲波。這種從麥克風到喇叭形成的迴授架構即是現在前 饋控制(Feedforward)架構的雛型,而用於前饋架構控制的適應性控制法方法像是 最小均方法(Least Mean Square,LMS)和他的變化型[2] [3]也在主動式噪音控制佔 有重要的一席之地。 然而當時 Paul Lueg 的想法並未得到重視,反倒是引起纳粹當局懷疑其可能 應用於軍事使其後半生潦倒。二十年的沉寂於 1953 年由 Olson 和 May[4] [5]率先 打破。他們引入電子吸音器(Electronic Soundabsorber)的觀念,其架構如圖 1.2.1 所 示利用麥克風偵測噪音訊號經由控制器處理後由喇叭播出,此迴授架構可以達到 區域性的寬頻消音效果。而 Olson 也以回饋控制(Feedback Control)在三度空間中製 造出寧靜區(Quiet Zone)此為今日噪音回饋控制奠定基礎。. 圖 1.2.2 Olson 和 May 所提出的電子吸音器架構 主動式噪音控制的觀念雖然在二十世紀就已經萌芽但是當時的技術並未允 許其蓬勃發展,像是電子元件特性等等因素都限制了其可能性,直到 70 年代拜 DSP(Digital Signal Processing)所賜,首先由Kido於 1975 年以數位控制建立了針對變 3.

(15) 壓器噪音的主動式噪音控制系統[6],以及Widrow於 1975 年和 1981 年發表適應性 訊號處理(Adaptive Signal Processing, ASP)的理論[7][8],使得前饋結構(Feedforward Structure)和回饋結構(Feedfback Structure)成為主動式噪音控制的主流。因為數位訊. 號處理的進步加上控制技術改善,使得原先不易實現較複雜的控制方法重新獲得 青睞,進而打開了主動式噪音控制的大門。許多其他的控制法像是適應性控制 法、強健控制中的H2以及H∞控制設計法[9-14]如雨後春筍般出現,而本論文所使 用的是強健控制中的H2和H∞設計理論,利用其訂定性能表現、穩定條件和限制條 件的方程式來設計的主動式噪音數位控制器。. 1.3. 論文主旨和架構與貢獻 傳統上許多主動式噪音控制都以類比電路實現,不同的耳機需要依規格設計. 不同的控制器,而設計的控制器若階數過高都難以用類比電路實現,故其無法利 用過於複雜的演算法來做噪音控制器的設計。而後當數位電路發展穩定後控制器 大多用 DSP 來完成,簡單的說就是控制器逐漸走向數位化。FPGA 發展初期因其 邏輯閘(Gate Count)太少而不適用於此。如今隨半導體製程演進 FPGA 的邏輯閘數 目已大幅增加,也因為線徑的寬度變細使邏輯閘之間的延遲時間越來越小,故選 用 FPGA 實現主動式噪音控制也成為選擇之一。在 FPGA 上設計完成後可以將控 制器模組化甚至可以視為 IC 設計的前身,整個系統的體積將縮小方便應用。 本論文承繼[15-19] D類放大器前級調變的Σ-Δ作為基礎,將從音源數位取樣 至撥放間所有過程數位化。Σ-Δ調變比起其他調變像是PWM擁有較寬的頻寬並 可以支援音調振鈴和MP3 的播放,而且也擁有較低的切換頻率甚至不需要後級的 濾波器。再結合經過以強健控制中的H2和H∞設計理論訂定性能表現、穩定條件和 限制條件所設計的主動式噪音數位控制器,將以上兩者全部於FPGA內實現,也 就是將所有的訊號處理都數位化模組化。下頁圖 1.3.1 為實作架構圖。. 4.

(16) 圖 1.3.1 實作架構圖. 1.4. 章節概要 本論文的章節組織如下: 第二章將說明將multi-bit數位訊號調變成 1bit切換訊號的SDM的調變原理以. 及用來設計控制器的H∞強健控制理論簡介還有本論文系統的簡介;第三章為本論 文理論核心,以H2和H∞設計理論訂定性能表現、穩定條件和限制條件所設計的主 動式噪音控制控制器;第四章為迴授控制器的模擬設計,說明如何利用已得到的 受控體頻率響應來設計所需要的迴授控制器,以及模擬設計的控制器其噪音抑制 的理論效果,並探討數種實現IIR濾波器的架構;第五章則是針對硬體方面的架構 和規格以及模擬軟體等等做說明;第六章提出該數位化噪音控制平台之效能量測 與比較;最後第七章為結論及對本系統的未來展望。. 5.

(17) 第二章 理論和系統簡介 用於將 16 位元訊號轉換為單位訊號流形式的方法除了最常見的Pulse-Width -Modulation(PWM)以外就是本論文沿用的Sigma-Delta Modulation(Σ-Δ)。這部份的 介紹將於 2.1 節呈現。而設計主動式噪音控制的方法至今已經發展出許多演算法 像是適應性控制法、H2以及H∞控制設計法,以其為基礎再結合其他設計法也尤受 青睞[20-22],本章將於 2.2 節對用於主動式噪音控制的H∞強健控制理論做簡單的 介紹。最後 2.3 節會對本論文的系統做簡單的說明。. 2.1. Sigma-Delta Modulation (SDM). 2.1.1. SDM 之發展由來. Sigma-Delta(Σ-Δ) Modulator 是由 Delta(Δ) Modulator 演變而來的,最早是在 1952 年由 Frank de Jager 提出[23] ,主要應用在通訊領域。圖 2.1.1 為 Delta(Δ) Modulator 和功率放大的方塊圖,虛線部分即為 Δ 調變器架構示意圖。假設 Si 代 表一個 16-bit 的數位音訊, S0 為△調變之 1Bit 雙準位輸出( ±1 )[52]。. Si. e. SΛ. ∫. S0. ∫. 圖 2.1.1 Delta Modulator 和功率放大方塊圖. 6.

(18) △調變之目的就是要使 S0 之積分波形愈接近 Si 愈好,當 S0 經 D 類放大器轉換 成類比訊號時,透過類比積分器與低通濾波器處理後所看到的類比訊號即為圖 2.1.2 所示的 S d ,△調變會在固定的頻率下透過現在的值和要追蹤輸入訊號 Si 的 差來調變。當 Z i 超過 Si 時就讓其 S0 值下一個時刻為負 1 表示需要往下修正,反之 則值下一個時刻為正 1 表示需要往上修正。不斷修正的結果就讓 S0 轉換為類比經 過類比積分器後的波形和 Z i 的波形一樣,唯一差別是其為類比訊號而 Z i 是數位訊 號。最後再透過類比低通濾波器以產生平滑重現類比訊號。. Z. S. i. i. S0. Sd S. i. 圖 2.1.2 Delta Modulator 操作機制. 但是△調變主要是有三個缺點:(i)若輸入訊號變化太劇烈將使得輸出 S0 積分 過後跟不上輸入訊號造成嚴重失真;(ii)當輸入訊號為直流或頻率極低時, S0 只會 不斷上下切換卻無法得知電壓大小,如下頁圖 2.1.3 所示;(iii)類比積分器較不穩 定且佔用面積。針對這些缺點 Inose 在 1962 年基於Δ調變器架構提出Σ-Δ調變 器[24],將Δ調變器的類比積分器移至輸入端維持系統的響應,如下頁圖 2.1.4 所 示。如此不但可以使輸入訊號因透過積分而變為較平緩以外,對於輸入訊號是直 流系統也能有效的追蹤。再將其中的二個積分器與減法器做等效處理,可省下一. 7.

(19) 個數位積分器,即成為圖 2.1.5(i)之基本一階Σ-Δ架構。. S. i. Z. S. i. S. i. S0. i. S0. 圖 2.1.3 Delta Modulator 的缺點. ∫. e. S0. SΛ. ∫. ∫. 圖 2.1.4 Inose Δ調變器. (i). (ii). 圖 2.1.5 (i)一階Σ-Δ調變器 (ii) 一階數位Σ-Δ調變器. 8.

(20) 圖 2.1.6 n 階數位Σ-Δ調變器 若在輸入端及迴授端設計乘法係數來設定權重,即成為一完整一階數位Σ- Δ調變器,如上頁圖 2.1.5(ii)所示。而將之串接數個之後即可得到圖 2.1.6 所表示 的n階數位Σ-Δ系統,其中an、bn、…、a1、b1為乘法器的係數,可以控制迴授 路徑以及訊號路徑各階的權重。. 2.1.2. SDM 之概念與系統效果. Sigma-Delta(Σ-Δ) Modulation 利用較高的取樣頻率補償訊號位元數之降低 [16],將多位元(multi-bit)的訊號轉成一連串單位元(1-bit)的訊號輸出,使得這串單 位元訊號的頻譜在音頻範圍內(20kHz)和輸入訊號一模一樣。量化器(Quantizer)因 為固定的階層差別產生的量化誤差則透過迴圈轉移函數使其盡量移往高頻的頻 帶,如此一來這些雜訊便可以利用類比低通濾波器或是揚聲器的低通效應還原音 頻內的訊號。 在輸入訊號通過最後的量化器之前會經過多級的低通濾波器,使量化器幾乎 只針對低頻訊號作量化,其目的是希望訊號經由量化器量化後低頻成分可以非常 精確。但是迴授端會夾帶量化後的高頻成分,因此低通濾波器目的便是在訊號進 入量化器前濾掉高頻成分。故當Σ-Δ調變器的階數越高,濾除高頻的能力越強 且量化器對於低頻訊號的量子化也越精準,量化誤差也就越往高頻推,來得到更 好的訊號雜訊比(Signal-to-Noise Ratio)。但階數越高數位濾波器成本越高且夾雜 9.

(21) 了穩定性分析的問題,因此如何在階數與規格要求取得平衡是很重要的。以圖 2.1.7 為例子雜訊有明顯被推至高頻的效果,而二階系統的量化雜訊比一階較往高 頻推擠,Noise-Shaping 的效果更加明顯,由此可以表示階數越高,效果越好。. 圖 2.1.7 一階與二階Σ-Δ輸出頻譜響應圖. 2.2. H∞強健控制理論簡介 在 1980 年以後控制理論正式將模式的不確定性因素納入問題,這種趨勢就. 是造成強健控制形成的原因。1981 年Doyle和Stein利用小增益定理(Small Gain Theorem)提出強健穩定條件(Robust Stability Condition)來保證受擾動的迴授系統 穩定。著名的迴授轉移函數復原(Loop Transfer Recovery;LTR)技術即是在這個時 候提出。同年Zames提出將靈敏函數的H∞範數最小化的穩定控制器參數解法來使 系統獲得最佳強健性[25],從此強健理論便開始納入最佳化設計過程[26]。 解H∞強健控制問題控制器分析方法大致上分成兩類:模式匹配演算法(Model Matching Algorithms,1984)和以Riccati方程式分析的演算法(Two Riccati Equation Algorithms,1988)。而下面簡單介紹H∞強健控制而不多做證明。首先考慮如下頁圖 2.2.1 所示單一輸入輸出的基本迴授架構,我們可以簡單的得到輸入和輸出的關係 式:. 10.

(22) ⎡ Z ( z )⎤ ⎡ P11 ( z ) P12 ( z )⎤ ⎡W ( z )⎤ ⎡W ( z )⎤ ( ) = = P z ⎢Y ( z )⎥ ⎢ P ( z ) P ( z )⎥ ⎢U ( z ) ⎥ ⎢U ( z ) ⎥,U ( z ) = C ( z )Y ( z ) ⎣ ⎦ ⎣ 21 ⎦ ⎣ ⎦ 22 ⎦⎣. (2.1). w. z. u. y. 圖 2.2.1 基本迴授架構. 其中 Pij , i, j = 1,2 為受控體分開可並存的區塊,因為用 Z-domain 來表示故其他的符 號寫成大寫。綜合(2.1)式的關係即可得到下列的關係式: Z (z ) −1 = P11 (z ) + P12 (z )C (z )(1 − P22 ( z )C (z )) P21 (z ) = Tzw (z ) = Fl (P (z ), C ( z )) W (z ). (2.2). 而(2.2)式中的 Fl (P( z ), C (z )) 即線性分式轉換(Linear fraction transformation;LFT)表 示式其中 det (1 − P22 (z )C (z ))−1 ≠ 0,而H∞控制原理就是將上述轉換式的H∞範數最小化 如式子(2.3)表示。. ( ). min Tzw ( z ) ∞ = min sup Tzw e jθ C (z ). C ( z ) 0 ≤θ < 2 π. (2.3). 上面式子(2.3)是最佳解,但是實際上因為太過繁雜使得我們並不會用(2.3)式 去解。取而代之的是這裡我們直接引用[26]第 378 頁推導出具有強健穩定性和良 好雜訊斥拒力的式子,亦即希望互補靈敏度和靈敏度均極小化的式子: ⎡W1 (I + PC )−1 ⎤ ⎡W1S ⎤ ( ) j ω = ⎢ ⎥ ( jω ) < 1 ⎢W T ⎥ −1 ( ) W PC I + PC 2 ⎦ ⎣ ⎣⎢ 2 ⎦⎥ ∞ ∞. (2.4). 其中 W1 ,W2 ∈ RH ∞ 為權重矩陣。 11.

(23) 接下來的演算法會選擇用模式匹配或是用 Riccati 方程式演算法來解[20] [27-29],但是本篇論文並不會使用上述兩種方法解,實際解法將會於下一章做說 明。. 2.3 系統簡介說明 2.3.1 架構簡介 本論文採用的主動式噪音消除頭戴耳機裝置類似 Harry Olson 和 Even May 所 提出的電子消音器(Electronic Soundabsorber) [3] [4]裝置。如圖 2.3.1 所示,將一個 偵測用麥克風至於耳機喇叭處,當外界發生噪音時由偵測麥克風錄得噪音訊號, 經過設計的控制器處理後迴授到Σ-Δ與要播放的原音源訊號一起輸入耳機。由 控制器輸出的訊號會讓耳機的喇叭播出另一個和原噪音形成破壞性干涉的訊號 使噪音降低,以達成在偵測麥克風附近的環境形成一塊消音區的目的。此種方法 對於區域性的消音非常有效,但是區域是以偵測麥克風為中心噪音波長 1/10 為半 徑的區域[30],所以消音的區域和噪音的頻率呈反比。當低頻時的消音區域夠大 到涵蓋耳機配戴的耳朵始消音效果較顯著,隨頻率越高範圍逐漸縮小一直到範圍 無法涵蓋時就無法讓配戴者感受到消音的效果。. 圖 2.3.1 ANC 耳機 本論文在實現控制器上需要受控體的模型,而對於受控體(Plant)的定義是以 輸入訊號進入Σ-Δ端到偵測麥克風輸出錄到的訊號之間的關係,其中包含了將 12.

(24) 多位元轉成單位元訊號輸出處理的Σ-Δ、頭戴式耳機的喇叭、偵測麥克風、耳 機內部環境(包括耳道)等等。我們以點對點的方式得到受控體每點頻率的頻率響 應,而後透過 MATLAB 運算轉成代表受控體的轉移函數。. 2.3.2 控制器設計限制 在製作閉迴路迴授架構的控制器時會發現此架構有隨頻率增加相位落後也會 隨之增加的現象,當相位落後超過 1800必須考慮到穩定度的問題,因此相位落後 的速度會影響控制器可以控制的頻寬。以往的數位電路因為運算速度的問題使得 控制器多用類比實現,但是類比有著準確度考量和控制器參數漂移的問題而無法 實現高階的控制器。隨科技進步且數位控制器有著可程式化、可實現複雜的演算 法、可實現高階的控制器和具省電性的優勢使得今日的控制器多數以數位來實現 之。 而前一小節提到消音區隨頻率增高而降低的問題始的設計的控制頻率只能在 較低的頻帶(約在 1000Hz 之內),而讓高頻區域的噪音不制於增長為主要目的。但 是事實上希望噪音在高頻不增長似乎很難,因為受控體有非極小相位零點(Nonminimum phase zero),因此會有水床效應的問題[31-33]。. 13.

(25) 第三章. 迴授控制器的設計. 第二章說明了設計控制器會用的基本理論以及架構的基本簡介,這裡將會詳 細說明設計數位控制器的計算方法。其中會用到 Q-參數化(Q-parameterization)的 概念[34]即 著名的內部模式控制[35], Q-參數化解出的是 FIR 濾波器的係數, 利用這樣解法的討論也出現其他的文獻上[36] [37],至於如何解出解出其參數則 可以參考[38] [39]。本章所引用的方法是由 Boaz Rafaely 和 Stephen J. Elliott 所提 出[40],不同的在於本論文將所有的過程都數位化在 FPGA 裡,其他的詳細內容 將於以下詳述之。. 3.1. 設計條件說明 在這個小節會分別說明用來設計控制器的條件。首先於 3.1 闡述問題,並說. 明用於設計迴授架構控制器的條件。3.2 說明如何將非凸規劃的問題轉換為凸規 劃的問題。3.3 為系統設計方法與流程。. 3.1.1 問題描述 考慮一個典型的 SISO 迴授控制系統,如圖 3.1.1 所示,C 代表控制器,P 代 表受控體,主要的目的即為在音頻內設計一個 n 階的控制器 C,在受控體 P 屬於 LTI 穩定系統的集合下不管 P 為何其閉迴路系統都為一個穩定的系統。. d u. y. 圖 3.1.1 典型反饋控制架構圖 14.

(26) 圖 3.1.1 可以看出由外界噪音到數位麥克風感測訊號到撥放訊號的喇叭之間的轉 移函數,這樣的轉移函數在設計的條件中佔有很重要的地位。由 Mason’s Gain Formula 可以得到: 1 Y (s ) = D(s ) 1 − P(s )C (s ). (3.1). 這樣的架構和圖 3.1.2 所示是一樣的涵義,但是以圖 3.1.2 可以明顯的對照後方使 用 Q 參數化的方塊圖。. d u. e. 圖 3.1.2 另一種表示反饋控制的架構圖 由於耳機隨配戴者的習慣不同會產生不同的受控體 P,故設計的控制器必須 能夠對所有可能性的受控體閉迴路穩定。也因此受控體的不確定性會在設計上有 條件限制。. 3.1.2 條件設定說明 假設已經知道受控體在頭戴式耳機普通配戴情況下的轉移函數P0,設計一個 控制器使得系統閉迴路具穩定性且達到有效的噪音消除性能。首先第一個條件就 是利用H2的性能標準(Performance Criterion)將噪音最小化如式子(3.2)所示。. min S0W1. 2 2. 1 = min W1 1 + CP0. 2. (3.2) 2. 其中W1是此條件的權重函數根據不同的頻率有不同的值,在設計上通常會是一個 低通函數(Lowpass Function);S0代表的是靈敏函數,其關係已由式子(3.1)獲得。. 15.

(27) 這種條件也同樣有用在前饋式的主動式聲音控制系統[41]。 而接下來是限制條件包括強健穩定性(Robust Stability)、擾動增加(Disturbance Enhancement)、輸入到感測點的訊號能量(Limitations on the Power Input)。首先針 對強健穩定性的限制條件,我們先假設式子(3.3)表示受控體的模型是複合不確定 (Multiplicative Uncertainty)模型的表示式[31]。 P = P0 (1 + Δ ). (3.3). 其中Δ是表示實際的受控體P與之前假設的受控體P0之間的差異,將其限制在權 重函數W2之下也就是式子(3.4)所表示的關係:. Δ < W2. (3.4). 根據以上的敘述閉迴路的抗擾動及模型不確定性的穩定性關係式就可以由式子 (3.5)表示之:. T0W2. ∞. = (1 − S0 )W2. ∞. =. CP0 W2 1 + CP0. <1. (3.5). ∞. T0是靈敏函數S0的補函數亦即T0 +S0=1,而式子(3.5)地詳細證明可以參考小增益 定理[44]的說明,至於權重函數在設計上因為在高頻的變異較大,通常會選擇高 通函數(Highpass Function)。 接下來是對於擾動增加的限制如式子(3.6)所示,對於靈敏函數的振幅設置上 限:. S0W3. ∞. =. 1 W3 1 + CP0. <1. (3.6). ∞. 其中以 1/ W3為想要設置的上限,可以依據頻率不同而設置不同的上限。這樣的 16.

(28) 限制對於主動示聲音控制是很有用的,其可以讓控制頻寬之外的擾動振幅清晰度 不會過大。 最後是對控制訊號u的限制(如圖 3.1.1 所示),讓其強度不會超過設定的權重 函數(1/ W4)2即讓(1/ W4)2為輸入控制訊號強度的上限,其關係式如式子(3.7)所示:. T0W1W4 P0. 2. 2. CP0 WW = (1 + CP0 )P0 1 4. 2. 2. C = W1W4 1 + CP0. 2. <1. (3.7). 2. 這是一個對於實作時可能會發生放大器或是喇叭過載的現象所做的限制條件,用 來避免播放的聲音失真為一個非必要的限制條件,以本論文的實驗並未納入這個 限制條件。 以上設計條件的權重函數都可以由現有的數據做設計,例如W1用擾動的頻譜 來設計、W2用量測的受控體不確定性來設計等等。綜合條件以上的條件即式子 (3.2)~(3.7)我們重新寫出設計條件的式子(3.8):. min S 0W1. 2 2. ⎧ T W <1 ⎪⎪ 0 2 ∞ subject to ⎨ S0W3 ∞ < 1 ⎪ 2 ⎩⎪ T0W1W4 P0 2 < 1. (3.8). 因為以上的式子是一個求解非凸規劃的問題(Nonconvex Programming Problem), 在計算上非常的繁雜一般會用到像是線性二次高斯(Linear Quadratic Gaussian)來 解,而且常常只能求到區域性的最佳解而非全域性的最佳解。所以在這裡要將其 轉換為求解凸規劃的問題(Convex Programming Problem),其會利用到如[42]所討 論的概念。其他詳細的將在 3.2 節說明。. 17.

(29) 3.2 條件求解 3.2.1 設計條件轉換 在 3.1 已經說明了設計上的條件,在此節將說明將條件式從非凸規劃的問題 轉成一個凸規劃的問題,就像是 Boyd et al.所提到的[42]。不過首先我們會先用到 Q 參數化的觀念[34]或是稱為內部控制模式架構[35]的觀念,這樣的架構簡單的說 即是預測誤差的概念。而後即可將圖 3.1.2 反饋控制的設計方塊圖改成圖 3.2.1 的 架構:. d. u. e. x. 圖 3.2.1 數位內部模式控制系統架構圖 根據圖 3.2.1 所示,在有一個穩定的受控體的情況下可以得到迴授控制器的 表示式為式子(3.9)所示:. C=. Q 1 − QP0. (3.9). 其中Q是一串數位FIR控制器的係數而P0 是受控體的FIR或是IIR轉移函數(用 Z-domain表示),其中的假設條件和 3.1 節中的假設條件一樣,而P即表示實際上 的受控體。. 18.

(30) 現在假設系統是線性的,其次假設在對所有頻率響應方程式的取樣是在線性 取樣空間的條件下取樣在單位圓上。然後就可以根據如[42]和[43]所敘述的頻率數 位化方法將條件近似成一個凸規劃的問題。在設計的頻率內取樣 N 個點在單位圓 上,式子(3.8)就可以改寫成式子(3.10):. 1 min q N. N −1. ∑ (1 − Q(k )P (k ))W (k ) k =0. 0. 1. 2. , q = [q0. q1 L qI −1 ]. T. ⎧ ⎪ Q(k )P (k )W (k ) < 1 , k = 0,L , N − 1 0 2 ⎪ ⎪ subject to⎨ (1 − Q(k )P0 (k ))W3 (k ) < 1 , k = 0,L , N − 1 ⎪ N −1 2 ⎪1 Q(k )W1 (k )W1 (k ) < 1 ⎪⎩ N ∑ k =0. (3.10). q 為 FIR 濾波器的係數,經過轉換後的條件式(3.10)就是一個求解凸規劃的問題, 簡單的說就是可以解出唯一的全域性最小值。. 3.2.2 求解條件 對於求解 FIR 濾波器係數向量 q 在[40]有詳細的說明,在這裡採用連續二次 計算(Sequential Quadratic Programming)來求解[38] [39],其他方法像是限制性最 佳化的一種 semidefinite programming 也是一種求解的途徑[46]。求解的方程式數 目由 N 決定,N 通常是受控體取樣頻率點的數目,當 N 取的太小會使誤差太大 不夠逼近原始連續時候(3.8)式子的解。至於 FIR 的階數根據 Titteron 和 Olkin 的 建議[36]適當的加長其數目直至其性能收斂為止來決定最佳的階數,本論文則根 據實作上不同階數的效果將階數定在 34 階。在本論文利用 MATLAB 解最佳化問 題的指令「fmincon」來幫助求得最佳解,詳細用法請參考[39]。. 19.

(31) 3.3. ANC 頭戴式耳機的迴授控制器設計 這一個章節將會介紹本論文錄製受控體平台的情況以及說明如何選擇不同. 限制條件的權重函數。. 3.3.1 錄音平台簡介. 圖 3.3.1 錄製受控體的平台方塊圖 圖 3.3.1 則是在量測受控體時的平台狀況方塊圖。訊號源(通常是PC)播放一 段頻率(0~15k Hz)的正弦波,在安靜的情況下我們由播放出與錄到的訊號兩者的 振幅以及相位變化得到整個平台的頻率響應。由於許多的因素像是不同環境造成 聲壓的變化(例如耳機配戴的位置以及配戴時的鬆緊度不同),會造成受控體的響 應不確定性,故許多設計都會錄製不同配戴情況下受控體的頻率響應來確保系統 的穩定。本論文則直接利用適合的高通函數來設計使迴授控制器具強健性,即是 式子(3.10)中的W2。而下頁圖 3.3.2 則是本論文平台在頭戴式耳機正常配戴情況下 所得到的頻率響應。. 20.

(32) 不同於其他需要在播放裝置上有數位轉類比的轉換器,本論文的受控體包括 了將 16 位元的數位訊號源調變為單一控制訊號的Σ-Δ調變器。錄音用的麥克 風亦不同於傳統上多利用的電容式麥克風,本論文採用的數位麥克風內部是簡單 的Σ-Δ,故錄製的麥克風訊號已是數位的 0 或 1。經由 FPGA 內部 Deciamtion 處理單位元轉回 16 位元數位訊號,故本論文的平台完全呈現數位化的狀態。. -10 -20 -30 -40 -50 1 10. 2. 3. 10. 10. 4. 10. 5. 10. 圖 3.3.2 用來設計控制器之受控體頻率響應. 3.3.2 頻寬和權重函數的選擇 在消音控制頻率的選擇上因為之前 2.3.1 節所提到的有效消音區域是以偵測 麥克風為中心噪音波長 1/10 為半徑的區域[30] [47],也就是消音的區域和噪音的 頻率呈反比亦即在高頻設計消音的效果是有限的,所以在設計時頻率的選擇通常 不會超過 600Hz。不過實際上的設計主要還是依據受控體的頻率響應,接下來是 權重函數的選擇的說明。 首先由 3.1.2 節知道W1是將雜訊的靈敏函數最小化條件的權重函數,根據不 21.

(33) 同頻率的需求有不同的值,在設計上通常會是一個低通函數(Lowpass Function), 也就是會選擇在 600Hz以下的低通函數,也有只要求在一段頻率之內例如:200Hz 至 600Hz之間的設計。 再來是權重函數W2也就是關於閉迴路的抗擾動及模型不確定性的穩定性的 比重關係,通常會選擇其為高通函數(Highpass Function),原因是因為受控體的頻 率響應大都在高頻的地方有劇烈振幅以及相位的改變。像是本論文採用的方法[40] 其量側許多種頭戴式耳機配戴位置時受控體的頻率響應,藉而得到不同情況下各 頻率奈式圖(Nyquist Plot)分佈的狀況。以正常情況的點為中心得到同一頻率點其 他狀況下最遠的位置為半徑,所得到不同頻率點的半徑大小不一,而以高頻的半 徑變化情形最大,其可用來當作設計權重函數W2的依據。 至於權重函數W3則是關於擾動增加的限制,也就是對於靈敏函數的振幅設置 上限,而 1/ W3即是想要限制振幅的上限,一般都設置 6dB即是兩倍的上限,也 就是說會W3會設定在 0.5。W4是對於輸入功率的限制的權重函數,即讓(1/ W4)2為 輸入控制訊號強度的上限。這是防止放大器或是喇叭過載的現象所做的限制條件 來避免播放的聲音失真,可設計也可不設計而本論文與參考的論文都並未納入設 計條件。. 22.

(34) 第四章. 迴授控制器設計實例分析與模擬. 前一章主要為闡述ANC控制器設計方法,在此章節則針對實際上ANC耳機設 計的平台以及流程做簡單的敘述。. 4.1. 受控體的定義 首先要確定 ANC 耳機的平台,這是量測受控體頻率響應的設定,如圖 4.1.1. 所示。用來運算的Σ-Δ調變器是採用四階的架構,所以受控體的設定即是虛線 框起來在 FPGA 內部用來處理 16 位元訊號的Σ-Δ和處理數位麥克風錄到訊號 的 Decimation 以及撥出聲音的密閉耳罩空間和數位麥克風。也就是說訊號從進入 第一階Σ-Δ處理到撥出後再經過數位麥克風錄到的訊號傳給 Decimation 處理 完後要回傳給 USB 的點為止是本論文認定受控體的部份。. 圖 4.1.1 量測受控體的平台方塊圖 根據量測不同頻率的正弦波計算其強度(Magnitude)和相位(Phase)的變化 得到受控體的頻率響應,再經由第三章所說明的設計條件經過 MATLAB 模擬進 而得到 FIR 濾波器 Q 的係數,由式子(3.9)即可得到控制器 C 的係數。最後再將計 算好的控制器寫入 FPGA 內 ANC 耳機平台才算完工。至於 MATLAB 計算的模擬 23.

(35) 結果在下一節作簡述。. 4.2 MATLAB 模擬 有了受控體的頻率響應以後接下來就是用MATLAB模擬設計控制器,在設計 上有許多可以調的參數,像是FIR濾波器Q的階數、權重函數W1~W4、受控體近似 成IIR轉移函數的階數等等。在FIR濾波器Q的階數在設計上階數越高效果會越 好,但是階數在超過一定值之後效果就會收斂[40]。況且階數越高會造成控制器 的階數也跟著提高,這會使得寫入FPGA後使用的加法器以及乘法器的數目大大 增加,連帶FPGA的使用面積也會增加。同樣的問題也發生在受控體近似成IIR轉 移函數的階數選定,階數太低會造成受控體的頻率響應失真與原先設計的不符 合,而太高則會造成上述的結果,所以在階數選定上要具備兼顧效果和成本考量。. 4.2.1 數位控制器模擬 由圖 3.3.2 的受控體頻率響應先簡單的定義需要有噪音抑制效果的頻帶,在本 論文選取的頻帶是 800~900Hz 要有抑制效果,而實際上可以根據不同的受控體或 不同的要求決定要有抑制效果的頻帶。再來就是階數的選擇,本論文所選取的階 數根據使用面積考量與效果之間作平衡的選取,訂定 FIR 濾波器 Q 的參數為 33 階。在不經過簡化的寫法也佔 FPGA 不到 70%的面積,故事實上經過簡化之後其 面積將遠小於 70%,如果未來製程 IC 其面積也不會過大而不便。至於權重函數 的選取方法如 3.3.2 節中說明的方法一樣。 接下來將列好的式子(3.10)求解即可得到 FIR 濾波器 Q 的參數,本論文直接 利用 MATLAB 的最佳化工具求解,其工具已在 3.3.2 節作說明,圖 4.2.1 即是將 設計好的 Q 參數配合受控體的頻率響應結果經由式子(3.9)由點對點得到的數位控 制器頻率響應圖。. 24.

(36) 60 40 20 0 -20 -40 0 10. 1. 10. 2. 3. 10. 10. 4. 10. 5. 10. 圖 4.2.1 設計出的數位控制器點對點畫出的頻率響應圖 在這裡我們尚未考慮將受控體做 IIR 近似,一樣考慮過大的階數雖然會越近 似原來的受控體但是也會增加數位控制器的階數,故此選用分子分母各 9 階的 IIR 轉移函數來近似受控體,圖 4.2.2 即是用受控體近似的結果經由式子(3.9)由得到 的數位控制器頻率響應圖,由圖可以看到相位以及大小均有失真。. 40 20 0 -20 -40 0 10. 1. 10. 2. 3. 10. 10. 4. 10. 5. 10. 圖 4.2.2 受控體近似後的數位控制器頻率響應圖 再來是考慮寫入 FPGA 後用 16 位元表示時的量化失真,圖 4.2.3 即是模擬寫 入 FPGA 係數所畫出的數位控制器頻率響應圖,由圖可以看到相位以及大小比對 25.

(37) 原來的點對點結果均有失真,但是與圖 4.2.2 的結果非常相近。. 40 20 0 -20 -40 0 10. 1. 10. 2. 3. 10. 10. 4. 10. 5. 10. 圖 4.2.3 量化後的數位控制器頻率響應圖 最後得到數位控制器係數如下: C (z ) = A. b0 + b1 z −1 + b2 z −2 + L + b43 z −43 , A = 25 −1 −2 − 43 a0 + a1 z + a2 z + L + a43 z. (4.1). 表 4.2.1 數位控制器係數(以 16 位元表示) b0 = 7 b7 = −271 b14 = 4. b1 = −93. b2 = 240. b8 = 123. b9 = −28. b10 = 7. b15 = 4. b16 = 3. b17 = 3. b3 = −441. b5 = −575. b12 = 6. b18 = 3. b19 = 3. b20 = 3. b25 = 9. b26 = 11. b27 = 13 b34 = −734. b22 = 5. b28 = 15. b29 = 18. b30 = 20. b31 = 23. b32 = 25. b33 = 27. b35 = 2589. b36 = −5377. b37 = 7954. b38 = −9026. b39 = 8085. b40 = −5659. b43 = 253. a0 = 1024. a1 = −4594. a2 = 11176. a6 = 20042. a7 = −12820. a8 = 6259. a9 = −2124. b42 = −1153 a5 = −24730. 26. b6 = 451. b11 = 6. b21 = 4. b23 = 6. b24 = 8. b4 = 564. a3 = −18919 a10 = 392. b13 = 5. b41 = 3053 a4 = 24329. a11 = 0.

(38) a12 = 0. a14 = 0. a13 = 0. a16 = 0. a17 = 0. a18 = 0. a21 = 1. a22 = 1. a27 = 1. a28 = 1. a29 = 1. a30 = 1. a31 = 1. a32 = 1. a34 = 3. a35 = 1. a36 = −2. a37 = 15. a38 = −30. a39 = 49. a41 = 44. a42 = −30. a19 = 1. a20 = 1. a26 = 1 a33 = 1 a40 = −53. a15 = 0. a24 = 1. a23 = 1. a25 = 1. a43 = 12. 這裡採用一般檢測系統閉迴路穩定性的方法即是奈式定理,由奈氏定理可知 當受控體乘上數位控制器的奈氏圖沒有繞過點(-1,0)即可斷定此系統是閉迴路穩 定,如圖 4.2.4(a)所表示的在受控體做 IIR 近似之後系統依然是閉迴路穩定,而經 過 16 位元量化表示後如圖 4.2.4(b)其系統閉迴路穩定依然存在。. 2.5. 2.5. 2. 2. 1.5. 1.5. 1. 1. 0.5. 0.5. 0. 0. -0.5. -0.5. -1. -1. -1.5. -1.5. -2 -1. -0.5. 0. 0.5. 1. 1.5. 2. 2.5. 3. -2 -1. 3.5. -0.5. 0. 0.5. 1. 1.5. 2. 2.5. 3. 3.5. (a) (b) 圖 4.2.4 (a)受控體近似後的奈氏圖 (b)量化後的奈氏圖 簡單的模擬此數位控制器在平常環境下輸入和輸出的關係,首先用數位麥克 風錄下平常環境下的噪音,在取樣頻率 48000 之下所錄到的結果如圖 4.2.5(a)。經 由數位控制器處理過後的結果則如圖 4.2.5(b)所示。. 27.

(39) 0.2. 0.15. 0.4. 0.1. 0.3. 0.05. 0.2. 0. 0.1. -0.05. 0. -0.1. 0. 500. -0.1. 1000 1500 2000 2500 3000 3500 4000 4500 5000 5500. 0. 500. 1000 1500 2000 2500 3000 3500 4000 4500 5000 5500. (a) (b) 圖 4.2.5 (a)平常實驗室的噪音 (b)經過數位控制器的輸出. 4.2.2 雜訊抑制效果模擬 由之前在第三章式子(3.2)定義的靈敏函數S0可以簡單的模擬對於噪音抑制效 果,首先是針對開迴路轉移函數的頻率響應模擬,亦即受控體和數位控制器相乘 的結果,如下頁圖4.2.6(a)所示其為點對點得到的開迴路頻率響應圖,根據此結果 即可得到靈敏函數S0的頻率響應圖如下頁圖4.2.6(b)所示。. 40. 10. 20. 0. 0. -10. -20. -20. -40 -60 0 10. -30 1. 10. 2. 10. 3. 10. 4. 10. -40 0 10. 5. 10. 1. 10. 2. 10. 3. 10. 4. 10. 5. 10. (a) (b) 圖 4.2.6 (a)開迴路點對點的頻率響應圖 (b)靈敏函數S0點對點的頻率響應圖. 28.

(40) 20. 10 5. 0. 0 -20 -5 -40 -60 0 10. -10 1. 10. 2. 10. 3. 10. 4. 10. -15 0 10. 5. 10. 1. 10. 2. 10. 3. 10. 4. 10. 5. 10. (a) (b) 圖 4.2.7 (a)近似後開迴路頻率響應圖 (b)近似後靈敏函數S0的頻率響應圖 同上一節所敘述的我們必須考慮將受控體做IIR近似所有的失真,將受控體近 似的結果經由如上述得到的開迴路轉移函數頻率響應圖如圖 4.2.7(a)所示,根據此 結果即可得到靈敏函數S0的頻率響應圖如上頁圖 4.2.7(b),由圖可以看到相位以及 大小均有失真。最後是考慮寫入FPGA後用 16 位元表示時的量化失真,同樣的如 上述得到的開迴路轉移函數頻率響應圖如圖 4.2.8(a)所示,根據此結果即可得到靈 敏函數S0的頻率響應圖如圖 4.2.8(b),由圖可以看到相位以及大小比對原來的點對 點結果均有失真,但是與圖 4.2.7 的結果非常相近。. 20. 10 5. 0. 0 -20 -5 -40 -60 0 10. -10 1. 10. 2. 10. 3. 10. 4. 10. -15 0 10. 5. 10. 1. 10. 2. 10. 3. 10. 4. 10. 5. 10. (a) (b) 圖 4.2.8 (a)量化後開迴路頻率響應圖 (b)量化後靈敏函數S0頻率響應圖 此模擬的結果可以當作實際平台量測的依據,至於實際上量測的結果將會在 29.

(41) 第六章做完整的呈現與說明。. 4.3. 數種 IIR 濾波器之實現架構討論 實際上IIR濾波器的實現方法有很多種,這裡將探討不同實現架構對於暫存器. 數目的影響,除此之外對於量化誤差也有減小的優點[45] [50]。本節則針對暫存 器的數目做討論。 直接形式(Direct Forms) 在上一節的數位控制器是以最傳統的方式表示: C (z ) =. b0 + b1 z −1 + b2 z −2 + L + b43 z −43 a0 + a1 z −1 + a2 z −2 + L + a43 z −43 43. 43. k =0. k =0. (4.2). y[n] = ∑ bk x[n − k ] − ∑ ak y[n − k ]. (4.3). 在寫入FPGA內部實現最直接的方法如式子(4.2)所示。這樣的表示法在IIR濾波器 的實現上是量化誤差最大的表示法,以簡單的方塊圖表示之如圖4.3.1。很明顯的 在這個架構中輸入需要44個暫存器而輸出需要43個,總共87個暫存器,同樣的乘 法器也需要87個。. x[n ]. b0. v[n]. z −1. z −1. b1. a1. x[n − 2]. b2. a2. x[n − 42]. b42. a42. b43. a43. x[n − 1]. z −1. z −1 x[n − 43]. y[n]. a0. 30. y[n − 1] z −1. y[n − 2]. y[n − 42] z −1 y[n − 43].

(42) 圖 4.3.1 第一種直接結構之信號流程圖 w[n]. x[n]. b0. y[n]. z −1 a1 a2. b1. z −1 b2. a42. a43. b42. z −1. b43. 圖 4.3.2 第二種直接結構之信號流程圖 第一種直接架構圖可以視為兩個線性非時變系統串接,所以前後順序可以對 調,對調完等效後即可得到上頁圖4.3.2的方塊圖。在這個架構中需要的乘法器和 第一種的一樣多,但是暫存器只有44個。第二種的架構可以節省一半的暫存器, 而根據對換式(Transposed Forms)的理論其還可以分成先執行零點再執行極點或 是先執行極點再執行零點,還有其所存在的量化誤差的問題等等詳細的細節可以 參考[45]。 串接形式(Cascade Form) 另一種形式則是串接式,即是把直接式的轉移函數做因式分解得到如式子 (4.3)所示,通常會選用串接二階系統以簡單的方塊圖表示之如圖4.3.3。這個架構 中每一階需要3個暫存器最後一階則是2個總共65個暫存器,而所需要的乘法器共 108個則遠比直接式多。. 31.

(43) ∏ (1 − e z )∏ (1 − f M1. C (z ) = A. k =1 N1. −1. k. k =1 N2. k. k =1. z −1 1 − f k* z −1. k. ∏ (1 − c z )∏ (1 − d −1. )(. M2. k. z. −1. ) ⎧M. )(1 − d z ) * −1 k. 1 + 2 M 2 = 43 ,⎨ ⎩ N1 + 2 N 2 = 43. (4.4). k =1. w1 [n] b 01. x[n]. z −1. a11. z −1. a21. y 21 [n]. y1 [n]. w22 [n] b022. b11. a122. z −1 b122. b21. a 222. z −1 b222. y 22 [n] y[n]. 圖 4.3.3 串接結構之信號流程圖 圖4.3.3的組合方式其實還有很多種,把二階的順序作不同的調換可以得到很 多理論上的等效系統。現在有21個二階系統和1個一階系統,假設視為22個二階 系統,則有22階乘(factorial)的延遲零點配對和22階乘的二階段排序法,總共會有 22階乘的平方種不同的配對和排序。在無限精準度的情況下可以得到一樣的輸入 輸出關係,但是一旦考慮有限精準度則以上的不同排序法中可以找出一種誤差最 小的排序法,這就是這種架構會比直接形式量化誤差較小的原因。 並聯形式(Parallel Form) 還有一種形式則是並聯式,即是把直接式的轉移函數做部份分飾展開得到如 式子(4.4)所示,通常會選用二階系統來並聯以簡單的方塊圖表示之如圖4.3.4。這 個架構中每一階需要3個暫存器最後一階則是2個總共65個暫存器,而所需要的乘 法器共86個,對於使用暫存器和乘法器的數目來說此種架構算是理想的選擇。. ⎧ N1 + 2 N 2 = 43 Ns N2 Ak Bk 1 − nk z −1 q0 k + q1k z −1 ⎪ C (z ) = ∑ , +∑ =∑ ⎢ (43 + 1) ⎥ * −1 −1 −1 −1 −2 ⎨ 1 − mk z − p2 k z ⎪ N s = ⎢ k =1 1 − g k z k =1 1 − mk z k =1 1 − p1k z ⎣ 2 ⎥⎦ ⎩ N1. (. (. )(. ). ). 32. (4.5).

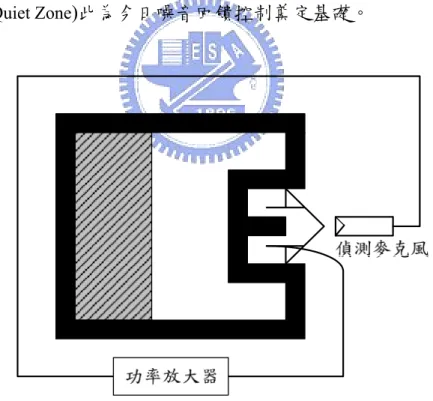

(44) w1 [n] q 01. z −1. p11. y1 [n]. q11. z −1. p 21. x[n]. y[n]. w22 [n] q. p122. p222. 022. z −1 q122. y 22 [n]. z −1. 圖 4.3.4 並聯結構之信號流程圖 實際上在實現時可以只產生一組二階的IIR,透過回圈的方式重複22次一樣可以 算出同樣的結果,而使用的暫存器剩3個乘法器剩4個,不過儲存係數的暫存數目 則不變[50]。. 第五章. 硬體架構與實現. 在前面的章節我們已經說明了設計的方法和模擬的結果,在此對時做的平台 做簡單的介紹。就如圖 1.3.1 的實作架構所示,由數位麥克風所錄到的訊號經由 寫在 FPGA 裡面的 Decimation 運算後與原來的訊號相減經過設計好的控制器,將 算設計好的訊號和將要撥放的訊號相加經過 Σ-Δ 的運算由喇叭端播出要撥放的 訊號和與噪音相位相反的訊號。 在平台上我們會用到兩個 USB,一個是用來作為 PC 端的介面所採用的 USB5.1 聲道音效控制器,將 PC 端送出的雙聲道數位數位儲存媒體一律轉為取樣 33.

(45) 率 48kHz、雙聲道、16 位元數位訊號,將此雙聲道訊號傳輸至以 FPGA 實現的數 位 Σ-Δ 調變器,產生一連串單位元的控制訊號。而另一個是可用來同步輸出數 位麥克風所錄到的訊號經過 Decimation 運算的結果。 本章主要闡述上述四個實現的部分:5.1 節介紹用來將數位麥克風傳輸處理 好的訊號傳回 PC 的 USB 介面 EZ-USB FX 平台;5.2 節說明將 16 位元訊號從 PC 傳到 Σ-Δ 間用到的 USB 介面 USB1.1 5.1 聲道音效控制器;5.3 節介紹用來實現 設計的控制器、Σ-Δ 和 Decimation 運算的 FPGA 板以完成 I2S 介面、Σ-Δ 調變 器和 Decimation 以及數位控制器;最後 5.4 節則是簡介用來錄音的數位麥克風。. 圖 5.1. 硬體實體圖. 上頁硬體實體為圖 5.1。左邊的 USB 版即是 EZ-USB FX 平台,主要用來錄 音用,實際上主動式噪音消除與這一部份 USB 的運作沒有直接的關係。而橘褐 色底板則是 USB1.1 5.1 聲道音效控制器的運作電路板,這一部分的電路負責處理 將 PC 端的資訊傳至 FPGA。最右邊則是數位麥克風將資料傳回 FPGA 板的電路, 因為實際上數位麥克風需要的工作電壓是 1.7V,而 FPGA 板只供應 3.3V 或是 5V,故此部分的工作電壓必須由另外電路製造。後面會有關於其詳細的介紹。. 34.

(46) 5.1. USB 介面 USB(Universal Series Bus)即萬用串列匯流埠,其傳輸類型分成以下四種:控. 制傳輸(Control Transfer)、中斷傳輸(Interrupt Transfer)、巨量傳輸(Bulk Transfer) 以及等時傳輸(Isochronous Transfer)。控制傳輸為雙向傳輸,主要用來溝通主機和 裝置之間的配置、命令或狀態;中斷傳輸也為雙向傳輸,由於 USB 並不支援硬 體中斷固其為依靠主機週期性的輪詢(Polling)而運作,通常適用於鍵盤、滑鼠等 等;巨量傳輸則可為單向也可為雙向是突發性的傳輸模式,適用於傳輸大量的資 料像是印表機和掃描機等等;等時傳輸亦可為單向也可為雙向,透過事先的與主 機的協議在一定的傳送速度下傳送資量,適用於 USB 麥克風、喇叭等等。在下 面介紹的 USB 則是利用等時傳輸的傳輸模式,每 1ms 等時中斷發生,等時傳輸 FIFO 中的資料將透過 USB 傳輸給主機。表 5.1.1 為四種傳輸模式的比較。. 表 5.1.1 USB 四種傳輸模式比較 本節先介紹用來傳送數位麥克風資訊的 EZ-USB FX,此硬體實際上是在量測 受控體時使用而在 ANC 耳機平台的運作不會用到,故在此只做簡單的介紹。至 於用來處理 PC 端連接 FPGA 傳給 Σ-Δ 調變器的 USB1.1 5.1 聲道音效控制器在 下一節再做詳述。. 35.

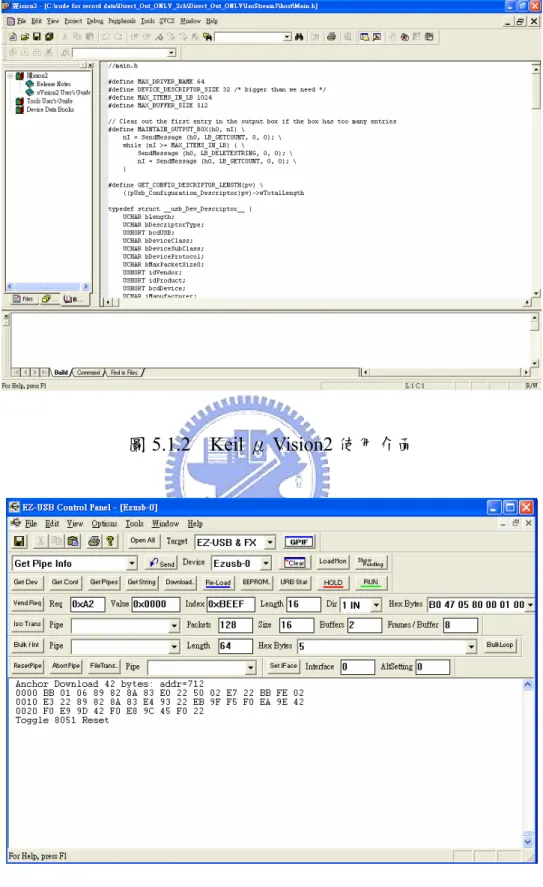

(47) 5.1.1 硬體介紹:EZ-USB FX EZ-USB FX 平台由 Cypress 半導體公司推出,將 EZ-USB 晶片和 USB 週邊 介面所需要的各種功能統整包裝成一個精簡的電路,實體如圖 5.1.1 所示。其微 處理機是一個增強的 8051 核心但是執行速度是標準 8051 的十倍,具許多優良特 性像是:符合 USB1.1 版 12Mbps 高速傳輸標準、支援等時、巨量、控制、中斷 四種傳輸模式、提供偵錯與發展的環境(Keil C Compiler)等等。其平台系統包括以 下三項:控制 S/H、Switch 和 A/D 的時序、接收 A/D 轉換器的數位資料輸出、將 數位資料傳送給 PC 端[53]。. 圖 5.1.1 EZ-USB 硬體圖[53]. 5.1.2 軟體介紹:KeilμVision2 and EZ-USB Control Panel KeilμVision 是用來編輯寫給 EZ-USB 專用晶片 C 程式的 hex 檔所用。而 EZ-USB Control Panel 則是將編輯完成的 hex 檔下載至控制面板,重新裝置列舉 之後可以將 Cypress AN2131Q USB 裝置轉型為 hex 檔所指定的 USB 裝置。. 36.

(48) 圖 5.1.2 Keil μ Vision2 使用介面. 圖 5.1.3 EZ-USB Control Panel 使用介面. 37.

(49) 5.2. USB1.1 5.1 聲道音效控制器 SONIX SN11116 支援 32kHz、44.1kHz(需要驅動程式或應用程式提供支援)、. 48kHz 三種數位錄音取樣頻率,以及 48kHz 類比錄音取樣頻率和類比/數位播放的 USB 聲音控制器。在數位撥放模式時,可經由 USB 介面直接接收來自 PC 的音源, 也可以經由 S/PDIF 消費性音效介面標準傳送音源。SN11116 亦提供三種包含 32kHz、44.1kHz、48kHz 的取樣頻率及自動判別鎖定頻率功能。SN11116 架構上 已完整地支援 1 個控制 PIPE,兩個即時 PIPE 和 1 個中斷 PIPE 為一個應用相當 廣泛的音源控制器[19] [48]。. 圖 5.2.1 SN11116 接腳圖[48]. 5.2.1 硬體介紹:SONIX SN11116 SN11116 主要功能是將 PC 端數位音訊擷取為 5.1 聲道、16-bit PCM,而在此 只運用到處理雙聲道的資訊。其應用軟體有取樣率轉換(Sample Rate Conversion). 38.

(50) 機制,可將各種取樣率的數位音訊轉為 48kHz。主要用到的功能為 USB 介面資料 線、運作模式選擇、I2S 格式輸出。. 圖 5.2.2 SN11116 方塊圖[48] z. USB 介面資料線(D+、D-):為 USB 資料傳輸線,用來負責與 PC 端溝通、音 效裝置列舉和 PC 端數位儲存媒體讀取用途。. z. 運作模式選擇: 如表 5.2.1 所示。. Setting. Codec CS4228A. AK4527. AV2188. VT1616. TYPE 2. 0. 0. 1. 1. TYPE 3. 0. 1. 0. 1. 表 5.2.1 TYPE 2、3 參照 SN11116 運作模式 z. I2S 格式輸出:由 XMCLK、XSCLK、XLRCLK、XSDO1、XSDO2、XSDO3 六條線來控制六聲道資料輸出。首先 XMCLK 為整個 I2S 同步介面提主要頻 率,連接於接收端同步 I2S 資料傳輸速率與後端系統輸入取樣率,在此提供 的是 12.288MHz 的 clock。XSCLK 為串列傳輸同步的頻率,經除頻倍率下為 39.

(51) 3.072MHz;XLRCLK 為決定 XSDO1~3 為左聲道或右聲道,在此設定為 48kHz,其中 XSDO1~3 為 1 位元串列傳輸線,每一條線可以傳輸兩聲道。而 本論文用到雙聲道的單位元串列輸出,故只會用到 XSDO1。. 5.2.2 I2S (Inter-IC Sound)介面 I2S(Inter-IC Sound)亦即指在晶片間傳遞的音源,作為數位音源在機內進行傳 遞與處理,而 S/PDIF 則適合外傳、外接[49]。 1. I2S 線路: ■SCK(Serial Clock):串列傳輸的時脈線,為獨立時脈傳遞。 ■SD(Serial Data):串列傳輸的資料線,傳遞兩個聲道的數位音源資訊。 ■WS(Word Select):字元選擇線,在此指音源聲道(Channel)選擇。 2. I2S 的連接: I2S 即發送端與接收端直接相連,上述線路都是單方向傳遞。凡是對外輸出 SCK 線路訊號的即是 I2S 的主控者(Master),至於 SD、WS 在設計上可決定由主 控端(Master)發送,也可決定由受控端(Slave)發送。 3. I2S 傳遞機制 SD 的位元串列傳遞以 SCK 為基準,當 SCK 上升緣觸發時發送端的 SD 資訊 就會被接收端給閂鎖住並同步於 SCK 不斷地位元傳遞。而 WS 則是控制 SD 聲道 資料輸出,0 即左聲道而 1 即是右聲道(圖 5.2.3)。當 WS 的 0、1 狀態轉變時,同 一上升緣的 SD 資訊依然是 WS 未轉態前的聲道資訊,等確定 WS 狀態轉變以後 才在下一個上升緣正式傳輸新指定聲道的音源資訊。. 40.

(52) 圖 5.2.3 I2S 傳輸機制[19] 還有一個特點是 I2S 不用事先溝通就可以直接傳送,其使用 MSB 先傳的特 性(圖 5.2.3)。舉個例子如果發送端是 16-bit,接收端是更高解析度的 24-bit,那麼 傳送完 20bits 後的剩餘 8bits 可以由接收端自行補 0,相反的如果接收端有 16-bit 但傳送過來的是 24bits,則最後 8bits 資訊直接忽略。以 SN11116 為例,其後接收 端最高解析為:3.072MHz(XSCLK) ÷ 48kHz(XLRCLK) ÷ 2-Channels = 32-bits。. 5.3 FPGA 核心實現 FPGA(Field Programmable Gate Array)由多個邏輯單元(Logic Cell)經可程式 的垂直通道(Vertical Channel)及水平通道(Horizontal Channel)的連線所構成。具有 可重複程式化的數位邏輯適合用作邏輯設計功能驗證[54]。. 5.3.1 硬體介紹:CycloneII EP2C35F484C6 Emulation Board • Altera Cyclone II Family EP2C20F484C8 Device (Provide 18752 LEs , 239,616 RAM Bits , 26 18X18 Multipliers & 4 PLLs) • Altera Serial Configuration Device EPCS4SI8 • 16M Bytes SDRAM Memory (MT48LC4M32B2) • 8 M Bytes Flash Memory (AM29LV065D). 41.

(53) • 2X16 Character LCD Module • PS2 Keyboard Interface • RS232 Serial Communication Port • 4 Bits DIP Switch • 5 Push Button Switchs • 8 LEDs • 50 Mhz Oscillator • Provide 185 In/Out Pin & 128 shareable In/Out Pin • USB Power Cable • Parallel Port Download Cable • User Define Extension Board. 圖 5.3.1 CycloneII EP2C35F484C6 Emulation Board[54]. 42.

(54) 5.3.2 軟體介紹:Quartus Quartus 是一個發展 FPGA 的環境,能夠編譯 VHDL 或是 Verilog code、 simulation 看波形圖檢驗、規畫 FPGA 的輸入輸出腳位、將編譯好的 code 程式化 FPGA。. 圖 5.3.2 Quartus 使用介面. 5.3.3. FPGA 實作. 在 FPGA 裡面主要實現的部分區分成下列四個:I2S Decoder、4 階數位 Σ-Δ 調變器、Decimation、數位控制器。 I2S Decoder 根據 I2S 的傳輸規格,將 I2S Decoder 的運算模式依照下頁圖 5.3.3 硬體方塊. 43.

(55) 圖進行。I2S 是一個多重 clock 輸入(XMCLK、XSCLK、XLRCLK、XSCLK)的電 路,而所有的 clock 以主頻 XMCLK 作同步(Synchronous)。內部運作包含串列輸 入並列輸出,判別左聲道音源、右聲道音源等等也皆由 XMCLK 同步。. 圖 5.3.3 I2S Decoder 硬體方塊圖[19] 4 階數位 Σ-Δ 調變器 本論文採用的 Σ-Δ 調變器的階數為 4 階架構實現演算法,設計一取樣率為 3.072MHz 的 Σ-Δ 調變器,係數與狀態變數皆以 16-bit 的精確度實現於 FPGA。 首先將係數乘以 32767( 215 )做量化處理(Quantization)後可得表 5.3.1 之 16-bit 實作 係數,其中乘法以移位加法器(Shift-and-Add)節省面積。在此 Σ-Δ 的運作並非本 論文的重點,詳細運作情形可以參考[17-19]。 表 5.3.1 四階 Σ-Δ 調變器實作係數 a1 = 666600 (HEX ). a2 = 199900 (HEX ). a3 = 0F5C00 (HEX ). a4 = 070 D00 (HEX ). b1 = 428F00 (HEX ). b2 = 14EA 00 (HEX ). b3 = 0EC500 (HEX ). b4 = 082700 (HEX ). 44.

(56) Decimation 此部份是將數位麥克風 1.2MHz 的單位元訊號轉換成一般常見取樣頻率的 16 位元訊號,亦即將 1.2MHz 的單位元訊號降頻取樣(Down Sample)成其他的取樣頻 率。考慮到混疊(aliasing)必須採用的低通濾波器來將超過 Nuquist Frequency 的成 分濾除,本論文採用的是平均濾波器(Average Filter)也就是在時域上作平均的動 作:. y[n] =. x[n] + x[n − 1] + L + x[n − M + 1] M. M 為平均的點數。Cut-off frequency 為. 頻取樣之後的頻率為原本頻率的. (5.1) fo , fo 為訊號之原始頻率 1.2MHz。而降 M. 1.2M 1 = ,故 M = 2 × 25 = 50 符合 Nyquist 理論。 48 K 25. 由於平均濾波器的(Stop Band Attenuation)較一般的低通濾波器來的大,故一 般會將訊號做兩次的濾波會有比較好的效果。最後將式子(5.1)做了一點改變將低 加法器的數目:. y[n] =. x[n] + x[n − 1] + L + x[n − M + 1] = y[n − 1] + x[n] − x[n − M ] M. (5.2). 數位控制器 此部份是將 decimation 完的 16 位元訊號透過設計好係數的 IIR 濾波器,傳新 轉換為新的控制訊號傳給訊號處理端的 Σ-Δ,比較式子(4.2)和式子(5.2)即可知此 部分的運算寫法和 decimation 的部份類似,而根據需求的不同可以依據 4.3 節當 中所敘述的方法做調整。 則最後 FPGA 內部總實現為圖 5.3.4:一個 I2S Decoder 解碼兩聲道資訊、一 個為雙聲道 4 階調變器 Σ-Δ、一個將數位麥克風錄到的單位元訊號處理為 16 位 元訊號的 Decimation、一個處理控制訊號和原始訊號相加、一個分離原始訊號和 數位麥克風錄的到訊號,而最後是數位控制器。 45.

(57) Minus Source Signal and Record Signal. Digital Signal. Controller. Sigma-delta. Headset. Add Source Signal and Control Signal. Decimation I2S Decoder. Inside FPGA USB. PC. USB. 圖 5.3.4 FPGA 內部總實現方塊圖. 5.4. 數位麥克風 本論文在錄製聲音的麥克風採用的是數位式的麥克風[51],因為裡面具有簡. 便的 Σ-Δ 不同於傳統類比式的麥克風,此麥克風直接回傳數位的 0 或 1 訊號而 非傳統類比麥克風的電壓訊號。. (a) (b) 圖 5.4.1 (a)數位麥克風的量測訊號架構圖 (b)數位麥克風的硬體示意圖[51]. 46.

(58) 第六章. 效能量測與比較. 本章主要是量測雜訊的抑制效果,於 6.1 節量測就單頻訊號的雜訊抑制效 果,其中會有不同頻率抑制效果的比較和不同的耳機配戴法之下抑制效果的比 較;而 6.2 節則利用街上錄到的聲音當雜訊量測其抑制效果。. 6.1. 單頻雜訊抑制效果量測 此部分重點在於驗證實現於 FPGA 之全數位主動式噪音消除的效果,比較不. 同頻率點其有控制器和沒有控制器抑制效果,另外也將比較不同配戴法對於抑制 效果的影響。. 6.1.1 不同頻率點的雜訊抑制效果量測 輸入訊號皆為取樣率 48kHz 的正弦波(Sine Wave),由不同頻率的所量測到的正 弦波大小來比較。首先如圖 6.1.1 所示,針對頻率 800Hz 撥放一個大小 0.5 的正 弦波,圖(a)和(b)是由 Cool Edit 所看到的大小,可以看出其明顯的差別。. (a) (b) 圖 6.1.1 800Hz 單頻正弦波當雜訊 (a)沒有數位控制器 (b)有數位控制器. 47.

數據

![圖 2.1.6 n 階數位Σ-Δ調變器 若在輸入端及迴授端設計乘法係數來設定權重,即成為一完整一階數位Σ- Δ調變器,如上頁圖 2.1.5(ii)所示。而將之串接數個之後即可得到圖 2.1.6 所表示 的n階數位Σ-Δ系統,其中a n 、b n 、…、a 1 、b 1 為乘法器的係數,可以控制迴授 路徑以及訊號路徑各階的權重。 2.1.2 SDM 之概念與系統效果 Sigma-Delta(Σ-Δ) Modulation 利用較高的取樣頻率補償訊號位元數之降低 [16],將多位元(multi-bi](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/20.892.194.744.113.342/ΣΔ調變器為一完整Σ所表示階數ΣΔ系統其ΣΔ較高取樣頻率.webp)

+7

相關文件

可程式控制器 (Programmable Logic Controller) 簡稱 PLC,是一種具有微處理機功能的數位電子 設備

數位計算機可用作回授控制系統中的補償器或控制

機器人、餐飲服務、花藝、雲端運算、網路安全、3D 數位遊戲藝術、旅 館接待、行動應用開發、展示設計、數位建設

媽媽將 651 元平分給 3 個孩子當零用 錢,爸爸又給每個孩子 125 元,請問現 在每個孩子有多少零用錢?. 換你試試看 換你試試看

• 田口方法 (Taguchi method) 的意義為利用損 失函數的概念評估品質,採用實驗設計的 方法使產品不易受到不想要或無法控制因 子

圖4 1 整合資訊系統風險 圖4.1 整合資訊系統風險..

可利用 HTML 控制項 中的 Table 控制項進 行排版動作. (最好將 Table

在設計九階段管線式類比數位轉換器中,除了第九級之外,第一到第八級皆 要用到

![圖 4.3.1 第一種直接結構之信號流程圖 [ ]nx − 1 z [ ]nw − 1 z − 1 z [ ]n0ybb1b2b42 b 43a1a2a42a43 圖 4.3.2 第二種直接結構之信號流程圖 第一種直接架構圖可以視為兩個線性非時變系統串接,所以前後順序可以對 調,對調完等效後即可得到上頁圖4.3.2的方塊圖。在這個架構中需要的乘法器和 第一種的一樣多,但是暫存器只有44個。第二種的架構可以節省一半的暫存器, 而根據對換式(Transposed Forms)的理論其還可以分成先執行零點](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/42.892.152.769.176.718/結構之信號流程圖一種直接架構圖可以視為兩個線系統串乘法器和.webp)

![圖 5.1.1 EZ-USB 硬體圖[53]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/47.892.281.655.549.779/圖511EZUSB硬體圖53.webp)

![圖 5.2.1 SN11116 接腳圖[48]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/49.892.286.686.519.906/圖521SN11116接腳圖48.webp)

![圖 5.2.3 I2S 傳輸機制[19]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/52.892.181.746.126.334/圖523I2S傳輸機制19.webp)

![圖 5.3.1 CycloneII EP2C35F484C6 Emulation Board[54]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8145854.166899/53.892.178.764.543.1036/圖-cycloneii-ep-c-f-c-emulation-board.webp)