國

立

交

通

大

學

電機學院 電信學程

碩

士

論

文

應用於 UWB 系統與 WiMax 無線網路之低雜訊放大器

Low Noise Amplifier for UWB System And WiMax Wireless Network

研 究 生:程郁娟

指導教授:鍾世忠 教授

應用於 UWB 系統與 WiMax 無線網路之低雜訊放大器

Low Noise Amplifier for UWB System And WiMax Wireless Network

研 究 生:程郁娟 Student:Yu-Chuan Cheng

指導教授:鍾世忠 Advisor:

Shyh-Jong Chung

國 立 交 通 大 學

電機學院 電信學程

碩 士 論 文

A Thesis

Submitted to College of Electrical and Computer Engineering National Chiao Tung University

in partial Fulfillment of the Requirements for the Degree of

Master of Science in

Communication Engineering January 2007

Hsinchu, Taiwan, Republic of China

應用於 UWB 系統與 WiMAX 無線網路之低雜訊放大器

學生:

程郁娟指導教授

:鍾世忠國 立 交 通 大 學 電 機 資 訊 學 院 電 信 學 程 碩 士 班

摘

要

本論文以TSMC 0.18μm 1P6M CMOS,來研製應用於超寬頻網 路的低雜訊放大器,及WiMAX 無線網路的多頻段低雜訊放大器。第一部 份為寬頻低雜訊放大器,適用於超寬頻系統,模擬結果如下所述:頻率範 圍為3.1 ~ 10.1 GHz,輸入與輸出返回損耗皆大於10dB,增益約為12±1 dB,最低雜訊指數為3.3 dB,在5.5 GHz及10.5 GHz的P1dB增益壓縮點分別 為-15.7 dBm和-9 dBm,IIP3截斷點分別為-6.6 dBm和-1.7 dBm;第二部份 為多頻帶低雜訊放大器(多頻帶輸入匹配),適用於WiMax 無線網路,工 作頻率為2.4/3.5/5.2 GHz,量測結果如下所述:輸出返回損耗皆大於10 dB,輸入返回損耗分別為8.7/10.7/9.3 dB,增益在分別為6.9/15.3/6.3 dB, 雜訊指數分別為4.2/4.4/6.3 dB;第三部份為多頻帶低雜訊放大器(多頻帶輸 出匹配),適用於WiMAX 無線網路,其模擬結果如下所述,工作頻率為 2.4/3.5/5.2 GHz : 輸 入 返 回 損 耗 大 於 10 dB , 輸 出 返 回 損 耗 分 別 為 10.1/19.5/13.7 dB , 增 益 在 分 別 為 13.6/13.1/9.4 dB , 雜 訊 指 數 分 別 為 3.0/2.8/3.3 dB,在2.4/3.5/5.2 GHz的P1dB增益壓縮點分別為-13.6/-11.8/-8.7 dBm,IIP3分別為-1.2/2.6/4.3 dBm。

Low Noise Amplifier for Ultra Wideband System

And WiMAX Wireless Network

student:Yuh-Chuan Cheng

Advisors:Dr.

Shyh-Jong Chung

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

ABSTRACT

This thesis presents the development of CMOS RFIC’s for Ultra Wideband system and WiMax System with TSMC 0.18um 1P6M CMOS processes. The first part studies on the UWB LNA for ultra wideband system, where the range of band is 3.1 ~ 10.1 GHz. The simulated performances are as follows: input and output return loss are greater than 10 dB, gain is about 12±1 dB, minimum noise figure is 3.3 dB,input power at 1dBgaincompression points are -15.7 dBm @ 5.5 GHz and – 9 dBm @ 10.5 GHz, input third intercept points are -6.6 dBm @ 5.5 GHz and – 1.7 dBm @ 10.5 GHz..

The second part studies on multi-band LNA design with multi input matching network for WiMax wireless system. The frequencies are 2.4/3.5/5.2 GHz, and the measurement performances as follows: output return loss are greater than 10 dB, gains are 10.1/15/10.1 dB, noise figures are 3.1/3.8 /4.3 dB.

The third part studies on multi-band LNA design with multi input matching network for WiMax wireless system. The frequencies are 2.4/3.5/5.2 GHz, and the simulated performances as follows: input return loss are greater than 10 dB, output return losses are 10.1/11.8/8.7 dB,gains are 13.6/13.1/9.4 dB, noise figures are 3.0/2.8/3.3 dB, 1dB gain compression points are -13.6/-11.8/-8.7, input third intercept points are -1.2/2.6/4.3 dBm.

誌 謝

能有機會再度進入學校求學,是一件很幸福的事情。在研究所進修的這段期 間,因為有老師和學長的指導、同學間的相互勉勵,以及課後的餐聚與旅遊活動, 讓我的生活變得更加多采多姿。 此次能順利完成論文,首先最要感謝的是指導教授--鍾世忠教授。不僅提供我 們一個優質的研究環境以利學習成長,更在研究方面給予細心的指導與方法的提 點,因而順利的踏進微波的領域。另外也要感謝口試委員孟慶宗教授、邱煥凱教 授及黃天偉教授的不吝指導,使我的論文內容更臻於完善。 還要感謝 Lab810 的夥伴們:佩宗學長及清標學長,在電路設計及 IC 製作的 指導和建議。顯鴻、唐源、竣義、換能、敦智在課業上互相的砥礪與下線時的協 助及精神上鼓勵,讓我順利的完成第一次的下線。還有天健學弟,在下線的緊要 關頭幫我傳檔給 CIC。同時也感謝同事黃國貞博士及陳興博士對於在學期間的鼓勵 及研究方法的指導。因著大家的幫忙,才能順利地完成電路的製作。 最後要感謝的是我的家人,特別是我的父母、妹妹馨儀與未婚夫俊仁,因為 有你們的支持,才讓我有充份的時間完成學業與研究。謹以此論文獻給所有幫助 與關心我的人。 郁娟 2007年1月 於新竹目

錄

中文摘要

………

I

英文摘要

………

II

誌謝

………

III

目錄

………

IV

表目錄

………

VII

圖目錄

………

VIII

一、

緒論………

1

1.1 研究動機………

1

1.2

研究成果………

1

1.3

章節概述………

2

二、

無線通訊系統介紹………

3

2.1

接收機………

3

2.1.1

超外差接收機架構(Superheterodyne Receiver)………

3

2.1.2

直接降頻接收機架構(Direct-Conversion Receiver) ………

4

2.1.3

鏡像消除接收機架構(Image-Rejection Receiver)…………

7

2.2

超寬頻(Ultra-Wide band,UWB)………

9

2.2.1

RF 傳送端簡介………

12

2.2.2

RF 接收端簡介………

13

2.3

WiMAX………

13

三、

CMOS Low Noise 之設計………

16

3.1

放大器的架構………

16

3.2

電晶體雜訊模型………

17

3.2.1

通道熱雜訊(channel thermal noise)………

17

3.2.2

超額雜訊(excess noise)………

18

3.2.3

分佈閘極電阻雜訊(distributed gate resistance noise)…

18

3.2.4

感應閘極電流雜訊(induced gate current noise)…………

18

3.2.5

顫抖雜訊(flicker noise) ………

19

3.3

1dB 壓縮點………

20

3.4

交互調變失真………

21

3.5

TSMC 0.18um 1P6M CMOS 製程元件簡介………

22

3.5.1

NMOS 電晶體………

22

3.5.2

MIM 電容………

23

3.5.3

螺旋式電感………

24

3.5.4

Bond-wire 及 pad………

26

3.5.5

電阻………

26

3.5.6

EM 模擬效應模擬………

27

四、

寬頻放大器的設計………

30

4.1

寬頻放大器理論基礎………

30

4.1.1

電阻回授寬頻輸入匹配………

30

4.1.2

LC-ladder 寬頻輸入匹配………

31

4.2

寬頻放大器的設計及製作………

33

4.2.1

串聯諧振匹配法………

33

4.2.2

並聯諧振匹配法………

36

4.2.3

轉正動作………

37

4.3

寬頻放大器的設計………

38

4.3.1

電路架構………

38

4.3.2

輸入匹配………

39

4.3.3

輸出匹配………

45

4.3.4

Cascode 架構的輸出負載………

45

4.4

模擬結果 ………

46

4.4.1

穩定圓 ………

47

4.4.2

S parameter………

47

4.4.3

Noise Figure………

48

4.4.4

P

1dB………

49

4.4.5

IIP3 ………

50

4.4.6

規格整理………

51

4.4.7

與其他論文比較

52

4.5

量測結果及結果討論………

53

4.6

未來工作………

56

五、

多頻帶低雜訊放大器設計理論………

57

5.1

多頻帶低雜訊放大器的基本架構………

57

5.2

輸入匹配………

57

5.2.1

多單頻輸入匹配………

57

5.2.2

雙頻輸入匹配………

59

5.3

輸出匹配………

61

5.3.1

多接頭電感負載輸出匹配………

61

5.3.2

LC 並聯諧振負載………

61

5.3.3

LC 阻抗匹配網路………

62

5.3.4

多頻帶輸出網路………

62

5.4

多頻帶放大器的設計及製作(多頻帶輸入匹配)………

63

5.4.1

電路架構………

63

5.4.2

輸入匹配………

64

5.4.3

輸出匹配………

65

5.4.4

模擬結果………

66

5.4.5

量測結果………

72

5.5

多頻帶放大器的設計及製作(多頻帶輸出匹配)………

78

5.5.1

電路架構………

78

5.5.2

輸入匹配………

79

5.5.3

輸出匹配………

80

5.5.4

模擬結果………

81

5.5.5

與其他論文比較………

89

5.5.6

未來工作………

90

六、

結論………

91

參考文獻

………

92

表 目 錄

表 1 已完成之射頻放大器電路設計……… 2 表 2 CDMA 和多頻段 OFDM 的比較表 ……… 12 表 3 IEEE802.16a 數據傳輸速率……… 15 表 4 標準型電感的尺寸調整範圍表……… 25 表 5 SA 電阻、RPO 電阻、HRL 電阻的尺寸調整範圍表……… 27 表 6 寬頻低雜訊放大器規格整理……… 51 表 7 寬頻低雜訊放大器與其他論文的比較……… 52 表 8 多頻帶放大器(多頻帶輸入匹配)模擬預計規格表……… 72 表 9 多頻帶放大器(多頻帶輸入匹配)量測總表……… 77 表 10 多頻帶放大器(多頻帶輸出匹配)模擬預計規格表……… 89 表 11 多頻帶放大器與其他論文的表……… 90圖 目 錄

圖 1 超外差接收機架構……… 3 圖 2 直接轉換接收機架構 ……… 4 圖 3 直流偏移的成因(a)本地振盪信號洩漏到放大器(b)放大器的輸出訊號 洩漏到本地振盪信號……… 5 圖 4 偶次階失真的效應 6 圖 5 I/Q 不匹配的分佈情形 7 圖 6 QPSK 信號的星狀圖(a)增益誤差(b)相位誤差 7 圖 7 Hartley 鏡像抑制接收機 8 圖 8 Weaver 鏡像抑制接收機 ……… 9 圖 9 UWB 的頻譜功率限制 9 圖 10 UWB 使用的頻譜 ……… 10 圖 11 MB-OFDM 頻寬規劃……… 11 圖 12 DSSS UWB 傳送端架構圖……… ……… 12 圖 13 MB-OFDM UWB 傳送端架構圖……… 13 圖 14 Wimax 頻譜分配情形 ……… 14 圖 15 IEEE802.16a 架構……… 15圖 16 resistive termination amplifier ……… 16

圖 17 m g 1 termination amplifier……… 16

圖 18 shunt-series feedback amplifier……… 17

圖 19 inductive degeneration amplifier……… 17

圖 20 CMOS 雜訊模型……… 18 圖 21 感應閘極雜訊(a)感應閘極雜訊電流示意圖 (b)等效雜訊電流源…… 19 圖22 氧化層與矽基板的不連續鍵結……… 20 圖 23 1dB 增益壓縮點……… 20 圖 24 非線性系統中的交互調變……… 21 圖 25 Two tone 測試交互調變失真……… 21 圖 26 RF NMOS transistor(a)NMOS 佈局圖(b)等效電路模型……… 23 圖 27 MIM 電容佈局示意圖……… 23 圖 28 電容等效電路模型(a)sheild (b)沒有 sheild……… 24 圖 29 標準型電感(a) 電感佈局 (b)標準型電感等效電路模型……… 26 圖 30 Bond-wire 及 pad 近似模型……… 26 圖 31 電阻佈局及等效電路模型……… 27 圖 32 跑線效應的模擬結果(a)birdview (b)收斂測試(c)跑線的 S 參數……… 29 圖 33 電阻回授寬頻輸入匹配(a)輸入匹配網路(b) 輸入匹配網路小訊號等效 模型……… 30 圖 34 LC 低通濾波器輸入阻抗與頻率的對應圖……… 31 圖 35 由低通網路轉換成的帶通網路……… 32 圖 36 帶通濾波器輸入阻抗與頻率的對應圖……… 32 圖 37 LC-ladder 寬頻輸入匹配(a)輸入匹配網路(b)基極端高頻等效電路… 33 圖 38 串聯諧振電路……… 33

圖 40 負載與串聯諧振腔相接……… 34

圖 41 ZL加串聯諧振後的阻抗匹配狀況……… 35

圖 42 Zx在 Z-Smith Chart 的走勢……… 35

圖 43 Zx轉成 Y-Smith Chart 的走勢……… 35

圖 44 並聯諧振電路……… 36

圖 45 負 Yp (a)示意圖 (b)在 Z-Smith Chart 的走勢……… 36

圖 46 負載 YL與並聯諧振腔相接……… 37 圖 47 ZL加串聯諧振後的阻抗匹配狀況……… 37 圖 48 將 ZL做轉正動作至 Zin……… 37 圖 49 將 ZL做轉正動作……… 38 圖 50 LNA 的系統方塊圖……… 38 圖 51 LNA 電路設計圖……… 39 圖 52 輸入匹配網路等效電路圖……… 39 圖 53 並聯諧振產生寬頻的輸入匹配……… 40 圖 54 S11 的 Smith Chart……… 40 圖 55 電晶體(尺寸為 W=4.5,L=0.18,n=40)閘極阻抗的 Smith Chart…… 41 圖 56 電晶體的閘極端加電感(L3) ……… 41 圖 57 電晶體加入電感 L3 後輸入端阻抗的 Smith Chart 42 圖 58 電感(L3)對寬頻放大器 S11 的影響(a)未加入電感(L3)(b)電感(L3)值很 小(c)電感(L3)值適當 的 S11 的 Smith Chart 44 圖 59 M3 的 Gate 端加 L3 與 Gate 端不加 L3 的增益比較……… 44 圖 60 輸出匹配電路圖……… 45 圖 61 inductive – paeking 的示意圖……… 45 圖 62 穩定圓的模擬圖……… 47 圖 63 S11、S21、S22 的模擬圖……… 47 圖 64 S12 的模擬圖……… 48 圖 65 Noise Figure 的模擬圖……… 48 圖 66 P1dB的模擬圖 @ 5.5 GH……… 49 圖 67 P1dB的模擬圖 @ 10.5 GHz……… 49 圖 68 IIP3 的模擬圖@ 5.5 GHz……… 50 圖 69 IIP3 的模擬圖 @ 10.5 GHz……… 50 圖 70 寬頻帶低雜訊放大器佈局圖 ……… 53 圖 71 寬頻帶低雜訊放大器量測照片圖 ……… 54 圖 72 量測結果與模擬比較圖輸入(a)反射係數 S11(b)隔離度 S12(c)增 S21(d) 輸出反射係數 S22……… 55 圖 73 修改後的 Layout 圖……… 56 圖 74 多頻帶低雜訊放大器……… 57 圖 75 多單頻輸入匹配架構……… 57 圖 76 單頻放大器 (a)電感源極回授 (b)電感源極回授輸入端的小訊號模型 58 圖 77 雙頻輸入匹配架構……… 59 圖 78 雙頻輸入匹配輸入阻抗的等效電路……… 59 圖 79 雙頻輸入匹配輸入阻抗等效電路的小訊號模型……… 60 圖 80 多接頭電感負載輸出匹配……… 61 圖 81 LC 並聯共振腔……… 62

圖 82 LC 阻抗匹配網路……… 63

圖 83 多頻帶輸出匹配網路(a)架構 1(b)架構 2……… 63

圖 84 Triple Band LNA 的系統方塊圖……… 64

圖 85 多頻帶放大器(多頻帶輸入匹配)最終電路設計圖……… 64

圖 86 輸入匹配的設計(a)單頻輸入匹配(b)多頻輸入匹配單……… 65

圖 87 輸出匹配電路圖……… 66

圖 88 Dual band mode 穩定圓的模擬圖……… 66

圖 89 Dual band mode S11、S21、S22 參數的模擬圖……… 67

圖 90 Dual band mode S12 的模擬圖……… 67

圖 91 Dual band mode 雜訊指數的模擬圖 ……… 68

圖 92 P1dB的模擬圖 @ 2.4 GHz……… 68

圖 93 P1dB的模擬圖 @ 5.2 GHz……… 69

圖 94 Single band mode 穩定圓的模擬圖……… 69

圖 95 Single band mode S11、S21、S22 參數的模擬圖……… 70

圖 96 Single band mode S12 參數的模擬圖……… 70

圖 97 Single band mode 雜訊指數的模擬圖……… 71

圖 98 P1dB的模擬圖 @ 3.5 GHz……… 71

圖 99 多頻帶放大器(多頻帶輸入匹配)佈局圖……… 72

圖 100 Dual band mode S 參數量測結果(a)S11(b)S21(c)S22……… 74

圖 101 Dual band mode 雜訊指數量測結果……… 75

圖 102 Single band mode S 參數量測結果(a)S11(b)S21(c)S22……… 76

圖 103 Single band mode 雜訊指數量測結果……… 77

圖 104 多頻帶放大器(多頻帶輸出匹配)的系統方塊圖……… 78 圖 105 多頻帶放大器(多頻帶輸出匹配)電路圖……… 79 圖 106 寬頻輸入匹配電路……… 79 圖 107 開關 SW1、SW2 同時短路時,輸出電路的等效電路圖……… 80 圖 108 開關 SW1、SW2 同時斷路時,輸出電路的等效電路圖……… 80 圖 109 輸出匹配的 Smith Chart 電路圖……… 81

圖 110 Dual band mode 穩定圓的模擬圖……… 82

圖 111 Dual band mode S 參數的模擬圖……… 82

圖 112 Dual band mode 雜訊指數的模擬圖……… 83

圖 113 P1dB的模擬圖 @ 2.4 GHz……… 83

圖 114 P1dB的模擬圖 @ 5.2 GHz……… 84

圖 115 IIP3 的模擬圖 @ 2.4 GHz……… 84

圖 116 IIP3 的模擬圖 @ 5.2 GHz……… 85

圖 117 Single Band Mode 穩定圓的模擬圖……… 85

圖 118 Single Band Mode S 參數的模擬圖……… 86

圖 119 Single Band Mode 雜訊指數的模擬圖……… 86

圖 120 P1dB的模擬圖 @ 3.5 GHz……… 87

圖 121 IIP3 的模擬圖 @ 3.5 GHz……… 87

一、 緒論

1.1 研究動機

追求自由自在的生活,是人類的天性。通訊技術的發展,從電話線的 Modem 到 Cable 和 ADSL,以及近兩年快速發展的 WiFi 到最近的 WiMax。除了通訊內容和應用 不斷的發展外,訊息溝通的功能也從文字轉變為音訊,然後進步到可傳遞圖像及影片, 甚至與資訊網路連接,取得更多資訊,無線通訊市場近幾年來發展的相當地快速,可 以預期的是在往後的日子中,無線通訊會在我們的日常生活中佔據著更重要的地位。 而射頻積體電路更是無線通訊中不可或缺的一個部份,目前在大城市無線網路已經可 以提供寬帶連接速度[1],但是接收寬帶信號的設備對於個人用戶而言價位偏高,往往 只有大企業才有能力負擔。目前,美國的電腦和通信公司已經逐漸在 WiMax 標準上達 成一致,也許不久的將來無線寬帶的成本將會大幅度下滑。 隨著 CMOS 製程技術的進步,CMOS 在元件上已可以達到高頻電路的要求,又加 上射頻電路的研發將使得多模態系統不只是空談,系統 on-chip 儼然已成為未來無線通 訊市場的趨勢。UWB 將成為無線通訊的新寵兒,未來可能廣泛的使用在生活中,使生 活更便利。本論文的第一部份研究將以此方向來設計 LNA,LNA 是進入 UWB 系統的 第一級,好的 noise figure 及頻寬寬的放大器將使系統的性能表現得更好,藉由此次的 研究來設計出更寬頻而且低雜訊的放大器;第二部份的研究為 WiMax 系統三頻帶低雜 訊放大器的研究,工作頻率分為三個頻段,2.3 ~ 2.7 GHz、3.3 ~ 3.8 GHz 及 4.9 ~ 5.9 GHz;在這三個頻段內,我分別選擇了 2.4 GHz、3.5 GHz 及 5.2 GHz 做為多頻帶放大 器的三個主頻,其中 2.4 GHz 及 5.2 GHz 與 WiFi 的頻段重疊,也可利用在 WiFi 的系 統;藉由此次的研究來設計出多頻帶低雜訊放大器。

1.2 研究成果

表 1 所列,為本論文已完成之射頻放大器電路設計,而各電路之理論及詳細之設 計內容,分別會在第三、四、五章中被敘述。表 1 已完成之射頻放大器電路設計 電路編號 電路名稱 頻率(GHz) 面積(mm2) 1 超寬頻低雜訊放大器 3.1 ~10.1 0.80 × 0.80 2 多頻帶放大器的設計及製作 (多頻帶輸入匹配) 2.4/3.5/5.2 0.98 × 0.94 3 多頻帶放大器的設計及製作 (多頻帶輸出匹配) 2.4/3.5/5.2 0.95 × 0.80

1.3 章節概述

本論文分為六個章節,第一章:敘述無線通訊發展的趨勢,以及論文之研究動機 與成果。第二章:介紹 UWB、WiFi 及 Wimax 系統的架構,發展趨勢及優缺點。第三 章:探討低雜訊放大器的基本架構、電晶體雜訊模型、線性度及簡介 TSMC 0.18um 1P6M CMOS 製程元件。第四章:敘述寬頻低雜訊放大器的設計原理及電路架構,說 明模擬結果,並探討量測結果無法達到寬頻的原因。第五章:敘述多頻帶低雜訊放大 器的設計原理及電路設計架構,說明模擬與量測的結果。第六章:本章為結論,說明 本論文研究之成果。二、 無線通訊系統介紹

無線通訊中[2],我們必須將所接收到的類比電波訊號,轉成數位訊號,再經過訊號處 理的方式,才能成為有用的資訊。而將類比訊號轉為數位訊號的方塊稱為類比至數位轉換 器(analog-to-digital converter,ADC)。實際的ADC因有取樣速率與動態範圍的限制,必須透 過射頻接收機,處理由天線接收到的微弱高頻電波訊號。在設計接收機時,不同的接收機 架構各有其特性及應用範圍,視系統規格的考量而定,一般考量的重點在於接收機的成本、 消耗功率、外加元件數目以及複雜度。本章將對於幾種常見的接收機架構作一簡述[2] [3] [4]。2.1 接收機

2.1.1 超外差接收機架構(Superheterodyne Receiver)

圖1 超外差接收機架構 於西元1918年,超外差接收機架構由Armstrong提出之後,此一接收機架構對 於系統設計者而言,影響深遠,時至今日無論是在工業界或是在學術界,此一架構 仍有多種改良及應用。適用於多種通訊協定之接收機的實現,其主要優點為具良好 的訊號選擇性(selectivity)以及靈敏度(sensitivity),其基本架構如圖1 所示。此種接 收機架構的工作原理[5] [6],是將外界接收到的高頻(RF)訊號,經過混頻器與本地 振盪(LO)訊號產生混頻,將原本高頻(RF)訊號轉換為較低頻的訊號,通常稱之為中 頻(IF)訊號(Intermediate Frequency)。IF訊號的中心頻率對接收機來說是一個關鍵性 參數,通常要跟接收機的其他各方面性能,做適當地調整始能有預期的性能。但缺 點是需要較多額外晶片的元件,因此成本也相對提高許多。2.1.2 直接降頻接收機架構(Direct-Conversion Receiver)

由於直接轉換架構的本地振盪頻率與射頻頻率相同,因此沒有鏡像頻率的問 題,所以不需要在混頻器前加一個鏡像濾波器。因為沒有中頻,故不需要在混頻 器後加上一個頻道選擇濾波器和中頻放大器,取而代之的是一個低通濾波器。因 此直接轉換架構比超外差架構所需的元件還要少,也易於將整個接收機整合為單 一晶片,接收機架構如圖2 所示。雖然直接降頻接收機有以上優點且架構簡單, 但過去未被普遍使用,原因有下列幾點。 圖2 直接轉換接收機架構 1. 直流偏移(DC Offset) 由於電容與基板耦合及鎊線耦合(Bonding wire)效應,混頻器的RF與LO的 隔離度是有限的。如圖3(a) 所示,當本地振盪信號洩漏到A點和B點時,洩漏的 信號將與本地振盪再次混頻並在C點混出直流信號;另一種情形是當較大的干 擾信號從B點洩漏到本地振盪 (Interferer Leakage),或者與同頻率的干擾訊號混 頻時,如圖3(b) 所示,也會在C點混出直流信號。這些現象稱為自我混頻 (Self-Mixing),自我混頻會使後級的主動電路飽和,或是干擾到所要處理的信號。圖3 直流偏移的成因(a)本地振盪信號洩漏到放大器 (b)放大器的輸出訊 號洩漏到本地振盪信號 2. 偶次階失真(Even-Order Distortion) 如圖4 所示,A1cos

ω

1t及A2cosω

2為兩個干擾信號,當它們很接近所要 的信號時,經過低雜訊放大器的非線性效應後,將會產生二階調變衍生信號, 若二階調變衍生信號很接近直流訊號,而且混頻器的RF-IF的隔離度不夠大,二 階調變衍生信號將經過混頻器漏到混頻器的輸出端,而對降頻後的基頻接收信 號造成干擾,此稱為偶次階失真。超外差式接收機的混頻器也同樣有此問題存 在,所以需要高線性度的低雜訊放大器和混頻器,以防止偶次階失真。圖4 偶次階失真的效應 3. 顫動雜訊(Flicker Noise) 電晶體的顫動雜訊屬於低頻雜訊,功率頻譜密度和頻率成反比(1/f),所以 顫動雜訊會使直接降頻至基頻訊號的訊號雜訊比降低,故一般在低雜訊放大器 及混頻器的地方把增益提高,減少顫動雜訊的影響,例如使用主動式混頻器來 取代被動式混頻器。 4 . I/Q信號的不匹配(I/Q Mismatch) 圖5 所示,實際上電路將會有I/Q不匹配的現象;當I/Q信號經過相位或是 增益不匹配電路時,I/Q信號的星狀圖(Constellation)會失真,位元錯誤率因此上 升。圖6(a)、(b) 是QPSK信號經過相位和增益不匹配電路時,所產生的失真星 狀圖。在超外差接收架構中,因I/Q信號是經由中頻降頻而成的,降頻的頻率比 在直接轉換架構中由射頻直接降頻的頻率還要來的低,且在分離I/Q信號後所用 的電路比在直接轉換架構中還要少,所以比較沒有I/Q不匹配的情形。

圖5 I/Q不匹配的分佈情形 圖6 QPSK信號的星狀圖(a)增益誤差(b)相位誤差

2.1.3 鏡像消除接收機架構(Image-Rejection Receiver)

另一種消除鏡像訊號的方式,乃利用鏡像抑制接收機。此類型的接收機可省 去在超外差接收機中所需之鏡像抑制濾波器,因此當接收機系統是以晶片方式來 製作時,此種鏡像抑制架構就能免除在晶片外掛一高Q值鏡像抑制濾波器的麻煩。 一般而言,常見之鏡像抑制架構有兩種:分別是Hartley架構及Weaver架構,兩種架構簡述如下。 1. Hartley架構 Hartley架構如圖7 所示,主要是由兩個具備有九十度相位相差的混頻器所 組成,此因混頻器的本地振盪器源是由兩個相差九十度的信號作為輸入所產 生。至於鏡像抑制的現象,則是使用混頻器與九十度相位轉移器對於I與Q兩路 徑之鏡像信號所造180度之相位轉移,最後用合成器做信號合成,使得鏡像信號 被消除。 圖7 Hartley鏡像抑制接收機 2. Weaver架構 在Hartley架構中,於一對具九十度相差混頻器之後放置九十度相移器,進 而達到鏡像抑制效果。但九十度的相移器是由被動元件所構成,傳遞訊號時會 有功率的耗損,且易因製程電容與電阻的變異量使得鏡像抑制效果大打折扣, 因此演化成Weaver鏡像抑制架構。其架構如圖8 所示,乃是使用九十度相差混 頻器取代九十度相移器,利用二次混頻將鏡像訊號消除。 Weaver鏡像抑制混頻器主要的優點是使用主動混頻電路取代被動的相移器。如 此,訊號在路徑中傳遞,將不會因被動電路而有衰減的現象;相對的,也因此 產生了二次鏡像干擾的問題。但是與Hartley架構相同,在I、Q兩路徑中,因增 益與相位的不匹配而降低鏡像抑制效果的因素依然存在。

圖8 Weaver鏡像抑制接收機

2.2 超寬頻(Ultra-Wide band,UWB)

Federal Communications Commission(FCC) 在 2002 年 2 月 14 日 發 佈 了 超 寬 頻 (Ultra-Wide band,UWB)技術的正式規範後,讓此技術將可在各種商品中得到廣泛的 應用。 圖9 UWB的頻譜功率限制 資料來源:[7] 在此規範下,無線超寬頻(UWB)技術可擁有超高頻寬,其實際的傳輸距離約為10 米,傳輸數據速率為110 Mbps到480 Mbps,超寬頻(UWB)所需要的消秏功率低,頻率

範圍在3.1~10.6 GHz間,UWB的頻譜功率限制如圖9 所示[7] ,功率發射被限制在-41.3 dBm/MHz,如圖10 所示[7]。由以上可知超寬頻(UWB)技術代表了無線技術高傳輸速 率時代來臨,這種高速率技術可廣泛應用於無線網路、家庭網路連接、短距離雷達等 應用中,如數位多媒體DVD、高畫質TV影像、衛星、電視機,並可實現數位相機、掃 描儀、印表機及MP3 player等設備與電腦之間的無線連接,取代目前的有線連接。透 過以上簡述的超寬頻(UWB)技術,我們從中可預見其巨大的市場潛力,將成為多媒體 消費性設備下一種流行的高速無線技術。 圖10 UWB使用的頻譜 資料來源: [7]

Federal Communications Commission(FCC)對超寬頻(UWB)技術的定義,為中心頻 率大於2.5 GHz,超寬頻系統至少需要500 MHz、-10 dB的頻寬,中心頻率在2.5 GHz以 下的超寬頻(UWB)系統則需要至少20%的頻寬比(fractional bandwidth)。透過傅立葉轉 換(Fourier Transform)的角度來看,訊號頻寬夠寬的話,相對於時域上的寬度就會很窄, 這時系統中的訊號已不再是週期性的弦波,而是寬度很窄的短脈衝訊號了,但也有使 用弦波被調變的超寬頻(UWB)系統。超寬頻的傳輸方式主要是利用脈衝(pulse)訊號進 行,因此功率的消耗將明顯降低。根據Channel Capacity理論:C=B*log2(1+S/N),當通 道的頻寬(B)愈大的時候,最大的傳輸速率(C)將會成等比級數的方式成長。因此 超寬頻的傳輸速率可高達100 Mbps,甚至有些技術較好的超寬頻系統其傳輸速率可高 達480 Mbps,傳輸速率未來將有可能提高至1 Gbps以上,可見得超寬頻技術在未來的 優勢。 而超寬頻技術標準可被分成兩類,一為單頻段直接序列CDMA(Direct sequence

CDMA) ,另一為多頻段OFDM(Multiband OFDM),但多頻段OFDM的支持者居多,以 下簡述這兩個標準的規格、比較及收、發機的架構。

1. 兩大門派超寬頻(UWB)技術標準

1.1 直接序列CDMA(Direct sequence CDMA)

直接序列CDMA是利用單脈衝(pulse)作為傳輸波形,單脈衝轉為頻域時,訊 號將為大頻寬訊號,簡單的說,直接序列CDMA是採用單頻段技術,由摩托羅拉 (Motorola)與XtremeSpectrum所力推的。

1.2 多頻段OFDM Multiband OFDM

Multiband OFDM將3.1~10.6GHz劃分成14個528MHz寬的子頻帶,前三個頻帶 是強制要求的,後四個高於5GHz的頻段是可選的。多頻段OFDM是由英特爾(Intel) 與德州儀器(Texas Instruments, TI)所帶領的MBOA聯盟,他們期望未來多頻段 OFDM技術能當成超寬頻的標準,MB-OFDM 頻寬規劃如圖11 所示,頻譜不再 一次使用整個頻帶來傳輸資訊而被分為若干子頻帶,子頻帶的頻寬約為500 MHz。透過各子頻帶的訊號交錯跳頻,UWB系統仍可以保持同樣的傳輸功能,而 使用的也是整個頻寬。 圖 11 MB-OFDM 頻寬規劃 2. 直接序列 CDMA 和多頻段 OFDM 比較表 直接序列 CDMA 和多頻段 OFDM 的比較,如表 2 所示

表 2 CDMA 和多頻段 OFDM 的比較表 多頻段 OFDM 直接序列 CDMA 主要領導廠商 英特爾(Intel)、德州儀器(Texas Instruments, TI)、諾基亞(Nokia) XtremeSpectrum/摩托 羅拉(Motorola) 技術 多頻段 單頻段 1.彈性 1.脈衝重複率低 2.低成本 2.較高傳輸速率 優點 3.與其他無線技術並存 3.抗干擾 資料來源:MBOA、DS-CDMA,Philips,2004 年 1 月

2.2.1 RF傳送端簡介

在此分別對這二大陣營的技術在傳送端(transceiver)和接收端(receiver)內的元 件討論其架構,並且針對設計的技術做比較,如在直接序列CDMA就對Pulse Generator多有著墨等,因為基本上直接序列CDMA就是在傳輸端(transceiver)產生 脈衝,使脈衝訊號傳輸出去,故Pulse Generator有分以串接delay blocks和一個XOR block來產生脈衝或是用四個可控制的CMOS PA來控制脈衝的波形,甚至利用將訊 號傳播出去的天線,以電流訊號經short dipole天線產生脈衝,在此亦可把short dipole天線視為Pulse Generator。圖12 就是為一個在直接序列CDMA傳送端的傳統 UWB架構。在傳輸端(transceiver)依設計所需求不同而加入其它不同元件,如filter 和PA等。圖12 DSSS UWB傳送端架構圖

個傳統的OFDM系統,除了載波頻率的改變是根據時頻(time-frequency)交錯 圖13 MB-OFDM UWB傳送端架構圖 的樣式之外,這個結構在TX部份有個Synthesizer,使訊號在不同的時間會使用不 同的頻段,並利用filter得到需求的波形,和直接序列CDMA一樣,傳輸端依設計 所需的不同加入filter和PA。

2.2.2 RF接收端簡介

這 兩 大 類 UWB 技 術 在 接 收 端 (receiver) 必 有 個 低 雜 訊 放 大 器 (Low Noise

Amplifier,LNA),將接收的訊號放大,並減少雜訊的干擾,所以在接收端重點將

是LNA的設計與討論,如要怎麼設計使之可以操作在3.1~10.6 GHz頻率範圍內,依 multi band OFDM的特性,亦可藉由改變LC負載,改變其操作中心頻率,使LNA 只需有500多MHz頻寬即可。 結合兩方面架構資料的結論,可幫助往後設計時概念的構想與建立。而單頻 段的優點在於增強了抗多路徑干擾的能力、其脈衝的重複率極低,因此能夠即時 的交替工作、以及提高傳輸的速度。多頻段擁有可滿足不同國家對於頻段使用的 彈性、消除窄頻的干擾、可使超寬頻與其他無線技術並存、以及成本較低等優點。

2.3

WiMAX

WiMAX 是 Worldwide Interoperability for Microwave Access 的縮寫[9],是「全球 互通的微波存取」標準,目前使用 IEEE 802.16 技術。WiMax 的設計是屬於都會型無 線網路(Wireless Metropolitan Area Networks,WMAN)的技術,所以在規格的彈性相 當大,但實際的應用必須考慮不同應用領域的差異。WiMax 802.16a 的傳輸距離將可 長達 50 公里[10],傳輸速率 74 Mbps,比起第三代行動通訊系統的傳輸速率 2Mbps,

更是快出許多。WiMAX 技術,將可克服無線區域網路僅 100 公尺傳輸距離及小的覆 蓋範圍,這兩方面不適用於移動通訊的不足。未來筆記型電腦無線傳輸距離可望更遠、 速率也會更快。目前 WiMAX 的頻段還未統一,各國最常見的頻段狀況為[9] : 1. 執照頻段(Licensed Band):

(1) 美國 WCS(Wireless Communication Services)頻段:2.305 - 2.320 GHz、2.345 - 2.360 GHz。

(2) 美國 MMDS(Multi-point Microwave Distribution System 或 Multi-channel Multi-point Distribution System)頻段:2.50 - 2.69 GHz。

(3) 國際 FWA(Fixed Wireless Access)頻段:3.4 - 3.7 GHz。

2. 免執照頻段(Unlicensed Band):

(1) 2.4GHz 工科醫(ISM)頻段:2.4000 - 2.4835 GHz。

(2) 5GHz U-NII(Unlicensed National Information Infrastructure)頻段:5.15 - 5.35 GHz、5.470 - 5.725 GHz、5.725 - 5.825 GHz。

WiMAX 頻譜分配情形如圖 14 所示。

圖 14 WiMAX 頻譜分配情形 資料來源:[9]

802.16a 所使用的頻段為 2 GHz 到 11 GHz,使用調變的方式為 OFDM (Orthogonal Frequency Division Multiplex),使用

(1)256 點快速傅立葉轉換的 OFDM (2)2048 點快速傅立葉轉換

(3)單一載波的傳送

64QAM,組成各種不同速率,如表 3 所示。 表 3 IEEE802.16a 數據傳輸速率 資料來源:[9] 圖 15 為 WiMAX802.16a 實體層發射器架構[9],802.16 使用了一些新的無線電技 術,包括在物理層上可使用單載波(Single Carrier,SC)、正交分頻多工(OFDM)或 正交分頻多重擷取(Orthogonal Frequency Division Multiplex Access,OFDMA)等載波 調變技術。在通道編碼(Channel Coding)採用 PRBS-15(Pseudo-Random Binary Sequence) 的方式 [11],接著使用前進錯誤編碼(Forward Error Coding)來保護資料,以交錯 (Interleaving)的方式提升接收機執行錯誤修正的效率。通道編碼之後進行調變,將資料 對應到使用的調變方式,接以 256 點反快速傅立葉轉換(IFFT),加上保護時間(Guard Time, Tg),Tb/Tg 可為 1/4,1/8,1/16 或 1/32,之後加上 Root Nyquist 濾波器,送至射 頻模組。

圖 15 IEEE802.16a 架構 資料來源 [9]

三、 CMOS Low Noise 之設計

3.1 放大器的架構

一般常見的放大器[12]大致可被歸類成 resistive termination (如圖 16 所示)、 m g 1termination (如圖 17 所示)、shunt-series feedback (如圖 18 所示)及 inductive degeneration (如圖 19 所示)四類,這四類型的架構簡介如下。 1. resistive termination 在閘極端並一個適當的電阻,提供 50 Ω的輸入阻抗,但這個架構因為並一個電 阻在輸入端,所以會使放大器的 noise figure 惡化。 2. m g 1 termination 使用 common-gate 架構的源極當作輸入端,輸入阻抗是從源極端看進去的阻抗, 其輸入阻抗約為 m g 1 。

圖 16 resistive termination amplifier 圖 17

m g 1 termination amplifier 3. shunt-series feedback 在閘極及汲極間串聯或並聯一回授電阻,來匹配放大器的輸入或輸出阻抗,此 類型的放大器有較小的 noise figure,但有較大的功率損耗。 4. inductive degeneration 在閘極及源極端各加一個電感,與電晶體閘極及源極間的的寄生電容 Cgs組合 後,將在輸入端產生實數的阻抗,此時的輸入阻抗 Zin,

s gs m gs g s in L C g sC L L s Z = ( + )+ 1 + ( 1) ,此類型的放大器為一窄頻的匹配,inductive degeneration 將在 5.2.1 將做一詳細說明。

圖 18 shunt-series feedback amplifier 圖 19 inductive degeneration amplifier

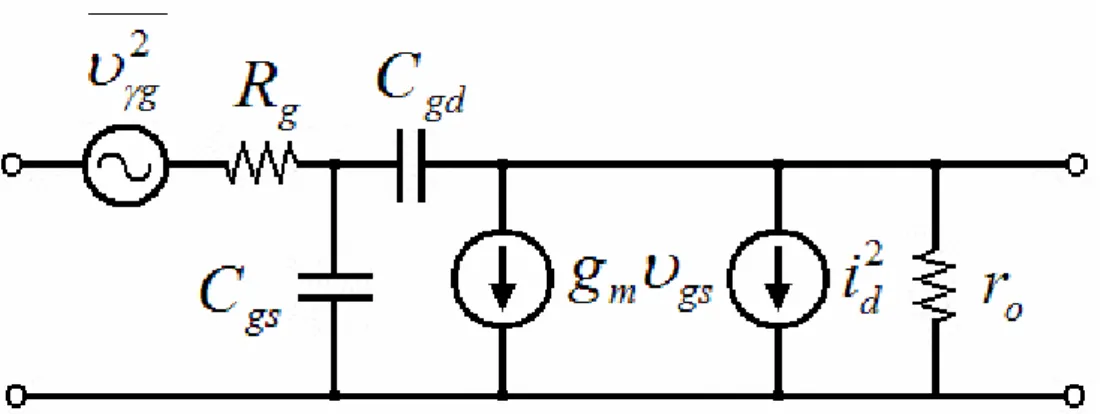

3.2 電晶體雜訊模型

3.2.1 通道熱雜訊(channel thermal noise)

標準的 CMOS 雜訊模型如圖 20 所示[12],CMOS 元件的雜訊主要來源為通道 熱雜訊,熱雜訊通常被模擬成在元件的輸出端,並聯一個電流源,雜訊是屬於 white noise,其 power spectral density 為

0 2 4 d d kT g f i = γ ∆ (1)

gd0是元件零偏壓時汲極電導值(zero bias drain conductance),γ是偏壓相依因子(bias

dependent factor),如果是長通道元件(long channel devices),必須滿足式(2)的 不等式, 1 3 2 ≤γ ≤ (2) 當元件在飽和狀態時,γ為 2/3,當源極及汲極間的電壓為零時,γ為 1;事實 上,工作在飽和區的短通道元件(short channel devices),γ值通常都遠大於 2/3, 也與偏壓的狀態有關。

圖 20 CMOS 雜訊模型

3.2.2 超額雜訊(excess noise)

高電場在次微米 MOS 元件引起超出晶格溫度的電子溫度(Te , electron temperature),使得通道上的載子被加熱,excess noise 可歸咎於存在在通道裏的熱 電子(hot electrons)。

3.2.3 分佈閘極電阻雜訊(distributed gate resistance noise)

在 MOS 的另一個雜訊源為分佈閘極電阻雜訊(distributed gate resistance noise) [12],這個雜訊源可被塑造成在閘極電路串上電阻及一白色雜訊(white noise)的產 生器,在指叉式的元件中,此項雜訊源將變得很小,在雜訊探討的用途上,distributed gate resistance 可被表示成式(3) L n R Rg 2 口 3 W = (3)

其中 R 是 polysilicon 的片電阻(sheet resistance),W 是元件閘極的總寬度,L 是 閘極的長度,n 是閘極的 finger 數。因此,在設計電路時,可用佈局技巧降低Rg ,

即可降低雜訊。

3.2.4 感應閘極電流雜訊(induced gate current noise)

圖21(a) 是MOS元件的橫截面[12],當電晶體受到偏壓而使通道反轉時,通道 內部擾動的電荷會經由電容耦至閘極而產生感應雜訊電流,圖21(b) 為包含感應效 應的閘極電路模型,包含並聯的雜訊電流( 2 g i )及電導(g ),其雜訊功率頻譜g 密度為: g g g kT f i δ 4 ) ( 2 = ∆ (4)

其中 0 2 2 5 d gs g g C g =ω (5) δ是閘極雜訊係數,在短通道情況下等於 4 / 3,因g 正比於g ω2,所以感應電流雜 訊並不是白色雜訊,而稱為藍色雜訊。也與i 與g i 有關,因此可把d i 分成與g i 相關d 部份及與i 不相關部份,且d i 與g i 相關係數d c≈0.395j,因此閘極感應雜訊電流可 表示為:

4

43

4

42

1

4

4 3

4

4 2

1

Correlated g ed Uncorrelat g gkT

g

c

kT

g

c

f

i

2 2 2|

|

4

)

|

|

1

(

4

)

(

∆

=

δ

−

+

δ

(6) (a) (b) 圖 21 感應閘極雜訊(a)感應閘極雜訊電流示意圖 (b)等效雜訊電流源 資料來源:[2]3.2.5 顫抖雜訊(flicker noise)

顫抖雜訊主要發生在低頻時[2],因電晶體閘極氧化層與矽基板接面,有許多 不連續懸吊的鍵結(dangling bonds),如圖22 所示,當載子在介面移動時,某些載 子將被隨機捕捉,並讓能階釋放,使得汲極電流產生閃爍雜訊。顫抖雜訊並不容易地預測出來,這與氧化層與矽基板接面之清潔度有關,也隨著不同的CMOS製程 技術而變化,但顫抖雜訊發生在頻率大於1 MHz以上,其影響將遠小於通道熱雜 訊,因此在射頻電路的製作上往往忽略其對整體雜訊的影響。又其雜訊頻譜密度 與 f 1 成正比,故又有 f 1 noise之稱。 圖22 氧化層與矽基板的不連續鍵結 資料來源:[2]

3.3 1dB 壓縮點

增益的壓縮與輸入的功率準位有關[13],當射頻信號輸入功率漸漸增加,增加到某 一程度時,會使得輸出功率不再輸入功率呈線性關係,放大器因而進入飽和狀態,如 圖23 所示。我們定義當輸出功率偏離此線性關係低1 dB時,稱之為“ 1-dB增益壓縮點 (1-dB compression point)”。

圖23 1dB增益壓縮點3.4 交互調變失真

當輸入端有兩個或兩個以上的信號,同時加入非線性的放大電路時,則在輸出信 號中,輸出將會出現非輸入頻率的諧波訊號,如圖24 所示。 圖24 非線性系統中的交互調變 資料來源[2] 因此,當輸入信號功率大到使輸出功率和第三階互調衍生信號輸出功率相同時, 此時三階互調衍生信號將嚴重干擾基頻之輸出信號,輸入信號功率的大小稱為Input Third-order Intercept Point (IIP3),輸出功率的大小稱為Output Third-order Intercept Point (OIP3) ,IIP3的計算如式(7),頻譜示意圖如圖25所示。一般而言,IP1dB與IIP 與的3 關係大約會相差10dB左右。 dBm in dB dBm P P IIP =∆ + 2 3 (7) 圖 25 Two tone 測試交互調變失真3.5 TSMC 0.18um 1P6M CMOS 製程元件簡介

在設計放大器時,必須要瞭解到每個元件的特性及模型,設計時才可以考慮到元 件的寄生效應。本論文電路製作,是採用國家晶片中心(CIC)所提供的 TSMC 0.18 µm 1P6M CMOS 製程,因此將介紹設計電路時,使用到元件模型的建立。本節內容及圖 均參考自 TSMC 0.18µm Mixed Signal/RF Salicide Design Rule[14]。

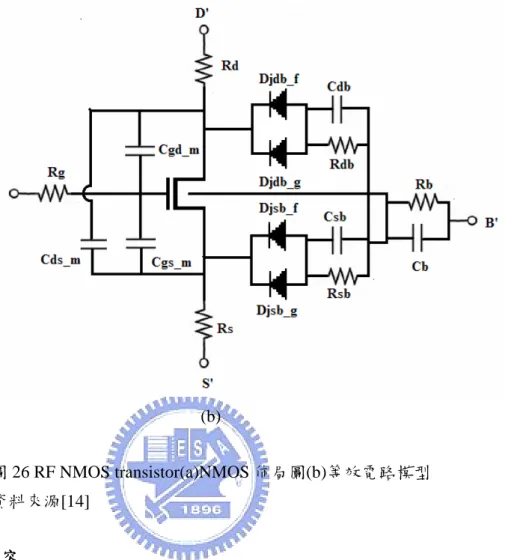

3.5.1 NMOS 電晶體

電晶體在元件佈局上採用多指叉(multi-finger)閘極架構,目的在於降低閘極電 阻,以提升元件高頻特性,如圖 26(a) 所示,等效電路模型如 26(b) 所示。1.8 V 的 N/PMOS,閘極的長度範圍為 0.18 ∼ 0.5 µm,每個 finger 的寬度度範圍為 1.5 ∼ 8 µm,finger 數目範圍為 1 ∼ 64 個,當元件的總工率超過 0.21 W 時,self-heating 效 應發生,將使元件的效率降低,所以最大功率上限為 0.21 W。 (a)(b) 圖 26 RF NMOS transistor(a)NMOS 佈局圖(b)等效電路模型 資料來源[14]

3.5.2 MIM 電容

TSMC 1P6M 0.18um 製程提供 MIM(metal-insulator-metal)電容,佈局架構示意 圖如圖 27 所示,係由絕緣層夾在二層金屬中間形成電容。分成有 shield 及沒有 shield 兩種,等效電路如圖 28(a)、 28(b) 所示。正方形及長方形的電容有下列幾種大小 30 um×30 um、25 um×25 um、15 um×15 um、10 um ×10 um、5 um×5 um、5 um×10 um、5 um×20 um、5 um×30 um、10 um×30 um、10 um×20 um 最小寬度 4 µm,最 大寬度 30 µm。圖 27 MIM 電容佈局示意圖

(a)

(b) 圖 28 電容等效電路模型(a)shield (b)沒有 shield 資料來源[14]

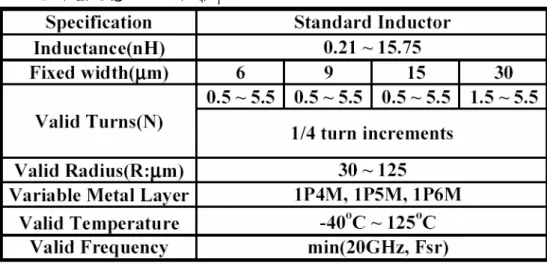

3.5.3 螺旋式電感

0.18um 製程提供的螺旋式電感在這只介紹標準形電感,標準形電感的佈局及 等效電路模型如圖 29 (a) 及 29 (b),尺寸調整範圍如表 4 所示,可改變圈數(N) 及半徑(R)去調整電感的值。

表 4 標準型電感的尺寸調整範圍表

資料來源[14]

(b)

圖 29 標準型電感(a) 電感佈局 (b)標準型電感等效電路模型 資料來源[14]

3.5.4 Bond-wire 及 pad

由於本論文電路量測是將晶片打鎊線至 FR-4 基板上,因此需先了解 bond-wire 及 pad 之等效電路模型。Bond-wire 通常可視為高 Q 值的電感,由 CIC 所給的資料 bond-wire 電感約為 0.8 nH/mm,等效串接電阻約為 0.16 Ω/mm,因此可把 bond-wire 模型化為電感串聯電阻。而 pad 可簡單的模型化為 0.15 pF 電容串聯 200 Ω電阻, 因此可把 3~4 mm 長度的 bond-wire 及 pad 近似模型成如圖 30 所示之等效電路。 圖 30 Bond-wire 及 pad 近似模型

3.5.5 電阻

0.18 µm製程提供的電阻有SA電阻、RPO電阻、HRL電阻,電阻的layout結構 如圖31 所示,尺寸調整的的範圍如表5 所示。圖 31 電阻佈局及等效電路模型 資料來源[14] 表5 SA電阻、RPO電阻、HRL電阻的尺寸調整範圍表 資料來源[14]

3.5.6 EM 模擬效應模擬

利用 HFSS 粹取較長跑線及 RF 訊號線之 EM 效應,將其跑線效應轉成 S2P 檔, 帶入電路加以模擬,圖 32(a) ~ (c) 分別為為其中一條跑線的模擬位置及結果。(a)

(c)

四、 寬頻放大器的設計

4.1 寬頻放大器理論基礎

現今的期刊,已發表很多篇有關寬頻放大器的製作,在此簡介與論文設計相關的 兩種寬頻輸入匹配,第一種為電阻回授輸入匹配[15];另一種為LC-ladder 輸入匹配[16] 。4.1.1電阻回授寬頻輸入匹配

(a) (b) 圖33 電阻回授寬頻輸入匹配(a)輸入匹配網路(b)輸入匹配網路小訊號等效模型 資料來源:[15] 圖 33(a) 為窄頻放大器結合並聯回授電阻,形成寬頻放大器,圖 33(b) 為輸入 匹配網路的小訊號模型,ωtLS的值將決定輸入阻抗的值,RfM為 Rf的米勒等效電 阻,RfM的值如式(8)所示 υ A R RfM = −f 1 (8) 其中 Aν為開迴路電壓增益,回授電阻的主要角色為降低窄頻輸入共振電路的 Q 值,如式(9)所示(

)

gs fM g S t S WB C R L L R Q ⋅ ⋅ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ + + ≈ 0 2 0 1 ω ω ω (9) 因此適當的選擇 Rf可將窄頻放大器轉成寬頻放大器。4.1.2 LC-ladder 寬頻輸入匹配

圖34 為一LC低通濾波器,在輸出的port接上電阻R,濾波器的截止頻率是ω0, 從輸入端的port看進去,當低於截止頻率ω0時,輸入阻抗(Zin)的值主要是電阻性, 且其值等於R,L與C的值分別為 0 ω R L= , R C 0 1 ω = 。 圖34 LC低通濾波器輸入阻抗與頻率的對應圖 資料來源:[16] 將L2串上C2取代圖34 的L,L1並上C1取代圖34 的C,便可將低通濾波網路轉 換成帶通濾波網路,轉換後的帶通網路如圖35 所示。圖35 由低通網路轉換成的帶通網路 資料來源:[16] 帶通濾波網路能在某一任意的頻段間,提供固定輸入電阻及增益,因而達到 寬頻輸入匹配,帶通濾波器輸入阻抗與頻率的對應圖如圖36 所示,ωL為低頻截止 頻率,ωU為高頻截止頻率, 帶通濾波網路中的L1、C1、L2與C2的值分別是 L R L ω ≈ 1 、 R C U ω 1 1 ≈ 、 R C l ω 1 2 ≈ 和 U R L ω ≈ 2 。 圖36 帶通濾波器輸入阻抗與頻率的對應圖 資料來源:[16]

(a) (b) 圖37 LC-ladder寬頻輸入匹配(a)輸入匹配網路(b) 基極端高頻等效電路 資料來源:[16] 圖 37(a) 為 LC-ladder 寬頻放大器,Zb為基極端看進去的阻抗,如圖 37(b) 所 示,圖 37(b) 的 LE、Cπ、ωTLE,分別等效圖 37 的 L2、C 2及 R,再加上並聯的 L1 及 C1,便形成了 LC-ladder 寬頻匹配。

4.2 寬頻放大器的設計及製作

這次寬頻的放大器設計,是採用諧振匹配法(The resonance matching technique) [17][18][19][20]的觀念來完成的,諧振匹配法的簡介如下:

4.2.1 串聯諧振匹配法

首先,先來回顧一下串聯諧振腔,串聯諧振電路如圖 38 所示。

串聯共振的阻抗為 ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = + = C L j C j L j Zs ω ω ω ω 1 1 (10) 0 = s Z 時,ω =ω0, ω0為串聯共振頻率; 當ω <ω0,Zs的電抗呈現電容性,也就是Zs =−jX; 當ω >ω0,Zs的電抗呈現電感性,也就是Zs =+jX。

如果有一個負載 ZL,如圖 39(a) 所示,它在 Z-Smith Chart 的走勢如圖 39(b) 所示,

(a) (b)

圖 39 負載 ZL (a)示意圖 (b)在 Z-Smith Chart 的走勢

這代表 ZL的電抗走向由低頻時的電感性,移至高頻時的電容性,因此在低頻時, 1 1 jX R ZL = + ,在高頻時,ZL =R2 − jX2,當負載移至實數軸時,ZL =R0,其中 R0、R1、R2、X1及 X2並不一定相等,若將負載 ZL與 LC 串聯諧振腔相接,如圖 40 所示,並適當的設計 L、C 的值,可以藉由諧振腔在低頻提供的 jX− 及高頻提 圖 40 負載與串聯諧振腔相接

供的+ jX,將 ZL 的+jX1及− jX2消掉,使得 Zin在 Z Smith Chart 上,有一接近實 數的值,阻抗的匹配如圖 41 所示。 圖 41 ZL加串聯諧振後的阻抗匹配狀況 若有一負載 Zx在 Z Smith Chart 的走勢如圖 42 所示,電抗的走向是由電容性 移動至電感性。串聯諧振的方法就不適用了,因此,我們將 Zx 在 Z Smith Chart 轉 180°,轉換成 Y Smith Chart。 圖 42 Zx在 Z-Smith Chart 的走勢 Zx在 Y Smith Chart 的走勢如圖 43 所示,將 Yx加上並聯諧振將與前述 ZL加 上串聯諧振的狀況有相同的效果,將在下一節描述並聯諧振的匹配方法。 圖 43 Zx轉成 Y-Smith Chart 的走勢

4.2.2 並聯諧振匹配法

接下來再來回顧一下並聯諧振腔,並聯諧振電路如圖 44 所示 圖 44 並聯諧振電路 並聯共振的導納為 ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = + = L C j L j C j Yp ω ω ω ω 1 1 (11) 0 = p Y 時,ω =ω0, ω0為並聯共振頻率; 當ω <ω0,Yp的電納呈現電感性,也就是Yp =−jB; 當ω >ω0,Yp的電納呈現電容性,也就是Yp =+jB。如果有一個負載 YL,如圖 45(a) 所示,它在 Z-Smith Chart 的走勢如圖 45(b) 所示,

這代表 YL的電納走向由低頻時的電感性,移至高頻時的電容性,因此在低頻時, 1 1 jB G YL = + ,在高頻時,YL =G2− jB2,當負載移至實數軸時,YL =G0,其中

圖 45 負 Yp (a)示意圖 (b)在 Z-Smith Chart 的走勢

G0、G1、G2、B1及 B2並不一定相等,若將負載 YL與 LC 並聯諧振腔相接,如圖

46 所示,並適當的設計 L、C 的值,可以藉由諧振腔在低頻提供的− jB 及高頻 提供的+ jB,將 YL 的− 及jB1 + jB2消掉,使得 Yin在 Y Smith Chart 上,有一接近 實數的值,阻抗的匹配如圖 47 所示。

圖 46 負載 YL與並聯諧振腔相接 圖 47 YL加並聯諧振後的阻抗匹配狀況

4.2.3 轉正動作

通常要設計匹配的頻寬,在頻寬內的阻抗不一定會剛好通過實軸,如圖 48 所 圖 48 將 ZL做轉正動作至 Zin示的 ZL,或者希望頻寬內的阻抗中點附近能剛好落在實軸上,如圖 48 所示的 Zin, 我們可以加電容、電感或傳輸線等元件,與 ZL相接,做一個轉正動作,示意圖如 圖 49 所示,將匹配頻寬的負載移至實軸處。 圖 49 將 ZL做轉正動作

4.3 寬頻放大器的設計

4.3.1 電路架構

CMOS LNA 的系統方塊圖如圖 50 所示,放大主體是採用電阻並聯回授的 Cascode,再加上 common-source 的輸出級所組成的。 圖 50 LNA 的系統方塊圖 電路設計圖如圖 51 所示,電路的設計如下所述。圖 51 LNA 電路設計圖

4.3.2 輸入匹配

LNA 設計的第一個步驟,是選擇電晶體的尺寸及偏壓點,讓 Noise Figure 達 到最小,再決定輸入匹配網的元件值,輸入匹配網路由 L1、CM、RM及 L3 所組成, 輸入小訊號等效電圖路如圖 52 所示,其中 CM及 RM為 C2、R1 的米勒等效電容 及電阻,分別為CM =C2

(

1−Aυ)

, υ A R RM − = 1 1 其中 A υ為 LNA 的開迴路電壓增益 [19],C2 也可以阻擋來自 Cascode 輸出端的電流[20],將 Cascode 放大級的輸出、 輸入的直流準位分開,讓電晶體 M3 的偏壓點能達到最佳化,同時使得 gm的值變 大,因此能降低功率的消耗及增加放大器的增益;50 Ω的匹配是由 RM決定的,適 當的調整 R1,能使輸入阻抗接近 50 Ω的匹配。 圖 52 輸入匹配網路等效電路圖L1、CM會產生並聯共振,利用共振前與共振後,所呈現的電感性及電容性的 電抗,去消掉待匹配電路的電抗,使得某段頻率間的阻抗,近乎是接近 50 Ω的實 數,從圖 53 可看出,S11 有一段軌跡繞著中心點,因而得到寬匹配。 圖 53 並聯諧振產生寬頻的輸入匹配 這次選用電晶體的尺寸為 W = 4.5,L = 0.18,n = 40,如圖 54 所示,ZGATE是 從電晶體的閘極端看進去的閘極阻抗,圖 55 為電晶體閘極阻抗的 Smith Chart。 。 圖 54 S11 的 Smith Chart

圖 55 電晶體(尺寸為 W = 4.5, L = 0.18,n = 40)閘極阻抗的 Smith Chart 為了做諧振輸入匹配,Gate 端的阻抗走向必須往電感性的方向延伸,讓實軸 能通過頻寬的中心附近,我們可以在閘極端加一電感 L3,如圖 56 所示,讓阻抗 的走向在 Smith Chart 往電感性的方向延伸,如圖 57 所示,L3 此時的功能如同前 一章節所提的 ″轉正″動作。 圖 56 電晶體的閘極端加電感(L3)

圖 57 電晶體加入電感 L3 後輸入端阻抗的 Smith Chart

圖 58(a)、(b)、(c)是加入 L3 對寬頻放大器 S11 的影響,圖 58(a) 是未加 L3 的 S11 ,圖 58(b) 加入值很小的 L3,圖 58(c) 所加的 L3 為最終設計,可發現高頻的 阻抗漸漸的往圓心集中,使得工作頻寬內的匹配效果變好,在不多消耗功率的情 況下,讓整體的增益提高,增益改善如圖 59 所示。

,

(a)

(c)

圖 58 電感(L3)對寬頻放大器 S11 的影響(a)未加入電感(L3) (b)電感(L3)值很小(c)電感(L3)值適當 的 S11 的 Smith Chart

4.3.3 輸出匹配

此級也有放大的作用,用來提高放大器整體的增益,電晶體(M4) Drain 端的負 載,是利用 NMOS 完成主動式負載,如圖 60 示,輸出負載等於 M3 從 soruce 端 看進去的阻抗,並聯 M4 從 Drain 端看進去的阻抗, Rout = 1/gm3 // ro4 ≅ 1/gm3, 將1/gm3設計約為 50 Ω,即可達到輸出端為 50 Ω的匹配。 圖 60 輸出匹配電路圖4.3.4 Cascode 架構的輸出負載

為了增加頻寬,Cascode 的輸出負載,使用 inductive -paeking 的方式來完成 如圖 61 所示,未加電感 L 的增益如式(12)示,加電感 L 的增益如式(13)示,

兩式比較後,加電感 L 會多出一個零點(zero)及一個極點(pole),零點將去抵 銷頻率較低的極點,留下頻率較高的極點,讓放大器的頻寬可以延伸。 1 1 ) 1 // ( ) ( + = = sRC R g sC R g s H m m (12) 1 1 ) / ( 1 // ) ( ) ( 2 + + + = ⎥⎦ ⎤ ⎢⎣ ⎡ + = sRC LC s R L s R g sC sL R g s H m m (13) 因電阻並聯回授 cascode 為主要放大級,所以流過的電流接近 6 mA,因此電 阻元件在實際應用上需要並聯 6 ~ 7 左右,而且電阻在製程上的飄移通常是很嚴重 的,因此 inductive -paeking 的電阻元件部分,我採 PMOS 來完成,如圖 51 的 M1, 將 PMOS 操作在深三極管區(deep triode region)[2],MOS 元件就像一個電阻, 不要讓 M1 的閘極電壓太大,才能確保所有電壓輸出的振幅,負載都能操作在深三 極管區,電阻 RON如式(14)所示。

(

DD b THP)

ox p on V V V L W C R − − = ) ( 1 µ (14)4.4 模擬結果

模擬結果如圖66 ~ 73與表5 所示,頻寬為3.1 ~ 10.1 GHz間,輸入與輸出返回損耗 皆大於10dB,增益為12 ± 1 dB,雜訊指數最小值為3.3 dB,在5.5 GHz及10.5 GHz的P1dB 增益壓縮點分別為-15.7 dBm和-9 dBm,IIP3截斷點分別為-6.6 dBm和-1.7 dBm。4.4.1 穩定圓

圖 62 穩定圓的模擬圖4.4.2 S parameter

2 4 6 8 10 12 14 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 Frequency(GHz) S11 S21 S22 圖 63 S11、S21、S22 的模擬圖0 2 4 6 8 10 12 14 16 -120 -100 -80 -60 -40 -20 S1 2 Frequency(GHz) S12 圖 64 S12 的模擬圖

4.4.3 Noise Figure

0 2 4 6 8 10 12 14 16 0 10 20 30 40 50 N o is e Figu re Frequency(GHz) Noise Figure NFmin 圖 65 Noise Figure 的模擬圖4.4.4 P

1dB -30 -25 -20 -15 -10 -5 0 0 2 4 6 8 10 12 14 G a in (dB) Input Power(dBm) 5.5 GHz 圖 66 P1dB的模擬圖 @ 5.5 GHz -25 -20 -15 -10 -5 0 4 5 6 7 8 9 10 11 G a in (dB) Input Power(dBm) 10.5 GHz 圖 67 P1dB的模擬圖 @ 10.5 GHz4.4.5 IIP3

圖 68 IIP3 的模擬圖@ 5.5 GHz

4.4.6 規格整理

規格列表如表 6 所示,僅以 CornerCase=TT 的模擬結果作為代表。 表 6 寬頻低雜訊放大器規格整理 Parameters (CornerCase=TT;Temperature=16.85°) Bandwidth (GHz) 3.1 ~ 10.1 S11 (dB) > 10 dB S21 (dB) 12 ± 1 S12 (dB) > 30 dB S22 (dB) > 10 dB NF (dB) 3.3 ~ 6 P1dB (dBm) -15.7@ 5.5 GHz;- 9 @ 10.5 GHz IIP3 (dBm) -6.6@ 5.5 GHz;- 1.7@ 10.5 GHz Power Consumption (mW) 16.5 Chip Size(mm × mm) 0.8 × 0.84.4.7 與其他論文比較

此次製作的寬頻低雜訊放大器模擬結果與其他論文比較,如表 7

所示。

4.5 量測結果及結果討論

寬頻帶低雜訊放大器佈局圖,如圖70 所示。 圖70 寬頻帶低雜訊放大器佈局圖 寬頻帶低雜訊放大器實際量測電路板如圖 71 所示,製作量測電路時,在不影響 鎊線及焊接的情況下,將傳輸線的長度盡量縮短,以減少傳輸線效應,並將電源電容 值變大,加強 AC 接地的效果。圖 71 寬頻帶低雜訊放大器量測照片圖 寬頻帶低雜訊放大器 S 參數量測結果與模擬如圖 72(a) ~ (d) 所示。 (a) (b) 電容值 傳輸線的 長度盡量

(c) (d) 圖 72 量測與模擬結果 (a)反射係數 S11 (b) 隔離度 S12 (c) 增益 S21 (d) 輸出反射係數 S22 量測與模擬之間結果比對,發現彼此有很大此落差,推測可能是模擬導線效應時, 因經驗不足,在搭配 HFSS 設定每層導線的介電參數時,考慮並不周詳,導致量測結 果無法達到寬頻的效果。

4.6 未來工作

對於本寬頻低雜訊放大器,未來電路製作建議如下 1.建立正確 chip 內部每層導線的介電參數。

2.DC 訊號可以利用 DC probe(on wafer)供應,就可以忽略 PCB 的跑線效應。 3.鎊線到 PCB 量測或 on wafer 量測,Layout 時應把 DC 訊號的 bypass 電容加大,讓

AC 訊號能有好的接地效果。 針對以上的建議修改 Layout,圖 73 為修改後的 Layout 圖。 圖 73 修改後的 Layout 圖 加大 DC 訊 號的 利用 DC 探針量測

五、多頻帶低雜訊放大器設計理論

5.1 多頻帶低雜訊放大器的基本架構

一般的多頻帶低雜訊放大器的基本架構如圖 74 所示,放大器的主體是 cascode amplifier,藉由架構不同的輸入或輸出匹配電路,達成多頻帶低雜訊放大器的設計,下 兩節將簡介發表在期刊上,多頻帶低雜訊放大器的輸入及輸出匹配電路。 圖 74 多頻帶低雜訊放大器5.2 輸入匹配

5.2.1 多單頻輸入匹配

圖 75 多單頻輸入匹配架構多單頻輸入匹配法[24],是將不同工作頻率的單頻放大器的輸入端並聯起來, 架構如圖 75 所示,當其中一組單頻低雜訊放大器工作時,其它組放大器的電晶體 將被關掉,每組單頻放大器是使用電感源極回授(inductive source degeneration)的架 構,如圖 76(a) 所示,小訊號等效電路圖如圖 76(b) 所示,輸入阻抗 Zin的推導如 式(15)所示[12], s gs m gs g s in L C g sC L L s Z = ( + )+ 1 +( 1) ≈ωTLs (at resonance)

(15) (a) (b) 圖 76 單頻放大器 (a)電感源極回授 (b)電感源極回授輸入端的小訊號模型 由式(15)得知,當輸入網路發生串聯共振時,阻抗為實數,而且正比於 LS, 所以適當的選擇 LS,可以讓輸入阻抗達到 50 Ω的匹配,通常 LS的值都不大,除了 可以使用製程提供的螺旋電感外,也可以使用 bond wire 來完成,依據式(15)我們 可算出不同頻率的 LS值,LS一但決定了,我們也就可以計算出 Lg的值,輸入匹配 網路的品質因素(quality)Qin ,如式(16)所示,是決定放大器功率消耗、增益、 雜訊、線性度重要參數。 0 0 2 1 Z C Q gs in = ω (16)

其中 C 是電晶體閘極及源極間的電容,gs ω0為工作頻率,Z 是特性阻抗,通常都0 設計在 50 Ω。多單頻輸入匹配的架構設計,是讓每個工作頻率都有自己專屬的輸 入匹配網路,因此輸入匹配可針對每個操作頻率作最佳化的設計,但此架構由許 多組單頻放大器組成,這也將使晶片的使用面積變大 。

![圖 14 WiMAX 頻譜分配情形 資料來源:[9]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8463842.183286/26.892.154.773.434.881/圖14WiMAX頻譜分配情形資料來源9.webp)

![圖 15 IEEE802.16a 架構 資料來源 [9]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8463842.183286/27.892.234.734.242.451/圖15IEEE8216a架構資料來源9.webp)

![圖 29 標準型電感(a) 電感佈局 (b)標準型電感等效電路模型 資料來源[14]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8463842.183286/38.892.160.777.157.412/圖29標準型電感a電感佈局b標準型電感等效電路模型資料來源14.webp)

![圖 31 電阻佈局及等效電路模型 資料來源[14] 表5 SA電阻、RPO電阻、HRL電阻的尺寸調整範圍表 資料來源[14] 3.5.6 EM 模擬效應模擬 利用 HFSS 粹取較長跑線及 RF 訊號線之 EM 效應,將其跑線效應轉成 S2P 檔, 帶入電路加以模擬,圖 32(a) ~ (c) 分別為為其中一條跑線的模擬位置及結果。](https://thumb-ap.123doks.com/thumbv2/9libinfo/8463842.183286/39.892.172.730.194.823/來源EM模擬效應模擬利用粹取較長跑線訊號加以模擬~分別為為.webp)