國立交通大學

材料科學與工程學系

碩士論文

以電鍍法製備高頻覆晶封裝用錫-銅击塊之研究

Preparation of Sn-Cu Bump for High-frequency Flip-chip

Bonding Utilizing Electroplating Process

研究生:王炯鑫

指導教授:謝宗雍 博士

以電鍍法製備高頻覆晶封裝用錫-銅击塊之研究

Preparation of Sn-Cu Bump for High-frequency Flip-chip

Bonding Utilizing Electroplating Process

研究生:王炯鑫 Student:Chon-Hsin Wang

指導教授:謝宗雍 博士 Advisor:Dr. Tsung-Eong Hsieh

國立交通大學

材料科學與工程學系

碩士論文

A Thesis

Submitted to Institute of Materials Science and Engineering Collage of Engineering

National Chiao Tung University in Partial Fulfillment of the Requirements

for the Degree of Master of Science in Materials Science and Engineering

Hsinchu, Taiwan, Republic of China

以電鍍法製備高頻覆晶封裝用錫-銅击塊之研究

學生:王炯鑫 指導教授:謝宗雍 博士 國立交通大學 材料科學與工程學系摘要

本研究藉由不同條件的電鍍製程製備符合高頻砷化鎵(GaAs)元件覆晶封 裝用高 50 m、直徑 50 m 的錫-銅接合击塊,電鍍實驗條件概分為定電流、定 電 壓 和 脈 衝 電 壓 , 完 成 之 击 塊 並 以 掃 描 式 電 子 顯 微 鏡 ( Scanning Electron Microscopy,SEM)與觀察其內部微觀結構及以推力測試分析击塊接合強度。定 電流實驗之結果顯示以電流密度 0.5ASD~1ASD 範圍執行電鍍,不論是否有加 入添加劑 PEG200,皆可獲得緻密性良好的击塊;在定電壓實驗中,加入添加劑 PEG200 確實可以改善击塊內部的緻密性,這是因為電流值會上升使鍍率升快, 增加孔洞的生成,而 PEG200 能抑制抑制還原反應、減緩沉積速率;另外發現脈 衝電壓法因鍍率太慢,不適合用來製備深孔電鍍。能量分散譜儀(Energy Dispersive Spectroscopy,EDS)對击塊內部的成分分佈顯示,不論是定電流析鍍 或定電壓析鍍,使用添加 PEG200 之鍍液所得之击塊內部的銅含量均減少。击塊 的推力測試(Shear test)顯示击塊與基板之剪力強度約在 40 Nt/mm2,大致符合 符合業界推力測試標準。Preparation of Sn-Cu Bump for High-frequency Flip-chip Bonding

Utilizing Electroplating Process

Student: Chon-Hsin Wang Advisor: Dr. Tsung-Eong Hsieh

Department of Materials Science and Engineering

National Chiao-Tung University

ABSTRACT

This study utilizes various electroplating processes to fabricate the Sn-Cu bumps with height and diameter both equaling to 50 m for the flip-chip bonding of high-frequency GaAs devices. The electroplating processes include galvanostatic, potentiostatic, and pulse-voltage methods. Afterward, scanning electron microscopy (SEM) and push test were adopted to characterize the microstructure and bonding strength of Sn-Cu bumps, respectively. In galvanostatic experiment, it was found that regardless of the addition of PEG200 additives in plating solution, the dense, nearly void-free bumps could be obtained in the current density ranging from 0.5ASD to 1ASD. In potentiostatic experiment, the increase of plating current increase the plating rate which, in turn, results in the void formation in the interior of bump. However, such plating defects could be effectively suppressed by adding PEG200 in plating solution. Energy dispersive spectroscopy (EDS) analysis revealed that reduction of Cu content in the bump when the plating solution contains PEG200. Shear test indicated that the shear strengths of bumps are about 40 Nt/mm2, satisfying the industrial requirement for practical usages.

誌 謝

感謝我的指導教授謝宗雍教授,老師在電子封裝這塊領域上,有著獨特的構 思和透徹的瞭解,悉心的指點我對實驗上的疑惑,並給予思考的方向,感激之情 難以言喻。 在研究的路上,遇到許多瓶頸,首先感謝虹君學姊能一一為我解答,提供諸 多的幫助和實驗建議,使本論文得以完成;還要感謝郁仁學長,能在我最失意、 最困惑的時候及時拉我一把,不時鼓勵我,並提供多方面的思考和意見;感謝沿 州同學帄時的砥礪。另外實驗室的其他成員當然也不能忘記,高手羽筠學姐、賀 昌、國璋和小麥、鴻鐘、凱第、謹聰、子欽與學弟,這兩年的日子有著你們的陪 伴,不論是實驗研究上的討論還是實驗室休閒活動,隨時提供歡樂搞笑,讓我每 天都很開心,我會銘記於心。感謝工研院電光所的建均學長,在工研院的一年, 不厭其煩的教導我,獲益匪淺;感謝工研院電子所的小陸先生,能提供實驗設備, 讓我得以完成實驗。感謝烏霖、鎮基、浩仰、季高、炯朝和永昌,帄常能有你們 這群好朋友的陪伴,日子不致枯燥乏味,我真的覺得很幸福。還要感謝雅榛,陪 我走過最後的碩士生活,增添了許多美好的回憶,被載也是一種幸福的。 最後僅把此論文獻給含辛茹苦撫養我長大的父母親,若沒有您們的督促、教 導,就不會有今日的我,您們是最偉大的父母親。目 錄 摘要... i ABSTRACT ... ii 誌謝... iii 目錄... iv 圖目錄... vi 表目錄... viii 符號表... ix 第一章 緒論... 1 第二章 文獻回顧... 2 2.1、電子封裝技術的演進... 2 2.2、覆晶封裝... 5 2.3、击塊的發展... 6 2.3.1、击塊製備技術... 6 2.3.2、適用於高頻元件之击塊... 10 2.4、電鍍... 11 2.4.1、電鍍的基本原理... 11 2.4.2、合金電鍍(Alloying Plating)[28] ... 14 2.4.3、直流與交流電鍍... 15 2.4.4、添加劑... 16 2.5、無鉛銲錫的發展... 17 2.6、研究動機... 19 第三章 實驗方法... 20 3.1、實驗流程... 20 3.1.1、基板前處理... 21 3.1.2、UBM 製作 ... 21 3.1.3、厚膜微影製程(Thick-film Lithography) ... 21 3.1.4、電鍍... 22 3.2、循環伏安法(Cyclic Voltammetry,CV)[48] ... 25 3.3、SEM 分析 ... 27 3.4、成份分析... 28 3.5、推力測試... 29 第四章 結果與討論... 31 4.1、鍍液的循環伏安分析... 31 4.2、電鍍條件對击塊形貌之影響... 33 4.2.1、定電流電鍍... 33 4.2.2、定電壓電鍍... 39

4.2.3、脈衝電壓電鍍... 43 4.3、EDS 分析 ... 46 4.4、推力測試... 50 第五章 結論... 55 第六章 未來研究與展望... 58 參考文獻... 59

圖目錄

圖 2.1、Moore‟s Law 的發展。[Source:Intel] ... 3

圖 2.2、矽晶圓加工尺寸發展趨勢。[Source:Intel] ... 3 圖 2.3、IC 封裝的演進。[13][14] ... 4 圖 2.4、三種最常見的晶片直接接合於電路板的方式(Chip-on-board,COB)。[14] ... 4 圖 2.5、現今封裝主要的趨勢。[Source:ITRI] ... 5 圖 2.6、覆晶接合的流程。[Source:IBM] ... 6 圖 2.7、击塊的基本架構。[17] ... 7 圖 2.8、一般常見击塊接合的形狀。[19] ... 8 圖 2.9、堆疊击塊的製程。[19,20] ... 9 圖 2.10、電場的分佈:左為微條線架構,右為共面波導架構。[24] ... 11 圖 2.11、電極表面上核形成與成長示意圖。[25] ... 12 圖 2.12、IC 導線與導孔三種填充模式。[33] ... 16 圖 3.1、實驗之流程圖。... 20 圖 3.2、光罩設計示意圖。... 21 圖 3.3、電鍍方式:左為掛鍍式,右為湧泉式。[21] ... 23 圖 3.4、電鍍裝置示意圖。... 23 圖 3.5、(a)初鍍完成之蘑菇狀击塊;(b)研磨後之柱狀击塊。 ... 25 圖 3.6、循環伏安之波形圖。... 26 圖 3.7、循環伏安之電流與電壓關係圖。... 26 圖 3.8、三極式循環伏安示意圖(開放式)。... 27 圖 3.9、SEM 試片製備流程。 ... 28 圖 3. 10、(a)Dage 2400 推力測試機;(b)錫球推力測試法示意圖。 ... 29 圖 3. 11、推力測試之六種破裂模式。[source:JESD22-B117] ... 30

圖 4.1、以(a)100 mV/sec(b)20 mV/sec 掃瞄速度測試之錫-10%銅鍍液循環伏 安圖;(c)為以 20 mV/sec 掃瞄速度測試之添加 PEG200 之錫-10%銅鍍 液循環伏安圖。 ... 32 圖 4.2、以(a)2ASD 與(b)3ASD 較高電流密度析鍍之击塊結構。 ... 33 圖 4.3、光阻厚度剖面分析圖。... 33 圖 4.4、以 0.5ASD 析鍍 3 小時之击塊形貌:(a)陰極面積 = 5.024103 cm2(b) 陰極面積 = 0.96 cm2。 ... 34 圖 4.5、以 1ASD 析鍍 3 小時,研磨後之击塊形貌。... 35 圖 4.6、不同定電流條件之鍍膜厚度對時間之變化:(a)0.5ASD(b)0.8ASD(c) 1ASD。 ... 35 圖 4.7、以電流密度 0.5ASD 析鍍之击塊形貌。... 36

圖 4.8、以電流密度 0.8ASD 析鍍之击塊形貌。... 37 圖 4.9、以電流密度 1ASD 析鍍之击塊形貌。... 37 圖 4.10、以電流密度 0.5ASD,電鍍液加 PEG200 析鍍之击塊形貌。 ... 37 圖 4.11、以電流密度 0.8ASD,電鍍液加 PEG200 析鍍之击塊形貌。 ... 38 圖 4.12、以電流密度 1ASD,電鍍液加 PEG200 析鍍之击塊形貌。 ... 38 圖 4.13、剛研磨完成之击塊頂端外擴現象。... 39 圖 4.14、以定電壓 100 mV 析鍍之击塊形貌;圈起處為孔洞位置。... 41 圖 4.15、以定電壓 150 mV 析鍍之击塊形貌;圈起處為孔洞位置。... 41 圖 4.16、以定電壓 200 mV 析鍍之击塊形貌;圈起處為孔洞位置。... 41 圖 4.17、以定電壓 100 mV,電鍍液加 PEG200 析鍍之击塊形貌。 ... 42 圖 4.18、以定電壓 150 mV,電鍍液加 PEG200 析鍍之击塊形貌。 ... 42 圖 4.19、以定電壓 200 mV、電鍍液加 PEG200 析鍍之击塊形貌。 ... 42 圖 4.20、一般電流與過電壓的關係。[29] ... 43 圖 4.21、定電壓下監測電流與時間的關係。... 43 圖 4.22、(a)10 Hz(b)100 Hz(c)10 kHz 脈衝電壓之設定波形與實際輸出波 形圖。 ... 44 圖 4.23、輸出源突然上升和下降,影響鍍層品質。... 45 圖 4.24、以(a)10 Hz(b)100 Hz(c)10 kHz 脈衝電壓析鍍之击塊橫截面 SEM 形貌。 ... 45 圖 4.25、以(a)定電流(b)定電壓(c)脈衝電壓析鍍之击塊外觀。 ... 45 圖 4.26、定電流電鍍完成之击塊(a)頂部(b)腰部(c)底部與(d)击塊整體 銅成分分佈圖。 ... 47 圖 4.27、錫-銅二元合金相圖。 ... 47 圖 4.28、以 0.55ASD 析鍍添加 PEG200 之鍍液所得之錫銅鍍膜之 DSC 分析。48 圖 4.29、定電壓電鍍完成之击塊(a)頂部(b)腰部(c)底部與(d)击塊整體 銅成分分佈圖。 ... 49

圖 4.30、(a)未添加 PEG200,以 110 mV 析鍍;(b)添加 PEG200,以 130 mV 析鍍所得之錫銅鍍膜 DSC 分析圖。 ... 49 圖 4.31、定電流析度之击塊推力強度分佈圖(a)0.5ASD(b)0.8ASD(c)1ASD。 ... 52 圖 4.32、定電壓析度之击塊推力強度分佈圖(a)100 mV(b)150 mV(c)200 mV。 ... 53 圖 4. 33、推力測試之 SEM 俯視圖:(a)未進行推力測試之前(b)(c)緻密性 好的击塊測試結果(d)(e)緻密性差的击塊測試結果(f)击塊黏著性 差。 ... 55

表目錄

表 2.1、無鉛系統。[43] ... 18 表 3.1、微影製程參數。... 22 表 3.2、電鍍條件參數。... 24 表 4.1、定電流析鍍完成之击塊的推力測試結果。... 51 表 4.2、定電壓析鍍完成之击塊的測試結果。... 51 表 4.3、無鉛系統的拉伸與剪力值。... 51 表 4. 4、有效與不良之击塊數目。... 54符號表

W:物質析出量 i:電流 t:時間 M:析出物分子量 n:電子轉移價數 F:法拉第常數 n M a :離子的活性 M a :電極的活性 T:溫度 R:氣體常數 E0:標準電極電位 M:活性係數 CM:離子濃度 :過電壓 E(i):產生電流 i 所施加的電壓 E(i=0):帄衡電壓 a 和 b:常數 iD:電流密度第一章

緒論

未來電子產品將朝向高速化、多功能化、小型化、輕薄化之趨勢發展,預期 將來的產品將以電腦通訊及多媒體等 3C 整合的產品產業為主流,因此不論是系 統業者、IC 產業、主被動元件業及電子材料均以可攜式、高速度、高功能及輕 薄短小化的產品技術為主要發展方向。就 IC 封裝的技術而言,一般常見的 IC 晶 片封裝技術是將晶片黏於導線架(Leadframe)上,再使用金線連接晶片的電極 與導線架上的引腳,最後再注模(Molding)將晶片封住。要達到高速化且輕薄 短小的目的,傳統封裝技術有其限制,就連線(Interconnetion)技術而言,如打 線接合(Wire Bonding,WB)等級無法有效提升封裝效益(Packaging Efficiency ),能省略第一層次封裝(First Level Packaging)的覆晶(Flip Chip,FC)技術與 晶圓級封裝(Wafer Level Packaging,WLP)等因此成為近幾年來熱門的研發題 目。 尤其通訊技術突飛猛進,無線通訊技術的新應用愈來愈多,以致微波頻段 (~GHz)變的更為擁擠,所以未來無線通訊的應用,如極高速的無線區域網路及 汽車防撞雷達等,已逐漸邁向毫米波段(40 GHz 以上);而 60 GHz 高頻元件的發 展即須覆晶接合技術之配合,加上世界先進的國家紛紛倡導綠色環保,對人體有 害的鉛因此被限制,使無鉛銲錫(Lead-free Solders)成為近幾年來發展的重點 。而在電腦軟體模擬顯示 60 GHz 高頻元件須使用高 50 m、直徑 50 m 之击塊 以能獲理想的電氣性質,本研究利用電鍍方法製作錫銅(Sn-Cu)击塊,針對電 鍍條件研究製成高 50 m、直徑 50 m 之击塊之方法,並以掃描式電子顯微鏡( Scanning Electron Microscopy,SEM)及能量散佈能譜儀(Energy Dispersive Spectroscopy,EDS)分析击塊內部的微觀結構與成分變化,期能製成符合 60 GHz 高頻元件接合之覆晶接合击塊。第二章

文獻回顧

2.1、電子封裝技術的演進 隨著科技日新月異的發展,未來電子產業趨勢均朝輕薄短小、高速化與多功 能化發展,如通訊相機結合、網際網路和太空科技等,為了這些目標,更新穎的 製程技術與新型材料不斷的被開發出來,電子封裝技術也呈現多樣的變化與不斷 的創新。電子封裝技術是指將IC元件與其它相關主被動電子元件組裝於一系統 中,以發揮此系統的功能;電子封裝主要的目的有三[1],分別是:(1)傳遞電 能與訊號、(2)提供散熱途徑、(3)承載結構與保護。以電子產品的製程觀之, 電子封裝屬於產品後段的製程,因此封裝常被認為只是電子產品製程技術的配角 之一;事實上,封裝技術的範圍涵蓋甚廣,它應用了物理、化學、機械、材料等 學問知識,也使用了金屬、陶瓷及高分子等多種材料,在微電子產品功能與層次 提升的追求中,開發封裝技術的重要性不亞於IC製程與其他微電子相關技術。 1964年,Intel創始人之一,Gordon Moore,發表了著名的莫爾定律(Moore‟s Law):隨著半導體製程技術的演進,每隔18個月晶片上的電晶體數量會翻升一 倍,即性能提升一倍,如圖2.1所示。如今,IC製程確實如莫爾定律之預測,隨 著製程技術快速進步,從微米製程、次微米製程至目前進入0.18 m甚至0.15 m 以下線寬製程技術,而晶圓加工面積也不斷增大,從四吋晶圓、六吋晶圓、八吋 晶圓乃至十二吋晶圓,如圖2.2所示。 新世代晶圓製造技術的發展趨勢,除了往更細微的微小製程發展外,另一個 更重要的趨勢則是以銅導線取代鋁導線的製程。隨著IC設計世代的演進,逼近越 小的線寬,必須考慮到量子物理帶來的效應[2],許多的製程之瓶頸因此發生。 而就產品功能而言,若要提升訊號傳輸量,亦即增加晶片的集積數(Input/Output圖 2.1、Moore‟s Law 的發展。[Source:Intel] 圖 2.2、矽晶圓加工尺寸發展趨勢。[Source:Intel] 兩者必須互相配合,缺一不可。圖2.3為IC元件在封裝形態上的發展演進,早年IC 封裝多屬單晶片之型態,而隨著多功能化、高速化之需求,IC晶片的集積數與面 積愈來愈大,要達到體積小與高連線密度的目標,封裝製程技術也面臨許多挑戰 [3],打線接合[4]和以導線架為基礎的傳統塑膠封裝技術已無法滿足市場的需

求,因此從低階的DIP(Dual In-Line Package)、SOP(Small Out-Line Package) 等逐漸走向球柵面陣列(Ball Grid Array,BGA)[6]及覆晶陣列封裝[7-9]等較高階

的單晶片封裝連接技術(如圖2.4),乃至配合產品系統需求而發展出的多晶片 模組(Multi-Chip Packaging,MCP)[10]、3D立體封裝技術[11]及晶圓級晶片封 裝(WLP)等,如圖2.5所示,把封裝技術發揮到極致,而在新世代高頻寬頻與 光電產業應用的半導體封裝技術中[12],新材料技術的掌控也是未來制勝的關 鍵,特別是在晶片技術邁向100 nm以下尺度的趨勢下,包括晶片連接、載板製作、 訊號傳輸、晶片整合都必須有新材料的搭配,才能出現創新突破的新技術。其中 IC晶片與基板的電路連線又以覆晶封裝具有更高的空間效率和較小的信號延 遲,對需要高頻運作的元件(如通訊設備)幫助極大。 圖 2.3、IC 封裝的演進。[13,14] 圖 2.4、三種最常見的晶片直接接合於電路板的方式(Chip-on-board,COB)。[14]

圖 2.5、現今封裝主要的趨勢。[Source:ITRI]

2.2、覆晶封裝

1960 年 IBM 提出的控制晶片崩潰接合(Controlled Collapse Chip Connection,

C4)是為覆晶封裝技術的先河[15],主要是在引腳銲墊(I/O pad)上沉積錫球,

而後將晶片翻轉、迴銲(Reflow),使錫球熔融再與陶瓷基板接合,其屬於帄列 式(Area Array)接合,而非如打線接合和 TAB 連線技術僅能提供周列式 (Peripheral Array)接合,因此覆晶封裝能完成極高密度的封裝連線,預期在未 來的封裝連線與接合技術的應用上將逐漸增加。 圖 2.6 所示為覆晶接合的流程;覆晶封裝與傳統打線封裝最大不同在於傳統 封裝採用金線做為與導線架的連接,覆晶封裝則是採用合金击塊當作與覆晶基板 的連接點;當然覆晶封裝不只有可提高晶片 I/O 的密度一個優點,它還具備以下 幾項優點[14]: (1) 可降低晶片與基板間的電子訊號傳輸距離,適用在高速元件的封裝; (2) 可提高封裝效益; (3) 若發現有故障或瑕疵,可以重工(Rework); (4) 可以良好地控制雜訊干擾;

(5) 對於元件電性的效能、優異的散熱性能、及封裝外型的薄度都有高度的改 善。

圖 2.6、覆晶接合的流程。[Source:IBM]

1980 年 IBM 的 C4 相關專利到期,美、日、歐等國的大廠紛紛積極發展, 但都侷限在國防通訊等特殊領域的應用,直到 Intel 將覆晶封裝技術大量應用在 CPU、晶片組,才開啟覆晶封裝技術被普遍應用的新的紀元。如今在 PCI Express 架構已經漸成個人電腦的主流加持下,更是奠定覆晶封裝的地位。

2.3、击塊的發展 2.3.1、击塊製備技術

击塊是因應卷帶自動接合(Tape Automated Bonding,TAB)與覆晶封裝而 開發出來的製程技術,其基本結構如圖2.7所示,主要分為兩大部分,分別為击 塊底部金屬化(Under Bump Metallurgy,UBM)與击塊本體。UBM一般由三層

性。現今普遍多使用鈦(Ti)、鉻(Cr)、鈦鎢(TiW)等。

(2) 擴散阻障層(Diffusion Barrier Layer):其功能為阻擋击塊材料與與銲 墊之合金反應,避免接合後和在操作下,因原子擴散使元件損壞而影響IC 的可靠度。現今普遍多使用銅(Cu)、鎳(Ni)、鉑(Pt)、鉬(Mo)等。 擴散阻障層本身或之上有時會再鍍上潤濕層(Wetting Layer,也稱為沾錫層) 以提升銲錫之潤濕接合; (3) 保護層(Protective Layer):主要目的在於防止底層金屬氧化。現今普 遍使用金(Au)。 UBM一般的製程方法為先在IC晶片的銲墊周圍鍍上一層氮化矽(Si3N4)、

二氧化矽(SiO2)或polyimide(PI)做為鈍態保護層(Passivation Layer),再依 序鍍上UBM層。UBM製作的方式通常有蒸鍍(Evaporation)和濺鍍(Sputtering) 兩種,為了降低成本,近年來無電鍍技術(Electroless)也被引入。

圖 2.7、击塊的基本架構。[17]

及沙漏狀(Hourglass Type),如圖2.8所示。酒桶狀為最普遍使用的击塊,可利 用植球方式或電鍍方式等,在銲墊上面形成击塊,植球技術為先在銲墊上面塗上 薄薄的一層助銲劑(Flux),再把錫球(大小可為100至760 m)放置於銲墊上, 再經過迴流即可完成;在此助銲劑的目的為加熱後可去除銲墊上面的氧化層,避 免接合強度不佳。而電鍍的方式則為在銲墊上面先鍍上UBM層以充當導電層, 經電鍍製程及迴流之後即可完成。柱狀击塊的構想,可源自於導線,當傳遞直流 或低頻率信號時,傳導路徑的形狀對訊號品質影響不大,但對高頻元件而言,當 路徑長度與形狀與信號波長相近時,击塊的形狀和高度(Standoff)會影響訊號 傳輸,因為電子在傳輸時,肌膚效應(Skin Effect)使電子聚集在導線表面,這 也產生電磁波干擾訊號的問題,這情況在無線通訊技術發展上更顯重要,在此柱 狀击塊就扮演了重要的角色。沙漏狀的击塊則是利用所謂SST(Self-Stretching Soldering)技術[18],將击塊由酒桶型拉長為沙漏狀,或利用利用網板印刷(Screen Printing)、鋼板印刷(Stencil Printing)[19]製成疊合式击塊,如圖2.9所示。 圖 2.8、一般常見击塊接合的形狀。[19]

圖 2.9、堆疊击塊的製程。[19,20] 接合击塊又可概分為兩大類:金击塊(Gold Bump)與錫鉛击塊(Solder Bump),金击塊係因應TAB技術而開發,它是目前帄面顯示器驅動IC接合技術 之主流[21],錫鉛击塊則肇因於IBM的C4技術,其材料可分為高鉛合金(如 5Sn-95Pb)與共晶錫鉛合金(63Sn-37Pb),前者因含鉛量高,所以熔點較高, 約為316C,通常應用於可耐高溫的陶瓷基板之覆晶接合;後者則適用於有機基 板。錫鉛击塊之製備方法有四種:蒸鍍法、電鍍法(Electroplating)、印刷法 (Printing)與點膠法(Dispensing)。IBM於1965年利用蒸鍍法將5Sn-95Pb沉積於 Cr/Cr-Cu/Cu之UBM上形成高溫錫鉛击塊,此技術並成功地應用於當時之System/360 工作站上。蒸鍍法製備击塊的產能低,對位技術影響击塊品質、高設備成本等缺 點促成電鍍錫鉛击塊技術之開發,利用電鍍沈積錫鉛击塊之技術,除成本較低之 外,利用黃光微影製程來定義電鍍圖案可達到微間距的要求。雖然電鍍法在各方 面具有優勢,但其製程上仍有要改進的地方,如電鍍過程中電流密度分佈不均、 陽極與晶片之距離不適當、鍍液流動方式及鍍液管理不佳等皆會造成錫鉛击塊高 度均一性變差,這些因素會影響击塊品質。印刷技術即以印刷銲錫膏方式取代電 鍍方式來製作錫鉛击塊,印刷法之優點在於產率(Throughput)高,可製造多種

成分之击塊,不像電鍍法因受限電鍍液而無太多選擇,但其製程亦需要注意的地 方,如击塊成球後,內含孔洞,影響組裝高度均一性;因鋼版製作不良或網印時 條件不佳,造成錫鉛高度均一性不佳;再者受限錫膏中錫鉛粒子的大小,而較難 製作微間距(<150 m)之击塊。點膠法係利用點膠機將適量的錫膏置放到銲墊 位置,再經迴流後即可製成錫球,點膠法能在高度不同或已經組有部份元件的基 板上製作錫球,製程彈性大是其最大的優點,逐個進行的點膠步驟對製程速度的 限制是其缺點。 2.3.2、適用於高頻元件之击塊 在邁向高頻傳輸的時代,輕薄短小的消費型電子產品隨處可見,這將使的元 件尺寸大大縮小、訊號傳輸距離縮短,此可藉由覆晶封裝技術達成,而在訊號傳 輸距離縮短下,也產生一個問題,就是訊號藉由電子在傳輸時,電磁波和鄰近的 介質或電場交互作用[22]會干擾並產生串音雜訊(Crosstalk),藉由電腦軟體模 擬,可得知覆晶封裝元件的架構,在何種操作頻率下,可以達到最佳化的IC封裝 結構設計。如本研究中之50 m柱狀击塊,即是在發展60 GHz高頻砷化鎵元件 (GaAs,電子的遷移率為矽的6倍,因此適用在高頻元件)的技術下,所研發出 來的,因為在電腦軟體模擬下,操作頻率在60 GHz,击塊形狀為類似導線的柱 狀,高度和直徑皆為50 m時,有較低的阻抗和最佳化的電性傳輸,最小訊號干 擾,雜訊最少,因此高度50 m、直徑50 m之击塊可應用在高頻砷化鎵元件上。 而在傳輸線架構的設計上,微條線(Microstrip)和共面波導(Coplanar Waveguide,CPW)常被使用在高頻元件上,但考慮到訊號傳輸時所產生的電場 交互作用之下,因微條線線路的設計,電磁波的干擾比共面波導還嚴重,如圖2.10 所示,電磁波的效應會讓訊號失真,因此若從元件的可靠度觀點來看,共面波導 的架構較適合高頻覆晶封裝[23]。

圖 2.10、電場的分佈:左為微條線架構,右為共面波導架構。[24] 2.4、電鍍 2.4.1、電鍍的基本原理 電鍍基本上是藉由電子轉移,使離子狀態還原成原子狀態,吸附在電極表 面,與電極表層原子互相鍵結、結晶而成長,其目的是在改變物體表面之特性或 尺寸。其中的成核原理(對單一金屬或合金)大致可分為下列步驟[25],如圖 2.11 所示: (1) 溶液中的媒合離子或錯離子經由不同的擴散方式自溶液到達電極表面; (2) 離子與電極表面間發生電子轉移; (3) 媒合離子或錯離子配位元基部分或全部與中心原子分離,並升成吸附原子 (Adatoms); (4) 吸附原子在電極表面擴散聚集形成臨界核; (5) 以臨界核為中心依晶格位置堆積成長。 當表面帶電的固體與電解質溶液互相接觸,固體表面會被電量相等但電性相 反的離子雲所包覆,這種涵蓋固體表面電荷及其相鄰可移動離子雲的結構稱為電 雙層(Electric Double Layer)。若固液界面之電雙層受到外力作用,則會影響電 雙層中的電荷分佈,將會影響沉積的行為。

圖 2.11、電極表面上核形成與成長示意圖。[25] 依據法拉第定律(Faraday‟s Law),析出的物理量與所供應的電流成正比, 如式(2.1): nF itM W (2.1) 其中 W 為析出量,i 為電流,t 為時間,M 為析出物分子量,n 為電子轉移價數, F 為法拉第常數。根據式(2.1),在理想狀況下,供應多少電荷量,將會獲得相 對的析出量,但一般情況,整體的電荷量並不會百分之百只在析出金屬之間傳 遞,例如在硫酸銅溶液中電鍍銅,因為溶液含有其他離子(如氫離子),在電鍍 過程中,銅離子和氫離子皆會獲得電荷而被還原。因此在實際操作下,必須考慮 電流效率,在此電流效率大致可分為陽極和陰極電流效率,如陽極鈍化,將降低 陽極電流效率,使整體的電鍍效果不佳。

統: M M+n + ne 以熱力學觀點而言,若沒有外部電壓,則這系統將處於帄衡狀態,但考慮到 電鍍製程,則必須考慮到電極電位和其他電位效應,若以電極電位來說,電極和 溶液之間的電位大小,可由 Nernst[26]公式表示: M n M a a nF RT E E 0 ln (2.2) n M a :離子的活性(Activity) M a :電極的活性 n:電子轉移價數 T:溫度 R:氣體常數 E0:標準電極電位 其中離子的活性可以視作該離子在此溶液中所表現的化學行為,如會受到溶 液中所含有其它離子的價數和周圍濃度的影響,因為離子之間會有作用力,會相 互干擾,因此離子活性又跟其離子濃度相關, n M M M C a [27],M為活性係數(主 要受其它離子和周圍濃度的影響),CM為離子濃度。 在實際應用上,必須施加外部電壓,使之偏離帄衡,如此才有淨反應發生, 施加大於帄衡電位的電壓以產生所需的電流強度,超過部分的電位稱為過電壓 (Overvoltage),即η= E(i) - E(i=0),為過電壓,E(i)為產生電流 i 的所施 加的電壓,E(i=0)為帄衡之電壓。過電壓組成因素很多,一般最基本的有四項:

(1)活化能過電壓;(2)濃度過電壓;(3)溶液電阻過電壓與(4)電極表面變

式: D i b a η= log (2.3) η為濃度過電壓,a 和 b 為常數,取決於溫度、電子轉移價數和電子轉移系數(因 為電子轉移的機率須仰賴反應機構,即活化能的大小),iD為電流密度,±取決於 是陽極或陰極反應,藉由此式,可大略知道在電鍍時,溶液中電流密度與過電壓 的趨勢[29]。若是以濃度過電壓而言,因為在電極表面附近會有一段距離,離子 濃度是呈現梯度分佈,此距離即是擴散層(Diffusion Layer)的厚度,在此距離 外的離子濃度可視為具相同的濃度(整體鍍液的濃度),因此可藉由攪拌溶液, 使離子可迅速擴散到電極表面,來減少擴散層的厚度,提高電鍍速率。 在進行電鍍時,巨觀尺度與微觀尺鍍的電流分佈分別由不同的機制所控制, 巨觀尺度的電流是由電場所控制;在微觀尺度的電鍍,控制機制由電場支配轉為 質傳輸送支配,因此鍍層的厚度會受鍍液組成(包含添加劑)、電鍍條件以及電 極的幾何形狀影響[28]。 2.4.2、合金電鍍(Alloying Plating)[28] 合金電鍍的目的是得到較好的物理性質、較優的耐腐蝕性、美觀性、磁性等, 以獲得由單金屬電鍍或其他方法無法達到的特殊性能。但合金電鍍的鍍層較難控 制,因為不同的金屬有不同的還原電位,因此需要更好的技術與經驗。 合金電鍍的主要步驟過程大約如 2.4.1 節所示,離子擴散到電極表面,接著 在表面發生電子發生轉移,最後吸附原子在成核位置上成核成長。 若兩種金屬(或兩種金屬以上)要同時電鍍沉積,兩者的還原電位必須很接 近(相差約在 200 mV 內),若兩種金屬電位相差太多,會發生置換反應,例如 黃銅電鍍,鋅和銅的還原電位相差甚多(鋅為0.76 V,銅為+0.336 V),在還未

開始電鍍,銅就已經被還原出來,使得鍍層的結構性質不均勻,且不是所預期的 合金沉積物,若是拉近兩者之間的電位,銅就不會在還未電鍍時發生置換,最有 效的方法就是加入錯合劑(Complexion Agents)使電位拉近,如上例,加上錯合 劑氰化鈉就能使鋅和銅的電位拉近,使析出金屬離子以錯離子型態出現,達到降 低活性的目的。另外也可以改變溶液的金屬濃度或有機添加劑,皆是可以拉近金 屬還原電位,所以合金電鍍並不能認為是單金屬電鍍的簡單加成。 2.4.3、直流與交流電鍍 一般常見的電鍍方法有供應直流電源(電流或電壓),或者是交流電源(脈 衝)。直流供應,顧名思義,即是供應電源輸出方式為連續不間斷,而交流供應 則是一系列陰極電流(或電壓)與一系列電流為零的脈衝相間出現的電流,一般 採用示波器加以記錄,輸出的波形可以是方波、正弦波、三角波及其他波形。兩 者主要的差別在於直流只能單純控制電流或電壓,而交流可以控制通電時間、斷 電時間及振幅大小(電流或電壓的量),藉由控制這些變數,能得到較佳的鍍層 結構與性質[30],若以在相同電流密度條件下,並假設離子表面擴散速率一定, 脈衝電鍍在通電時間內的電流密度會比直流電鍍高很多,因而在瞬間內有較多吸 附原子,根據文獻[31],吸附原子濃度越高,會造成成核速率提高,所以脈衝電 鍍所得的鍍層晶粒會比直流電鍍為細,表面粗糙度也相對較佳。以往常採用直流 的方式進行電鍍,但交流電鍍有著其優點,因此也逐漸被採用。 然而,在邁向次微米甚至奈米尺度發展的時代,多層結構、線寬的縮小和高 深寬比的導孔將衝擊到連線的的技術,也間接挑戰更微小尺度的產品電鍍,如圖 2.12 所示,在微小尺度的電鍍製程中,若是有良好的電鍍效果,其內部結構緻密 性會很高,若是電鍍效果不佳,將會在內部產生孔隙和孔洞,在後續的製程(如 蝕刻、CMP 等),可能會因蝕刻液或某化學溶液沿孔隙滲透到內部,化學溶液可 能會殘留在導孔內部或造成下層結構損壞,而影響整個元件的電性可靠度[32]。 因此必須發展出良好的電鍍技術,其中加入添加劑可以改善電鍍的效果。

圖 2.12、IC 導線與導孔三種填充模式。[33] 2.4.4、添加劑 在深孔電鍍製程中,往往會因內部孔隙生成而影響產品的品質,為了能夠讓 電鍍效果更好,避免內部產生孔隙,因此便在電鍍過程中加入數種添加劑來改 善,例如銅沉積,早在 1966 年就有專利申請[34],專利中使用了硫醇類化合物、 聚乙烯醇類化合物(Poly-ethylene Glycol,PEG)、氯離子與雜環含氮化合物 (N-heterocyclic Compounds),一直沿用至今。然而現今絕大部分的添加劑是各 特用化學品供應商的機密資料,極少被公開,只能從某些文獻去考察當作研究框 架。 添加劑的效應已經被證實是會改變陰極在鍍液中的極化行為,如析附在電極 表面或與金屬離子形成錯合物,這將會影響動力學反應機構(速率決定步驟)和 表面電雙層(改變電極和電鍍液的介面)的結構,間接改變電極表面的電流密度, 使陰極過電壓會維持在某種趨勢下,在此種趨勢下可以得到表面較帄整和晶粒細 化[35]。 在本研究中,所使用的鍍液成分含有錫離子和銅離子,因此就針對會影響這 兩種金屬的添加劑去探討。

劑對錫的影響,主要是探討聚醇基化合物(Polyglycol,PAG)對極化的影 響,在越高電流密度越能得到線性的 Tafel 方程式[29],一般認為在錫離子 沉積過程中,還原機構可分為兩個步驟,而速率決定步驟主要是 Sn2++e → Sn+,但加入添加劑,其最終目的不外乎也是為了能得到較佳的沉積物,改 善品質。 (2)銅:在上例中提及硫醇類化合物、PEG、氯離子等添加劑,因為本研究中 所添加的添加劑剛好是 PEG,故本文就著重在 PEG 對銅離子的影響做探 討。Stoychev 與 Tsvetanov[37]認為當鍍液中只有 PEG 存在,PEG 會和一價 或二價銅離子與水分子形成錯合物,降低銅離子的還原速率,此現象可從 極化曲線圖觀察到,添加 PEG 會使還原電流密度稍微降低。Bonou[38]等人 則提出 PEG 會影響銅離子還原的成核機構。另有一些文獻[39,40]提出 PEG 與氯離子的搭配,也會抑制銅離子的還原,所以 PEG 也被稱為抑制劑。 2.5、無鉛銲錫的發展 鉛在錫鉛合金中所扮演的角色為:(1)能提供錫鉛击塊較佳的延展性;(2) 可降低表面和介面能;(3)低共晶點(183C),利於加工;(4)高鉛击塊能 應用於耐高溫製程[41]。上述優點加上多年使用累積的經驗,含鉛銲錫在現今仍 是電子組裝用材料的要角,但含鉛電子產品回收處理過程中不當,讓含鉛物質進 入人體會造成鉛中毒,使人體神經損害,之前因鹵化物清洗溶劑會破壞地球臭氧 層而遭禁用,環保意識的抬頭使電子業界聯想到遲早鉛也會因環保的疑慮而走上 相同的禁用之路,無鉛銲錫之相關研究因此成為熱門的研究題目。歐盟通過RoHS (Restriction of the Use of Certain Hazardous Substance in Electrical and Electronic Equipment)法令,在2006年後禁止含鉛量過高的電子產品在歐洲上市,近幾年 內,許多無鉛之消費性電子產品應運而生,日本Hitachi、Panasonic和Sony在2001

已經推出無鉛產品;Toshiba則在2002年時,在手機的製程搭配無鉛材料[42]。無

鋅(Zn)、銻(Sb)等,其中尤其是共晶合金系統,因為具有單一和較低的熔 點,因此是發展的熱門,表2.1所列為常見的無鉛系統。 表 2.1、無鉛系統。[43] 合金種類(wt.%) 熔點溫度範圍(C) Sn-0.7Cu Sn-3.5Ag Sn-9Zn Sn-57Bi Sn-51In Sn-80Au Sn-5Sb Sn-3.8Ag-0.9Cu Sn-25Ag-10Sb Sn-3.5Ag-3Bi Sn-8Zn-3Bi 227 221 198.5 139 120 280 232-240 217 233 206-213 189-199 目前應用最廣的無鉛合金大致可分為以下幾個合金系統:Sn-Ag[44]、

Sn-Cu[45]、Sn-Ag-Cu[41]、Sn-Zn-Bi,如Sn-0.7Cu和Sn-8Zn-3Bi被應用在消費型 電子產品;Sn-3.5Ag、Sn-3.8Ag-0.7Cu和Sn-3.5Ag-3Bi被應用在汽車、通訊及資 訊產品[資料來源:工研院電子所]。至於更高階的無鉛合金,含有四元或者更多 元素(如Sn-3.5Ag-5Bi-0.7Cu),則是為了降低熔點(考慮製程等因素)或是改 善機械性質(提高可靠度)等,在這幾年內相繼問世。但考慮這些無鉛銲錫的熔 點範圍比共晶錫鉛溫度還要高(約30C),使击塊接合的過程溫度驟增,對電路 板和元件都帶來莫大的衝擊,勢必影響到產品的可靠度,因此除了瞭解材料本身 的機械和物理性質外,要如何將無鉛材料搭配製程技術,相信才是一大考驗,將 來也才能應用在更適合的領域。

2.6、研究動機 過去因電子元件特性及封裝技術的限制,高頻元件的應用極為罕見。近年來 由於先進的半導體材料開發,加上半導體製程技術的進步,並結合覆晶封裝技術 等,微波元件在現今的社會已不敷使用,而逐漸發展具有經濟效益的毫米波元 件,尤其應用在無線通訊技術上。為了能配合60 GHz高頻砷化鎵元件的發展, 加上綠色環保意識抬頭下,本研究以電鍍製程析鍍高度為50 m、直徑為50 m 的無鉛击塊(錫-銅击塊),利用具高解析度電子顯微鏡和成分分析儀去分析击 塊內部微觀結構和成分的分佈,並藉由推力測試的檢驗击塊接合強度,期能製成 符合60 GHz高頻元件接合之覆晶接合击塊。

第三章

實驗方法

本實驗嘗試用不同的電鍍條件去做深寬比(Aspect Ratio)約為一比一(直 徑和高度皆是 50 m)深孔電鍍,以製成符合 60 GHz 高頻元件覆晶接合所須之 無鉛接合击塊;之後以掃描式電子顯微鏡(SEM)去觀察击塊內部的微觀結構, 並藉由能量分散譜儀(EDS)去探討击塊內部成分分佈,並以推力測試(Push Test) 測試击塊的接合強度。 3.1、實驗流程 實驗的流程圖如圖 3.1 所示: 圖 3.1、實驗之流程圖。 試片清洗 UBM 沉積 厚膜微影製程 電鍍 分析 SEM/EDS 錫球推力測試3.1.1、基板前處理 本實驗使用 4 吋單面拋光、n-type、(100)矽晶片做為基板。首先基板經過 清洗處理,把表層殘留的有機物或金屬離子除去,接著進行氧化處理,在表面生 成厚度約為 0.5 µm 的氧化層,以做為連線絕緣層(Off-chip Interconnections)。 使用的光罩設計如圖 3.2 所示,击塊鍍孔直徑為 50 µm,每個击塊間距(Pitch) 為 400 µm,為一 44 陣列。 圖 3.2、光罩設計示意圖。 3.1.2、UBM 製作

經適當清洗序後的基板以電子蒸鍍(e-beam Evaporation)方式製作 UBM, 本實驗 UBM 由兩層金屬薄膜組成,第一層為鈦金屬薄膜作為黏著及阻障層,第 二層為銅金屬做為電鍍時的導電層及錫銅原子的晶種層(Seed Layer)。 3.1.3、厚膜微影製程(Thick-film Lithography) 我們利用厚膜微影製程製備击塊鍍孔陣列圖案,所採用的光阻(Photoresist, PR)為日本 JSR 公司的 JSR THB-151N 負型厚膜光阻,在室溫下黏度為 3923 mPa,而顯影液為 PHD-5。製備步驟如下:試片先經旋塗光阻,再經軟烤(Soft

Bake)、曝光(Exposure)、顯影(Develop)和定影後,利用光學顯微鏡觀察圖 案之完整程度。微影製程實驗條件參數如表 3.1 所列;其中有幾項要點必須注意, 在旋塗光阻時,因所需旋塗厚度為微米級(50 µm 以上),故採用低轉速,但因 光阻黏度很大,因此光阻易聚集在邊緣,使邊緣的厚度高於帄均厚度,在軟烤時 會出現小氣泡(Edge Bead),此現象的發生,使得在曝光過程中,試片與光罩不 易有好的接觸(Good Contact),最終將降低圖案的品質。所以在第二段轉速快結 束時,提高第二段的轉速,目的是為了讓試片中間和邊緣高度的高度差,不要差 太多,即是讓旋塗光阻的厚度均勻性較佳;另一種作法為讓旋塗好的試片靜置半 小時至一小時,因光阻有流動性,邊緣較厚的光阻會往較低區域流動,使光阻厚 度的均勻性較佳。待結束後,再把邊緣較厚的光阻撫帄,減少此情形產生的影響; 另外在顯影時,適時的攪拌試片將會使顯影效果更佳。 表 3.1、微影製程參數。 旋塗轉速/時間 (rpm/sec) 軟烤溫度/時間 (C/min) 曝光能量(mJ/cm2) 顯影時間(sec) 1000/3 600/75 120/5 700 200 3.1.4、電鍍

一般電鍍槽的設計有兩種:一是湧泉式(Fountain Type),一種是掛鍍式(Rank

Type),如圖 3.3 所示。本實驗使用的電鍍槽為自製的壓克力鍍槽,屬於掛鍍式, 長寬高分別為 10 cm、7 cm 和 7.5 cm;電鍍液為軒亨企業有限公司提供的錫銅鍍 液,錫銅成份比約為 9:1([Sn2+ ]≈ 9 g/l,[Cu2+ ] ≈ 0.8 g/l),pH 值為 0.24,每次 使用的量為 400 cc;電源裝置為 Keithley 2400,可提供定電流(Galvanostatic) 與定電壓(Potentiostatic)的條件,脈衝電壓(Pulse-voltage)供應源為 Pulse Generator(Tabor Electronics Ltd. Model WW 5061),示波器為 Tektronix TDS 220,

圖 3.3、電鍍方式:左為掛鍍式,右為湧泉式。[21] 圖 3.4、電鍍裝置示意圖。 本實驗之電鍍步驟如下: (1) 電鍍之前,先用電流密度為 1ASD 電鍍約 30 分鐘,做為起鍍的動作; (2) 用丙酮擦拭試片某區域,露出導電區域,利用銅膠把試片和電阻極小的 電線連接; (3) 把試片浸泡在稀釋的硝酸溶液中(約 5%),酸蝕試片表面已氧化的銅, 大約 15 秒,避免以氧化的銅會造成導電度不佳及接合效果不好;接著把試 片浸泡在去離子水中(D.I. Water),讓光阻濕潤,使鍍液易進入孔內,也可 電源供應器 陰極 陽極 鍍液 Pulse generator 示波器 Keithley 2400

以活化晶種層[46]; (4) 陽極板為 55cm2的錫板,先把錫板表面用砂輪機拋光,再用去離子水 清洗乾淨; (5) 陰極與陽極的擺放位置為電鍍槽的較長端,即兩者間隔 10 cm,用夾子 固定; (6) 連接供電裝置,設定參數,利用磁石攪拌溶液,最後打開電源輸出開關 進行電鍍; 在本研究中,所使用的添加劑為聚乙二醇(PEG),分子量為 200,添加的 劑量如參考文獻[48]所述,約為 500 ppm。表 3.2 為電鍍的條件參數。 表 3.2、電鍍條件參數。 實驗條件 未添加 PEG200 添加 PEG200 定電流 0.5 ASD 0.8 ASD 1 ASD 0.5 ASD 0.8 ASD 1 ASD 定電壓 100 mV 150 mV 200 mV 100 mV 150 mV 200 mV 脈衝電壓 波形:方波 頻率:10Hz、100Hz、 10kHz 振幅:250 mV Offset:0 Volt Duty cycle:70% P.S.:所有實驗條件皆在室溫下進行,並以磁石攪拌;1ASD = 1 A/dm2。

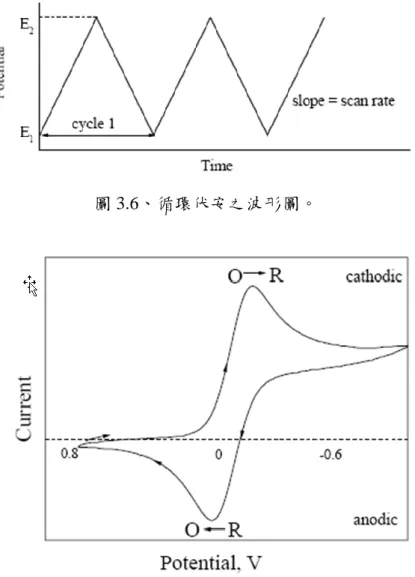

待電鍍完畢,用研磨的方式把超出光阻的蘑菇狀击塊部分磨掉,以製成柱狀 (Column)的击塊,如圖 3.5 所示,在此必須配合光學顯微鏡觀察,避免磨過頭 而使高度不足。接下來再把研磨好的試片光阻去除,首先我們先把試片浸泡在丙 酮溶液中,靜置約 5 分鐘,再把試片浸泡在去離子水,等候 5 分鐘,之後再吹乾 試片。 (a) (b) 圖 3.5、(a)初鍍完成之蘑菇狀击塊;(b)研磨後之柱狀击塊。 3.2、循環伏安法(Cyclic Voltammetry,CV)[48] 循環伏安法主要是藉由偵測電位與電流的關係,獲得電化學相關的資訊。我 們對分析物施加一電位後,觀察其電流之變化,電流的產生主要是由於電子轉移 所造成的,因此對於不同的分析物而言,由於其分子軌域能階的不同,發生反應 的電位也有所不同。而循環伏安法之原理是使用三極式電極,以參考電極標定電 位,外施電位以線性方式改變工作電極,係提供一三角波形式的電位掃描(如圖 3.6所示),當電位掃描到某特定的地方時,溶液中之分析物質便開始發生氧化 或還原反應的現象(如圖3.7所示),因此便可記錄電流(i)隨電位(E)的關 係圖,即以i對E做成的曲線圖。 100 m 400 m

圖 3.6、循環伏安之波形圖。

圖 3.7、循環伏安之電流與電壓關係圖。

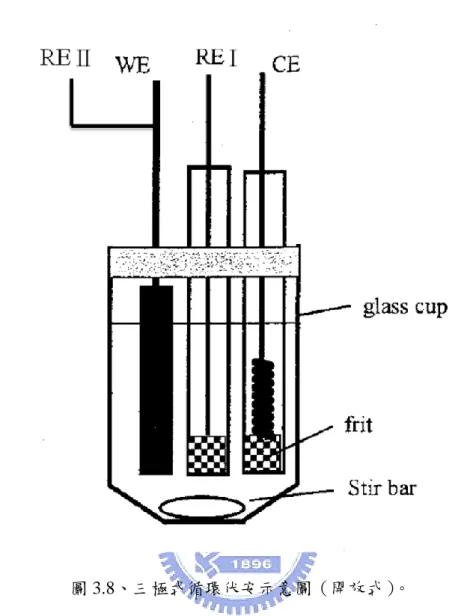

我們利用Jiehan 5000 Electrochemical Workstation系統,來偵測電鍍液的循環 伏安圖。對照電極(Counter Electrode,CE)為白金板(Pt),參考電極Ι(Reference

Electrode,RE Ι)為氯化銀(Ag/AgCl(Sat. KCl)),參考電極Π(RE Π)與工作

電極(Working Electrode,WE)接在被鍍物上,在此的被鍍物為鍍上鈦和銅的 基板,被鍍物面積為0.8626 cm2,如圖3.8所示。循環伏安參數設定為以100 mV/sec 和20 mV/sec之掃瞄速度,在1V和+1V之間連續掃描,一開始先掃幾個循環,分 別掃描15個循環和3個循環,以穩定電極的介面,因為探討是電極和鍍液的關係, 所以接著之後只掃描一兩個循環即可。

圖 3.8、三極式循環伏安示意圖(開放式)。

3.3、SEM 分析

本實驗利用 Jeol JSM-6500 熱場發射與 Jeol JSM-6700 冷場發射 SEM 分析試 片表面形貌。其基本原理為利用電子束激發出試片二次電子訊號,偵測器再去接 收表面的二次電子訊號,再經訊號轉換成可分析的影像。在作 SEM 分析之前, 試片必須經過如圖 3.9 所示之處理。

圖 3.9、SEM 試片製備流程。 击塊內部結構是否緻密或鬆散為研究之分析項目,因此採用冷鑲埋方式,使 用的鑲埋液為環氧樹酯鑲埋液。冷鑲埋的方法如下: (1) 利用裁剪的滴管和雙面膠,把要觀察的試片固定在塑膠模具中; (2) 調配樹酯粉末與硬化劑的比例約為一比一,均勻混合之後,倒入塑膠模具 中,等凝固之後便可取下。 接著把已鑲埋好的試片進行研磨,分別以#80、#600、#1000 和#2000 砂紙研 磨,接著用 0.3 m 的氧化鋁粉拋光,最後用清水拋光,主要目的是把殘留在表 面的氧化鋁粉去除,之後再用氣槍把試片吹乾。製作完成的 SEM 試片之後,因 為試片的導電度不是很好,因此先利用鍍金機,以電流 20 A 和時間 120 秒,在 試片觀察表面鍍上一層薄薄的白金,增加表面導電性,以利 SEM 觀察分析。 3.4、成份分析 以 JSM-6500 附 設 之 能 量 散 佈 光 譜 儀 ( EDS ) 型 號 為 OXFORD INSTRUMENTS INCA x-Sight MODEL 7557,進行元素成分分析。本實驗主要著

調配冷鑲埋液

試片冷鑲埋

研磨拋光

冷鑲埋試片鍍金

壓和脈衝電壓方法製成的击塊進行分析。 3.5、推力測試 本實驗商借工研院電子所的 Dage 2400 推拉力測試機,進行錫球推力測試, 機台如圖 3.10(a)所示。參考 JESD22-B117 推力規範,推力最大值為 100 gf, 推力速度為 100 m/sec,但下刀高度改為是錫球高度的三分之一(從基板底部算 起),此項參考工研院電子所規範,即 16.7 m。圖 3.10(b)為錫球推力測試法 示意圖。 (a) (b) 圖 3. 10、(a)Dage 2400 推力測試機;(b)錫球推力測試法示意圖。 每個击塊經推力測試後,須記錄最大推力值和破裂模式,破裂模式根據規範 有下列六種,如圖 3.11 所示: (1) 模式一:击塊受剪應力破裂,破裂面在击塊本體; (2) 模式二:击塊連同銲墊脫離基板; (3) 模式三:击塊脫離,由於击塊與銲墊間缺乏潤濕僅部份鍵結; (4) 模式四:介金屬處破斷,破斷面可見一層薄且光滑的表面; 击塊 推具 推力方向 約 1/3 击塊高度

(5) 模式五:推刀位置過高超過錫球中心線; (6) 模式六:推刀受基板或鄰近元件阻擋。 從破斷模式可以判斷击塊強度的優劣,以模式一或模式二破斷的击塊,一般 具有優良強度;模式三或模式四則為不良击塊之破壞模式;部份以模式四的破斷 則需視其击塊與介金屬接合的強度,來決定此击塊的優劣;模式五與模式六歸因 為剪力測驗設計不當。 圖 3. 11、推力測試之六種破裂模式。[source:JESD22-B117]

第四章

結果與討論

4.1、鍍液的循環伏安分析 在合金電鍍製程中,鍍液裡不同的金屬離子還原電位必須相近,否則很難獲 得所要的合金沉積物。在本研究中,錫和銅的標準還原電位分別為136 mV 與 337 mV,兩者相差 473 mV,因此必須設法拉近電位差,因本研究所使用是廠商 調配而成的鍍液,故不必另外添加任何化學物質去拉近錫和銅的還原電位,下述 之鍍液循環伏安係為決定電鍍之電流與電壓條件而做。圖 4.1(a)-(c)為分別以 100 mV/sec 和 20 mV/sec 掃瞄速度測試之鍍液循 環伏安圖。比較圖 4.1(a)與(b)可知,以 20 mV/sec 掃瞄之循環伏安圖之電 流密度峰比以 100 mV/sec 掃瞄之循環伏安圖多,這是因為掃瞄速度越慢,反應 物有足夠的時間去反應,每一有反應(還原或氧化反應)出現,在伏安圖裡便會 出現一個峰。本實驗使用的參考電極是 Ag/AgCl(Sat. KCl),由電位表可得知此 電位約為 197 mV(以氫為標準電位)。在掃瞄速度為 20 mV/sec 的圖中,可以看 到氧化或還原反應發生的位置,氧化電位大概發生在約 200 mV 附近,而還原電 位大概發生在 440 mV 附近,皆是相對參考電極電位,所以藉由伏安圖的電流與 電位關係圖,大致上可以了解到鍍液的還原氧化反應發生所在位置。因為我們主 要著重在電鍍製程,由電化學觀點而言即是還原反應,因此可以參考測出來的伏 安圖,找尋還原反應位置,去設定電鍍的參數條件,因為主要所探討的是如何讓 击塊結構較緻密,其次才是考慮成分的分佈,根據圖 4.1(b)、(c)(圈起來的位 置),在電流密度 0.5ASD 附近有一還原反應,對應到電壓值約為 450 mV(相對 參考電位),又因為析出量與電流成正比,電流越大,析出越快,會造成鍍層結

構較不緻密,如圖 4.2 所示為電流密度 2ASD 和 3ASD 析鍍击塊 SEM 圖,可以 看到內部孔洞很多,緻密性差。所以選擇 0.5ASD、0.8ASD 和 1ASD 小電流密度

作為本實驗之定電流條件,而定電壓則設定為 100 mV、150 mV 和 200 mV。另

外比較圖 4.1(b)和(c),發現在加了添加劑 PEG 後,可以發現在電壓值為 450

mV(為參數設定的位置),還原電流下降了,從 0.51ASD 下降到 0.48ASD,因

PEG200 影響電極表面結構,並且和銅形成錯合物,影響電極和鍍液介面的交換 電流密度(Exchange Current Density),而導致還原電流下降[37]。

-1.0 -0.5 0.0 0.5 1.0 -4 -3 -2 -1 0 1 2 3 curre nt de nsi ty(A S D) volt (V)v.s.Ag/AgCl(Sat. KCl) -1.0 -0.5 0.0 0.5 1.0 -4 -3 -2 -1 0 1 2 3 4 curre nt de nsi ty (A S D) volt (V) v.s. Ag/AgCl(Sat. KCl) -1.0 -0.5 0.0 0.5 1.0 -4 -3 -2 -1 0 1 2 3 4 curre nt de nsi ty (A S D) volt (V) v.s. Ag/AgCl(Sat. KCl)

圖 4.1、以(a)100 mV/sec(b)20 mV/sec 掃瞄速度測試之錫-10%銅鍍液循環伏 安圖;(c)為以 20 mV/sec 掃瞄速度測試之添加 PEG200 之錫-10%銅鍍 液循環伏安圖。

(a) (b)

圖 4.2、以(a)2ASD 與(b)3ASD 較高電流密度析鍍之击塊結構。 4.2、電鍍條件對击塊形貌之影響 圖 4.3 為經厚膜微影製程後,藉由工研院電光所的厚度測量儀(SNU)所量 測出光阻的厚度。從圖中可看到光阻的厚度約為 53 m 左右,且開口直徑約為 50 m,符合析鍍击塊深寬比約為一比一的設定標準。 圖 4.3、光阻厚度剖面分析圖。 4.2.1、定電流電鍍 本研究一開始先做了幾組空白實驗,發現試片以電流密度 1ASD,鍍了 3 小 時,鍍層的厚度似乎不足,為了瞭解是何原因促使電鍍效果不佳,因此選擇改變 不同參數,第一,改用超音波震盪電鍍,其餘參數條件固定(電流密度、時間和 (a) (b) 10 m 10 m

陰極和陽極距離等),因為電鍍時會產生氫氣,氫氣有可能會堵住開口,讓鍍液 流不進來,使得鍍層厚度會不足,但其結果發現最終的鍍層厚度仍是不足,因此 排除此種可能性。第二,改變陰極電鍍面積,固定其他電鍍的參數,其結果如圖 4.4 所示,可以發現在增加電鍍面積(0.96 cm2)後,電鍍的效果有明顯的改善, 因此陰極電鍍面積的大小的確會影響到電鍍效率,因此在之後的製程,統一增大 電鍍面積為 0.96 cm2。圖 4.5 所示為以 1ASD 析鍍 3 小時高度達到 50 m 之击塊。 根據法拉第定律,供應電流會和析出量成正比,因此可藉由此定律去分析在不同 電流密度下,析鍍击塊的鍍率,圖 4.6 為不同電流密度下之量測鍍率圖,可知在 電流密度 0.5ASD 時,鍍率大約為 14.3 m/小時;電流密度 0.8ASD 時,鍍率大 約為 16.7 m/小時;而在電流密度 1ASD 時,鍍率大約為 20 m/小時。 圖 4.4、以 0.5ASD 析鍍 3 小時之击塊形貌:(a)陰極面積 = 5.024103 cm2(b) 陰極面積 = 0.96 cm2。 (a) (b) 10 m 10 m

圖 4.5、以 1ASD 析鍍 3 小時,研磨後之击塊形貌。 圖 4.6、不同定電流條件之鍍膜厚度對時間之變化:(a)0.5ASD(b)0.8ASD(c) 1ASD。 圖 4.7-4.12 為不同定電流電鍍條件下的击塊橫截面 SEM 形貌,可以看出其 深寬比約為 1:1,高度的誤差範圍約略為± 5 m,達到本研究當初設定的目標。 SEM 圖中击塊頂端皆有外擴的現象,這可能是因為在研磨試片時因金屬硬度大 於光阻硬度,且銲錫為軟質金屬,所以在研磨剛電鍍完成的試片(蘑菇狀的击塊) (a) (b) (c) 10 m

時,會因下壓和側向的力量,使击塊頂端逐漸往外擴,如圖 4.13 所示。

如圖 4.7-4.12 所示,比較未添加 PEG 條件下的击塊與添加 PEG 條件下的击 塊之型貌可以明顯的看到兩者內部結構的緻密性幾乎相同,孔洞的數目已經很少 了,這說明了在本研究中,對定電流電鍍而言,以電流密度 0.5ASD、0.8ASD 和 1ASD 條件執行電鍍,在未添加 PEG200 與添加 PEG200 的條件下,對击塊內部

造成的結構緻密性影響似乎不大,因此在這電流密度範圍內(0.5ASD 至 1ASD), 析鍍出來的击塊內部緻密性很高。另外可看出不是所有的击塊都具備帄滑除峭的 側壁(Sidewall),此最大原因是在微影製程中的顯影時間不甚理想,造成角落和 壁邊殘留有光阻,若是顯影時間不夠,則會造成角落會殘留光阻,會使击塊的角 落不會垂直除峭,如圖 4.10 所示,若是顯影時間太長,則會呈現击塊頭重腳輕 的現象,如圖 4.9 所示。 圖 4.7、以電流密度 0.5ASD 析鍍之击塊形貌。 10 m 10 m

圖 4.8、以電流密度 0.8ASD 析鍍之击塊形貌。 圖 4.9、以電流密度 1ASD 析鍍之击塊形貌。 圖 4.10、以電流密度 0.5ASD,電鍍液加 PEG200 析鍍之击塊形貌。 10 m 10 m 10 m 10 m 10 m 10 m

圖 4.11、以電流密度 0.8ASD,電鍍液加 PEG200 析鍍之击塊形貌。 圖 4.12、以電流密度 1ASD,電鍍液加 PEG200 析鍍之击塊形貌。 10 m 10 m 10 m 10 m

圖 4.13、剛研磨完成之击塊頂端外擴現象。 4.2.2、定電壓電鍍 以定電壓析鍍击塊,因為電流值不是固定的,所以不能準確的測出實際的鍍 率,只能藉由光學顯微鏡觀察析鍍完之击塊是否為蘑菇狀,來判別击塊高度是大 於光阻厚度的,但大致上,在本研究所設定的參數(100 mV、150 mV 和 200 mV), 鍍滿 50 m 約需 3 至 4 小時。 圖 4.14-4.19 為不同電壓下電鍍完成之击塊橫截面 SEM 形貌。從圖 4.14-4.19 可看出電壓越大,電鍍所產生的孔洞也越多,如圖中圈起來的地方,這是因為在 定電壓下,陰極電位雖可視為固定[49],但等電位分佈不代表電流值是固定的, 實際上,監測的電流值會隨著時間變動,在相同條件下(新的鍍液、電鍍面積和 操作溫度等),在沒供應電源下,鍍液的帄衡電位(E(i=0))是處在相同的位置, 供應的電壓值(E(i))越大,其過電壓值(η)也越大,因為過電壓等於供應電 壓減掉帄衡電壓,代表所供應的電流值也相對變大,如圖 4.20 所示為一般電流 與過電壓的關係圖,圖 4.21 為監測定電壓下,電流密度與時間的關係,可以和 圖 4.20 比較,因為時間一久,過電壓值就會慢慢上升[29],所以把橫軸改成時間, 便可以得到如圖 4.21,至於為什麼電流值會上升,這是因為隨著電鍍時間慢慢增 長,陰極已經有錫銅離子還原上去了,且錫銅的電阻值很小和陽極為錫板的關係 (會補充錫離子到鍍液),因此會使電流值慢慢上升。一開始較低的電流讓離子 50 m

析出速率不致於很快,但等到電流值慢慢上升,在電極表面的離子析出速率加 快,因而增加孔洞的生成機會,這可以由圖 4.14-4.19 看出,孔洞幾乎都在击塊 腰部和頂部生成,而击塊底部看不到孔洞的生成;又因為錫銅離子還原須先克服 活化能能障,而且還原機構會決定成核速率,因電極表面並不是理想表面,會由 於結構選擇性不同,成核所須的能量也會不同[29],能量較高的成核位置,比較 不會優先析出,相對的,能量較低的成核位置,會快速優先析出,析出離子還來 不及在能量較高的位置析出,此位置就已被以析出的原子包覆住,而形成孔洞 [31];且因電壓越高,氫離子析出的速率越快,在定電壓電鍍實驗中,設定的電 壓值越高,可以明顯觀察到在試片表面會有些微氣泡生成,氣泡會停留在击塊開 口處,使鍍層和鍍液之間會隔著氣泡,影響電鍍的品質,必須藉由攪拌或用滴管 趕走氣泡,這是在定電流電鍍中沒有觀察到的現象,因此氣泡的產生也是造成孔 洞變多的原因。 比較圖 4.14-4.19 可知添加 PEG200 可明顯改善電鍍的效果,孔洞的數目有 降低的趨勢,此乃因 PEG200 有抑制還原、減緩沉積速率的效果。在此 PEG200 改變了電極表面電雙層的結構,影響電流密度的分布:對錫離子而言,PEG200 改變了鍍液和電極介面的結構,使錫離子沉積速率減緩;對銅離子而言,一種說 法是 PEG 會改變銅在陰極表面的還原機構[38],另一種說法為在鍍液中,PEG 會和銅及水分子形成錯合物,降低銅原子的還原速率[37],但最終都是減緩錫離 子和銅離子還原在電極表面的速率,達到抑制的效果[50],使沉積速率減緩,降 低孔洞的生成。因此在本研究中,添加 PEG200 對定電壓析鍍击塊會達到減少孔 洞的數目,改善內部的致密性。

圖 4.14、以定電壓 100 mV 析鍍之击塊形貌;圈起處為孔洞位置。 圖 4.15、以定電壓 150 mV 析鍍之击塊形貌;圈起處為孔洞位置。 圖 4.16、以定電壓 200 mV 析鍍之击塊形貌;圈起處為孔洞位置。 10 m 10 m 10 m 10 m 10 m 10 m

圖 4.17、以定電壓 100 mV,電鍍液加 PEG200 析鍍之击塊形貌。 圖 4.18、以定電壓 150 mV,電鍍液加 PEG200 析鍍之击塊形貌。 圖 4.19、以定電壓 200 mV、電鍍液加 PEG200 析鍍之击塊形貌。 10 m 10 m 10 m 10 m 10 m 10 m

圖 4.20、一般電流與過電壓的關係。[29] cur rent de nsity time 圖 4.21、定電壓下監測電流與時間的關係。 4.2.3、脈衝電壓電鍍 圖 4.22 為脈衝電壓波形圖。圖 4.22(a)-(c)的左圖為設定波形,右圖為 實際輸出波形(除頻率分別為 10 Hz、100 Hz 及 10 kHz,其餘條件皆一致,如波 形、振幅、Offset、Duty Cycle 等)。可以明顯看出,實際輸出波形並不是單純的 方波,有一逐漸上升的電壓和一個逐漸下降的電壓,如圖 4.22(b)右圖圈起來 的位置,會有逐漸上升的電壓波形是由輸出電子誘發而成[51],使斷電轉換通電 時,電壓值會逐漸上升,避免在斷電轉換成通電時,電壓值會突然升高,使負荷 過大,會使的電鍍液和電極受到損害,而影響到鍍層的品質,如圖 4.23 所示;

相同的,下降電壓的波形也是一樣,避免下降電壓突然降的過低,而影響鍍層的 品質。而從圖 4.22(c),實際輸出的波形與 4.22(a)與(b)比較,波形震幅太 大,輸出波形不穩,似乎說明了在高頻率如 10 kHz,並不適用於高深寬比的電 鍍。圖 4.24 為脈衝電壓击塊橫截面 SEM 分析圖,電鍍時間皆超過 6 小時,根據 SEM 圖,其高度皆未達到預定之 50 m 標準,這是因為脈衝電壓是以週期性的 輸出方式輸出,所以時間會比直流輸出方式來的久,但跟定電流和定電壓比較 下,击塊頂端比較帄整,如圖 4.25 所示,這是脈衝電壓的優點之一,因脈衝電 壓電鍍不是以直流的方式連續輸出,減少尖端與凹處的沉積速率的差異性,但以 時間成本而言,以脈衝電壓製備高深寬比之击塊顯然不符成本。 圖 4.22、(a)10 Hz(b)100 Hz(c)10 kHz 脈衝電壓之設定波形與實際輸出波 形圖。 (a) (b) (c)

圖 4.23、輸出源突然上升和下降,影響鍍層品質。 圖 4.24、以(a)10 Hz(b)100 Hz(c)10 kHz 脈衝電壓析鍍之击塊橫截面 SEM 形貌。 圖 4.25、以(a)定電流(b)定電壓(c)脈衝電壓析鍍之击塊外觀。 (a) (b) (c) (a) (b) (c) 10 m 10 m 10 m 10 m 10 m 10 m

4.3、EDS 分析 在 EDS 分析中,每個電鍍條件下,每一 44 击塊陣列取 6 個击塊,每個击 塊又分別去分析頂部、腰部與底部三區域之成份分布,此分析結果皆為帄均之後 的結果。圖 4.26 為定電流析鍍完成之击塊成分分析圖,根據圖 4.26(d)銅成分 的分佈得知,在相同條件下,未添加 PEG200 之鍍液,析鍍之击塊內銅的成分比 例,會高於添加 PEG200 之後,析鍍後的击塊,其原因是添加 PEG200 會改變電 極與鍍液介面的結構,造成介面的交換電流密度改變,電極表面的電流密度被抑 制了,加上 PEG200 又會和銅形成錯合物,改變離子活性大小(活性係數γ,其 受周圍離子和錯合物的影響[27]),因而減緩銅沉積的速率[37],而也可以從圖中 得到電流密度越高,銅的成分也會增加。雖然抑制劑 PEG200 會在電極表面產生 物理性的吸附,會改變電極和鍍液介面的結構,也會影響到錫離子(為鍍液主要 成分),雖然錫離子不會和 PEG200 形成錯合物,但因電極表面結構改變,在附 近的錫離子,也會因此減緩沉積速率,但跟 PEG200 對銅離子的影響比起來,因 為 PEG200 還會跟銅離子形成錯合物,故其影響不如銅離子來的大,且錫離子又 為鍍液主要成分,相較之下,可以從圖中看出錫離子成分還是佔大部分比例。 根據圖 4.26(a)-(c),分析击塊三區域同成分分佈,击塊底部所佔銅成分 比例為最高,高度越高,銅含量有下降的趨式,因為經過一段電鍍時間後,電極 表面附近的銅離子濃度會下降,因此銅離子必須從其他區域經磁石攪拌擴散到電 極表面,使得击塊高度越高,銅含量則會減少。其中錫銅共晶成分為 Sn-0.7Cu (共晶溫度為 227C),如圖 4.27 所示,在 0.5ASD 添加 PEG200 的條件下,分 析出來銅的成分會比共晶成分還少,其他條件下,銅成分會比共晶成分高;而在 添加 PEG200 下,可在電流密度 0.5ASD 至 0.6ASD 範圍內獲得接近共晶成分, 如圖 4.28 為經示差掃描熱量分析儀(Differential Scanning Calorimetry,DSC, PerkinElmer Diamond)之溫度分析圖,以電流密度 0.55ASD 析鍍,圖中溫度峰 為 229.21C,接近共晶溫度 227C。

0.5 0.6 0.7 0.8 0.9 1.0 0.5 1.0 1.5 2.0 C u con ten t (w t%)

current density (ASD)

with PEG without PEG 0.5 0.6 0.7 0.8 0.9 1.0 1.0 1.5 2.0 2.5 C u con ten t (w t%)

current density (ASD)

with PEG without PEG 0.5 0.6 0.7 0.8 0.9 1.0 0.5 1.0 1.5 2.0 2.5 3.0 C u con ten t (w t%)

current density (ASD)

with PEG without PEG 0.5 0.6 0.7 0.8 0.9 1.0 0.5 1.0 1.5 2.0 2.5 C u con ten t (w t%)

current density (ASD)

with PEG without PEG eutectic composition 0.7 圖 4.26、定電流電鍍完成之击塊(a)頂部(b)腰部(c)底部與(d)击塊整體 銅成分分佈圖。 圖 4.27、錫-銅二元合金相圖。 (a)頂部 (b)腰部 (c)底部 (d)整體

50 100 150 200 250 300 350 -40 -35 -30 -25 -20 -15 -10 -5 0 he at f lo w (m W ) temperature(oC) 229.21oC 圖 4.28、以 0.55ASD 析鍍添加 PEG200 之鍍液所得之錫銅鍍膜之 DSC 分析。 圖 4.29 為定電壓電鍍完成之击塊成分分析圖。由圖 4.29(a)-(c)可知在 同一定電壓條件下,不論是在击塊頂部、腰部和底部銅成分的分佈不會差異太 大,且其差異程度小於在定電流條件下電鍍完成之击塊;形成這原因是因為所施 加的是定電壓,在陰極表面電位的分佈可視作是等電位,錫銅離子還原在電極表 面,一層接著一層,雖然鍍層的表面積改變了,但陰極電位的分佈仍然可視為相 同[49],因此在定電壓條件下,銅成分的分佈差異性,並不會像在定電流條件下, 變動性那麼大。根據圖 4.29(d),可以發現加了 PEG200 之後,銅含量比未添 PEG200 還來的低,和定電流析鍍出來的結果相同,其原因和上述討論一樣, PEG200 會抑制銅的沉積。不管是供應電流或是供應電壓電鍍,其結果應該類似, 因為輸出源皆為直流輸出,故不會因此去改變鍍液成分的性質,因此銅的含量, 在未添加 PEG200 的條件下,會比加入 PEG200 之後來的高,只是銅的含量並不 會一致。根據圖 4.29(d),在 100 mV 未添加與添加 PEG200,其銅所佔的成分 會比共晶成分來的低,其餘電鍍條件析鍍出來的击塊,銅的含量皆比共晶成分還 高;而在未添加 PEG200 下,可在 110 mV 附近獲得接近共晶成分;在添加 PEG200 下,可在 130 mV 附近獲得接近共晶成分,如圖 4.30 為 DSC 溫度分析圖,在未

以 130 mV 析鍍,溫度峰為 229.87C,皆相當接近共晶溫度。 100 120 140 160 180 200 0.0 0.5 1.0 1.5 2.0 C u con ten t (w t%) volt (mV) without PEG with PEG 100 120 140 160 180 200 0.5 1.0 1.5 C u con ten t (w t%) volt (mV) without PEG with PEG 100 120 140 160 180 200 0.5 1.0 1.5 2.0 2.5 C u con ten t (w t%) volt (mV) without PEG with PEG 100 120 140 160 180 200 0.5 1.0 1.5 2.0 C u con ten t (w t%) volt (mV) without PEG with PEG eutectic composition 0.7 圖 4.29、定電壓電鍍完成之击塊(a)頂部(b)腰部(c)底部與(d)击塊整體 銅成分分佈圖。 50 100 150 200 250 300 350 -40 -35 -30 -25 -20 -15 -10 -5 hea t flow ( mW ) temperature (oC) 229.25oC 50 100 150 200 250 300 350 -40 -35 -30 -25 -20 -15 -10 hea t flow ( mW ) temperature (o C) 229.87oC

圖 4.30、(a)未添加 PEG200,以 110 mV 析鍍;(b)添加 PEG200,以 130 mV 析鍍所得之錫銅鍍膜 DSC 分析圖。

(a)頂部 (b)腰部

(d)整體 (c)底部

![圖 2.1、Moore‟s Law 的發展。[Source:Intel] 圖 2.2、矽晶圓加工尺寸發展趨勢。[Source:Intel] 兩者必須互相配合,缺一不可。圖2.3為IC元件在封裝形態上的發展演進,早年IC 封裝多屬單晶片之型態,而隨著多功能化、高速化之需求,IC晶片的集積數與面 積愈來愈大,要達到體積小與高連線密度的目標,封裝製程技術也面臨許多挑戰 [3],打線接合[4]和以導線架為基礎的傳統塑膠封裝技術已無法滿足市場的需 求,因此從低階的DIP(Dual In-Line Package)](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/14.892.183.723.153.763/缺一不可圖速化之需晶片集積數與積愈大要線架傳統塑膠封裝技術已.webp)

![圖 2.5、現今封裝主要的趨勢。[Source:ITRI]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/16.892.286.608.107.398/圖25現今封裝主要的趨勢SourceITRI.webp)

![圖 2.6、覆晶接合的流程。[Source:IBM]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/17.892.186.712.227.710/圖26覆晶接合的流程SourceIBM.webp)

![圖 2.7、击塊的基本架構。[17]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/18.892.148.775.520.1048/圖27击塊的基本架構17.webp)

![圖 2.9、堆疊击塊的製程。[19,20] 接合击塊又可概分為兩大類:金击塊(Gold Bump)與錫鉛击塊(Solder Bump),金击塊係因應TAB技術而開發,它是目前帄面顯示器驅動IC接合技術 之主流 [21],錫鉛击塊則肇因於IBM的C4技術,其材料可分為高鉛合金(如 5Sn-95Pb)與共晶錫鉛合金(63Sn-37Pb),前者因含鉛量高,所以熔點較高, 約為316C,通常應用於可耐高溫的陶瓷基板之覆晶接合;後者則適用於有機基 板。錫鉛击塊之製備方法有四種:蒸鍍法、電鍍法(Electrop](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/20.892.231.666.130.464/之主流金如Pb與共晶錫鉛合SnP因含鉛量高所以熔點較約為通常Electrop.webp)

![圖 2.11、電極表面上核形成與成長示意圖。[25] 依據法拉第定律(Faraday‟s Law),析出的物理量與所供應的電流成正比, 如式(2.1): nFW itM (2.1) 其中 W 為析出量,i 為電流,t 為時間,M 為析出物分子量,n 為電子轉移價數, F 為法拉第常數。根據式(2.1) ,在理想狀況下,供應多少電荷量,將會獲得相 對的析出量,但一般情況,整體的電荷量並不會百分之百只在析出金屬之間傳 遞,例如在硫酸銅溶液中電鍍銅,因為溶液含有其他離子(如氫離子),在電鍍 過程中,銅離](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/23.892.258.642.108.519/為時間為電子轉移價數為法拉第常數根據之百析出金屬之間他離子.webp)

![圖 2.12、IC 導線與導孔三種填充模式。[33] 2.4.4、添加劑 在深孔電鍍製程中,往往會因內部孔隙生成而影響產品的品質,為了能夠讓 電鍍效果更好,避免內部產生孔隙,因此便在電鍍過程中加入數種添加劑來改 善,例如銅沉積,早在 1966 年就有專利申請[34],專利中使用了硫醇類化合物、 聚乙烯醇類化合物(Poly-ethylene Glycol,PEG)、氯離子與雜環含氮化合物 (N-heterocyclic Compounds),一直沿用至今。然而現今絕大部分的添加劑是各 特用化學品供應商的](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/27.892.314.577.111.419/過程中加入數種添加劑來改如銅沉積早在氯離子一直至今然而現今.webp)

![圖 3.3、電鍍方式:左為掛鍍式,右為湧泉式。[21] 圖 3.4、電鍍裝置示意圖。 本實驗之電鍍步驟如下: (1) 電鍍之前,先用電流密度為 1ASD 電鍍約 30 分鐘,做為起鍍的動作; (2) 用丙酮擦拭試片某區域,露出導電區域,利用銅膠把試片和電阻極小的 電線連接; (3) 把試片浸泡在稀釋的硝酸溶液中(約 5%) ,酸蝕試片表面已氧化的銅, 大約 15 秒,避免以氧化的銅會造成導電度不佳及接合效果不好;接著把試 片浸泡在去離子水中(D.I](https://thumb-ap.123doks.com/thumbv2/9libinfo/8135472.166415/34.892.176.719.116.363/本實驗極小電線連接把試片浸泡在稀釋硝酸溶液中約試片去離子DI.webp)