國立高雄大學電機工程學系

碩士論文

快速熱退火及不同鰭寬度的

NCFET 之電性分析及 HCI 可靠

度研究

The Impact of RTA and Different Fin Widths on the Device

Performance and Reliability of NCFET

研究生:方振宇 撰

指導教授:葉文冠 博士

i

快速熱退火及不同鰭寬度的

NCFET 之電性分析及 HCI 可

靠度研究

指導教授:葉文冠 博士 國立高雄大學電機工程研究所 學生:方振宇 國立高雄大學電機工程研究所摘要

本論文研究了不同鰭寬度對具有負電容效應場效電晶體(NCFET)進行基本電性分析及 可靠度影響,以及元件經過快速熱退火後(RTA)之基本電性及可靠度分析,元件通道與鰭 高度分別固定於40nm 與 20nm,並以 HZO 作為鐵電層。 在不同鰭寬度實驗中,隨著鰭寬度降低,鰭片的體積減少有助於更好的控制元件,因此元件之飽和電流(IDsat)、轉導(GM)、次臨界擺幅(SS)值皆會降低。而經過熱載子(HCI)可

靠度測試後,鰭側壁的缺陷是主要影響電性的原因,因此在較小鰭寬度元件有較大鰭側壁 比例,所以衰退量較為嚴重。 在經過快速熱退火實驗中,我們發現次臨界擺幅(SS)和遲滯(Hysteresis)明顯降低,顯 現出元件開關特性變好,而飽和電流以及 GM值皆上升,元件獲得能量會使得晶格擾動鐵 電層,且經過RTA 後表面缺陷受到氫離子(H+)填補而缺少,使得基本電性得到改善。在經 過HCI 可靠度測試後,我們發現填補缺陷的 H+受到熱載子影響而與Si 鍵結被打斷,而逸 散到元件中形成類似移動電荷的機制,導致經過 RTA 後之元件受到更嚴重的破壞使得電 性變化量衰退更明顯。 關鍵字:鰭寬度、負電容場效電晶體、快速熱退火、HCI、鐵電層

ii

The impact of RTA and Different Fin Widths on the Device

Performance and Reliability of NCFET

Advisor : Dr. Wen-Kuan Yeh Insititute of Electrical Engineering

National University of Kaohsiung

Student: Zhen-Yu Fang Insititute of Electrical Engineering

National University of Kaohsiung

Abstract

In this work, we study the effect of different fin width on field-effect transistor with negative capacitance(NCFET),and the components after rapid thermal annealing(RTA) to conducted the device performance analysis and reliability. The device channel and fin height are fixed at 40nm and 20nm, respectively. And use HZO as the ferroelectric layer.

In experiment with different fin widths, as the fin width decreases, the volume of the fin decrease, which help to better control the components. Therefore, the saturation current(IDsat),transconductance(GM), and Sub-threshold Swing(SS) values of the device will be

reduced. After the Hot Carrier Injection(HCI) reliability test, the defects on the sidewall of the fin are the main reason that affects the electrical properties. Thinner fin width device have a larger proportion of fin sidewalls, so the amount of decline is more serious.

In the rapid thermal annealing experiment, we found that the SS and hysteresis were reduced. It shows that the switching characteristics become better, and both the saturation current and GM

value increase. The device gained energy causes the lattice to disturb the ferroelectric layer. Because the surface defects were filled by H+ after the device passed RTA, the device performance

improved. After the HCI reliability test, we found that the H+ filling the defect is affected by HCI

and the bond with Si is broken. And the mechanism that spills into the device to form similar mobile charge, make the device degradation after RTA more obvious.

iii

誌謝

時光匆匆,兩年的碩士生活即將結束,這段寶貴的時光為我人生中寫下精彩的一章。 回顧這兩年,從一個懵懂無知對半導體產業抱持著憧憬的學士生,十分榮幸的進到了葉文 冠教授的半導體實驗室學習,這兩年的求學過程中,感謝所有幫助過我的人。 首先要感謝的是我的指導教授葉文冠老師,帶我進入了半導體領域,並且提供良好的 實驗室環境與充足的資源,令我在學習上得到莫大的幫助,老師也常常分享業界的經驗, 並且給予我未來就業的方向。再來感謝高雄師範大學的楊宜霖教授及師母章聞奇博士,他 們也教導了我許多知識,有困難時也會耐心地替我解決問題,並提供了許多幫助,感謝以 上三位在半導體專業知識、論文架構與方向、實驗技巧、數據分析等對我耐心的指導與幫 助。也要特別感謝國家奈米實驗室的李耀仁博士給予我們研究上各種幫助以及解決我們的 問題,並不厭其煩教導我們新的知識,另我萬分感激。 我的同學伸亦和尹宏,謝謝你們這兩年與我一起學習與相處,有了你們一起任何困難 我們都能迎刃而解,我們也常常一起討論該怎麼讓實驗更加順利,十分感謝。也感謝學長 煒得與孟琰,在我做實驗以及數據遇到困難時,你們總可以替我解決問題以及指導我正確 的步驟。再來感謝學弟柏融與芳議,在我忙著做實驗以及寫論文沒空時,協助處理實驗室 大小事務,讓我能順利完成實驗,也替實驗室帶來不少歡笑。 我還要特別感謝我的家人,在我求學過程中一路的支持我,並提供我良好的學習環境, 讓我可以放心的好好學習,在我遇到挫折時,總會給我最大的支持與鼓勵,讓我更有信心 可以克服所有困難,陪伴我失落的時候。最後,我要感謝幫助過我的所有人,因為太多人 了在這裡就不一一贅述請見諒,祝福各位身體健康萬事如意。 在這鳳凰花開的季節裡,即將脫離學生的身份,邁向下一個人生的階段,步入職場生 活,感謝所有曾經幫助我的人,在實驗室的這段時光,以後我一定也會特別懷念的。 方振宇 109 年 7 月 于 國立高雄大學電機所iv

目錄

摘要... i Abstract ... ii 誌謝... iii 目錄... iv 圖目錄... vi 第一章 緒論... 1 1.1 研究背景與動機... 1 1.2 文獻探討... 2 1.3 論文架構... 3 第二章 基礎理論與實驗方法... 5 2.1 先進元件製程... 52.1.1 快速熱退火(Rapid Thermal Annealing) ... 5

2.2 負電容效應(Negative Capacitance Effect) ... 6

2.3 元件可靠度量測理論... 7

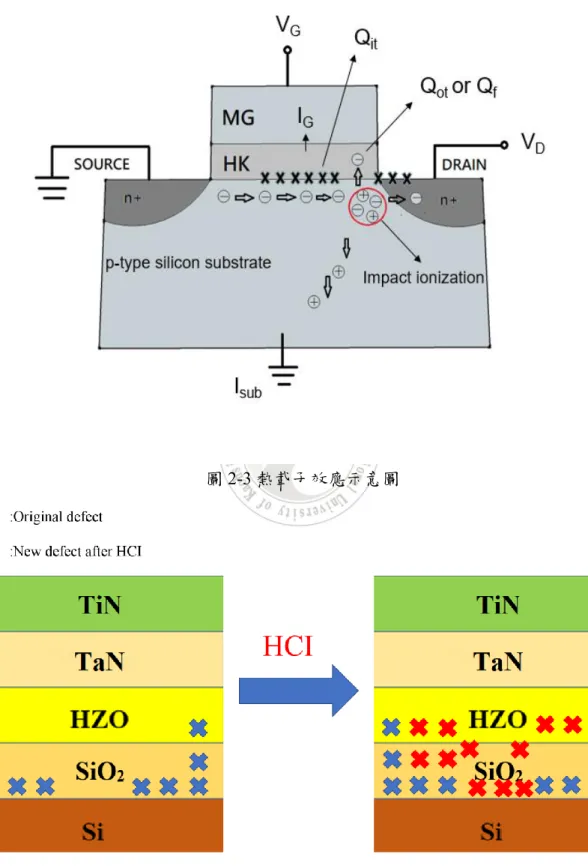

2.3.1 熱載子效應(Hot Carrier Effect,HCE) ... 7

2.4 實驗儀器介紹... 8 2.5 元件基本電性量測... 9 2.6 元件參數電性分析... 9 2.6.1 ID-VG特性曲線 ... 9 2.6.2 ID-VD特性曲線 ... 9 2.6.3 臨界電壓(Vth) ...11 2.6.4 轉移電導(GM) ... 12 2.6.5 次臨界擺幅(S.S.) ... 12 2.6.6 飽和電流(ID,sat) ... 13 2.6.7 遲滯(Hysteresis) ... 13

v 第三章 不同鰭寬度之基本電性分析與可靠度研究... 14 3.1 不同鰭寬度之元件基本電性實驗... 14 3.1.1 實驗設計... 14 3.1.2 基本電性分析... 14 3.2 不同鰭寬度之元件可靠度研究... 15 3.2.1 實驗設計... 15 3.2.2 可靠度研究結果分析... 15 第四章 經過快速熱退火之元件基本電性與可靠度研究... 17 4.1 快速熱退火後之元件基本電性... 17 4.1.1 實驗設計... 17 4.1.2 基本電性分析... 17 4.2 快速熱退火後之可靠度研究... 18 4.2.1 實驗設計... 18 4.2.2 可靠度研究結果分析... 18 第五章 結論與未來展望... 20 5.1 結論... 20 5.2 未來展望... 21 參考文獻... 53

vi

圖目錄

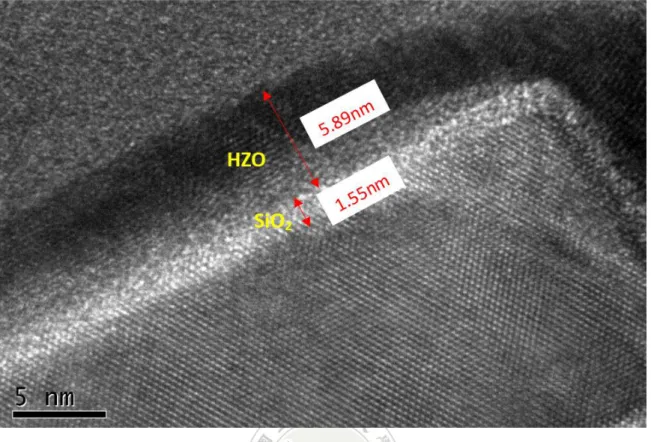

圖2-1 探針座量測系統 ... 22 圖2-2 半導體參數分析儀(Agilent B1500A) ... 22 圖2-3 熱載子效應示意圖 ... 23 圖2-4 NCFET 元件 Gate 端經過熱載子注入後介面缺陷示意圖 ... 23 圖3-1 NCFET 結構示意圖 ... 24圖3-2 NCFET 元件在 Fresh 狀態時之 TEM 圖 ... 24

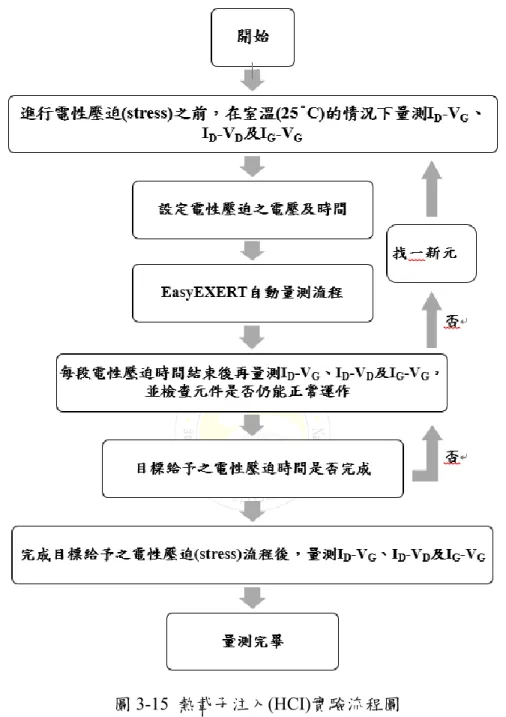

圖 3-3 鰭寬度 20nm 之 ID-VG曲線... 25 圖 3-4 鰭寬度 20nm 之 ID-VD曲線 ... 25 圖 3-5 鰭寬度 20nm 之 GM-VG曲線 ... 26 圖 3-6 鰭寬度 30nm 之 ID-VG曲線 ... 26 圖 3-7 鰭寬度 30nm 之 ID-VD曲線 ... 27 圖3-8 鰭寬度 30nm 之 GM-VG曲線 ... 27 圖 3-9 鰭寬度 400nm 之 ID-VG曲線 ... 28 圖 3-10 鰭寬度 400nm 之 ID-VD曲線 ... 28 圖 3-11 鰭寬度 400nm 之 GM-VG曲線 ... 29 圖3-12 不同鰭寬度之 ID-VG比較圖 ... 29 圖3-13 不同鰭寬度之 ID-VD比較圖 ... 30 圖 3-14 不同鰭寬度之 GM-VG比較圖 ... 30 圖3-15 熱載子注入(HCI)實驗流程圖 ... 31

圖3-16 NCFET 元件經過 5000 秒 HCI 之 TEM 圖 ... 32

圖3-17 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 ID-VG曲線 ... 32

圖3-18 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 ID-VD曲線 ... 33

圖3-19 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 GM-VG曲線 ... 33

圖3-20 鰭寬度 30nm 經過 5000 秒 HCI Stress 之 ID-VG曲線 ... 34

vii 圖3-22 鰭寬度 30nm 經過 5000 秒 HCI Stress 之 GM-VG曲線 ... 35 圖3-23 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 ID-VG曲線 ... 35 圖3-24 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 ID-VD曲線 ... 36 圖3-25 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 GM-VG曲線 ... 36 圖3-26 不同鰭寬度經過 5000 秒 HCI Stress 之 ID-VG比較圖 ... 37 圖3-27 不同鰭寬度經過 5000 秒 HCI Stress 之 ID-VD曲線比較圖 ... 37 圖3-28 不同鰭寬度經過 5000 秒 HCI Stress 之 GM-VG曲線比較圖 ... 38 圖3-29 不同鰭寬度經過 5000 秒 HCI 與 Fresh 之 ID-VG曲線比較圖 ... 38 圖3-30 不同鰭寬度經過 5000 秒 HCI 與 Fresh 之 ID-VD曲線比較圖 ... 39 圖3-31 不同鰭寬度經過 5000 秒 HCI 與 Fresh 之 GM-VG曲線比較圖 ... 39

圖3-32 不同鰭寬度經過 5000 秒 HCI Stress 之 ΔSS(Fwd)-Time 比較圖 ... 40

圖3-33 不同鰭寬度經過 5000 秒 HCI Stress 之 ΔSS(Rvs)-Time 比較圖 ... 40

圖3-34 不同鰭寬度經過 5000 秒 HCI Stress 之 ΔVth-Time 比較圖 ... 41

圖3-35 不同鰭寬度兩側壁距離示意圖 ... 41

圖3-36 不同鰭寬度經過 5000 秒 HCI Stress 之 Hysteresis-Time 比較圖 ... 42

圖3-37 NCFET 元件 Fresh 之晶格 ... 42

圖3-38 NCFET 元件經過 5000 秒 HCI Stress 後之晶格 ... 43

圖3-39 不同鰭寬度經過 5000 秒 HCI Stress 之 SS(Fwd)-Hysteresis 比較圖 ... 43

圖3-40 不同鰭寬度經過 5000 秒 HCI Stress 之 SS(Rvs)-Hysteresis 比較圖 ... 44

圖4-1 未經過快速熱退火之 NCFET Gate 端結構示意圖 ... 44

圖4-2 經過快速熱退火後之 NCFET Gate 端結構示意圖 ... 45

圖4-3 鰭寬度 400nm 下 RTA 前後之 ID-VG曲線 ... 45

圖4-4 鰭寬度 400nm 下 RTA 前後之 ID-VD曲線 ... 46

圖4-5 鰭寬度 400nm 下 RTA 前後之 GM-VG曲線 ... 46

圖4-6 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 ID-VG曲線 ... 47

圖4-7 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 ID-VD曲線 ... 47

圖4-8 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 GM-VG曲線 ... 48

viii

... 48

圖4-10 鰭寬度 400nm 下 RTA 前後 Fresh 與經過 5000 秒 HCI 之 ID-VD曲線比較圖 ... 49

圖4-11 鰭寬度 400nm 下 RTA 前後 Fresh 與經過 5000 秒 HCI 之 GM-VG曲線比較 圖... 49

圖4-12 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 ΔSS-Time 圖 ... 50

圖4-13 電子電動攻擊 H+示意圖 ... 50

圖4-14 H+離子鍵結被打斷逸散到元件示意圖 ... 51

圖4-15 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI 之 Hysteresis-Time 圖 ... 51

1

第一章 緒論

1.1 研究背景與動機

利用半導體材料的獨特性能,人類開發了各種精美的元件,改變了我們的世界。

自 1998 年以來,電子行業是世界上最大的行業,而半導體元件是該行業的基礎。談

到半導體的起源,1947 年,雙極性接面型電晶體(Bipolar Junction Transistor, BJT)誕生 了,它的出現對半導體產業帶來前所未有的影響,William Shockley、John Bardeen 和 Walter Brattain 三位科學家也因發現電晶體效應獲得了諾貝爾物理學獎,這也宣告了 早期體積龐大的真空管時代結束,進入了電晶體的世代,然後開始有了積體電路 (Integrated Circuit, IC)的概念。1960 年,發明了金屬氧化物半導體場效應電晶體 (MOSFET)。 MOSFET 成為積體電路中必不可少的元素,並且是影響過去幾十年最 重要的電晶體結構。

從次微米到深次微米(Deep Submicron)的連續微型化,到當今尺寸小於 0.1μm 的 奈米元件,隨之而來的是製程上的許多困難,摩爾定律也受到物理極限的挑戰。摩 爾定律(Moore's law)是由戈登·摩爾(Gordon Moore)於 1965 年提出的,該定律預測單個

矽晶片上電晶體的數量密度每 18 個月將增加一倍,因此可以在晶片上容納更多的電 晶體。改善製造成本的降低,這可以有效地提高操作速度並降低功耗。因此,半導 體產業的研究以摩爾定律為重要藍圖。 對於更高的元件密度,仍然有必要繼續減小等效通道長度,並且源極和汲極之 間的電場將改變以影響電荷分佈。這些短通道元件表現出許多長通道元件無法預料 的現象,這些現象稱為“短通道效應”[16],並且會產生許多負面影響,例如:漏極引 起的勢壘降低(DIBL),擊穿和穿透現象(Punch-Through),閘極洩漏電流(leakage)等等, 這些影響元件特性的現象限制了小型化製程的發展。 不斷在提出各種抑制上述負面影響的製程方法,如源/汲工程與基板工程,期望 通過改變摻雜濃度來克服短通道效應;Intel 也在 45 nm 的製程中引入高介電系數的介

2

電層,以抑制閘極漏電流並增加物理氧化層厚度,但即便抑制了負面影響,這些製 程 方 法 仍 在 元 件 中 不 斷 微 縮 , 同 時 又 引 入 了 介 面 密 度 較 高 、 降 低 載 子 遷 移 率 (Mobility)等缺點,再次遇到了元件縮小化的瓶頸。許多研究團隊已經開始發展不同

的元件結構,並且在具最大發展潛力的立體結構之鰭式場效電晶體 FinFET 中脫穎而

出,Intel 也於 2012 年在自己 22 nm 的 Ivy Bridge 處理器架構中率先量產 FinFET,後 來各大半導體廠陸續跟進並持續推進製程節點。台灣積體電路公司(TSMC)已量產 10

奈米製程,並已著手興建 5 奈米新廠,此立體架構的 FinFET 成功取代了發展多年的

平面MOSFET。

近年來,迫切開發智慧型手機、物聯網(Internet of things, IOT)等低功耗的電子發 展需求,其中 Tunneling FET(TFET)和 Negative Capacitance FET(NCFET)是目前被證 實有別於傳統Si-based FET 去突破<60mV/dec sub-threshold swing(SS)熱物理極限,使

得電晶體可以在更小的偏壓導通。由於 TFET 最大問題在於 Ion並不容易提升,並且

與 Ioff有 Trade off 之效果,而且負電容還可以跟 FinFET 結合,因此負電容效應場效

電晶體(NCFET)更具有發展成為低功耗電晶體元件優勢[14]。本論文將對具有負電容 效應之場效電晶體在不同鰭寬度下進行電性分析,並經過熱載子注入後來研究其元 件可靠度以及電性變化,目前相關研究不多,因此作為本篇論文的研究方向。

1.2 文獻探討

近30 年來,隨著 CMOS 製程不斷改進和元件微縮,電晶體可以做得越來越小, 晶圓上電晶體數量不斷增加,開關速度也隨著加速提高,電晶體縮小,IC 性能不斷 提高。然而,由於尺寸不斷微縮,再次微米級進入奈米級後,電晶體還面臨物理極 限,這也增加了製程難度,伴隨著嚴重的短通道效應,以及過薄氧化層造成的漏電 流等惱人的問題,尋求其他提升元件性能的方法也非常重要。具有極低的低功率元 件對於新興應用具有吸引力,例如高端計算單元或電池供電的便攜式電子產品,為 了實現低功耗,MOSFET 必須在較小的汲極電壓(VD)下工作,並要求較低的次臨界 擺幅值(SS)以實現相同性能。但是在室溫(300K)下受波茲曼分佈限制的 MOSFET 的3

SS 最小值為 60mV/dec,為了克服這個限制,近年來開發了一種新的元件,稱為 SS 低於60mV/dec 的負電容 FET。

2014 年,在平面 Si MOSFET 上將鐵電 HfZrO2層感應high-K 閘極電介質,接著

在閘極層中使用各種鐵電材料,以獲得更陡峭的 SS[5]。基於 Hf 的 FeFET 與 CMOS 具有高度兼容性的優勢,不久就被引入到 FinFET 結構上,與傳統平面 MOSFET 不 同,3D 構造的 FinFET 在製造時遇到了有關鰭側壁粗糙度的問題,因為鰭側壁的粗糙 度影響了FinFET 整體的性能,例如臨界電壓(Vth)、DIBL 與次臨界擺幅(SS)。對於規 格化的 FinFET 電晶體,通道的寬度需要縮小至奈米級以提高段通道的抗擾度。然而, 具有窄通道寬度的 FinFET 具有嚴重的鰭側壁粗糙度問題和較高的陷阱密度(Dit),這 可能會使負電容FinFET 的 SS 惡化。根據文獻資料,具有較寬鰭寬度的 NCFET 經常 顯示 SS 低於 60mV/dec 超過 ID的兩個數量級[7]。隨著鐵電材料應用於 FinFET 結構 後,SS 低於 60mV/dec 通常低於 ID的兩個數量級[8]。因此通道尺寸可能會影響 NCFET 的電性,從而導致有超陡峭的 SS 產生。 另一方面,事實證明氣體退火製程可有效提高CMOS FinFET 中的表面粗糙度[9], 由於蝕刻側壁引起的介面缺陷可通過氫氣鈍化而減少,因此我們在 NCFET 的閘極推 疊上使用氣體熱退火來改善元件特性,並進一步分析電性,例如SS 和遲滯。

1.3 論文架構

本論文在探討不同鰭寬度(Fin Width)下對具負電容效應之場效電晶體(NCFET)元 件電性影響,為了進行更詳盡,更深入的分析,我們使用熱載子注入實驗對 NCFET 元件進行了長時間的可靠度測試以及探討經過快速熱退火(RTA)後元件的電性受到的 影響。 本論文主要內容分為五個章節: 第一章:緒論 敘述研究動機與背景,以及NCFET 元件文獻探討 第二章:基礎理論與實驗方法4 對負電容效應場效電晶體之結構及製程做概論,再介紹量測所採用的各項軟硬 體設備、實驗方法以及各項電性量測的基礎理論 第三章:不同鰭寬度之元件基本電性與可靠度研究 此章節分為兩節 1.不同鰭寬度之 NCFET 元件基本電性 2.不同鰭寬度之 NCFET 元件可靠度分析 第四章: 經過快速熱退火前後之元件基本電性與可靠度研究 此章節分為兩節 1. 快速熱退火後之元件基本電性 2. 快速熱退火後之可靠度研究結果分析 第五章:結論與未來展望 總結上述實驗結果,統整不同鰭寬度以及快速熱退火後對於負電容場效電晶體 (NCFET)之影響與討論,並提出未來展望的方向。

5

第二章 基礎理論與實驗方法

2.1 先進元件製程

隨著製程技術不斷進步,鰭式場效電晶體已成為全球各大半導體廠的主要產品, 並在元件微縮基礎上對技術的持續投資。本研究使用之元件為高介電材料(High-k)與 具負電容效應之三閘極鰭式場效電晶體(NC-FinFET),為目前最具發展潛力元件之一。 其中採用Hf0.5Zr0.5O2(HZO)薄膜作為 NC-FinFET 鐵電層薄膜,詳細規格如下,元件通道長度(Length)為 40nm,鰭寬度(Fin Width)分別為 20nm、30nm、400nm,鰭高度(Fin Height)為 20nm。

2.1.1

快速熱退火

(Rapid Thermal Annealing)

一般快速熱退火爐是以鹵素燈(Halogen lamp)紅外線照射為主,為了使 Si 順利吸 收光,故放出的紅外線光能量必須大於矽的能帶間隙 1.12ev(Energy Gap),才能讓 Si 進行反應[2]。為了不讓二氧化矽產生反應,紅外光能量必須小於其能隙 8ev。 符合 以上條件的能量轉換為波長的話,約在 0.15~1.10 微米之間,而紅外線光所提供的波 長在 0.75~1000 微米之間,能與 Si 進行反應,而不會與二氧化矽進行反應。由於所 產生的紅外線光波長並不會對不鏽鋼內腔以及石英載具等起反應,因此唯一受到加 熱的就是矽元件,如此一來將可達到極快的升溫效果。 大致上來說在爐管中需要 24 小時的退火過程,在 RTA 機台可以幾分鐘內就完成 同樣的退火效果。而 RTA 與準分子雷射退火比較的話,則具有分子均一性較佳的優 點, 對於做成元件的後的品質會比較平均。

6

2.2 負電容效應(Negative Capacitance Effect)

以往負電容場效電晶體是以穩定 S 形極化電場(PE)曲線理論來解釋,但近年 來有些學者認為應將 NC 效應改為由 FE 極化切換延遲引起的瞬變現象[10-13]來的更 加貼切,透過NCFET 的次臨界擺幅(S.S.)的公式(框線中為 S.S.MOSFET): 𝑆. 𝑆.𝑁𝐶𝐹𝐸𝑇= 𝑑𝑉𝐺 𝑑𝑉𝑖𝑛𝑡 (𝑑𝑉𝑖𝑛𝑡 𝑑𝜑𝑠 ∙ 𝑑𝜑𝑆 𝑑𝑙𝑜𝑔𝐼𝐷 ) 再考慮電荷平衡方程式後我們可以得到差分電壓放大(AV)的定義式: 𝐴𝑣 =𝑑𝑉𝑖𝑛𝑡 𝑑𝑉𝐺 = 1 𝐶𝑝 𝑑𝑄 𝑑𝑉𝐺 差分電壓放大(AV)被用來代替電容匹配理論(總是將 FE 電容是為穩定負數)動

態極化匹配(dynamic polarization matching)被認為是產生 NC 的先決條件,極化值 (P)對鐵電(FE)的方程式為: 𝑑𝑃 𝑑𝑉𝐺 = 𝜕𝑃 𝜕𝑡 𝑑𝑡 𝑑𝑉𝐺+ 𝜕𝑃 𝜕𝑉𝐹𝐸 𝑑𝑉𝐹𝑒 𝑑𝑉𝐺 將式2.2.1 和式 2.2.2 結合後我們可以得到𝐴𝑣的新關係式: 𝐴𝑣 = 1 𝐶𝑝( 𝜕𝑃 𝜕𝑡 𝑑𝑡 𝑑𝑉𝐺+ 𝜕𝑃 𝜕𝑉𝐹𝐸 𝑑𝑉𝐹𝑒 𝑑𝑉𝐺)/𝑑𝑉𝐺 在考慮電壓分配(Voltage divider)後對式 2.2.3 做進一步修正得到: 𝐴𝑣 = 1 𝐶𝑝( 𝜕𝑃 𝜕𝑡 𝑑𝑡 𝑑𝑉𝐺 + 𝜕𝑃 𝜕𝑉𝐹𝐸)/( 𝜕𝑃 𝜕𝑉𝐹𝐸+ 𝐶𝑃) 根據動態極化匹配的測量結果產生 NC 的先決條件為𝐴𝑣>1,而滿足 Av>1 的條 件為𝜕𝑃 𝜕𝑡 ∙ 𝑑𝑡 > 𝑑𝑉𝐺 ∙ 𝐶𝑃(式 2.2.6),其所代表的物理含義是時間引起的極化電荷增量 ((𝜕𝑃 𝜕𝑡∙ 𝑑𝑡))應超過不延遲 CP的電荷增量(𝑑𝑉𝐺∙ 𝐶𝑃) 。 (式 2.2.5) (式 2.2.4) (式 2.2.3) (式 2.2.2) (式 2.2.1)

7

2.3 元件可靠度量測理論

在技術飛速發展的今天,人們對產品質量的要求越來越高。隨著半導體工藝技 術的不斷發展,為了平衡性能和質量,半導體組件的可靠性不可忽視。為了進行可 靠性測試,即使 IC 產品在比正常環境更惡劣的環境條件下運行(例如更高的環境溫 度,更高的工作電壓和環境濕度等),也通常使用加速測試方法。這些因素會大大縮 短測試時間,加快產品失效機制的發生[15]。 可靠性議題是提升半導體工業發展的主要任務,而常見的可靠度研究亦可分 為下列五種:(1) 熱載子注入(Hot Carrier Injection / Effect,HCI/HCE)。

(2) 時依性介電層崩潰(Time Dependent Dielectric Breakdown,TDDB)。 (3) 電致遷移(Electro migration,EM)。

(4) 崩潰電荷(Breakdown Charge,QBD)。

(5) 定電壓應力(Constant Voltage Stress,CVS)。

結合使用各種提高可靠性的方法、可靠性工藝技術來提高整個 IC 產品的可靠

性。最終目標是提高產品產量。

本論文主要以熱載子注入 Hot Carrier Injection (HCI)對不同鰭寬度之具有負電

容效應新型三閘極FinFET 元件做可靠度偏壓測試。就一般傳統 CMOS 元件而言,

熱載子效應對元件可靠度之影響較為嚴重。故為了瞭解 NCFET 的可靠度,我們將

以熱載子效應來對元件做電性壓迫並進一步分析測試後產生之現象,針對不同鰭

寬度之NCFET 進行深入的探討與研究。

2.3.1

熱載子效應

(Hot Carrier Effect,HCE)

熱載子效應(Hot Carrier Effect)是一種會使載子偏離應有路徑的機制,當載子受到 外力影響,脫離了原本的路徑,造成元件漏電流變大,產生氧化層內的缺陷(Oxide Traps)或是形成介面層的缺陷(Interface Defect),造成元件衰退,將使得電晶體的開關

8 特性變差。 當元件的尺寸繼續縮小時,閘極的氧化層厚度變薄,並且通道長度變短,此時 如果施加到元件的電壓沒有同步降低,而是與長通道元件保持一致,則短通道元件 中的橫向電場將急遽增加(電場=電壓/長度),如圖 2-3 的熱載子效應圖所示,當載子 從源極(Source)轉移到汲極(Drain)時,由於較大的橫向電場,該載子將獲得更多的能 量從而成為熱載子,且這些熱載子將在汲極極端附近的通道中累積,當載子能量達 1.3eV 時,在汲極附近會發生碰撞游離(Impact Ionization),然後碰撞出電子電洞對, 形成介面層缺陷,且碰撞出的電子電洞對會流向閘極和基極,注入到閘極的電子將

使氧化層劣化並導致缺陷。當載子能量達3.7eV 時,在閘極氧化層跟基板之間會產生

介面缺陷狀態,當載子流經介面時,載子會被缺陷所束縛,將使元件性能降低並導

致嚴重的退化,如圖2-4 所示,元件經過熱載子注入施壓後,會使元件在介面層缺陷

增加。在超大型積體電路中,熱載子效應通常是電路失效的主要原因,熱載子注入 實驗(Hot Carrier Injection, HCI)利用此元件退化機制來測試元件的可靠性,也是主要 的元件可靠度試驗方法之一。 在半導體物理性質中,電洞的載子遷移率以及平均自由路徑遠小於電子,因此 過去熱載子效應主要用於討論n 型電晶體,但在電晶體進入奈米製程後,橫向電場變 大,使得p 型元件受熱載子效應的影響亦變得不可忽視。

2.4 實驗儀器介紹

本研究中所使用到的儀器介紹如下: 一組八吋晶圓探針台系統(DC Probe Station, 圖2-1),其外以大型金屬暗箱作為隔絕,晶片托盤連接至幫浦,目的是藉由幫浦抽真 空將晶片固定在托盤之上,以防在實驗過程中晶片的位移造成量測誤差。探針台上 放置四組探針座,分別對應電晶體的四個電極: 閘極(Gate)、源極(Source)、基極 (Body)、汲極(Drain),並以四條訊號線連接至安捷倫半導體元件參數分析儀(Agilent B1500A,圖 2-2),再連接至電腦操作,給予待測元件各項量測條件,以取得各項電 性參數。9

2.5 元件基本電性量測

將待測之晶片置於八吋探針台,將四枚探針分別下在四個腳位,閘極(Gate)、源 極(Source)、基極(Body)、汲極(Drain)上,將半導體元件參數分析儀 Agilent B1500A

連接到電腦之後,搭配其專用軟體 Easy EXPERT 給予元件適當的量測條件,取得 ID -VG、ID-VD等電性曲線,並從中萃取出臨界電壓 Vth、次臨界擺幅 S.S.等電性參數,再 藉由繪圖軟體 Origin 8 將各項數據繪製成圖以便進行後續分析。

2.6 元件參數電性分析

2.6.1

I

D-V

G特性曲線

量測設定首先將元件的基極端(Body)跟源極端(Sourse)同時接地(VB=VS=0)及設定 為Common,閘極端(Gate)設定為 Sweep(p 型從-1.5V 到 2.5V)掃描指定範圍的電壓, 汲極端(Drain)給定常數值(p 型元件為-0.05V),即代表取出當元件操作在線性區時, 以閘極電壓為橫軸(X 軸)變數,對應縱軸(Y 軸)之電流值,以 10 為底取對數後所構成 之 圖 形 , 而 透 過 ID-VG 之 間 的 關 係 曲 線 , 可 進 一 步 得 到 臨 界 電 壓(ThresholdVoltage,Vth)、轉移電導(Transconductance,GM)及次臨界擺幅(Subthreshold Swing,S.S.)。

2.6.2

I

D-V

D特性曲線

量測設定首先將元件的基極端(Body)跟源極端(Source)同時接地(VB=VS=0)及設 定為 Common,閘極端(Gate)設定為常數(n 型元件設為 VG=Vth+1V,p 型元件設為 VG=Vth-1V),汲極端(Drain)設定為 Sweep(n 型元件設為從 0V 到+1.8V,p 型元件設為 從0V 到-1.8V)掃描指定範圍的電壓,以汲極電壓(VD)為橫軸(X 軸)變數,相對應縱軸 (Y 軸)之汲極電流值(ID)所構成之圖形。10 汲極電流的產生來自三種工作模式: (一) VGS≤ Vth,閘極與源極之間無通道產生,且汲極電壓高於源極,此時閘 極汲極間更無通道,故汲-源間不導電,稱為截止區(Cut-Off Region)。 (二) VGS≥ Vth,是當閘極電壓超過臨界電壓(VGS>Vth),會產生電子反轉層, 當外加汲極偏壓後,反轉層內汲極端與源極端之間電荷流動,與閘極間產生通道, 形成汲極電流

(I

D)

,可分為兩種情形: (1) VGD≥ Vth, 閘 極 汲 極 間 產 生 通 道 , 稱 為 歐 姆 區 、 三 極 體 區(Ohmic Region;Triode Region),遵守的電流方程式如下: 𝐼𝐷𝑆 = K × [2(𝑉𝐺𝑆− 𝑉𝑡) × 𝑉𝐷𝑆− 𝑉𝐷𝑆2 ] (式 2.6.1) 其中K =1 2× 𝜇𝑛× 𝐶𝑂𝑋× ( 𝑊 𝐿)𝑁 = 1 2𝑘 ́ × 𝑊 𝐿 𝜇𝑛:電子遷移率;𝐶𝑂𝑋:單位面積電容;W:通道寬;L:通道長 (2) VGD≤ Vth,閘極汲極間並無通道產生,稱為飽和區、夾止區(Saturation Region;Pinch-Off Region),遵守的電流方程式如下: 𝐼𝐷𝑆 = 𝐾 × (𝑉𝐺𝑆 − 𝑉𝑡)2 (式 2.6.2) 其中𝑉𝐺𝑆− 𝑉𝑡 又稱為𝑉𝑂𝑉 (Overdrive Voltage)11

2.6.3

臨界電壓

(V

th)

臨界電壓(Threshold Voltage,Vth)是元件的重要的參數。對元件的微縮工程而言, 低功率、低電壓的設計相當為重要。臨界電壓的原理相當複雜,除了與氧化層的特 性有關外,金屬層的特性也有影響。Vth公式如下𝑉𝑡ℎ = ∅𝑚𝑠− 𝑄𝑜𝑥 𝐶𝑜𝑥− 𝑄𝑠𝑐 𝐶𝑜𝑥+ 2𝜑𝐵,因為 Vth與∅𝑚𝑠(金屬閘極語矽基底間的功函數差)有關,經由選擇適當的閘極材料來調整 功函數差是一種控制 Vth的方法。而本篇論文所採用的方法為 GM,MAX外插法。由元 件的 ID-VG轉換曲線中,電流對電壓微分後得元件之轉導對電壓(GM-VG)曲線,由轉 導之最大值對應到轉換曲線上相對應點取切線並交於橫軸,最後再減去(−1 2𝑉𝐷),即 可得到線性區之臨界電壓,這也是目前最廣泛看到取臨界電壓的方法之一。12

2.6.4

轉移電導

(G

M)

轉移電導(Transconductance,GM)乃是 FET 作為放大器重要的參數,其代表輸出 電流(IDS)變化與輸入電壓控制(VGS)的比值,當 GM值越大,即代表微小電壓變化就能 導致很大的輸出電流變化,GM的公式如下: 𝐺𝑀 = 𝜕𝐼𝐷𝑆 𝜕𝑉𝐺𝑆 (式 2.6.3)2.6.5

次臨界擺幅

(S.S.)

評估一個電晶體的開關特性,次臨界擺幅(Subthreshold Swing,S.S.)是一個很重 要的指標,其定義為電流上升十倍所對應之閘極電壓增加值,公式為: S. S. = [∆𝑙𝑜𝑔𝐼𝐷𝑆 ∆𝑉𝐺𝑆 ] −1 (式 2.6.4) 其中VGS為閘極電壓;IDS為汲極電流 我們利用量測得到的 ID-VG圖,萃取出電流上升 10 倍所對應之電壓差值,利用 上述公式得知。由公式可知道ID-VG圖斜率的倒數即代表次臨界擺幅(S.S.),當斜率越 大,意即次臨界擺幅越小,代表只需要變動較少的閘極電壓便可控制元件,電晶體 的開關控制特性越優異。反之當斜率越小,即次臨界擺幅越大,即則代表元件無法 快速且明確的關閉,代表其開關特性較差。另外在探討漏電流問題時,次臨界擺幅 也能派上用場。13

2.6.6

飽和電流

(I

D,sat)

ID的電性量測結果,以n型為例,採用閘極電壓(Vth+1V)所量測出汲極飽和電流

(Drain Saturation Current,ID,sat)來作討論。當通道長度越長時,汲極的電壓造成通

道內汲極-源極電場效應越小,使得驅動電流減少,此特性符合傳統MOSFET之飽和 區電流公式(6)所示: ID(sat) = 1 2μCox W L (VGS− Vth) 2 (式 2.6.5) 在固定鰭長度下,當鰭寬度越大時,驅動電流越大。鰭寬度增加時,其通道的 體積亦會增加,內部通道能提供傳輸的載子也隨之增加,使元件的驅動電流也會越 高。

2.6.7

遲滯

(Hysteresis)

磁滯現象是變量對說明變量的影響不能在短時間內完成。在此過程中通常會有 時間滯後,也就是說,變量需要一段時間才能完全影響解釋變量。而本論文主要探 討的是鐵電極化導致的遲滯效應,大多數材料的極化與施加電場成線性比例,並且 非線性效應不明顯,這種極化稱為介電極化,一些稱為順電材料的材料具有更明顯 的線性極化效應。因此,與極化曲線的斜率相對應的介電常數是所施加電場的函數, 除非線性效應外,鐵電材料中還存在自發極化。鐵電材料之間的區別在於,在施加 電場的作用下,其自發極化可以反轉,從而產生遲滯曲線。14

第三章 不同鰭寬度之基本電性分析與可靠度

研究

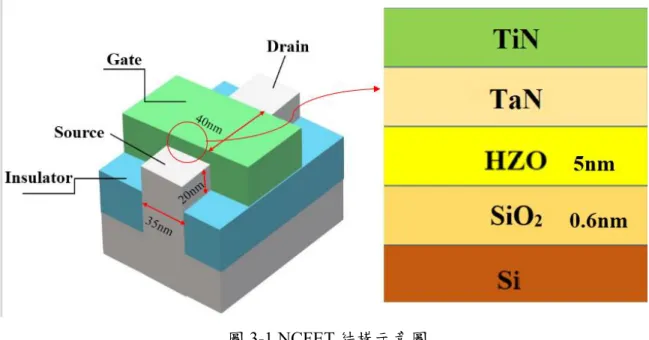

為了突破 SS<60mV/dec 的熱物理限制,使電晶體可以在更小的偏壓下啟動,因 而發展出負電容場效電晶體(NCFET),相關研究漸漸被發表,然而對於此結構的基 本電性與可靠度影響之研究仍不多。本節論文將探討改變不同鰭寬度(Width)下 N 型 NCFET 之元件基本電性與可靠度的影響,圖 3-1 為 NCFET 結構示意圖。其構造為在 Si 基板上有一層 0.6nm 的 SiO2做為介面層(IL),之後通過 ALD 在 250ºC 下沉積 5nm 的HZO 薄膜做為鐵電層,在鐵電層上面是元件的金屬閘極層是 TaN,而 50nm 厚 TIN 則 為金屬層。

3.1 不同鰭寬度之元件基本電性實驗

3.1.1

實驗設計

本研究使用的的元件是通道長度(Length)為 40nm,鰭寬度(Fin Width)分別為 20nm、30nm、400nm,鰭高度(Fin Height)為 20nm 並使用 HZrO2薄膜做為鐵電層的

NCFET 元件,圖 3-1 為 NCFET 元件 Gate 端結構示意圖, 圖 3-2 為元件在 Fresh 狀

態時的TEM 圖,圖上標示 5.85nm 地方為鐵電層 HZO,而結晶部分為 Si 基板,並藉

由 keysight B1500A 取得之 ID-VG曲線、ID-VD曲線,以及萃取出之臨界電壓(Vth)、

次臨界擺幅(SS)等參數,分別探討在不同鰭寬度下,對於元件電性有何不同影響。

3.1.2

基本電性分析

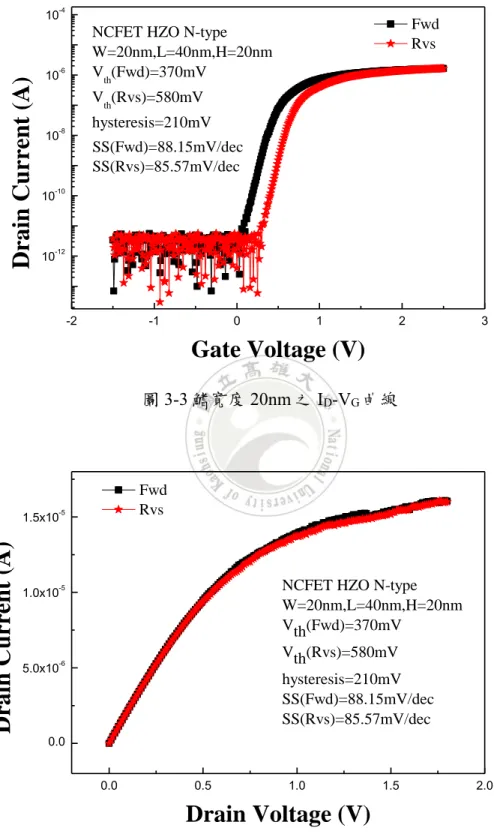

圖3-3、圖 3-4、圖 3-5 分別為鰭寬度 20nm 之 ID-VG曲線、ID-VD曲線、GM-VG曲

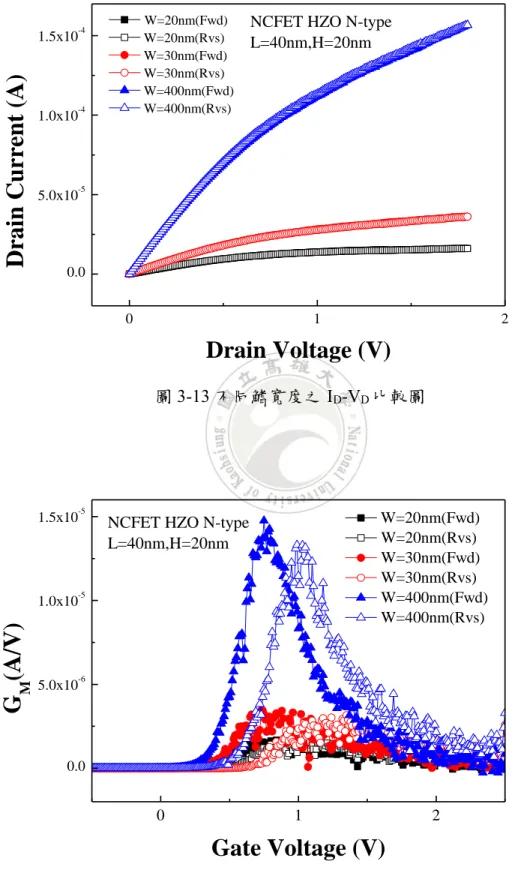

15 線,圖 3-9、圖 3-10、圖 3-11 分別為鰭寬度 400nm 之 ID-VG曲線、ID-VD曲線、GM -VG曲線,再來將三者不同鰭寬度放在一起做比較,圖3-12、圖 3-13、圖 3-14 分別為 不同鰭寬度之ID-VG曲線比較圖、ID-VD曲線比較圖、GM-VG曲線比較圖。 我們可以發現鰭寬度越小的元件,其次臨界擺幅(SS)、飽和電流(IDsat)與轉導(GM) 值越小,因為減少鰭片的體積有助於更好的控制元件,因此鰭寬度較小的元件有較 小的閘極控制面積,這會使得驅動能力上升[3]。

3.2 不同鰭寬度之元件可靠度研究

3.2.1

實驗設計

本節我們對鰭寬度 20nm、30nm、400nm 之元件進行熱載子注入(HCI)實驗來探 討可靠度,圖 3-15 為熱載子注入(HCI)之實驗流程圖,在其他參數相同下觀察他們的退化情形,圖3-16 為元件經過 5000 秒 HCI 施壓後的 TEM 圖,從 TEM 圖中我們觀察

到元件經過 HCI 施壓後,被載子碰撞後形成的電洞影響了介面層,導致介面層與元

件Fresh 狀態下有著變厚的趨勢,顯現出元件經過 HCI 後會影響元件本身的結構。

在 進 行 HCI 可 靠 度 實 驗 時 , 將 元 件 的 基 極 端(Body)跟 源 極 端(Sourse)接 地 (VB=VS=0),而閘極端(Gate)與汲極端(Drain)給定偏壓 2.3V 並壓力測試時間共 5000 秒, 中途取數個固定時間點進行元件之電性量測,再做 ID-VG及 ID-VD曲線並萃取出相關 電 性 參 數 , 比 較 不 同 鰭 寬 度 下 的 元 件 臨 界 電 壓(Vth)、 次 臨 界 擺 幅(SS)、 遲 滯 (Hysteresis)變化量以及次臨界擺幅與遲滯的分布圖,並分析不同鰭寬度經過 HCI 後的 影響。

3.2.2

可靠度研究結果分析

圖3-17、圖 3-18、圖 3-19 分別為鰭寬度 20nm 經過 5000 秒 HCI Stress 之 ID-VG、16

ID-VD、GM-VG曲線圖,圖 3-20、圖 3-21、圖 3-22 分別為鰭寬度 30nm 經過 5000 秒

HCI Stress 之 ID-VG、ID-VD、GM-VG曲線圖,圖3-23、3-24、3-25 分別為鰭寬度 400nm

經過5000 秒 HCI Stress 之 ID-VG、ID-VD、GM-VG曲線圖。

接著我們把所有鰭寬度放一起做比較圖,圖3-26、3-27、3-28 分別為 ID-VG、ID -VD、GM-VG曲線比較圖,接著我們把元件 Fresh 狀態時和經過 5000 秒 HCI 施壓後的 狀態放在一起做比較,如圖3-29、3-30、3-31,我們可以發現經過 5000 秒 HCI Stress 後,鰭寬度越大之次臨界擺幅(SS)、飽和電流(IDsat)與轉導(GM)值還是大於鰭寬度小 的元件,這跟我們3.1.2 節的結果符合,而且每個元件經過熱載子注入(HCI)施壓後其 電性都有所衰退,但是最大的鰭寬度400nm 元件經過 HCI Stress 後退化不明顯,顯然 較小的鰭寬度具有更大的漏電流降級與臨界電壓變化。再來我們看到圖 32、圖 3-33、圖 3-34 中發現,次臨界擺幅(SS)以及臨界電壓(Vth)在較小的鰭寬度中有較大的變 化量,而較大的鰭寬度之元件雖也有衰退卻不明顯。主要是鰭寬度小的元件之兩側 壁距離小於鰭寬度後之元件,如圖 3-35 為不同鰭寬度兩側壁距離示意圖,因為鰭側 壁的粗糙度影響了 FinFET 整體的性能,這可能會使負電容 FinFET 的電性惡化[6], 因此經過 HCI 施壓後,鰭寬度較小的元件受到鰭側壁影響的比例較高,對於鰭側壁 缺陷增加更為敏感,因此鰭寬度小的元件衰退量大於鰭寬度大的元件。 但在圖 3-36 中我們發現,鰭寬度小的元件之遲滯經過 HCI Stress 後越來越小, 而鰭寬度大的元件反之,我們發現 HCI 和其他退火機制一樣都會給予元件能量[4]使 得晶格轉換,如圖3-37 元件 fresh 時的晶格,圖 3-38 為元件經過 5000 秒 HCI 施壓後 的晶格,而鰭寬度小的元件之晶格受到橫向電場能量影響的比例較高,導致鰭寬度 小的元件在經過 HCI 後產生晶格轉換擾動了鐵電層而有了負電容效應,使得遲滯變 小,而鰭寬度大的元件則因為能量不足,所以晶格轉換比例較低無法影響鐵電層, 只表現出單純的可靠度衰退,導致遲滯越來越大。 最後我們統整以上數據製成次臨界擺幅(SS)和遲滯(Hysteresis)的分布圖表示在圖 3-39 和圖 3-40,可以發現到,當鰭寬度不斷增加,SS 值也會跟著增加而集中分布, 這跟我們 3.1.2 節的理論一致。而鰭寬度較小的元件,因為受到負電容效應影響,其 SS 值會隨著遲滯變化上下浮動。

17

第四章 經過快速熱退火之元件基本電性與可

靠度研究

4.1 快速熱退火後之元件基本電性

4.1.1

實驗設計

此部分探討 N-type NCFET 經過快速熱退火後的基本電性影響,本節使用之NCFET 元件其鰭寬度(fin Width,W)為 400nm,通道長度(Gate lengh,L)為 40nm,鰭高 度(Fin height,H)為 20nm,之後將元件透過 30 秒 700ºC 快速熱退火將 HZO 薄膜轉變 為結晶狀態。 因為在第三節實驗中發現鰭寬度越寬之元件受熱載子影響較小,因此選擇本論 文中鰭寬度最寬400nm 之元件,主要探討在快速熱退火前後的影響。 此次使用的元件分為後續再做一次 RTA 處理以及未經後續處理的兩種,後續 RTA 的參數為,通過 95%的 N2及5%的 H2於400ºC 持續 5 分鐘,此步驟旨在利用 H2 修補界面層的缺陷。圖4-1 為 NCFET 元件 Gate 端未經過快速熱退火結構示意圖,圖 4-2 為經過快速熱退火後之 NCFET 元件 Gate 端結構示意圖,我們可以發現,快速熱 退火後,元件表面的缺陷被H2填補了,因此表面的缺陷減少。

4.1.2

基本電性分析

圖 4-3 為 ID-VG曲線,可以發現在經過快速熱退火(RTA)後,其整體趨勢向右偏 移,而次臨界擺幅(SS)和遲滯(Hysteresis)明顯降低,顯現出元件開關特性變好,接著 看到圖4-4 的 ID-VD曲線,我們看到了元件經過RTA 後,飽和電流(IDsat)微幅上升了,18 再來看到4-5 的 GM-VG曲線,整體 ID-VG曲線往右偏移而 GM值也些微變高,總結上 述觀察發現,當元件經過RTA 後,SS 值變得更低,我們發現 RTA 會給予元件能量導 致鐵電層晶格震動,影響鐵電材料,使得負電容特性更明顯,而元件因為介面層缺 陷受到氫氣填補而缺少,導致其他基本電性也得到改善。

4.2 快速熱退火後之可靠度研究

4.2.1

實驗設計

熱載子注入(HCI)之實驗流程如圖 3-14 所示,我們將探討元件經過 RTA 後,再對其做HCI 施壓,與未經過 RTA 之元件做比較,觀察元件 RTA 前後,HCI 對其的影響。

本節所有測量元件的鰭寬度、通道長度、鰭高度分別固定在 400nm、40nm、 20nm。進行 HCI 施壓測試時,我們將元件的基極端(Body)、源極端(Sourse)同時接地 (VB=VS=0),而汲極端(Drain)和閘極端(Gate)給定偏壓(VG=VD=2.3V),壓力測試時間 共進行 5000 秒,中途取數個固定時間點進行元件之電性量測,再測量出其 ID-VG、 ID-VD曲線並從中萃取出相關電性參數,比較元件經過RTA 前後的臨界電壓(Vth)、轉 導(GM)、次臨界擺幅(SS)等電性參數,來探討 N 型 NCFET 在經過 RTA 後對元件的可 靠度影響。

4.2.2

可靠度研究結果分析

圖4-6、圖 4-7、圖 4-8 分別為鰭寬度 400nm 下是否經過快速熱退火(RTA)且經過 5000 秒 HCI Stress 之 ID-VG曲線、ID-VG曲線以及GM-VG曲線,然後我們將RTA 前後之Fresh 狀態元件以及經過 5000 秒 HCI Stress 元件放在一起做比較,如圖 4-9、4-10、 4-11,我們發現 RTA 後之元件的次臨界擺幅(SS)衰退量大於未經過快速熱退火(RTA)

19 而我們從圖 4-9 的 ID-VG曲線萃取出各時間點的 SS 值並做出 ΔSS 變化圖,如圖 4-12 所示,可以發現到 ΔSS 值都隨著施壓時間越趨退化,而經過 RTA 之元件的退化 量高於未經RTA 之元件,我們發現元件經過 RTA 後,表面的缺陷被氫氣所填補,導 致電性改善,而對其做熱載子注入(HCI)施壓後,原本填補缺陷的 Si-H 鍵結被打斷, 如圖 4-13 所示,而氫離子(H+)因此逸散到元件中,形成類似移動電荷的機制,如圖 4-14 所示,並破壞元件,再加上原本經過 HCI 的電子電動對破壞後,使得經過 RTA 後之元件電性退化得更顯著。 再來我們看到圖 4-15 為遲滯(Hysteresis)變化量圖,兩者施壓後的遲滯皆有增加 且趨勢一致,最後我們看到圖 4-16 為 SS 對遲滯的分布圖,經過 RTA 後的元件因為 缺陷被填補會使得開關特性變好,因此經過RTA 後之元件 SS 值集中在較低的位置, 而未經 RTA 之元件集中在 SS 值較高的位置,且因為電性得到改善,因此 RTA 元件 的SS 分布較為集中。

20

第五章 結論與未來展望

5.1 結論

本論文用不同鰭寬度與經過 RTA 前後兩種設計參數對元件特性的影響作為研究 方向,兩者設計參數皆對於N 型負電容效應場效電晶體在 Fresh 狀態下之基本電性, 以及經過5000 秒熱載子注入實驗下的可靠度分析。 在不同鰭寬度的實驗中,我們使用了20nm、30nm、400nm 三種不同鰭寬度,且 通道長度與鰭高度皆分別固定在 40nm 與 20nm。在此章節中我們認為,隨著鰭寬度 減少,我們發現減少鰭片的體積有助於更好的控制元件,使得閘極控制能力提高, 因此元件之飽和電流(IDsat)、轉導(GM)、次臨界擺幅(SS)值皆會降低。接著經過熱載 子可靠度測試後,在較小的鰭寬度中電性有較大的衰退量,而較大的鰭寬度之元件 雖也有衰退卻不顯著。我們發現鰭寬度小的元件在經過 HCI 後會發生晶格轉換導致 晶格排列改變擾動鐵電層,產生負電容效應,使得遲滯變小,而鰭寬度大的元件則 因為橫向電場能量不夠,使晶格轉換比例較低而無法影響鐵電層,導致遲滯隨著 HCI 後缺陷增加而變大。 而 在 元 件 經 過 快 速 熱 退 火 前 後 的 實 驗 中 , 我 們 發 現 次 臨 界 擺 幅(SS)和遲滯 (Hysteresis)明顯降低,顯現出元件開關特性變好,而飽和電流(IDsat)微幅上升以及 GM 值也些微變高,我們認為主要是因為元件得到能量擾動了鐵電層晶格,影響鐵電材 料,使得SS 及遲滯都下降,且元件因為經過 RTA 後表面缺陷受到氫氣填補而減少, 使得基本電性也得到改善。接著經過熱載子可靠度測試後,我們發現填補缺陷的 Si-H 鍵受到熱載子影響而被電子電動對打斷,因此氫離子(Si-H+)逸散到元件中形成類似移 動電荷機制,導致經過 RTA 後之元件受到更嚴重的破壞使得電性變化量衰退更明顯。21

5.2 未來展望

為了突破電晶體次臨界擺幅(SS) < 60 mV/dec 的熱限制,NCFET 元件結構已漸漸 被大家重視。本論文鰭寬度最大只到 400nm,表現出對鐵電層影響不明顯,希望未 來研究方面能增加更多的鰭寬度並觀察是否影響NCFET 元件之鐵電層。 並且在經過熱載子注入(HCI)靠度實驗後,我們發現施加能量會導致晶格轉換, 希望研究未來能加入晶格轉換對NCFET 元件電性影響更深入的探討。 另外在快速熱退火實驗中,我們發現氫離子(H+)受到 HCI 施壓後鍵結被電子電動 對打斷而逸散到元件中形成和移動電荷類似的機制,因此希望未來能去了解氫離子 (H+)是如何在元件中運動,進而破壞元件導致元件衰退。22

圖2-1 探針座量測系統

23

圖2-3 熱載子效應示意圖

24

圖3-1 NCFET 結構示意圖

25 -2 -1 0 1 2 3 10-12 10-10 10-8 10-6 10-4

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

Fwd Rvs NCFET HZO N-typeW=20nm,L=40nm,H=20nm V th(Fwd)=370mV Vth(Rvs)=580mV hysteresis=210mV SS(Fwd)=88.15mV/dec SS(Rvs)=85.57mV/dec 圖 3-3 鰭寬度 20nm 之 ID-VG曲線 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-6 1.0x10-5 1.5x10-5

NCFET HZO N-type W=20nm,L=40nm,H=20nm Vth(Fwd)=370mV Vth(Rvs)=580mV hysteresis=210mV SS(Fwd)=88.15mV/dec SS(Rvs)=85.57mV/dec

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

Fwd Rvs 圖 3-4 鰭寬度 20nm 之 ID-VD曲線26 -2 -1 0 1 2 3 -5.0x10-7 0.0 5.0x10-7 1.0x10-6 1.5x10-6 2.0x10-6

NCFET HZO N-type W=20nm,L=40nm,H=20nm Vth(Fwd)=370mV Vth(Rvs)=580mV hysteresis=210mV SS(Fwd)=88.15mV/dec SS(Rvs)=85.57mV/dec

G

M(A/V)

Gate Voltage (V)

Fwd Rvs 圖 3-5 鰭寬度 20nm 之 GM-VG曲線 -2 -1 0 1 2 3 10-14 10-12 10-10 10-8 10-6NCFET HZO N-type W=30nm,L=40nm,H=20nm Vth(Fwd)=240mV V th(Rvs)=490mV Hysteresis=250mV SS(Fwd)=121.74mV/dec SS(Rvs)=126.99mV/dec

Drain

Cu

rr

ent(A

)

Gate Voltage(V)

Fwd Rvs 圖 3-6 鰭寬度 30nm 之 ID-VG曲線27 0.0 0.5 1.0 1.5 2.0 0.0 1.0x10-5 2.0x10-5 3.0x10-5 4.0x10-5

NCFET HZO N-type W=30nm,L=40nm,H=20nm Vth(Fwd)=240mV V th(Rvs)=490mV Hysteresis=250mV SS(Fwd)=121.74mV/dec SS(Rvs)=126.99mV/dec

Drain

Cu

rr

ent(A

)

Drain Voltage(V)

Fwd Rvs 圖 3-7 鰭寬度 30nm 之 ID-VD曲線 -2 -1 0 1 2 3 0.0 1.0x10-6 2.0x10-6 3.0x10-64.0x10-6 NCFET HZO N-type W=30nm,L=40nm,H=20nm

Vth(Fwd)=240mV V th(Rvs)=490mV Hysteresis=250mV SS(Fwd)=121.74mV/dec SS(Rvs)=126.99mV/dec

G

M(A/V)

Gate Voltage(V)

Fwd Rvs 圖3-8 鰭寬度 30nm 之 GM-VG曲線28 -1 0 1 2 3 10-14 10-12 10-10 10-8 10-6 10-4

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

Fwd RvsNCFET HZO N-type

W=400nm,L=40nm,H=20nm V th(Fwd)=220mV V th(Rvs)=390mV Hysteresis=170mV SS(Fwd)=151.9mV/dec SS(Rvs)=153.4mV/dec 圖 3-9 鰭寬度 400nm 之 ID-VG曲線 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-5 1.0x10-4 1.5x10-4

NCFET HZO N-type

W=400nm,L=40nm,H=20nm

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

Fwd Rvs 圖 3-10 鰭寬度 400nm 之 ID-VD曲線29 -2 -1 0 1 2 3 0.0 5.0x10-6 1.0x10-5 1.5x10-5

NCFET HZO N-type

W=400nm,L=40nm,H=20nm

G

M(A/V)

Gate Voltage (V)

Fwd Rvs 圖 3-11 鰭寬度 400nm 之 GM-VG曲線 0 1 2 10-14 10-12 10-10 10-8 10-6Drai

n C

urre

nt

(A)

Gate Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400nm(Rvs) NCFET HZO N-type L=40nm,H=20nmSS=88

SS=121

SS=151

30 0 1 2 0.0 5.0x10-5 1.0x10-4 1.5x10-4

Drai

n C

urre

nt

(A)

Drain Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400nm(Rvs)NCFET HZO N-type L=40nm,H=20nm 圖3-13 不同鰭寬度之 ID-VD比較圖 0 1 2 0.0 5.0x10-6 1.0x10-5 1.5x10-5

G

M(A

/V)

Gate Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400nm(Rvs) NCFET HZO N-typeL=40nm,H=20nm

31

32

圖3-16 NCFET 元件經過 5000 秒 HCI 之 TEM 圖

-2 -1 0 1 2 10-12 10-10 10-8 10-6 10-4

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

neg~pos pos~neg NCFET HZO N-typeW=20nm,L=40nm,H=20nm HCI: V G=VD=2.3V V th(Fwd)=770mV Vth(Rvs)=1000mV Hysteresis=230mV SS(Fwd)=112.2mV/dec SS(Rvs)=118.4mV/dec 圖3-17 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 ID-VG曲線

33 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-6 1.0x10-5 1.5x10-5 2.0x10-5 2.5x10-5

NCFET HZO N-type W=20nm,L=40nm,H=20nm HCI: V G=VD=2.3V V th(Fwd)=770mV Vth(Rvs)=1000mV Hysteresis=230mV SS(Fwd)=112.2mV/dec SS(Rvs)=118.4mV/dec

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

Fwd Rvs 圖3-18 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 ID-VD曲線 -2 -1 0 1 2 3 -5.0x10-7 0.0 5.0x10-7 1.0x10-6 1.5x10-6NCFET HZO N-type W=20nm,L=40nm,H=20nm HCI: V G=VD=2.3V V th(Fwd)=770mV Vth(Rvs)=1000mV Hysteresis=230mV SS(Fwd)=112.2mV/dec SS(Rvs)=118.4mV/dec

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

Fwd Rvs 圖3-19 鰭寬度 20nm 經過 5000 秒 HCI Stress 之 GM-VG曲線34 -2 -1 0 1 2 3 10-15 10-13 10-11 10-9 10-7 10-5

NCFET HZO N-type W=30nm,L=40nm,H=20nm HCI: V G=VD=2.3V Vth(Fwd)=780mV Vth(Rvs)=960mV Hysteresis=180mV SS(Fwd)=142.32mV/dec SS(Rvs)=134.13mV/dec

Drain

Cu

rr

ent(A

)

Gate Voltage(V)

Fwd Rvs 圖3-20 鰭寬度 30nm 經過 5000 秒 HCI Stress 之 ID-VG曲線 0.0 0.5 1.0 1.5 2.0 0.0 1.0x10-5 2.0x10-5 3.0x10-5 4.0x10-5NCFET HZO N-type W=30nm,L=40nm,H=20nm HCI: V G=VD=2.3V Vth(Fwd)=780mV Vth(Rvs)=960mV Hysteresis=180mV SS(Fwd)=142.32mV/dec SS(Rvs)=134.13mV/dec

Drain

Cu

rr

ent(A

)

Drain Voltage(V)

Fwd Rvs 圖3-21 鰭寬度 30nm 經過 5000 秒 HCI Stress 之 ID-VD曲線35 -2 -1 0 1 2 3 0.0 1.0x10-6 2.0x10-6 3.0x10-6

NCFET HZO N-type W=30nm,L=40nm,H=20nm HCI: V G=VD=2.3V Vth(Fwd)=780mV Vth(Rvs)=960mV Hysteresis=180mV SS(Fwd)=142.32mV/dec SS(Rvs)=134.13mV/dec

G

M(A/V)

Gate Voltage(V)

Fwd Rvs 圖3-22 鰭寬度 30nm 經過 5000 秒 HCI Stress 之 GM-VG曲線 -1 0 1 2 3 10-12 10-10 10-8 10-6Drain

Cu

rr

ent

(A)

Gate Voltage (V)

Fwd RvsNCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:VG=VG=2.3V Vth(Fwd)=500mV Vth(Rvs)=730mV Hysteresis=230mV SS(Fwd)=156.38mV/dec SS(Rvs)=162.07mV/dec 圖3-23 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 ID-VG曲線

36 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-5 1.0x10-4 1.5x10-4

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:VG=VG=2.3V Vth(Fwd)=500mV Vth(Rvs)=730mV Hysteresis=230mV SS(Fwd)=156.38mV/dec SS(Rvs)=162.07mV/dec

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

Fwd Rvs 圖3-24 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 ID-VD曲線 -2 -1 0 1 2 3 0.0 5.0x10-6 1.0x10-5 1.5x10-5NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:VG=VG=2.3V Vth(Fwd)=500mV Vth(Rvs)=730mV Hysteresis=230mV SS(Fwd)=156.38mV/dec SS(Rvs)=162.07mV/dec

G

M(A/V)

Gate Voltage (V)

Fwd Rvs 圖3-25 鰭寬度 400nm 經過 5000 秒 HCI Stress 之 GM-VG曲線37 0 1 2 10-12 10-10 10-8 10-6

Drai

n C

urre

nt

(A)

Gate Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fed) W=400nm(Rvs) NCFET HZO N-typeL=40nm,H=20nm HCI:VG=VD=2.3V SS=156 SS=142 SS=112 圖3-26 不同鰭寬度經過 5000 秒 HCI Stress 之 ID-VG比較圖 0 1 2 0.0 5.0x10-5 1.0x10-4 1.5x10-4

Drai

n C

urre

nt

(A)

Drain Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400(Rvs)NCFET HZO N-type L=40nm,H=20nm HCI:VG=VD=2.3V

38 0 1 2 0.0 5.0x10-6 1.0x10-5 1.5x10-5

G

M(A

/V)

Gate Voltage (V)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400nm(Rvs) NCFET HZO N-typeL=40nm,H=20nm HCI:VG=VD=2.3V 圖3-28 不同鰭寬度經過 5000 秒 HCI Stress 之 GM-VG曲線比較圖 0 1 2 10-12 10-10 10-8 10-6 SS=88 SS=121 SS=151

Drai

n C

urre

nt

(A)

Gate Voltage (V)

W=20nm(Fresh) W=20nm(5000s) W=30nm(Fresh) W=30nm(5000s) W=400nm(Fresh) W=400nm(5000s) NCFET HZO N-typeL=40nm,H=20nm HCI:VG=VD=2.3V SS=156 SS=142 SS=112 圖3-29 不同鰭寬度經過 5000 秒 HCI 與 Fresh 之 ID-VG曲線比較圖

39 0 1 2 0.0 5.0x10-5 1.0x10-4 1.5x10-4

Drai

n C

urre

nt

(A)

Drain Voltage (V)

W=20nm(Fresh) W=20nm(5000s) W=30nm(Fresh) W=30nm(5000s) W=400nm(Fresh) W=400nm(5000s)NCFET HZO N-type L=40nm,H=20nm HCI:V G=VD=2.3V 圖3-30 不同鰭寬度經過 5000 秒 HCI 與 Fresh 之 ID-VD曲線比較圖 0 1 2 0.0 5.0x10-6 1.0x10-5 1.5x10-5

G

M(A

/V)

Gate Voltage (V)

W=20nm(fresh) W=20nm(5000s) W=30nm(fresh) W=30nm(5000s) W=400nm(fresh) W=400nm(Rvs) NCFET HZO N-type L=40nm,H=20nm HCI:VG=VD=2.3V

40 1 10 100 1000 10000 0 5 10 15 20 25 30

SS

(Fw

d)

(mV/dec)

Time (S)

W=20nm W=30nm W=400nm NCFET HZO N-type L=40nm,H=20nm HCI:VG=VD=2.3V圖3-32 不同鰭寬度經過 5000 秒 HCI Stress 之 ΔSS(Fwd)-Time 比較圖

1 10 100 1000 10000 -5 0 5 10 15 20 25 30 35 40

SS

(Rvs

)

(mV

/dec

)

Time (S)

W=20nm W=30nm W=400nm NCFET HZO L=40nm,H=20nm HCI:VG=VD=2.3V41 1 10 100 1000 10000 0 100 200 300 400 500 600

NCFET HZO N-type L=40nm,H=20nm HCI:VG=VD=2.3V

Vt

h (mV

)

Time (S)

W=20nm(Fwd) W=20nm(Rvs) W=30nm(Fwd) W=30nm(Rvs) W=400nm(Fwd) W=400nm(Rvs)圖3-34 不同鰭寬度經過 5000 秒 HCI Stress 之 ΔVth-Time 比較圖

42 1 10 100 1000 10000 120 140 160 180 200 220 240 260 280 300

Hyster

esi

s (mV)

Time (S)

W=20nm W=30nm W=400nm NCFET HZO N-typeL=40nm,H=20nm HCI:V

G=VD=2.3V

圖3-36 不同鰭寬度經過 5000 秒 HCI Stress 之 Hysteresis-Time 比較圖

43

圖3-38 NCFET 元件經過 5000 秒 HCI Stress 後之晶格

100 150 200 250 300 80 100 120 140 160 W=20nm W=30nm W=400nm

SS

(Fwd)

(mV

/dec

)

Hysteresis (mV)

NCFET HZO N-type L=40nm,H=20nm HCI:VG=VD=2.3V

44 150 200 250 100 120 140 160 W=20nm W=30nm W=400nm

SS

(R

v

s) (mV

/dec

)

Hysteresis (mV)

NCFET HZO N-type L=40nm, H=20nm HCI:V

G=VD=2.3V

圖3-40 不同鰭寬度經過 5000 秒 HCI Stress 之 SS(Rvs)-Hysteresis 比較圖

45 圖4-2 經過快速熱退火後之 NCFET Gate 端結構示意圖 0 1 10-12 10-10 10-8 10-6

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs)NCFET HZO N-type

W=400nm,L=40nm,H=20nm RTA: After 5min with 95%N2,5%H2 in 400C Hysteresis(W/O RTA)=170mV Hysteresis(W/ RTA)=120mV SS=125 SS=151 圖4-3 鰭寬度 400nm 下 RTA 前後之 ID-VG曲線

46 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-5 1.0x10-4 1.5x10-4

NCFET HZO N-type

W=400nm,L=40nm,H=20nm RTA: After 5min with 95%N 2,5%H2 in 400C Hysteresis(W/O RTA)=170mV Hysteresis(W/ RTA)=120mV

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs) 圖4-4 鰭寬度 400nm 下 RTA 前後之 ID-VD曲線 0 1 2 3 0.0 5.0x10-6 1.0x10-5 1.5x10-5NCFET HZO N-type W=400nm,L=40nm,H=20nm RTA: After 5min with 95%N2,5%H2 in 400C Hysteresis(W/O RTA)=170mV Hysteresis(W/ RTA)=120mV

G

M(A/V)

Gate Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs) 圖4-5 鰭寬度 400nm 下 RTA 前後之 GM-VG曲線47 0 1 10-12 10-10 10-8 10-6

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C Hysteresis(W/O RTA)=230mV Hysteresis(W/ RTA)=170mV

Drai

n C

urre

nt

(A)

Gate Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs) SS=156 SS=134圖4-6 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 ID-VG曲線

0.0 0.5 1.0 1.5 2.0

0.0 5.0x10-5 1.0x10-4 1.5x10-4

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/RTA(Rvs)48

0 1 2 3

0.0 5.0x10-6 1.0x10-5

1.5x10-5 NCFET HZO N-type

W=400nm,L=40nm, H=20nm

HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C

GM

(A/V)

Gate Voltage (V)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs)圖4-8 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 GM-VG曲線

0 1 2

10-12 10-10 10-8 10-6

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C

Drain

Cu

rr

ent

(A)

Gate Voltage (V)

W/O RTA(fresh) W/O RTA(5000s) W/ RTA(fresh) W/ RTA(5000s) SS=151 SS=156 SS=125 SS=13449 0.0 0.5 1.0 1.5 2.0 0.0 5.0x10-5 1.0x10-4 1.5x10-4

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:VG=VD=2.3V

RTA: After 5min with 95%N2,5%H2 in 400C

Drain

Cu

rr

ent

(A)

Drain Voltage (V)

W/O RTA(fresh) W/O RTA(5000s) W/ RTA(fresh) W/RTA(5000s)圖4-10 鰭寬度 400nm 下 RTA 前後 Fresh 與經過 5000 秒 HCI 之 ID-VD曲線比較圖

0 1 2 3

0.0 5.0x10-6 1.0x10-5

1.5x10-5 NCFET HZO N-type

W=400nm,L=40nm, H=20nm

HCI:VG=VD=2.3V RTA: After 5min with 95%N2,5%H2 in 400C

GM

(A/V)

Gate Voltage (V)

W/O RTA(fresh) W/O RTA(5000s) W/ RTA(fresh) W/ RTA(5000s)50 1 10 100 1000 10000 0 4 8 12 16

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C

SS

(mV

/dec

)

Time (S)

W/O RTA(Fwd) W/O RTA(Rvs) W/ RTA(Fwd) W/ RTA(Rvs)圖4-12 鰭寬度 400nm 下 RTA 前後經過 5000 秒 HCI Stress 之 ΔSS-Time 圖

51 圖4-14 H+離子鍵結被打斷逸散到元件示意圖 1 10 100 1000 10000 -40 0 40 80

NCFET HZO N-type

W=400nm,L=40nm,H=20nm HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C

Hyster

esis

(mV

)

Time (S)

W/O RTA W/ RTA52

120 160 200 240

135 150 165

NCFET HZO N-type W=400nm,L=40nm, H=20nm

HCI:V

G=VD=2.3V

RTA: After 5min with 95%N 2,5%H2 in 400C W/O RTA W/ RTA

SS

(mV

/dec

)

Hysteresis (mV)

53

參考文獻

[1] Cheng-Li Lin, Po-Hsiu Hsiao, Wen-Kuan Yeh, Han-Wen Liu, Syuan-Ren Yang, Yu-Ting Chen, Kun-Ming Chen, Wen-Shiang Liao, “Effects of Fin Width on Device Performance and Reliability of Double-Gate n-Type FinFETs”, IEEE

Transactions on Electron Devices, vol. 60, pp.3639-3644, 2013.

[2] M. O. Thomyson, "Rapid thermal annealing in the microsecond regime," 10th IEEE International Conference of Advanced Thermal Processing of Semiconductors, Vancouver, BC, Canada, 2002, pp. 193-, doi: 10.1109/RTP.2002.1039460.

[3] W. Yeh, W. Zhang, C. Shih and Y. Yang, "Effects of fin width on performance and

reliability for N- and P-type FinFETs," 2016 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, 2016, pp. 361-364, doi: 10.1109/EDSSC.2016.7785283.

[4] P. Sung et al., "Effects of Forming Gas Annealing and Channel Dimensions on the

Electrical Characteristics of FeFETs and CMOS Inverter," in IEEE Journal of the Electron Devices Society, vol. 8, pp. 474-480, 2020, doi: 10.1109/JEDS.2020.2987005.

[5] C. H. Cheng and A. Chin, “Low-voltage steep turn-on p-MOSFET using ferroelectric high-k gate dielectric,” IEEE Electron Device Lett., vol. 35, pp. 274– 276, 2014.

[6] G. C. Tettamanzi, A. Paul, S. Lee, S. R. Mehrotra, N. Collaert, S. Biesemans, G. Klimeck, and S. Rogge, “Interface trap density metrology of state-of-the-art undoped Si n-FinFETs,” IEEE Electron Device Lett., vol. 32, no. 4, Apr. 2011. [7] Z. Krivokapic, U. Rana, R. Galatage, A. Razavieh, A. Aziz, J.Liu, J.Shi, H.J. Kim,

R. Sporer, C. Serrao, A.Busquet, P. Polakowski, J. Müller, W. Kleemeier, A. Jacob, D. Brown, A. Knorr, R. Carter, and S. Banna , “14nm ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications,” in Proc.

IEEE IEDM, 2017.

54

of Ω-gated negative capacitance FinFETs and SRAM,” in Proc. IEEE VLSI-TSA, 2019.

[9] J. S. Lee, Y. K. Choi, D. Ha, "Hydrogen annealing effect on DC and low-frequency noise characteristics in CMOS FinFETs," IEEE Electron Device Lett., vol. 24, no. 3 , Mar. 2003.

[10] M. Hoffmann, B. Max, T. Mittmann, U. Schroeder, S. Slesazeck and T. Mikolajick,

"Demonstration of High-speed Hysteresis-free Negative Capacitance in Ferroelectric Hf0.5Zr0.5O2," 2018 IEEE International Electron Devices Meeting

(IEDM), San Francisco, CA, 2018, pp. 31.6.1-31.6.4, doi:

10.1109/IEDM.2018.8614677.

[11] Z. Yu et al., "Negative capacitance 2D MoS2 transistors with sub-60mV/dec

subthreshold swing over 6 orders, 250 μA/μm current density, and nearly-hysteresis-free," 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 23.6.1-23.6.4, doi: 10.1109/IEDM.2017.8268448.

[12] C. W. Yeung, A. I. Khan, A. Sarker, S. Salahuddin and C. Hu, "Low power negative

capacitance FETs for future quantum-well body technology," 2013 International

Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu,

2013, pp. 1-2, doi: 10.1109/VLSI-TSA.2013.6545648.

[13] H. Lee, K. Tseng and P. Su, "Interface discrete trap induced variability for negative

capacitance FinFETs," 2018 International Symposium on VLSI Technology,

Systems and Application (VLSI-TSA), Hsinchu, 2018, pp. 1-2, doi:

10.1109/VLSI-TSA.2018.8403836. [14] 李愷信、陳旻政、林昌賢、魏耘捷,低於 60 毫伏特次臨界擺幅之負電容效 應鰭式場效電晶體,國家奈米實驗室 [15] 劉傳璽、陳進來,2013,半導體元件物理與製:程理論與實務,台北市: 五南圖書出版股份有限公司 [16] 葉文冠、陳柏穎、翁俊仁,2011,積體電路製程技術與品質管理,台北市: 臺灣東華書局股份有限公司 [17] 林煒得,民 108,功函數對於多鰭數 p-FinFET 之電性分析及熱載子效應可 靠度研究,國立高雄大學電機工程研究所碩士論文

55 [18] 林孟琰,民 108,功函數對於多鰭數 p-FinFET 之電性分析及 NBTI 可靠度 研究,國立高雄大學電機工程研究所碩士論文 [19] 陳詩堯,民 105,不同金屬閘極對多重鰭數 N 型鰭式場效電晶體之可靠度 研究,國立高雄大學電機工程研究所碩士論文 [20] 許值誠,民 107,熱載子效應及定電壓應力對不同主動區面積 Tri-Gate FinFET 元件之可靠度研究,國立高雄大學電機工程研究所碩士論文 [21] 鍾思行,民 96,以快速熱退火加強金屬側向誘發結晶速率之研究,國立交 通大學材料科學與工程研究所碩士論文