國立交通大學

電機與控制工程學系

碩士論文

一種應用於連續近似式類比數位轉換器

之數位校正方法

A Digital Calibration Scheme for the Successive

Approximation Analog-to-Digital Converter

研 究 生:謝宗殷

指導教授:洪浩喬 教授

一種應用於連續近似式類比數位轉換器

之數位校正方法

A Digital Calibration Scheme for the Successive

Approximation Analog-to-Digital Converter

研 究 生:謝宗殷 Student:Tsung-Yin Hsieh 指導教授:洪浩喬 Advisor:Hao-Chiao Hong 國立交通大學 電機學院 電機與控制工程學系 碩士論文 A Thesis

Submitted to Department of Electrical and Control Engineering College of Electrical Engineering

National Chiao-Tung University In Partial Fulfillment of the Requirements

for the Degree of Master

In

Electrical and Control Engineering

March 2009

Hsinchu, Taiwan, R.O.C

一種應用於連續近似式類比數位轉換器

之數位校正方法

研 究 生:謝宗殷 指導教授:洪浩喬 博士 國立交通大學電機與控制工程學系碩士班摘要

傳統 SAR ADC 的解析度主要受限於製程製作出的電容比例是否準確。 本論文提出一種適用於 SAR ADC 的新穎校正方式。對於一個由已知比例關 係之方式所構成的待校電容陣列,我們可以使用此演算法去找出該陣列中各 個電容因製程變異而產生的誤差量,並將之數位化後儲存。然後,在 SAR ADC 進行轉換時計算出每一輸出碼的誤差量再以數位方式修正,如此便可 提升該 SAR ADC 的解析度。 由於此校正法採用全數位方式校正,因此具有低功耗且不容易受製程變 異或其他環境因素影響的優點。此外,所提出的校正演算法,不論各待校電 容的誤差量為正或負,在電路實現上僅需一個單向的類比參考電壓,就可以 找出各電容的數位誤差值。相較於文獻上其他需要兩個對稱參考電壓的校正 方式,成本更低也更具實用性。其所需的額外硬體除少數類比開關與電容 外,皆為數位電路,因此硬體成本很低且非常容易移植到先進製程。 我們使用 TSMC 0.18μm 1P6M CMOS 製程設計並實現一具校正功能的 1-V,12-bit SAR ADC 之晶片,來驗證此校正法是否有效。實際測量顯示,對於同一個晶片,開啟校正功能的 SAR ADC 可以操作在更快的時脈頻率, 並且擁有更寬的有效頻寬;此晶片之 DNL 與 INL 在經過校正後,分別由 -1~+18 個 LSB 與-8~+18 個 LSB,大幅降至-1~+9 個 LSB 與-6~+9 個 LSB; 且在同樣的輸入信號下,開啟校正功能後其 SNDR 最多有 5dB 的改善,換 言之經校正後約可提升 1 個有效位元,且在 1-V 的電源電壓下其耗能僅 20μW。

A Digital Calibration Scheme for the Successive

Approximation Analog-to-Digital Converter

Student:Tsung-Yin Hsieh Advisor:Dr. Hao-Chiao Hong

Institute of Electrical and Control Engineering National Chiao-Tung University

Abstract

It is the mismatched capacitors due to process variation that mainly limit the resolution of conventional SAR ADCs. To address this issue, this thesis proposes a novel calibration scheme for SAR ADCs. The proposed calibration scheme first estimates the ratio errors of the capacitors under calibration in the weighted capacitive array. Then, the errors will be digitized and stored. During the normal conversion of SAR ADCs, the corresponding error code of every ADC’s output will be calculated according to the stored error codes. Finally, the error code will be compensated in digital domain. With the proposed calibration scheme, the resolution of the SAR ADC can be enhanced.

The hardware overhead consists of several capacitors and a few of switches in addition to the digital function blocks. Since the proposed calibration scheme estimates and calibrates the errors digitally, it is very robust, low-power, and can be easily ported to advanced technologies. In practical implementation, only one reference voltage is necessary no matter the capacitor errors are positive or

negative. Comparing with the state-of-the-art calibration schemes which require precisely symmetric dual reference voltages to handle the signed errors, the proposed calibration scheme is more practical and low-cost.

We implemented a 1-V SAR ADC with the proposed calibration scheme in TSMC 0.18μm 1P6M CMOS process. Measurement results show that the SAR ADC can operate faster and has a wider effective resolution bandwidth after calibration. The DNL and INL values are enhanced from -1~+18 LSB and

-8~+18 LSB to -1~+9 LSB and -6~+9 LSB after calibration. With the same input, the SNDR of the ADC can have up to 5dB improvement after calibration. It corresponds to around an additional effective number of bit (ENOB). The ADC consumes less than 20μW at 1-V.

誌謝

本研究能匯集成論文,再由初稿彙整成最終版本,要感謝的對象甚多, 故作誌謝文一篇: 首謝吾師浩喬,春風化雨,惠我良多。由基礎之研究精神,至求學態度, 實驗方法、報告寫作與投影片製作等技巧,不一而足。此乃其他實驗室所不 能及之處,兩年半載,甚是充實。 亦要感謝鄭教授、黃教授、張教授,百忙之中抽身來擔任學生之口試委 員,給予學生之論文許多寶貴的意見與指導,十分受用。 再謝吾之嚴父慈母,使吾之求學過程中,衣食飽暖,不虞匱乏。每當汝 問曰:「此不肖子何時能畢業?」吾苦笑,答曰:「近期、再近期、亦或再近 期矣。」實此乃緩兵之計也,而汝總能包容且諒解之,感謝之心,難以言表。 三謝實驗室之各位學長,聖泉與家昕學長,指導學弟佈局與除錯等,獲 益良多。孟軒小學長雖時常唆使學弟與盜版為伍,並且出言「關照」學弟, 實則孟軒小學長之一種關心之表現也。國銘學長則帶領學弟一路前進,並與 學弟分享奇某公司之內幕,甚是熱心。皇承學長終日鎮守實驗室,維護實驗 室之和平,不甚感謝。而時常與宏慶、芳毅學長,進行拳皇或投壺之勝負, 學弟自終未從學長手中獲得一勝,學長技術了得,學弟甘拜下風。 振綱學長總是關心學弟身體健康,多向學弟推銷營養補充品等,好意心 領,而荷包不能容許。榮洲學長,陪伴學弟一年多,耳提面命,提攜上進, 或當電路焊將、或在電資露營過夜等,實則難忘。 後謝同窗永順,永順乃笑傲江湖之歌王也!同窗勇成,勇成乃潘安再世 也!與吾人度過二載寒暑,同窗之情,永不忘懷。學弟明達,又一鎮守實驗室,維護和平之義士也。學弟紹峰、韋傑,時常與吾人運籌帷幄中,討論掌 中之小宇宙,了解宇宙之奧秘,乃研究之外另一樂趣也。 末謝學弟志健,伴吾於電資大樓組隊測量,或協助吾人文章除錯,甚是 辛苦。學弟崐池、逸瑋、毓賢,雖相處之日不長,實乃後起之秀,頗有長江 後浪推前浪之勢。實驗室人才濟濟,吾人可安心登入國軍ㄤ賴矣。 特謝舊識兼好友冠廷,憶當時你我於長庚圖書館寒窗苦讀,或在據德樓 住宿時以外掛組隊交心四載寒暑。及在風城時,初來乍到,人生地不熟,互 相照應、互吐苦水等,實為求學生涯難忘之回憶,彌足珍貴。 欲感謝之人、事、物,不勝枚舉,謝天、足矣! 己丑年 孟春 吉日 良時 謝宗殷 謹識 於風城

目錄

摘要...I Abstract ...III 誌謝... V 目錄... VII 圖目錄...IX 表目錄... XIII 第一章 緒論...1 1.1. 研究背景...1 1.2. SA ADC 介紹 ... 2 1.3. 傳統單端輸入之 SA ADC ...4 1.4. 改良型單端輸入之 SA ADC ...5 1.5. 採用非二進位加權式電容陣列之單端 SA ADC ...6 1.6. 傳統雙端輸入之 SA ADC ...8 1.7. 改良型虛擬雙端輸入之 SA ADC ...10 1.8. 特殊型式之雙端輸入 SA ADC ...13 1.9. 研究動機與目的...14 1.10. 論文章節組織及研究方法...16 第二章 具有自我校正功能之 SA ADC 介紹...18 2.1. 可變解析度的 SA ADC ...18 2.2. 應用於 SA ADC 之由高至低式校正演算法 ...20 2.3. 應用於 SA ADC 之由低至高式校正演算法 ...29 2.4. 具有自我校正功能的 SA ADC 之一[21]...34 2.5. 具有自我校正功能的 SA ADC 之二[22]...35 2.6. 結論:關於前人提出之校正法的缺失...37 第三章 提出之應用於電容陣列的校正演算法...39 3.1. 提出之演算法架構選擇...39 3.2. 提出之演算法簡介...42 3.3. 使用單一參考電壓完成誤差計算的方法...46 3.4. 誤差計算模式時的改良...51 3.4.1. 以參考電壓當預先充電與逼近基準...52 3.4.2. 全電容式的數位類比轉換器與新開關切換方式...56 3.5. 使用單一參考電壓完成誤差補償的方法...58 3.6. 所提出之新穎的誤差計算模式...603.6.1. 計算待校電容陣列中 MSB 電容負向誤差之方法... 61 3.6.2. 計算待校電容陣列中 MSB-1電容負向誤差之方法 ... 65 3.6.3. 計算待校電容陣列中 MSB 電容正向誤差之方法... 69 3.7. 加入校正演算法之電路動作流程... 73 3.8. 以電路之行為模型驗證所提出之演算法... 75 3.8.1. 範例一:最大可校正於 MSB 電容之誤差... 77 3.8.2. 範例二:最大可校正的亂數誤差... 80 3.8.3. 範例三:由先前下線經驗所得到之誤差... 83 3.9. 與先前所提出之校正方法比較... 87 第四章 具校正功能之 12 位元 SA ADC 設計 ... 90 4.1. 提出之 SA ADC 架構 ... 90 4.2. 提出之 SA ADC 類比電路設計 ... 91

4.2.1. 取樣保持電路(Sample and Hold, S/H)... 96

4.2.2. 具偏移量補償功能的比較器級... 101

4.2.3. 數位類比轉換器(Digital to Analog Converter) ... 111

4.3. 提出之 SA ADC 數位電路設計 ... 124 4.3.1. 控制區塊(Controller block) ... 125 4.3.2. 暫存器與 ALU 區塊 ... 132 4.4. ADC 佈局圖 ... 135 4.5. 電路模擬與驗證... 136 4.6. Hardware Overhead ... 141 第五章 量測結果與性能分析... 144 5.1. 量測環境設定與晶片照... 144 5.2. 測量用 PCB 板與 PCB 板設定... 145 5.2.1. 具有誤差校正功能的測量模式設定... 147 5.2.2. 不具誤差校正功能的測量模式設定... 148 5.2.3. 誤差量數位碼觀測模式設定... 149 5.3. 在供應電壓 1 伏特下的測量結果... 151 5.3.1. 時脈頻率 560k Hz 之測量結果 ... 153 5.4. ADC 之測量結果分析 ... 163 第六章 結論與未來發展... 171 6.1. 結論... 171 6.2. 未來發展與待改進之處... 172 6.2.1. SA ADC 編碼輸出方式的改進 ... 172 6.2.2. 具有偏移量補償功能之比較器級的改進... 174 6.2.3. 晶片實做方面之改進... 176 6.2.4. 電路模擬時間過長之改進... 178 參考文獻... 180

圖目錄

圖 1- 1 基本的連續近似式類比數位轉換器架構...2 圖 1- 2 以具體化的天平秤重概念描述 SA ADC...3 圖 1- 3 以逼近的方式完成天平秤重...3 圖 1- 4 傳統的單端輸入連續近似式類比數位轉換器架構[2] ...4 圖 1- 5 改良型的單端輸入連續近似式類比數位轉換器架構[5] ...5 圖 1- 6 二進位加權式的十二位元電容陣列...6 圖 1- 7 使用非二進位加權式電容陣列的單端 SA ADC...7 圖 1- 8 傳統的雙端輸入差動式 SA ADC...8 圖 1- 9 改良型傳統雙端輸入差動式 SA ADC...9 圖 1- 10 虛擬雙端輸入之 SA ADC 架構圖...10 圖 1- 11 新穎的虛擬雙端追蹤保持電路... 11 圖 1- 12 提出之虛擬雙端輸入 SA ADC 與前端電路整合晶片圖...12 圖 1- 13 具有自我時序控制比較器的雙端輸入之 SA ADC...13 圖 1- 14 對稱中心式的電容佈局...15 圖 2- 1 可變解析度的 SA ADC 方塊圖...18 圖 2- 2 新式二分搜尋架構圖...19 圖 2- 3 應用由高至低式校正演算法之 SA ADC 架構圖...21 圖 2- 4 以由高至低演算法找出電容 CN之誤差量的方法 ...22 圖 2- 5 以由高至低演算法找出電容 CN-1之誤差量的方法 ...25 圖 2- 6 應用由低至高演算法之 SA ADC 架構圖...30 圖 2- 7 文獻[19]所提出之 SA ADC 類比部分架構 ...31 圖 2- 8 具有自我校正功能的 SA ADC【1】類比部分之架構...34 圖 2- 9 具有自我校正功能的 SA ADC【2】架構方塊圖...36 圖 3- 1 抽象化的描述 SA ADC 之動作方式...42 圖 3- 2 以天平自身的秤重功能找出 16 克法碼的誤差量...44 圖 3- 3 若 16 克之法碼誤差量為-Δ克時之情形 ...45 圖 3- 4 將天平兩端互換後,於右側加入測重法碼使天平重歸平衡...46 圖 3- 5 交換 DAC 電容充放電之方式 ...47 圖 3- 6 以改良的由高至低演算法找出「負向誤差」的方式...48 圖 3- 7 以改良的由高至低演算法找出「正向誤差」的方式...50 圖 3- 8 傳統的由高至低校正法架構[15,16,17] ...52 圖 3- 9 改良後的誤差計算模式電路...54 圖 3- 10 改良前的比較器負端電壓示意圖...55圖 3- 11 改良後的比較器負端電壓示意圖... 55

圖 3- 12 再次改良後的誤差計算模式電路其類比電路之部分... 56

圖 3- 13 將 Sub DAC 與 Calibration DAC 切換至「1」... 57

圖 3- 14 將 Sub DAC 與 Calibration DAC 切換至「0」... 57

圖 3- 15 以提出之誤差計算演算法計算 C7之負向誤差的方式 ... 63 圖 3- 16 以提出之誤差計算演算法計算 C6之負向誤差的方式 ... 66 圖 3- 17 以提出之誤差計算演算法計算 C7之正向誤差的方式 ... 70 圖 3- 18 加入新穎的誤差計算演算法之電路動作流程圖... 73 圖 3- 19 誤差計算模式時之動作流程圖... 74 圖 3- 20 具有校正功能的正常轉換模式之動作流程圖... 74 圖 3- 21 範例一模擬時由提出之校正演算法求出之誤差量... 77 圖 3- 22 範例一校正前的頻譜分析圖... 78 圖 3- 23 範例一校正後的頻譜分析圖... 78 圖 3- 24 範例一校正前的 INL 圖 ... 79 圖 3- 25 範例一校正後的 INL 圖 ... 79 圖 3- 26 範例二模擬時由提出之校正演算法求出之誤差量... 81 圖 3- 27 範例二校正前的頻譜分析圖... 81 圖 3- 28 範例二校正後的頻譜分析圖... 82 圖 3- 29 範例二校正前的 INL 圖 ... 82 圖 3- 30 範例二校正後的 INL 圖 ... 83 圖 3- 31 範例三模擬時由提出之校正演算法求出之誤差量... 84 圖 3- 32 範例三校正前的頻譜分析圖... 85 圖 3- 33 範例三校正後的頻譜分析圖... 85 圖 3- 34 範例三校正前的 INL 圖 ... 86 圖 3- 35 範例三校正後的 INL 圖 ... 86 圖 4- 1 提出之具校正功能的 SA ADC 架構圖 ... 90 圖 4- 2 提出之 SA ADC 的類比電路方塊圖 ... 92 圖 4- 3 類比部分之動作時序圖... 93 圖 4- 4 在具校正功能的正常轉換模式下類比電路之動作... 95 圖 4- 5 在誤差計算模式下類比電路之動作... 96 圖 4- 6 常見的 Bootstrapped 開關架構[3]... 97 圖 4- 7 各種不同架構的開關之導通電阻比較... 98 圖 4- 8 所使用的取樣保持電路[10] ... 99 圖 4- 9 取樣保持電路當輸入信號為 1k Hz 時之頻譜分析圖 ... 100 圖 4- 10 取樣保持電路當輸入信號為 25k Hz 時之頻譜分析圖 ... 101 圖 4- 11 具有偏移量補償功能的比較器級... 102 圖 4- 12 提出之操作於低電壓下的軌對軌前置放大器設計... 109 圖 4- 13 供應電壓 1 伏特時 PA1 之頻率響應... 109

圖 4- 14 供應電壓 1 伏特時 PA2 系列之頻率響應 ... 110

圖 4- 15 軌對軌之低耗能比較器... 111

圖 4- 16 一般的二進位加權電容式 DAC ... 112

圖 4- 17 將 DAC 陣列分成 Sub DAC 與 Main DAC 之架構... 114

圖 4- 18 提出之數位類比轉換器架構... 117 圖 4- 19 加上寄生電容後的數位類比轉換器... 118 圖 4- 20 三組 DAC 之佈局 ...123 圖 4- 21 提出之數位部分方塊圖...124 圖 4- 22 提出之控制區塊架構圖...125 圖 4- 23 提出之控制器 A 之架構...127 圖 4- 24 控制器 A 之時序圖...129 圖 4- 25 提出之暫存器與 ALU 區塊架構圖 ...133 圖 4- 26 ADC 佈局圖 ... 135 圖 4- 27 不啟動誤差校正功能時的輸出頻譜...137 圖 4- 28 啟動誤差校正功能後的輸出頻譜...138 圖 4- 29 不同輸入信號頻率對 SNDR 之模擬結果分析圖 ...140 圖 4- 30 誤差觀測模式之誤差量數位碼製圖...140 圖 5- 1 透過 Wire bounding 於 PCB 板上後之晶片圖 ...144 圖 5- 2 量測儀器與環境設定...145 圖 5- 3 測試用 PCB 板 ...146 圖 5- 4 測量模式一時,控制面板之設定...147 圖 5- 5 測量模式一時,輸出面板之連接...147 圖 5- 6 測量模式二時,控制面板之設定...148 圖 5- 7 測量模式二時,輸出面板之連接...149 圖 5- 8 觀測模式時,控制面板之設定...150 圖 5- 9 觀測模式時,輸出面板之連接...150 圖 5- 10 不同的時脈頻率對 SFDR 之測量結果...152 圖 5- 11 不同的時脈頻率對 SNDR 之測量結果 ...152 圖 5- 12 不同的時脈頻率對消耗功率之測量結果...153 圖 5- 13 校正前之 DNL 圖形 ...154 圖 5- 14 校正後之 DNL 圖形 ...154 圖 5- 15 校正前之 INL 圖形 ...155 圖 5- 16 校正後之 INL 圖形 ...155 圖 5- 17 校正前之輸出頻譜圖...156 圖 5- 18 校正後之輸出頻譜圖...157 圖 5- 19 輸入信號振幅為-0.3 dBFS 時之 ERBW 測量結果...157 圖 5- 20 輸入信號振幅為-10 與-20 dBFS 時之 ERBW 測量結果 ...158 圖 5- 21 輸入信號振幅為-30 與-40 dBFS 時之 ERBW 測量結果 ...158

圖 5- 22 不同的輸入信號振幅對 SFDR 之測量結果... 159 圖 5- 23 不同的輸入信號振幅對 SNDR 之測量結果 ... 160 圖 5- 24 誤差觀測模式所測量之電容相對誤差量分佈... 161 圖 5- 25 經過分析後的測量所得之未校正的 INL 圖形 ... 161 圖 5- 26 誤差觀測模式所測量之電容相對誤差量分佈... 164 圖 5- 27 根據誤差觀測模式之測量結果所估計的電容相對誤差量分佈... 164 圖 5- 28 測量得到的未校正之 DNL 圖形 ... 165 圖 5- 29 測量得到的校正後之 DNL 圖形 ... 165 圖 5- 30 根據測量結果調整電容誤差量且重新校正後的 DNL 圖形 ... 165 圖 5- 31 測量得到的未校正之 INL 圖形 ... 167 圖 5- 32 測量得到的校正後之 INL 圖形 ... 167 圖 5- 33 根據測量結果調整電容誤差量且重新校正後的 INL 圖形 ... 167 圖 6- 1 提出之 SA ADC 在具有校正功能之正常轉換模式下的動作流程圖 .. 173 圖 6- 2 改進之 SA ADC 在具有校正功能之正常轉換模式下的動作流程圖 .. 173 圖 6- 3 提升比較器精準度之校正法[33] ... 175 圖 6- 4 改進後的 SA ADC 晶片連接方式 ... 177

表目錄

表 1- 1 類比數位轉換器種類[1] ...1 表 3- 1 範例一之電容值設定...77 表 3- 2 範例二之電容值設定...80 表 3- 3 範例三之電容值設定...84 表 3- 4 與前三篇校正經典作比較...87 表 4- 1 分析位元數之結果比較... 115 表 4- 2 控制器 B 之連續近似暫存器動作 ...126 表 4- 3 控制器 A 計算電容 C7的負向誤差時所需之信號 ...130 表 4- 4 控制器 A 計算電容 C6的負向誤差時所需之信號 ...131 表 4- 5 控制器 A 計算電容 C7的正向誤差時所需之信號 ...132表 4- 6 佈局後之 ADC 各 Active area 所佔面積 ...136

表 4- 7 進行 ADC 模擬時的基本設定 ...136 表 4- 8 模擬時的電容誤差量設定...137 表 4- 9 各個 Corner 下啟動誤差校正功能之模擬結果...138 表 4- 10 各個 Corner 下不啟動誤差校正功能之模擬結果...139 表 4- 11 不同輸入信號頻率對 SNDR 之模擬結果 ...139 表 4- 12 ADC 各電源所消耗之功率 ... 141 表 4- 13 ADC 模擬時所達到的預計規格列表 ... 141 表 4- 14 各種條件下的 ADC 消耗面積及其實作所需之成本 ...142 表 5- 1 各種條件下的 DNL 與 INL 值比較...168 表 5- 2 測量所得之誤差量與估計所得之誤差量的差異...169

第一章

緒論

1.1. 研究背景

心電圖為人體最重要的信號之一,我們可以藉由觀測心電圖之波形,來 得知個人的身體健康狀態,能有效發現各種和心臟有關的疾病,達到及早預 防、勝於治療的功效。 然而,心電圖是一個類比訊號,為了要使之能與各類醫療儀器溝通,所 以我們需要一個類比數位轉換器(Analog-to-Digital Converter, ADC),負起 將類比信號轉換成數位信號的重要角色。此類比數位轉換器之解析度會直接 影響了診斷的準確性,而為了能更加仔細觀測,提早發現不正常的心電圖波 形,我們通常需要一個十位元以上的類比數位轉換器。 考量到功率消耗以及解析度等因素,加上心電圖之頻段考量,我們需要 的類比數位轉換器規格為:超低耗能、中等轉換速度、與中等解析度。綜合 以上規格,經由表 1-1 之類比數位轉換器規格表所示,發現連續近似式類比 數位轉換器(Successive Approximation Analog-to-Digital Converter, SA ADC) 是比較符合所需的。 表 1- 1 類比數位轉換器種類[1] Low-to-Medium Speed, High Accuracy Medium Speed, Medium Accuracy High Speed, Low-to-Medium Accuracy Oversampling Integrating Successive-approximation Algorithmic Cyclic Flash Two-step Interpolating Folding Pipelined Time-interleaved1.2. SA ADC 介紹

連續近似式類比數位轉換器(Successive Approximation Analog-to-Digital Converter, SA ADC)之基本架構如圖 1-1 所示,其主要的構成元件為一個比 較器、一個 N-bit 的數位類比轉換器(Digital-to-Analog Converter, DAC)及 一個連續近似式暫存器(Successive approximation register, SAR)。

圖 1- 1 基本的連續近似式類比數位轉換器架構

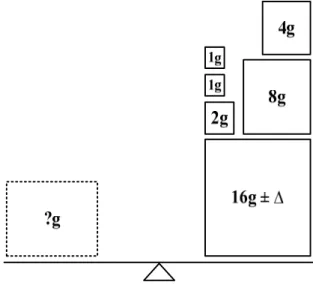

SA ADC 主要精神是二分搜尋(Binary search algorithm)演算法,二分 搜尋法被廣泛應用於各種搜尋動作中。利用被搜尋的數列已經有排序之特 性,減少搜尋比對的次數。 在二分搜尋法中,從數列的中間開始搜尋,如果這個數小於我們所搜尋 的數,由於數列已排序,則該數左邊的數必定都小於要搜尋的對象,所以無 需浪費時間在搜尋左邊的數;如果搜尋的數大於所搜尋的對象,則右邊的數 無需再搜尋,直接搜尋左邊的數。 我們將此抽象的演算法描述具體化,可用天平秤重作比喻,如圖 1-2 所 示。此天平秤重範圍為 0 克到 7 克,它有三個分別為 4 克、2 克、和 1 克的 法碼。

圖 1- 2 以具體化的天平秤重概念描述 SA ADC 第一步我們先以 4 克法碼嘗試比較,發現比待測物還輕,故在下一步驟 中保留 4 克法碼,並且放上 2 克法碼。此時發現比待測物還重,因此移除 2 克法碼。第三步則放上 1 克法碼,於是天平趨近於平衡,法碼總數為 5 克, 則完成此次物體的測重;其動作步驟如圖 1-3 所示。 圖 1- 3 以逼近的方式完成天平秤重 將上述測物重之動作原理延伸至 SA ADC:透過比較器比較兩輸入端電 壓之大小,輸出一個為 0 或 1 的編碼給 SAR,SAR 便會經由一些控制線去 控制 DAC 陣列中各元件是接到 0(接地)或 1(接 VREF),如此便可改變下 次 DAC 之輸出。如此反覆動作 N 次後,便可逐次逼近至一筆長度為 N 位元

的數位編碼,此數位編碼即為最後將類比輸入數位化後的結果。

1.3. 傳統單端輸入之 SA ADC

傳統的連續近似式類比數位轉換器主要的構成元件為一個比較器、一個 N-bit 的數位類比轉換器(Digital-to-Analog Converter, DAC)及一個連續漸 近暫存器(Successive approximation register, SAR)。其架構如圖 1-4 所示。

此架構的轉換原理主要是使用上述二分搜尋法的觀念,其操作方式分成 三個步驟,分別是取樣模式、保持模式及電荷重新分佈模式。 取樣模式是將 Sb切到 Vin且 Sa將 Vdac端接至地端;接著進入保持模式, 此時 Vdac端電壓為-Vin,下一步則進入轉換模式,也就是電荷重新分佈模式。 這個模式需要 N 次的轉換,N 取決於類比數位轉換器的解析度,除了最後一 次的轉換,其餘的轉換後都會在 Vdac端加或減 VREF/2C,其中 C 為第幾次的 轉換,而藉由加或減來得到最後相對的數位輸出。 此種架構具有低耗能的優點,因為其主動元件僅有一個比較器。但是在 今日以 CMOS 重新設計時則會碰上若干問題,因此有了改良型態的出現。 圖 1- 4 傳統的單端輸入連續近似式類比數位轉換器架構[2]

1.4. 改良型單端輸入之 SA ADC

傳統的 SA ADC 會面臨的問題之一,當 Vin愈大時,其 Vdac端則會得到 愈大的負值,而若使用一般之傳輸閘(Transmission gate, TG)來完成開關 Sa的話,將會造成開關 Sa會出現漏電流情形。為了避免開關 Sa漏電流的情 況,於是使用[3]之架構,將一端接輸入訊號,並且另一端接 DAC 的方式, 且在 DAC 的部份採用了[4]中的 grounded-switches 的技巧,即是接 VDD或 GND 兩個電位的技巧,圖 1-5 為改良型之 SA ADC 架構。 圖 1- 5 改良型的單端輸入連續近似式類比數位轉換器架構[5] 如今比較器的兩輸入端從 DAC 之輸出與地端,變為 DAC 之輸出與經 過取樣與保持的輸入信號端。因為經過取樣與保持的輸入信號並不會出現負 值,所以在逼近過程中 Vdac端也不會有負電壓出現,如此便可避免開關 Sa 漏電流的情形。 此架構被普遍的應用在今日流行的單端 SA ADC 之上,各種新穎的單端 SA ADC 幾乎都由此種架構改良而來,至此對於 SA ADC 的研究開始蔚為一 股風氣。然而,單端輸入的 SA ADC 本身存在著極限。因為儀器上的限制,輸入 信號或多或少都會帶點雜訊(Noise)存在,當電壓越來越低,而解析度越 來越高的時候,輸入信號本身的雜訊就會影響了單端輸入 SA ADC 的解析 度,因此常見的單端 SA ADC 其解析度大多為 8 到 12 位元。 若要突破這個極限,一般是將輸入方式改成雙端差動輸入,這是比較常 見的解決方案,所以通常 12 位元以上的 SA ADC 我們會以雙端差動輸入的 方式來完成。

1.5. 採用非二進位加權式電容陣列之單端 SA ADC

一個 N-bit 的數位類比轉換器(Digital-to-Analog Converter, DAC)是連 續近似式類比數位轉換器的必須元件之一。然而完成它的方法有許多種,包 含 R-2R 類型、電阻串(Resistor string)分壓類型、R-C 混合類型等等。其 中最普遍被使用的則是二進位加權式(Binary weighted)的電容陣列,如圖 1-6 所示。 圖 1- 6 二進位加權式的十二位元電容陣列 傳統的由二進位加權式電容陣列構成之數位類比轉換器如上圖所示,以 十二位元為例,則電容數量有 13 個。除了 C0和 C1之外,C1到 C12之間互相 保持一定的關係,如圖 1-6 所示,「二進位加權式」也是因此比例關係而得

名。使用此種架構的消耗功率會遠低於電阻串架構,故二進位加權式的電容 陣列被廣泛的應用在今日的數位類比轉換器元件中。 另外有一種不使用二進位加權式電容陣列去完成數位類比轉換器之架 構被提出[6],其電容陣列中的各個電容間也維持著一個固定的比例關係,和 以往不同的是,傳統的二進位加權式電容陣列,其各電容間比例常數為 2; 而此架構使用非 2 例如 1.8 當作各電容間的比例常數。 因為各電容之間的比例常數不為 2,因此可以有效節省晶片中被大電容 所佔掉的面積;由於電容值的減小,同時也節省了數位類比轉換器的消耗功 率,特別是當位元數提高時效果更加顯著。但是我們必須加入一些數位解碼 電路去將它的數位編碼正規化(Normalized),故此種架構的 SA ADC 其數 位電路將會非常複雜,其架構如圖 1-7 所示。 圖 1- 7 使用非二進位加權式電容陣列的單端 SA ADC 由圖 1-7 我們可以發現,此種架構的 SA ADC 雖然節省了晶片中被電容 佔去的面積,節省了大電容切換所消耗的功率,但是卻會被過度複雜的數位

解碼電路佔去更大的面積,消耗更多的功率。因此,此架構之創新度雖然高, 但是在實作上可能不合乎經濟效益。

1.6. 傳統雙端輸入之 SA ADC

為了讓類比電路更能夠抵抗因輸入信號帶來的雜訊(Noise),我們通常 會以雙端輸入的方式去完成類比電路的輸入端,通常稱此種技術為差動輸入 (Differential input)。此技術被廣泛的應用在類比電路之中,如常見的差動 輸入式放大器、比較器級。 傳統的雙端輸入差動式 SA ADC 如圖 1-8 所示[7, 8],其接收兩個差動輸 入的類比信號,將此類比信號轉換成數位輸出。 圖 1- 8 傳統的雙端輸入差動式 SA ADC 此種傳統雙端輸入差動式之 SA ADC 架構有兩個主要之缺點,第一為使 用了一個緩衝器(Buffer)去提供共模電壓 VCM,所以主動元件除了比較器之外又多了一個 Buffer,因此會消耗額外的功耗。其次為此種架構之晶片面 積幾乎取決於位元數 N,N 越大,數位類比轉換器中的電容越多;由於兩輸 入端都各採用了一個由電容陣列構成之數位類比轉換器,所以電容面積為單 端輸入之 SA ADC 的兩倍。 於是 K.C. Smith 提出第二種雙端輸入之差動式 SA ADC [2],其架構如 圖 1-9 所示。將 Buffer 由電路中移除,主動元件僅有一個比較器,消耗功率 會比未改良前的來得小。但是其晶片面積被數位類比轉換器之電容陣列佔掉 大半的弊病仍未改善。 而當我們在低電壓下設計雙端輸入差動式 SA ADC 時會碰到另一個問 題。數位類比轉換器電容陣列中,電容下板極之開關,若由普通的傳輸閘 (TG)去完成,由於操作在低電壓下,在輸入信號接近 2 1 VDD時,構成 TG 的 PMOS 和 NMOS 都會無法完全導通,因此這些開關會有導通性不良的問 題。 VREFN C8 C7 C6 C5 C4 C3 C2 C1 C0 SAR 10 8 VinN VREFP C8 C7 C6 C5 C4 C3 C2 C1 C0 VinP 10 D1~D8 Srstp Srstn S0p S0n S1p S1n S2p S2n S3p S4p S5p S6p S7p S8p S3n S4n S5n S6n S7n S8n 圖 1- 9 改良型傳統雙端輸入差動式 SA ADC 解決開關在低電壓設計下導通性不良的處理方法有二:使用低臨界電壓

製程去完成電路(Low VT)[11] ,或靴帶式倍壓開關技術(Bootstrapped switch)[9, 10]之技巧。 由成本的觀點來看,使用靴帶式倍壓開關技術是比較可行的。但是在兩 個輸入端之數位類比轉換器電容陣列中,各個電容下板極都要使用倍壓式開 關,消耗的功率實在驚人。所以此種電路在低電壓的設計下,還有許多改良 的空間。

1.7. 改良型虛擬雙端輸入之 SA ADC

為了克服在低電壓下設計傳統雙端輸入之 SA ADC 會碰到的問題,我們 於[12]提出一種虛擬雙端輸入之 SA ADC,如圖 1-10 所示。 圖 1- 10 虛擬雙端輸入之 SA ADC 架構圖比較器的正端是一個虛擬雙端差動式的追蹤保持電路(Track & Hold), 使用此種新穎的追蹤保持電路,使電路可以接受雙端差動輸入信號,而僅需

要一個數位類比轉換器電容陣列即可完成,大幅減少了晶片中被數位類比轉 換器中的電容所佔掉的面積。 比較器負端是一個由二進位加權式電容陣列所構成的數位類比轉換 器,由於我們將輸入信號移到比較器正端,所以在這裡可以對所有開關使用 Grounded-switches 之技巧。換言之這些開關即使在低電壓操作下也不會有導 通性不良的問題,大幅減少了 Bootstrapped switches 所需要的的數目。 我們將圖 1-10 中的追蹤保持電路放大來看,如圖 1-11 所示,僅由兩個 靴帶式倍壓器與三個 Bootstrapped switches 構成,大幅降低了 Bootstrapped switches 所需的數量。此電路可以接受一個雙端輸入的類比信號,而其電路 動作可以分成追蹤模式與保持模式。

圖 1- 11 新穎的虛擬雙端追蹤保持電路

電路在追蹤模式時,開關 Sp和 Sn導通,Scm關閉,將壓降 2Vp.p儲存在

路進入保持模式時,開關 Sp和 Sn關閉,Scm導通,由於取樣電容 CS兩板壓 降必須保持一定,所以電壓 VSH 會是(VCOM+2Vp.p)之值。接著 SA ADC 進入轉換模式,負端會對作電壓 VSH 逼近,而最終得到一個表示電壓 VSH 之值的數位編碼。 此種虛擬雙端輸入的好處為節省了晶片中被數位類比轉換器中的電容 陣列所佔去的面積,同時在低電壓設計下,我們僅需要三個 Bootstrapped switches 就可完成,大幅減少了 Bootstrapped switches 所需要的數量。然而 此種架構的消除輸入信號雜訊的功能卻比不上真正的雙端差動輸入架構,若 想做到更高的解析度,還是必須使用真正的雙端差動輸入架構。

此電路整合於由一感測器與一前端放大器組成之整合型電路晶片內,使 用 0.18μm 製程,透過 CIC 下線完成且驗證 Function work,其晶片照如圖 1-12 所示。

1.8. 特殊型式之雙端輸入 SA ADC

Gilbert Promitzer 於[13]提出另一種具有一個有自我時序控制的比較器 (Self-timed comparator)的雙端輸入 SA ADC,如圖 1-13 所示。傳統的比較 器通常只有兩個時序,即比較時序與重置時序,各佔 Duty cycle 的 50%。而 這種具有自我時序控制的比較器則能根據輸入信號之大小,改變比較時序與 重置時序在一個時脈時間(Clock time)內所佔的長短。 圖 1- 13 具有自我時序控制比較器的雙端輸入之 SA ADC 當比較器之兩輸入信號相差很大時,比較器能在瞬間完成這次的比較, 經由 LATCH 信號回傳比較完成信號後,剩下的時間則可以挪給下個比較時 序使用。通常緊接在後的比較時序內,比較器之兩輸入信號差異會變小,此 時比較器會需要更多的時間去完成這次的比較,由於之前的時序有剩下時間 可以利用,所以藉由加長這次比較的時間,讓比較器可以精確的完成這次的 比較動作。 此種電路架構利用比較器之自我時序控制技術,讓比較器在兩輸入信號 相差較大時使用較短的時間完成比較;反之當兩輸入信號相差很小時,就加

長這次比較所花的時間。這種做法可以讓比較器減少亞穩態(Meta-stable) 的出現,讓比較的結果更加精確。

1.9. 研究動機與目的

以上簡介了幾種 SA ADC 的架構,我們可以發現,不論各種各類的 SA ADC 架構,其基本元件都如圖 1-1 所示,包含一個比較器以比較兩端信號大 小、一組連續近似暫存器用以儲存比較值和時序控制、以及一組數位類比轉 換器。 其中數位類比轉換器架構中,又以二進位加權式電容陣列最廣泛被使 用。因為其本身各元件就已經具備比例常數為 2 的條件,恰巧和二進位碼權 重相同,所以不需要外加一組解碼器電路去將輸出碼編成標準二進位編碼。 加上以電容陣列構成,本身耗能較電阻串型式構成來得低,所以幾乎各 SA ADC 內都存在著一組由二進位加權式的電容陣列所構成的數位類比轉換器 架構。 然而這會面臨一個問題,由於製程是非理想的,晶片出廠後最終所得到 的電容或是電阻值,往往會和實際值有所出入。這個結果將導致各電容或電 阻值在出廠後產生漂移,使其值與模擬時不同。 也就是本來預期數位類比轉換器中,各電容值為一個公比為 2 的等比級 數,如今會因為製程因素改變其比例關係,使其各元件間權重不為 2,如此 將導致最後輸出的二進位數位編碼和理想值有所出入。這個現象在 ADC 位 元數上升,電容數目變多、電容值變大時會更加明顯,因而限制 SA ADC 的 解析度與線性度。 由以上我們可以得知,若要提升 SA ADC 的解析度,其關鍵元件為二進位加權電容式的數位類比轉換器,改善電容陣列中各電容間的匹配度,將是 提升 SA ADC 解析度的首要問題。 增加電容匹配度的方法有很多種,在電路設計時,一種常見的方式是將 電容陣列中的各個電容切割成許多小單位電容,再將這些單位電容以對稱中 心佈局(Common centroid)的方式佈局而成,如圖 1-14 所示。如此這些單 位電容將在 X 軸和 Y 軸上均勻的分佈,期望可以將因製程漂移造成的變異 量降到最小。 圖 1- 14 對稱中心式的電容佈局 接著我們可以利用晶圓廠所提供的 RC 萃取檔案(RCX command file) 去估計各個電容之間,因佈局走線造成的寄生電容值,若我們可以估計這些 寄生電容,則我們也可以預先將此寄生電容值調整成 2 的冪次。如此再使用 電路模擬軟體如 Hspice 進行後模擬(Post layout simulation),則可以將電容 的匹配度問題降到最小。

然而這必須建立在 RC 萃取檔案(RCX command file)是準確且可靠的 條件下,我們所估算的電容值才有意義。一旦 RC 萃取檔案有誤差發生,則

整體電路的效能仍將會和預期有所偏差。 另一種解決方法是在晶片出廠後,根據測量靜態參數的結果分析,我們 可以知道究竟是數位類比轉換器中,那個電容出現了問題。接著我們可以使 用雷射校正(Laser trimming)的方式,將此電容值作修正。 但是使用雷射校正成本昂貴,且需要大量的晶片測量出統計數據,才可 以確定是那個電容需要被修正,浪費大量的人力、時間、測試成本。加上雷 射校正機台本身價值不菲,這種方式並不適合用在大量生產的產品中。 本論文提出一種適用於連續近似式類比數位電路的校正演算法,此校正 演算法能讓電路自動找出數位類比轉換器,電容陣列中各電容間的比例誤 差,然後在轉換過程中進行自我校正(Self-calibration)。如此不需完全仰賴 RC 萃取檔案的精準度,也不需要昂貴的雷射校正儀器,是真正符合實際效 益且可量產的方法。

1.10.論文章節組織及研究方法

本論文共分為六章,第一章除簡介各種 SA ADC 外,並闡述本論文研究 背景、動機、目的以及研究方法;第二章介紹且分析各種目前已發表過的應 用於 SA ADC 之自我校正方法;第三章提出我們的校正方法,並且使用電路 之行為模型(Behavior model)做驗證;第四章為電路設計及其於 Hspice 軟 體的模擬及驗證;第五章為晶片量測結果與性能分析;第六章為結論及未來 展望。本論文所設計的類比數位轉換器是利用 0.18μm CMOS 1P6M 製程來完 成晶片的實現。希望能在加入校正演算法到 SA ADC 的同時,也能兼顧低功 率的需求。

為提出一種新穎的校正演算法,首先要分析數位類比轉換器電容陣列 中,各電容之誤差對電路的影響,及其誤差來源;同時也要參考前人所提出 的演算法有何優點與缺點,最後提出一種創新的校正演算法。再以 Matlab 建立將此種演算法加入 SA ADC 後的動作模型,使用動作模型檢查演算法的 可行性。確認動作模型無誤後再將之轉化成實際電路,透過 Hspice 進行前 模擬(Pre-simulation),確認電路功能與整體設計無任何錯誤後,才開始進 行佈局與後模擬(Post-simulation)。 至於降低功率,則先由電路層面來看,降低供應電壓通常是最快速降低 整體耗能的方法,故降低供應電壓來達到我們低耗能的需求;次從電晶體層 面來看,由於數位電路的功率消耗與其負載電容成正比關係,故盡可能的降 低數位電路的電晶體大小以減少負載電容,來降低功率消耗。

第二章

具有自我校正功能之 SA ADC 介紹

2.1. 可變解析度的 SA ADC

從上一章的結論中,我們可以知道 SA ADC 其解析度(Resolution)與 線性度(Linearity)會被數位類比轉換器(Digital-to-Analog Converter, DAC) 中,二進位加權式電容陣列(Binary weighted capacitor array)之匹配性所影 響。所以要將 SA ADC 之效能更往上提升,我們可以利用校正演算法來修正 DAC 中各電容間的不匹配問題。 另一種思考方向是,既然 DAC 陣列中的電容會因為不匹配而造成誤 差,那我們何不降低電容的數量?電容數量降低,相對的電容最大值也降 低,就算它有誤差發生,對電路影響也不會太大。這的確是個不錯的方法, 所以傳統的八位元以下 SA ADC 幾乎是不需要校正的,因為其電容數量並不 多。但是這會造成整體解析度無法提高的問題,因此不做校正的 SA ADC 其 有效位元(Effective number of bits, ENOB)將會很難突破十位元。

於[14]提出一種可變解析度的 SA ADC,其架構如圖 2-1 所示。

其架構採取雙端輸入,經過一個類比減法器後得到差動輸入信號 Vdiff,

再將此信號經由取樣保持電路(Sample and Hold Circuit, SHC),與使用新式

二分搜尋法所產生的信號送入比較器做比較,最終得到一筆序列格式輸出 (Serial format)的 N 位元數位編碼。 其新式的二分搜尋法如圖 2-2 所示,利用一個連接成電壓緩衝器的 Op-amp,加上兩個電容串聯之分壓,組合而成一個除二電路。取代傳統的 二進位加權式電容陣列之 DAC,提供給比較器一個

( )

VREFi i V 2 = 之類比輸入信 號,其中 i 為此 SA ADC 之位元數,可以隨需求而改變。 圖 2- 2 新式二分搜尋架構圖 由圖 2-2 可知,傳統的二進位加權式電容陣列 DAC,所提供的二進位權 重式的類比電壓,如今被一組電壓除二電路所取代。此電路之輸出類比電壓 為V( )

i VREFi 2 = ,電壓除二電路的輸出與輸入端之間存在一個類比式的 Delay cell。故若要提升此 SA ADC 之解析度,只要增加除二電路動作之時脈數, 使其反覆除二次數 i 增加,就可以讓 V(i)經由更多次的除二步驟,被切割成 更小更精準的 V(i)。由於此電路只由兩個單位電容構成,所以只要控制好此兩個電容的匹配 度,就可以使電路有良好的解析度與線性度。同時比起傳統的二進位加權式 電容陣列之 DAC,此電路被電容所佔面積非常小,可以大幅減少晶片面積 以降低成本。而即使電容數目下降,也不會因此限制了它的解析度。 然而此電路之缺點為使用了大量的「類比式」減法器,類比式減法器其 原理為差動式 Op-amp,比較兩輸入端差值而輸出一類比電壓。當解析度提 高的時候,其對於減法器要求更嚴格,而類比減法器在設計上是十分困難 的,特別是高精準度的類比減法器。所以當 SA ADC 之解析度不再受限於 DAC 的時候,卻受限於類比減法器,是提升這個架構精確度的主要問題。 另外此架構在轉換模式時,所需時脈過長也是問題之一。傳統二進位加 權式電容陣列 DAC,依序將 2 REF V 、 4 REF V 、 8 REF V 到VREFN 2 加入比較器負端,若 要完成 N 位元的轉換則至少需要 N 個時脈週期。 如今此電路產生 2 REF V 需要 1 個時脈週期,產生 4 REF V 需要 2 個時脈週期, 產生VREFN 2 則需要 N 個時脈週期,所以其完成 N 位元之轉換時,所需時脈週 期至少為

(

N)

N 2 1 + 個,過長的轉換周期使此 SA ADC 之速度受到限制。就以 上之問題看來,此種新穎架構之 SA ADC 尚有許多改善空間。2.2. 應用於 SA ADC 之由高至低式校正演算法

於 1983 年,D.A. Houges 等人提出一種應用於 SA ADC 之校正演算法 [15][16][17],因為其誤差計算之順序是由最高位元(Most Significant Bit, MSB)電容開始,至最低位元(Least Significant Bit, LSB)電容結束,故以 下稱其為「由高至低(Top-Down)」式演算法。

其架構如圖 2-3 所示,此種 SA ADC 在開機後會有一小段的自我校正 (Self-Calibration)時間,在此時間內利用所提出的由高至低式演算法,找

出待校正電容陣列中(CN、CN-1、CN-2…C1),各電容的誤差量。其值為一數

位化的編碼,儲存於暫存器內,接著進入正常轉換模式。其中校正用數位類

比轉換器(Calibration DAC)透過單位電容 Ccal與比較器負端連結。

電路進入正常轉換模式後,其動作與一般 SA ADC 無太大差異,但是會 在轉換同時,根據當下之位元輸出為 0 或 1,而決定是否要累加其對應的誤 差量校正項。若此時輸出之位元為 1,則將此電容之誤差量的數位編碼,透 過 Calibration DAC 將其轉換成類比電壓,於比較器負端扣除此值。如此邊 轉換邊扣除對應的誤差量校正項,最終可以得到一個校正後的數位輸出。 圖 2- 3 應用由高至低式校正演算法之 SA ADC 架構圖 待校電容陣列是二進位加權式的電容陣列,各電容間的關係為: i i C C+1=2 (i=1,2,3…,N-1),我們以其計算 MSB 電容 CN、與 MSB-1電容 CN-1 之誤差量做範例,詳細說明整體誤差計算步驟。

計算 MSB 電容 CN之誤差量的方式如圖 2-4 所示,包含兩個主要步驟。

以此演算法完成一個電容的誤差計算至少需要兩個主要步驟,第一個步

驟為預先充電模式(Pre-charge phase),第二個步驟為電荷重佈模式(Charge

re-distribution phase)。接著第三個步驟起則是將 Vdac(2)數位化的 SA ADC 標

準轉換模式,此步驟之長度則視 Calibration DAC 之位元數決定。 先定義參數如下: sub N i i tot C C C =

∑

+ =1 表示參與誤差計算步驟中,所有的電容值總和。其中Csub是連接 Main DAC 與 Sub DAC 之單位電容,其值和 LSB 電容 C1相等。

N tot N C C C = +Δ 2 表示 MSB 電容之實際值有了大小為ΔCN之誤差量, MSB 電容之理想值,為整體參與誤差計算步驟中之電容值總和之一半。 N tot N C C C = −Δ 2 表示除了 MSB 電容之外,其餘參與誤差計算步驟中之 電容值和。 在第一個步驟,也就是預先充電模式時,將開關 Sx導通,於是比較器構 成一個負回授,由於虛短路(Virtual short)的關係,此時比較器負端電壓 Vdac(1)為 0。同時設定各參與誤差計算步驟之電容,其下板開關之位置如圖 2-4 之 Step.1 所示。 第二步驟為電荷重佈模式,關閉開關 Sx,於是比較器負端之電荷將會進 行電荷重佈。同時設定各參與誤差計算步驟之電容,其下板開關之位置,切 換為和 Step.1 完全反向的位置,如圖 2-4 之 Step.2 所示。且得到此時比較器 負端之電壓為: tot N N REF N N N N REF dac C C C V C C C C V V = − + − = ) 2 ( (2.1) 由上式(2.1)可以觀察到,當CN與CN 相等時,也就是ΔCN為零時,

此電壓 Vdac(2)為 0,也就是此時電容CN為理想值且無誤差。

接著第三個步驟開始則是轉換模式,設定各參與誤差計算步驟之電容,

其下板開關位置保持在 Step.2 之位置,如圖 2-4 之 Step.3~所示。將 Vdac(2)以

Calibration DAC 數位化後,進行一些運算後且儲存,此步驟之長度將取決於 Calibration DAC 之位元數。 為了推導 Vdac(2)與 CN之誤差量的關係式,將式(2.1)重新整理後,重 新表示成如下之型式: ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = Δ = 2 1 2 2 2 2 ) 2 ( tot N REF tot tot N REF tot N REF dac C C V C C C V C C V V (2.2) 定義數位化之運算子為D

( )

x ,符號 D 為表示一個「數位化」之動作的 算符(Operator),定義 CN之誤差量數位化後的結果為 DeN: ⎥⎦ ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = 2 1 tot N REF eN C C V D D (2.3) 則由式(2.2)與(2.3)可以得到兩者之關係:(

)

eN tot N REF dac C D C V D V D 2 2 1 2 ) 2 ( ⎥⎦= ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = (2.4)(

(2))

2 1 dac eN DV D = (2.5) 故由式(2.5)可知,若要由數位化後的 Vdac(2)找出 CN之誤差量,所需 要的運算僅僅是把數位碼 D(Vdac(2))右移一位即可。 接著進入計算 MSB-1電容 CN-1的誤差量之步驟,在這步驟中必須排除已 完成誤差計算之電容 CN,對該次誤差計算的影響。也就是在預先充電、電 荷重佈模式、以及數位化轉換模式時,將電容 CN之下板開關位置保持一定, 不論固定接地(0)或是固定接 VREF(1)皆可。計算 MSB-1電容 CN-1的誤差量之步驟如圖 2-5 所示。

先定義參數如下: sub N i i tot C C C =

∑

+ =1 表示參與誤差計算步驟中,所有的電容值總和。其中Csub是連接 Main DAC 與 Sub DAC 之單位電容,其值和 LSB 電容 C1相等。

N tot N C C C = +Δ 2 表示 MSB 電容之實際值有了大小為ΔCN之誤差量。 1 1 4 − − = +Δ N tot N C C C 表示 MSB-1電容之實際值有了ΔCN-1之誤差量, MSB-1電容之理想值,為整體參與誤差計算步驟中之電容值總和之 4 1 。 1 1 4 − − = −Δ N −Δ N tot N C C C C 表示除了 MSB 與 MSB-1電容之外,參與誤差 計算步驟中之電容值和。 在第一個步驟,也就是預先充電模式時,將開關 Sx導通,於是比較器負 端構成一個負回授(Negative feedback),由於虛短路的關係,此時比較器負 端電壓 Vdac(1)為 0。此時設定各參與誤差計算步驟之電容,其下板開關之位 置如圖 2-5 之 Step.1 所示。 第二步驟為電荷重佈模式,關閉開關 Sx,於是比較器負端之電荷將會進 行電荷重佈。同時設定各參與誤差計算步驟之電容,其下板開關之位置,切 換為和 Step.1 完全反向的位置,如圖 2-5 之 Step.2 所示。且得到此時比較器 負端之電壓為: tot N N REF N N N N N REF dac C C C V C C C C C V V 1 1 1 1 1 1 ) 2 ( − − − − − − = − + + − = (2.6) 接著第三個步驟開始則是轉換模式,設定各參與誤差計算步驟之電容,

其下板開關位置保持在 Step.2 之位置,如圖 2-5 之 Step.3~所示。將 Vdac(2)以

Calibration DAC 數位化後,進行一些運算後且儲存,此步驟之長度將取決於 Calibration DAC 之位元數。

為了推導 Vdac(2)與 CN-1之誤差量的關係式,將式(2.6)重新整理後,重 新表示成如下之型式: tot tot N tot N REF tot N N REF dac C C C C C V C C C V V ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = Δ + Δ = − − 4 2 2 2 1 1 ) 2 ( (2.7) 再化簡式(2.7)可得: ⎥⎦ ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = − 2 1 4 1 2 1 ) 2 ( tot N tot N REF dac C C C C V V (2.8) 定義 CN-1之誤差量數位化後的結果為 DeN-1: ⎥⎦ ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = − −1 1 14 tot N REF eN C C V D D (2.9) 則由式(2.3)結合式(2.9)後,代入式(2.8)可以得到三者之關係:

(

)

eN eN tot N tot N REF dac C D D C C C V D V D = + ⎭ ⎬ ⎫ ⎩ ⎨ ⎧ ⎥⎦ ⎤ ⎢⎣ ⎡ ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − = − − 1 1 ) 2 ( 2 14 12 2 (2.10)(

)

[

dac eN]

eN DV D D −1= (2) − 2 1 (2.11) 故由式(2.11)可知,若要由數位化後的 Vdac(2)找出 CN-1之誤差量,所 需要的運算僅僅是把數位碼 D(Vdac(2))減去 DeN後,再右移一位即可。 將式(2.11)延伸,可以推導出以下之通式:(

)

⎥ ⎦ ⎤ ⎢ ⎣ ⎡ − =∑

+ = N i p e dac ei DV i D p D 1 ) 2 ( 2 1 (2.12) 至此知道了每個步驟中之 Vdac(2)與 Dei 的關係,如此就可以看出圖 2-3 中各元件的作用,必須在普通的 SA ADC 內加入一個累加器與暫存器去完成 這些數位運算。以及加入一些控制電路去控制整體電路時序之動作,並且加入一組 Calibration DAC 負責將每個步驟中之 Vdac(2)數位化,以及將每次轉換 時累積的誤差量校正項轉換成類比電壓。 此校正演算法於 1983 年提出至今已有 20 多個年頭,依舊是 SA ADC 中 校正演算法的先驅與典範,之後被應用於各式的 SA ADC 中,成為照亮 SA ADC 的一盞明燈。更被列於[18]之教材章節中,成為每個修習類比積體電路 的學子必讀之經典,可見此篇論文之重要性與可貴性。 然而此篇校正演算法先驅存在三個主要缺點,這也是我們所提出之演算 法所欲改良的地方。 第一,此篇論文使用了「混合信號式校正」。 將每個步驟中之 Vdac(2)轉換成數位編碼後,進行一些運算後儲存;之後 在每次轉換時,根據當下的輸出是 0 或 1 決定是否要將此電容之誤差量加入 累積的誤差量校正項中。邊轉換邊透過 Calibration DAC 將累積至今的誤差 量校正項轉換成類比電壓模式,於比較器之負端扣除此誤差量校正項。 如此會經過一次類比數位轉換,一次數位類比轉換,其中產生了兩次的 轉換誤差,這表示對於 Calibration DAC 之精準度要求甚高;特別是當 SA ADC 之解析度很高的時候。 第二,此篇論文需要兩個精準對稱的正負參考電壓。 由於比較器正端始終接地,所以比 0 還小的 Vdac(2)才能被轉換成數位編 碼,由式(2.1)發現,Vdac(2)有可能比 0 大、亦可能比 0 小,取決於該電容 的誤差量是比標準值多或低。若當 Vdac(2)有正值發生,則無法將此值數位化, 也就是無法處理誤差量是負值的情形。 為了解決此情形,該作者於電路中使用了正向與負向的參考電壓,如此 便可應付電容的誤差量是比標準值多或低的情形。由此可知,此正向與負向

的參考電壓需要精準對稱,以免在轉換過程中產生誤差。然而在現實世界中 難以實現完全精準對稱的電壓源對,這也是尚待改善的地方。

另一個缺點是當負電壓的 Vdac(2)出現在比較器負端時,開關 Sx可能會有

漏電流發生,這表示負向的 Vdac(2)有其可以處理的極限值,若負的過多可能

會造成電荷由開關 Sx漏光。

第三,連接 Calibration DAC 的電容 Ccal並未在其誤差校正項中被考慮。

電容 Ccal為連接 Calibration DAC 的單位電容,理論上該電容值應該在校

正過程中被考慮,才能將各電容間之「絕對誤差」量修正成「相對於比較器 負端整體電容值的『相對誤差』」量。 若不考慮電容 Ccal對誤差量校正項之影響,則得到的校正項是「絕對」 於「理想值」的校正項;必須考慮電容 Ccal在誤差計算時的角色,才能得到 「相對」於「比較器負端並聯電容值總和」之誤差量校正項。 雖然有以上幾種小缺點,但是此篇論文對 SA ADC 之貢獻仍然瑕不掩 瑜,此論文至 1983 年提出至今,尚未有人提出過其他的校正法,仍然是 SA ADC 校正法內的翹楚。

2.3. 應用於 SA ADC 之由低至高式校正演算法

另一種應用於 SA ADC 之校正法在隔年(西元 1984 年)被提出,其架 構如圖 2-6 所示。在申請專利[19]兩年後,作者本人 K.S TAN 又將此架構改 良且應用於雙端差動輸入的 SA ADC 之上[20]。 和前篇不同的是,此種架構之校正法是採用「由低至高(Bottom-up)」 的方式計算待校電容陣列中各電容之誤差,也就是先從計算 LSB 電容之誤 差量開始,至計算 MSB 電容之誤差量為止,由最小電容開始至最大電容結束的方式。其中各組 DAC 皆以 Binary weighted capacitor 之架構完成,和先 前的架構相比,有著相對較低的功率消耗。

圖 2-6 所包含之附加元件大致和圖 2-3 所提出之架構類似,需要多一組 控制電路控制整體電路動作之時序、需要一組記憶體來儲存各個電容的誤差 校正項、以及需要一組誤差電容陣列(Error capacitor array)當做整體校正 演算法的核心。

圖 2- 6 應用由低至高演算法之 SA ADC 架構圖

而其類比部份之元件如圖 2-7 所示,以圖 2-7 講解其誤差計算之步驟。

其中 Capacitor array 為二進位加權式電容陣列,待校正部份為 CN、CN-1、

CN-2…C1,各元件之關係為:Ci+1=2Ci(i=1,2,3…,N-1),C1為單位電容,C0

為達成二進位權重之單位電容,Ccal為連接 Error capacitor array 之單位電容。

以計算 MSB、MSB-1、和 MSB-2這三顆電容之誤差量做範例說明。

起。MSB-2電容 CN-2其理想值為 Ctot 8 1 ,其中定義

∑

= = N i i tot C C 0 。這種由低至高 的演算法也包含主要的兩個步驟。 圖 2- 7 文獻[19]所提出之 SA ADC 類比部分架構 步驟一,將開關 Sx導通,於是比較器的負端被接地,同時將各電容陣列 內,其中各電容下板開關之位置設定成:{

SN,SN−1,SN−2,SN−3,SN−4,...,S0} {

= 0,0,0,1,1,...,1}

{

SE6,SE5,SSE4,SE3,SE2,...,SE0} {

= 0,0,0,0,0,...,0}

如此第一步驟為預先充電模式,此時比較器負端之電壓為 0,和前篇之 第一步驟原理相同。 第二步驟將開關 Sx關閉,於是比較器的負端進入電荷重佈模式,再將各 電容陣列內,其中各電容下板開關之位置設定如下:{

SN,SN−1,SN−2,SN−3,SN−4,...,S0} {

= 0,0,1,0,0,...,0}

{

SE6,SE5,SSE4,SE3,SE2,...,SE0} {

= 0,0,0,0,0,...,0}

經由改變各電容陣列內,其中各電容下板開關之位置,使電荷重新分佈 後,由∑

− = − = 3 0 2 N i i N C C 之關係,則電荷重佈的結果,將使比較器之負端出現一個 類比電壓。此類比電壓之型式和式(2.1)所描述的型式雷同,取決於CN−2和∑

− = 3 0 N i i C 之差異,此類比電壓即為電容CN−2之誤差量。 和前篇論文之不同地方在於,SN和 SN-1由於和計算CN−2之誤差量的步驟 無關,所以在此並不將其加入預先充電模式或是電荷重佈模式中,故在這兩 個步驟中將 SN和 SN-1保持在固定電位即可。接下來的步驟中,利用 Error capacitor array 將比較器負端出現的,表示

2 − N

C 之誤差量的類比電壓數位化,此步驟因為 Error capacitor array 有七個位

元,所以總共需要七個時序完成數位化的動作,且將其儲存於記憶體內。接 著進入計算 MSB-1電容 CN-1之誤差量的步驟。 計算 MSB-1電容 CN-1之誤差量的第一步驟,仍然是將開關 Sx導通,於 是比較器的負端被接地,同時將各電容陣列內,其中各電容下板開關之位置 設定成:

{

SN,SN−1,SN−2,SN−3,SN−4,...,S0} {

= 0,0,1,1,1,...,1}

{

SE6,SE5,SSE4,SE3,SE2,...,SE0} {

= Error codeofCN-2}

由於已經對 MSB-2電容 CN-2完成誤差計算,所以在此必須排除 CN-2對此次誤差計算步驟之影響,透過將 Error capacitor array 內各電容下板開關之

位置,設定成表示電容 CN-2之誤差量的數位編碼,如此便能以「類比電壓」

接著第二步驟將開關 Sx關閉,於是比較器的負端進入電荷重佈模式,將 各電容陣列內,其中各電容下板開關之位置設定成:

{

SN,SN−1,SN−2,SN−3,SN−4,...,S0} {

= 0,1,0,0,0,...,0}

{

SE6,SE5,SSE4,SE3,SE2,...,SE0} {

= Error codeofCN-2}

同理,經過電荷重新分佈後,由∑

− = − = 2 0 1 N i i N C C 之關係,比較器之負端將出 現一個類比電壓。此類比電壓之型式和式(2.1)所描述的型式雷同,取決 於CN−1和∑

− = 2 0 N i i C 之差異,此類比電壓即為電容CN−1之誤差量。接下來的步驟中,利用 Error capacitor array 將比較器負端出現的,表示

1 − N C 之誤差量的類比電壓數位化且儲存。接著進入計算 MSB 電容 CN之誤差 量的步驟,在此就不多加贅述。 由以上的步驟中發現,使用由低至高演算法的好處是,其數位計算步驟 更加簡略,不需要一些額外的減法器電路就可完成,比起使用由高至低演算 法來說,節省了數位部分的面積。 但其缺點是,由於每次執行誤差計算演算法時,都要排除已完成誤差計 算之電容,對這次之誤差計算的影響,所以必須以「類比方式」透過 Error capacitor array 之設定,由比較器之負端扣除。如計算 MSB 電容 CN之誤差

量時,Error capacitor array 之設定為:

{

SE6,SE5,SSE4,SE3,SE2,...,SE0}

={

Error codeof(

CN−2 +CN−1)

}

如此可以發現,當欲計算誤差的電容數量上升時,Error capacitor array 內所設定之誤差量便會累積,故需要加大 Error capacitor array 之位元數來達 成此需求。節省了數位計算的面積,卻浪費了更大的 Error capacitor array 電 容面積,似乎看不出能有效減少的面積。

其另外三個主要缺失也和上篇雷同:「使用混合信號式校正」和「需要 兩個精準對稱的參考電壓」以及「當比較器負端出現負電壓時,開關 Sx之漏 電流疑慮」。故此篇專利也有待改進之處,但仍不失與上篇並列 SA ADC 校 正法唯二經典的光采。

2.4. 具有自我校正功能的 SA ADC 之一[21]

有一篇整合以上兩者之 SA ADC 於 2001 年被提出[21],其取 H.S LEE 之演算法,採取「由高至低」之誤差計算方式;然而將數位類比轉換器陣列 由高耗能的電阻串架構,改良成 K.S TAN 之電容陣列架構以降低耗能。其 類比部份之架構如圖 2-8 所示。 此電路共有四個二進位加權電容陣列構成之數位類比轉換器,其中 Main DAC 為待校電容陣列,與 Sub DAC 構成此 ADC 之主要數位類比轉換 器陣列,其兩者位元數總和則為此 SA ADC 之位元數。圖 2- 8 具有自我校正功能的 SA ADC【1】類比部分之架構

capacitor array,負責處理電路的 Offset 問題。其處理方式和 Error capacitor array 雷同:

先將所有電容下板開關都切換到 0(接地),如此比較器負端應該出現 之電壓為 0 伏特;換言之,若有不為 0 伏特的電壓出現在比較器負端,則此 值即為電路 Offset 電壓。透過 Offset capacitor array 將其數位化後,不需要儲 存,只要在之後的所有步驟都將 Offset capacitor array 之電容下板開關切換成 此值,就能以類比方式在比較器負端消除該 Offset 電壓。 然而此篇論文沿用兩篇經典之架構,缺點仍和兩篇經典雷同:「使用混 合信號式校正」和「需要兩個精準對稱的參考電壓」以及「當比較器負端出 現負電壓時,開關 Sx和 Sr之漏電流疑慮」。

2.5. 具有自我校正功能的 SA ADC 之二[22]

第二篇整合以上兩篇經典的論文於 ISSCC 1990 被提出[22],其架構之豪 華如圖 2-9 所示。 其架構之方塊圖如圖 2-9 所示,依然是取 H.S LEE 之演算法,採取「由 高至低」之誤差計算方式;然而將數位類比轉換器陣列由高耗能的電阻串架 構,改良成 K.S TAN 之電容陣列架構以降低耗能。 此篇論文所提出之 SA ADC 共有 18 位元,其解析度為當今世上 SA ADC 所見最高;然而其輸入電壓範圍為 20 伏特,也是當今世上所見最高。 此「雙重最高」殊榮的 SA ADC 將類比和數位晶片獨立,透過外部接線 互相連接,如此便可單獨測試類比與數位方面的良率與問題所在;但是如何 克服連接兩晶片之導線的寄生電容卻是個問題。圖 2- 9 具有自我校正功能的 SA ADC【2】架構方塊圖

然而此篇論文沿用兩篇經典之架構,缺點仍和兩篇經典雷同:「使用混

合信號式校正」和「需要兩個精準對稱的參考電壓」以及「當比較器負端出