高介電閘氧化層深次微米 MOS 元件電漿製程傷害可靠性之研究

Investigation of the Plasma Induced Damage on High Gate Dielectric Deep-Submicron MOSFET’s

計畫編號:NSC 90-2215-E-009-065

執行期限:90 年 08 月 01 日至 91 年 07 月 31 日

主持人:莊紹勳 國立交通大學電子工程學系

一、中文摘要 隨半導體製程技術的演進及元件尺寸 的微縮,量子穿隧效應使得閘氧化層有嚴 重的漏電流產生。為了有效的降低閘氧化 層漏電流,採用具有較高介電係數(K 值) 之閘氧化層,諸如 High-K[1-7]或是高濃度 電漿氮化閘氧化層[8-10]都是近一兩年內 半導體產業發展的重點。然而,受限於 High-K 閘氧化層的材料特性仍在研究階 段,其熱穩定性差且內部缺陷多,所以短 期內無法整合於先進之半導體製程中;相 對於 high-K 材料,高濃度電漿氮化閘氧化 製程與先進半導體製程相容性高,製程整 合容易,即使其氧化層材質 K 值稍低一 些,可以解決漏電流問題。因此,本計劃 著眼於此,針對高濃度電漿氮化閘氧化層 0.1µm 元件進行一系列的分析。 在本計劃中,吾人將研究 0.1µm 元件 製程所使用之高濃度電漿氮化閘氧化層 (16Å)的電漿製程傷害及其相關製程可靠 性。首先,吾人設計及製作超小型(0.1µm) 元件一批,利用 RTNO 成長基層氧化層 (base oxide),接著進行高濃度電漿氮化 (RPN)處理,而得到小約 2-3 個 order 的閘 極漏電流值。本計劃所得的重要結論包含 以下數點: (1) 高濃度電漿氮化氧化層有 效的降低了 0.1 微米元件的漏電流,可進 一步的降低電路操作的功率消耗﹔(2)高 濃 度 氮 化 成 份 被 導 入 基 層 氧 化 層 (base oxide),這使得元件的界面缺陷變多,這 會退減元件的遷移率(mobility)﹔(3) 高濃 度電漿氮化製程會造成額外的電漿製程傷 害,這使得晶圓良率/品質/電特性的分佈 變的不均勻。所以如何找出一個更適切設 備來完成更穩定的高介電材質成長,為未 來小於 0.1 微米元件設計之關鍵技術。 關鍵詞:高介電閘氧化層,高濃度電漿氮 化閘氧化層,電漿製程傷害,電荷幫浦法, 元件可靠性。 AbstractWith the aggressive scaling of CMOS technology continues and the scaling of the device channel length, the gate leakage current increases as a result of direct tunneling. In order to reduce the gate leakage current, the higher K dielectric constant materials, such as high-K and the plasma-nitrided oxides, are mandatory. However so far, the high-K gate dielectrics technology used in CMOS devices are not matured at all. Most of them do not have good thermal stability but have more traps or defects, which will worsen the device reliability. On the other hand, even the K value of plasma- nitrided oxide is not so-high (around 4-5), its leakage can meet the requirement of sub-100nm device specification, which has been used in nano-scaled device design. Thus, in this project, we will focus on the plasma-nitrided oxide and analyze its plasma-induced ozide damage.

In this project, we will study the plasma induced damage and the related reliability issues for the 16Å plasma-nitrided gate oxide in 100nm device. First, we designed and fabricated test samples with 100nm feature size. The base oxide is formed by RTNO process, and then remote plasma nitradation (RPN) treatment was used to obtain a lower gate leakage and a near high-K gate dielectric. Several important results have been drawn from this study. First, as expected, the plasma-nitride oxide has reduced

tunneling leakage for the 100nm devices. This can reduce the power consumption during circuit operation. Second, the high concentration nitrogen has been driven into gate oxide in the plasma-nitrided oxide, which will induce large amount of interface traps and degrade the device mobility. Third, the plasma-nitrided oxidation will induce extra plasma damage and be reflected in the non-uniform wafer yield, oxide quality, and device characteristics. Therefore, to find the more suitable manufacturing equipment for forming a higher quality gate dielectric has become a key technology for the sub-100nm device design.

Keywords: high-K gate dielectric, plasma- nitrided oxide, plasma damage, charge pumping technique, device reliability. 二、計劃緣由與目的 CMOS 製程技術發展迄今,開始面臨 到一個重大的問題。隨著元件尺寸縮小, 元件閘氧化層必須微縮。迄今,採用傳統 二氧化矽(SiO2)的閘氧化層開始面臨量子 穿隧效應的極限,這使得閘極漏電流過 大,而無法符合積體電路的要求。美國 SIA Roadmap 指出,為了有效降低元件閘氧化 層漏電流,勢必將採用高介電係數(High-K) 之閘氧化層材質[1-10]。然而,傳統 SiO2 閘氧化層已經被應用多年,其材料特性穩 定且與現行半導體製程相容性最高,但是 受限於閘極漏電流﹔若改以 High-K 材料 [1-7]作為閘氧化層材質時,則必須克服材 料穩定性及製程相容性的問題。目前有個 折衷的辦法已被廣為採用,那就是利用高 濃度電漿氮化閘氧化製程(plasma-nitrided oxide)[8-10],來抑制閘極漏電流的發生﹔ 其優點在於,其製程整合相容性高,且漏 電流可降低數個 order 電流。 在高濃度電漿氮化閘氧化製程中,所 會遭遇到的第一的問題會是- 此一高劑量 的電漿製程所帶來的製程傷害。它除了會 造成晶圓各區域元件電性特性的變異外, 也會對元件的可靠性造成嚴重的傷害。而 且在此一超小(小於 0.1 微米)元件,超薄閘 氧化層(16Å)中,這種高濃度電漿傷害造成 的電性及可靠性影響更是難以去估計。 本計劃即設計多個實驗,用來檢測此 一高濃度電漿氮化閘氧化製程所導致的製 程傷害以及相關電性及可靠性問題。用來 建立新世代元件(小於 0.1 微米 CMOS 元件) 之閘氧化層相關可靠性之研究。是故,本 計劃的目的有三:其一乃是開發適用於小 於 0.1 微米 CMOS 元件之超薄高濃度電漿 氮化閘氧化製程﹔其二為探究電漿製程傷 害對此類型氧化層之特性影響﹔其三乃是 評測該氧化層之電性暨可靠性。於是,本 研究之完成,將可提升小於 0.1 微米 CMOS 超薄氧化層製程之品質、良率以及可靠 性,對半導體工業生產上有莫大的助益。 三、結果與討論 本計劃旨在研究電漿製程傷害對高介 電閘氧化層可靠性之影響,用以建立未來 0.1 微米以下 CMOS 元件閘氧化層相關技 術。在本研究中,吾人以高濃度電漿氮化 閘氧化製程來完成超薄氧化層之製作,同 時進行多種電性分析,來觀測元件電漿製 程傷害及其元件的可靠性問題。 在本計劃中,乃以高濃度電漿氮化閘 氧化層元件為研究對象,以電漿蝕刻傷害 的研究為目標,分別進行以下兩個部分的 探討:(1) 高濃度電漿氮化閘氧化層元件 之基本電性分析﹔(2) 高濃度電漿氮化閘 氧化層元件之電漿製程傷害分析。各項研 究工作細節分述如下: (1) 高濃度電漿氮化閘氧化層元件之基本 電性分析 首先,我們針對此一系列之研究,設 計兩種不同的氧化層材質。一種為快速回 火氮化氧(RTNO)成長之氧化層,此材質為 當代最常用之閘極氧化層(base oxide)﹔另 一種為將前述之 RTNO 氧化層,再進行高 濃度電漿氮化(plasma-nitrided oxide),完成

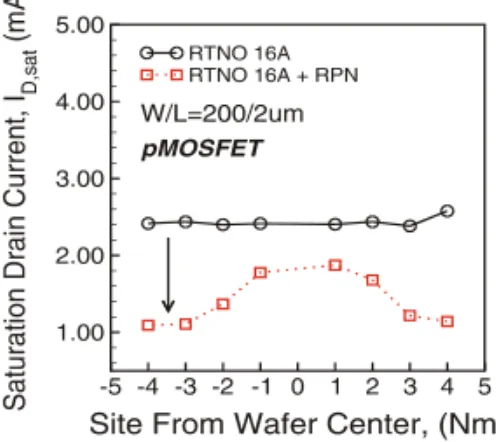

一個介電值稍高且漏電流較低之閘氧化 層。兩者厚度皆設計在 16Å,以適用於設 計小於 0.1 微米閘極長度(其採用 0.14 微米 光罩長度)元件。 首先,吾人量得 300*3µm2 大小 nMOS 元件的電容值,由 Fig. 1 上可知 plasma- nitrided oxide 的介電值約為 RTNO 氧化層 的 1.2 倍,推估可得知其介電係數約在 4~5 之間。 接著,吾人分析位於 Wafer 中心區域 的 MOSFET 元件基本電性。Figs. 2 和 3 分別表示 nMOSFET 元件的次臨界區域電 流特性以及飽和電流特性。由 Fig. 2 可 知,大量的電漿氮化製程造成的會是元件 VTH值的下降。所以,這個特性反映到 Fig. 3 中將會是造成飽和電流(ID,sat)微微的上 升。接著吾人量測其電荷幫浦電流(charge pumping current),其結果如 Fig. 4 所示。 其中,因為 plasma-nitrided oxide 被導入了 大量的氮成份進入氧化層(oxide),形成一 個介於 SiO2與 Si3N4的材質﹔其材料上會 類似於 Si3N4 的特性,它造成的是閘氧化 層界面缺陷多,所以量測出來的 ICP 電流 也就較大。最後,如 Fig. 5 中所示,採用 高濃度電漿氮化閘氧化層之元件確實獲得 較小的漏電流,可以有效的降低電路操作 時的功率消耗。 同樣的,吾人分析 pMOSFET 元件的 特性。Figs. 6 和 7 分別表示 pMOSFET 元 件的次臨界區域電流特性以及飽和電流特 性。在 pMOSFET 元件中,大量的電漿氮 化製程造成的會是元件 VTH值的下降以及 飽和電流(ID,sat)微微的上升。其電荷幫浦電 流結果如 Fig. 8 所示,同樣的因為材料特 性類似於 Si3N4,它亦會造成較多的閘氧化 層界面缺陷,所以量測出來的 ICP 電流也 就較大。附帶一提的,吾人看到 pMOSFET 元件中產生的界面缺陷量遠比 nMOSFET 元件來的多,所以對 mobility 的影響將會 來的更大。最後,如 Fig. 9 中所示,採用 高濃度電漿氮化閘氧化層的 pMOSFET 元 件亦會獲得較小的漏電流,可以有效的降 低功率消耗。 (2) 高濃度電漿氮化閘氧化層元件之電漿 製程傷害分析 要研究高濃度電漿氮化閘氧化層元件 的電漿蝕刻傷害,吾人可以沿著 Wafer 中 心到邊緣區域,分析各種元件電性的變化 情形。 A. nMOSFET 元件之電漿製程傷害分析 首先吾人將探討不同尺寸 nMOSFET 元件在採以高濃度電漿氮化製程之後,所 造成的電性變化情形。先看到小尺寸元件 (其 LMASK=0.14µm,在 poly-Si gate 蝕刻完

後,Lgate約為 0.10µm﹔而 WMASK=10µm)

的電性變化情形。

Figs. 10 及 11 中,分別為臨界電位(VTH)

與轉導(GM)。對於 RTNO (base oxide)來

說,VTH在 Wafer 的任何位置幾乎都是差 不多的,但是採以高濃度電漿氮化製程 後,其 VTH值不僅會有下降的情形,而且 會隨著位置而有所變化。由相關的電漿蝕 刻傷害的論文中可知,此類型的元件已經 承受了某種程度的電漿製程傷害。另外, 由 GM來看,發現它也呈現下降的趨勢。

Fig. 12 中圖示飽和電流(ID,sat)的變化情

形,由這張圖可看出在 Wafer 中心區域幾 乎沒有變化﹔而在邊緣區域因為臨界電壓 (VTH)變小,所以飽和電流變大。 接著來看電荷幫浦法量測的結果,由 Fig. 13,可以發現 RTNO 的氧化層界面缺 陷的產生量很接近﹔倒是高濃度電漿氮化 閘氧化層元件的界面缺陷產生量非常的不 均勻。在漏電流研究上,由 Fig. 14 可以看 出類似的結果,Wafer 中心區域的 gate leakage 較大,邊緣的 gate leakage 較小。

相對於前述之小尺寸元件,對於大尺 寸的 nMOSFET 元件來說,這種高濃度電 漿氮化氧化製程造成的電漿製程傷害影響 較小。由 Figs. 15 到 19 秀的分別是大尺寸

nMOSFET 元件所量測出來的結果。特別 是在 Fig. 17 中,飽和電流(ID,sat)在高濃度

電漿氮化前後幾乎是沒有變化﹔而在其他 張圖中,也可很明顯的看出其影響皆小於 它對於小尺寸元件的影響。 B. pMOSFET 元件之電漿製程傷害分析 我們亦探討採以高濃度電漿氮化製程 小尺寸 pMOSFET 元件的電性變化情形。 Figs. 20 到 22 中所示的分別為臨界電位 (VTH)、轉導(GM)與飽和電流(ID,sat) 的量測

結果。對於 RTNO (base oxide)來說,各種 量測結果在 Wafer 任何位置幾乎都是接近 的﹔相對的,採以高濃度電漿氮化製程之 後,即在各區域呈現不同程度的變化- 例 如: VTH在 Wafer 中心區域降低,而在邊緣

區 域 上 升 。 ( 一 方 面 加 劇 了 短 通 道 效 應 (short channel effect)﹔一方面產生了電漿 傷害。) 接著由 Fig. 23 電荷幫浦法量測的結果 高濃度電漿氮化閘氧化層元件的界面缺陷 產生量較大,也較不均勻。Fig. 24 中所示 為漏電流的量測結果,高濃度電漿氮化閘 氧化層明顯的降低了元件的漏電流值。 對於大尺寸的 pMOSFET 元件,吾人 量測出 Figs. 25 到 29 的結果。結果與小尺 寸量測出來的結果很類似,唯獨大尺寸元 件不會受到 short channel effect 的影響,所 以各個圖形的變化不是遞增就是遞減。例 如: 高濃度電漿氮化後 VTH上升,飽和電 流呈現遞減,而元件漏電流大幅降低。 C. 結果與討論 由前述結果可知,高濃度電漿氮化製 程對 0.1 微米以下超薄氧化層元件的設計 上,仍有諸多的缺點。即使元件的漏電流 大幅度的被降低外,但是付出的代價除了 因為含了 Si3N4 多氧化層缺陷的材料特性 外,另外也造成晶圓生產上因為電漿製程 傷害造成的良率/品質/電特性的分佈不 均﹔如何開發出一套新的高濃度電漿氮化 製程設備,可以有效的降低不勻稱的結 果,將會是未來 0.1 微米以下元件設計之 關鍵技術。 四、計劃成果自評 本 研 究 成 功 的 分 析 (16Å) 高濃度電 漿氮化閘氧化層 0.1 微米元件的電漿製程 傷害。此一結果,乃是高濃度電漿氮化製 程的相關研究中,最先披露其電漿製程傷 害結果,以及其對不同尺度元件之影響。 目前結果雖未發表於任何國際論文中,但 相信對現今之半導體界之 High-K 及高濃 度電漿氮化閘氧化層的研究將有長足之貢 獻。同時本計劃培育的國內優秀博、碩士 生在此半導體領域將可增進半導體研發之 能力與潛力。會有實質的幫助與具有極大 的參考價值。亦即,本計劃的完成,將對 學術界及工業界,將會有莫大的助益。 五、參考文獻

[1] K. Yoshikawa, in International Electron

Devices and Materials Symposium (IEDMS),

p. 11, 2000.

[2] I. -S. Park et al., in Symposium on VLSI Tech., p. 42, 2000.

[3] D. -G. Park et al., in Symposium on VLSI

Tech., p. 46, 2000.

[4] W. -J. Qi et al., in IEDM Tech. Digest (IEDM), p. 145, 1999.

[5] W. -J. Qi et al., in Tech. Digest of VLSI Tech., p. 40, 2000.

[6] S. J. Lee et al., in IEDM Tech. Digest (IEDM), p. 31, 2000.

[7] H. F. Luan et al., in IEDM Tech. Digest

(IEDM), p. 141, 1999.

[8] S. Song et al., in IEDM Tech. Digest (IEDM), pp. 3.2.1-3.2.4, 2001.

[9] S.-F. Ting et al., IEEE Electron Device Lett.

(EDL), vol. 22, pp. 327-329, 2001.

[10] C.-H. Chen et al., IEEE Electron Device Lett.

Fig. 1 Capacitance measurements for the 16Å base oxide (RTNO) and RPN treated gate dielectrics in nMOSFET’s.

Fig. 10 Threshold voltages for the 16Å base oxide and RPN treated gate dielectrics in short channel nMOSFET’s at various wafer sites.

Fig. 7 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in pMOSFET’s.

Fig. 4 Charge pumping measurements for the 16Å base oxide and RPN treated gate dielectrics in nMOSFET’s.

Fig. 11 Transconductances for the 16Å base oxide and RPN treated gate dielectrics in short channel nMOSFET’s at various wafer sites.

Fig. 8 Charge pumping measurements for the 16Å base oxide and RPN treated gate dielectrics in pMOSFET’s.

Fig. 5 Gate currents for the the 16Å base oxide and RPN treated gate dielectrics in nMOSFET’s.

Fig. 2 Subthreshold characteristics for the 16Å base oxide and RPN treated gate dielectrics in nMOSFET’s.

Fig. 9 Gate currents for the the 16Å base oxide and RPN treated gate dielectrics in pMOSFET’s.

Fig. 6 Subthreshold characteristics for the 16Å base oxide and RPN treated gate dielectrics in pMOSFET’s.

Fig. 3 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in nMOSFET’s.

Fig. 12 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in short channel nMOSFET’s at various wafer sites.

VB=0, -0.6, -1.2V VG=1.2V VG=0.6V VB=0, 0.6, 1.2V VG= -1.2V VG= -0.6V

Fig. 13 Charge pumping currents for the 16Å base oxide and RPN treated gate dielectrics in short channel nMOSFET’s at various wafer sites.

Fig. 22 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in short channel pMOSFET’s at various wafer sites.

Fig. 19 Gate tunneling leakages for the 16Å base oxide and RPN treated gate dielectrics in long channel nMOSFET’s at various wafer sites.

Fig. 16 Transconductances for the 16Å base oxide and RPN treated gate dielectrics in long channel nMOSFET’s at various wafer sites.

Fig. 23 Charge pumping currents for the 16Å base oxide and RPN treated gate dielectrics in short channel pMOSFET’s at various wafer sites.

Fig. 20 Threshold voltages for the 16Å base oxide and RPN treated gate dielectrics in short channel pMOSFET’s at various wafer sites.

Fig. 17 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in long channel nMOSFET’s at various wafer sites.

Fig. 14 Gate tunneling leakages for the 16Å base oxide and RPN treated gate dielectrics in short channel nMOSFET’s at various wafer sites.

Fig. 21 Transconductances for the 16Å base oxide and RPN treated gate dielectrics in short channel pMOSFET’s at various wafer sites.

Fig. 18 Charge pumping currents for the 16Å base oxide and RPN treated gate dielectrics in long channel nMOSFET’s at various wafer sites.

Fig. 15 Threshold voltages for the 16Å base oxide and RPN treated gate dielectrics in long channel nMOSFET’s at various wafer sites.

Fig. 24 Gate tunneling leakages for the 16Å base oxide and RPN treated gate dielectrics in short channel pMOSFET’s at various wafer sites.

Fig. 25 Threshold voltages for the 16Å base oxide and RPN treated gate dielectrics in long channel pMOSFET’s at various wafer sites.

Fig. 28 Charge pumping currents for the 16Å base oxide and RPN treated gate dielectrics in long channel pMOSFET’s at various wafer sites.

Fig. 29 Gate tunneling leakages for the 16Å base oxide and RPN treated gate dielectrics in long channel pMOSFET’s at various wafer sites.

Fig. 26 Transconductances for the 16Å base oxide and RPN treated gate dielectrics in long channel pMOSFET’s at various wafer sites.

Fig. 27 Saturation drain currents for the 16Å base oxide and RPN treated gate dielectrics in long channel pMOSFET’s at various wafer sites.