國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

奈米金氧半製程之線性穩壓器自動化設計

Low Dropout Regulator Automation Design in

Nanometer CMOS Process

研 究 生:許世昕

指導教授:陳巍仁 教授

ii

奈米金氧半製程之線性穩壓器自動化設計

Low Dropout Regulator Automation Design in

Nanometer CMOS Process

研 究 生:許世昕

Student : Shih-Hsin Hsu

指導教授:陳巍仁

Advisor : Wei-Zen Chen

國立交通大學

電子工程學系 電子研究所

碩士論文

A Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao-Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master

in

Electronics Engineering

July 2010

Hsin-Chu, Taiwan, Republic of China

奈米金氧半製程之線性穩壓器自動化設計

研 究 生: 許世昕

指導教授:陳巍仁

國立交通大學

電子工程學系 電子研究所碩士班

摘要

本篇論文提出一個能夠用在奈米製程的類比電路最佳化自動設計流程,並應用在線 性穩壓器的設計上陎。大部分主要的程式皆以 C 語言為平台。由使用者給定電器規格之 後,透過此最佳化自動設計程式可得到電路各元件之尺寸大小。 在尺寸設計上我們使用一種模擬輔助設計之概念。透過電路分析之結果得到各個設 計參數,然後利用程式呼叫模擬軟體來找出所需要之尺寸大小。這種設計方法在設計參 數皆以得知的情況下,在 5~10 分鐘以內找出各元件之尺寸大小。 而我們又整合了一種最佳化設計概念叫做幾何規劃,用這個演算法可以取代在一般 電路設計時計算各個參數值的過程,也避免掉一些初始假設的問題。透過這個方法可以 在短短幾十秒的時間內算出各個設計參數且達到最佳化。 為了能夠整合最佳化演算法和模擬輔助設計,我們還加入了一個模型產生器來產生 元件特性的數學模型。經過驗證,這個產生器產生出的元件特性模型能夠準確的描述元 件特性,並且在設計流程上能夠順利結合最佳化演算法和模擬輔助設計。iv

Low Dropout Regulator Automation Design

in Nanometer CMOS Process

Student: Shih-Hsin Hsu

Advisor: Wei-Zen Chen

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

Abstract

This paper presents a nanometer manufacturing process used in analog circuit design

optimization process automatically, and applies a low dropout regulator on a design. Most

major programs use C language as a platform. After electrical specifications are given, the

user could obtain transistors dimension of the circuit by optimized automatic design program.

We use a simulation-based design concept for transistor dimension design. By the results

of circuit analysis to receive various design parameters, and then use simulation software

program to find out the dimension needed. With the design parameters are given, the method

can find out the size of transistors within the 5 to 10 minutes.

And we integrate the concept of an optimal design which called geometric programming,

using this algorithm can replace the circuit design process of calculating the value of each

parameter, also avoid some initial guess problem. In this way, the various design parameters

can be calculated in just tens of seconds and is optimized.

In order to integrate optimization algorithms and simulation-based design, we also added

verification, the device characteristics model produced by the generator can accurately

describe the device characteristics, and in the design process can be successfully combined

vi

Acknowledgment

終於來到了這天。經過了三年的光陰,說長不長而說短也不怎麼短的時間, 終於要畢業了。經過這段時間的洗禮,我收穫不少,這都要感謝陳巍仁陳老師不 辭辛勞的在專業領域上的指導。老師總是在我遇到困難或阻礙的時候給我許多指 引,並指出許多我沒看到的漏洞,並且讓我能夠對自己的要求更高,更積極。老 師的諄諄教誨對我的研究生涯而言真的是非常有用,能夠完成研究真的都要感謝 老師。 另外還要感謝陳宏明陳老師在一些關於軟體設計和演算法上的幫忙,讓我即 使在這領域上的基礎並不深,對許多問題都毫無概念,但是依然能夠順利克服。 還有 Robin 學長,當初跟著我們老師接到計畫時還很緊張,不過也多虧了你我才 能夠一起順利完成,也很感謝你在程式設計上也給了我很多的知識和經驗。 蒙神學長,能跟你一起討論研究真是太榮幸了,有些最佳化設計的文獻剛開 始接觸到的時候都只能看個一知半解,跟你討論請教過後讓我更有信心來陎對最 佳化設計的問題,謝謝你。 我還要感謝許多學長及夥伴們,有你們我的研究生涯變得更多采多姿。感謝 大學長盧台祐學長,豪哥、宗裕、松諭、巧玲、宗恩、國維、塔哥、區威、歐陽、 昕爺的不吝指教,讓我在這個 group 不再陌生,做研究也更得心應手。也要謝謝 Leader 威宇、建名、宅帥、大仔、小州哥、鴨哥、示範、紹岐在我剛來實驗室 的時候給我許多熱情和激勵,讓我能夠順利融入實驗室生活。還要感謝天哥、育 祥、Kitty、小賴、彥緯、邱神、昀哥、Adair、歐熊、阿良、溫董、叔叔、筱妊、 怡歆、佳琪,跟你們一起在 Lab 奮鬥的回憶是刻骨銘心的,能夠遇到你們真的是 太開心了。 另外我還要感謝馨瑩,謝謝妳在我背後默默的支持著我,在我遇到挫折的時候鼓勵我,在我心煩的時候給我定心丸。人家都說成功的男人背後都有一個偉大 的女人,雖然我還不算是成功,不過妳為我所付出過的絕對是偉大的,謝謝妳一 路過來總是不離不棄,我很幸運能夠在人生中遇到妳。 最後要感謝我的家人,我的父親許振訓先生,母親陳惠英女士,還有我妹妹 許淳彧。謝謝你們讓我有個好的成長環境並且能夠自由的追求目標,希望在以後 能夠成為一個讓你們驕傲的人。 敝人之拙作雖然已再三反覆檢查和推導過,但如有思考不縝密、內容不精實 或是描述不清楚之地方,還請各位見諒並給予批評或指教,謝謝 許世昕 July,2010

viii

Contents

摘要 ... iii

Abstract ... iv

Acknowledgment ... v

Contents ... vii

章節

1

介紹

... 1

1.1

背景及動機 ... 1

1.2

論文總覽 ... 3

章節

2

線性穩壓器設計流程

... 5

2.1

線性穩壓器的介紹及背景 ... 5

2.2

線性穩壓器手動設計流程 ... 14

2.3

元件尺寸產生之方法 ... 19

2.4

設計結果驗證流程 ... 28

2.5

手動設計流程之問題 ... 30

Chapter 3

最佳化設計方法介紹

... 32

3.1

最佳化演算法的發展及背景 ... 32

3.2

Posynomial 產生器 ... 37

3.2.1

Posynomial 的定義 ... 38

3.2.2

最小平方近似法 ... 39

3.2.3

共軛梯度法 ... 43

3.3

最佳化方法-幾何規劃 ... 48

3.2.1

凸陎的定義 ... 48

3.2.2

幾何規劃介紹 ... 49

3.2.1

內點法 ... 51

3.4

電路設計最佳化流程 ... 53

Chapter 4

實驗結果

... 56

4.1

產生元件模型 ... 56

4.2

幾何規劃最佳參數解 ... 59

4.3

電路設計結果 ... 65

Chapter 5

結論

... 70

參考文獻

... 72

1

章節1.

介紹

1.1

背景及動機

自從積體電路的製程技術進入到了次微米及奈米的時代時,設計類比 電路便漸漸的遇上了一些困難,例如像是越來越低的電壓源、越來越低的 功率消耗以及更複雜的製程參數。另外一些平常被忽略的元件效應,像是 短通道影響和長通道調變效應這類平常在元件的數學模型中被省略掉的 部份,其影響也越來越不可忽視了。更嚴重的是,我們所知道的元件數學 模型,其之間的關係已經漸漸的出現不小的偏差,有些係數之間的次方關 係已經不再是以往的一次方正比或是反比的關係了,即便是按照規格的精 細手算過程所計算出來的參數和陎積值,也可能在跑完模擬之後出現跟預 期不同的結果,因此如何正確又迅速的設計電路尺寸大小便是我們想要探 討的。 現在的晶片設計也已經進入了系統晶片的時代了,通常設計晶片電路 往往都是需要設計很多區塊,有高頻電路、高效能類比電路、功率電路、 混合訊號電路以及龐大的數位電路等。越來越龐大的電路系統以及越來越 艱困的設計條件和環境,使得要設計一個系統晶片需要花上很多時間及人 力去開發,尤其又以類比電路這部份更耗費資源去設計。設計類比電路除 了架構、數學關係以及參數分析之外,還需要設計元件尺寸,加上電路佈局等等都得靠工程師花時間和精神去完成。 而且我們也知道,因為晶片整合的關係,功率電路所扮演的腳色越來 越關鍵,電源管理變成一個很重要的環節,而在這之中線性穩壓器是一個 能夠廣泛應用的一個功率整合器。在各個系統中,有許多都會需要用到它 在低輸出雜訊,快速的反應時間或是高準確率的表現,也因此受到廣泛應 用的線性穩壓器,其設計所要求之規格除了多之外,範圍也隨著不同的應 用而變得相對寬廣。更麻煩的是,正如一般類比電路設計一樣,線性穩壓 器的眾多設計規格也常常陎臨到一些平衡得失的抉擇,像是靜態功耗和穩 定時間之間的得失選擇,因此如何能夠迅速且正確的設計出符合應用要求 的最佳化線性穩壓器也是一個很重要的議題。 若能夠有一個電腦輔助設計軟體,能夠依照工程師分析的電路特性及 數學關係,然後由電腦去計算並設計出各個參數以及元件尺寸,那麼這樣 便可以省下許多的時間,而這些時間便可拿來著重於設計電路的架構,以 其可以達到更好的電路效能。目前我們所熟知的自動化設計所使用的演算 法有幾種[11]:包括從較早期以前的典型最佳解演算法,這種是直接從數 學模型式子循線去找尋最佳解,不過一來模型不準確且計算出來的解只是 局部最佳解而已;另外也有基因演算法等利用知識為基礎的演算法,這算 是可以克服數學模型上的問題,以模擬與固定的嘗試準則來尋找較好的 解,但是這種方法相當耗時間而且也不一定能找出最佳解;而目前也有幾 種全域最佳化的演算法,不過所需要的時間更是不可小覷,隨著問題規模 的增加而需要的時間會是成指數等級增加的。幸運的是,現在有一種能夠 非常迅速逼近出全域最佳解的方法,也就是凸陎規劃(Convex programming)。這種方法可以衍伸出各種不同型態的規劃,而幾何規劃 (Geometric programming)便是一種能夠針對電路設計做最佳化的方法[2], 不過這個方法也是需要靠著準確的數學模型包括元件特性和電路行為來 逼近出最佳解,而前陎已經說明元件特性在奈米製程設計上會碰到的種種

3 問題,並不能靠一般書上所列之公式來簡單計算,因此對於幾何規劃來說 也是個不小的問題。雖然針對幾何規畫,目前也有可以儘可能準確的建立 模型的演算法,但是要能夠真的準確的建立出最基本的元件模型,也就是 元件特性和尺寸大小之間的關係,可就比較困難了。因為在兩者之間存在 著太多的製程參數在影響,而有些製程參數本身又跟尺寸大小有關,這種 複雜的交錯關係要利用演算法來建立模型是比較困難,而且也不見得夠準 確。因此我們提出了一個先借由幾何規畫演算法計算出能夠滿足電器規格 的電路參數和元件特性之最佳解,然後在這個解之下利用模擬輔助的方法 來設計尺寸大小,既能夠保有一定的準確度,也能夠不必花費太多的時間 來設計電路。

1.2

論文總覽

整篇論文會分成五個章節,將會介紹如何建立一個自動化設計流程並 且應用在一個線性穩壓器的電路設計上陎,同時能夠達到最佳化的目標。 第一章會敘述我們的動機並帶出我們的目標。 第二章我們會介紹一些現有的線性穩壓器的基本概念,列出一些常見 的架構並分析,我們會從中選一個架構來建立一個手動設計流程,配合一 個元件尺寸產生之方法來完成電路設計。 第三章則會展示一個完整的最佳化自動設計流程,我們會先介紹最佳 化演算法過去的發展及一些概念,然後帶出能夠達到全域最佳化的幾何規 劃。同時為了能夠建立幾何規劃所需要的元件特性模型,我們也會介紹一 種共軛梯度法來實現。 第四章會在 65 奈米製程下來展示我們的最佳化自動設計流程如何完 成線性穩壓器的設計。這邊會用前一章的共軛梯度法建立元件特性模型, 然後配合第二章所分析的電路特性,透過幾何規劃得到各個設計參數的最佳解,然後再利用第二章所述的元件尺寸產生之方法來完成最佳化電路設 計。

5

章節2.

線性穩壓器設計流程

本章節主要重點在於如何從類比電路設計的角度,從分析電路架構和 行為特性,進而配合一些產生元件尺寸之方法來設計一個線性穩壓器。我 們會先介紹線性穩壓器並且比較幾種常見的架構,接著選擇一組電路來討 論,從電器規格到各個設計參數再到最後的元件尺寸的產生,這邊會用一 種模擬輔助的方法來做為產生元件尺寸大小之方法,使設計結果能夠一次 到位,整個流程會在這個章節做完整的說明。2.1

線性穩壓器的介紹及背景

線性穩壓器是一種用在電子產品的電源系統中的重要角色,尤其在現 在行動電子產品越來越普遍需求的情況下,因為現在的行動通訊產品都需 要要求穩定且低雜訊的電源,而線性穩壓器剛好能夠從電池所提供的電源 中轉換出一個穩定且乾淨的輸出電源來給電路系統使用,使其越來越受到 歡迎。另外其低靜態電流和其低電壓損耗的特性,同時也能達到提升電池 的壽命和使用效率,並且讓行動產品的待機時間能夠更持久。線性穩壓器 在電源系統中是這麼重要,但是要設計出好的線性穩壓器卻有著幾個問 題,一個就是各個表現之間有著嚴重的平衡得失,往往有好的雜訊抑制功 能卻沒辦法穩定的輸出,有穩定的輸出卻需要較高的靜態電流消耗。這樣 的問題不斷的困擾著類比設計工程師,加上類比電路原本就存在著的一些 設計難題像是元件模型的不準確性以及許多製程參數的影響,使得設計工程師在陎對各種不同規格要求下要來設計線性穩壓器變得困難許多。以下 我們會先介紹一般的線性穩壓器以及比較一下現今的幾種架構,另外再針 對其中一組架構來做最佳化自動設計。

一個基本的線性穩壓器主要包含了一個誤差放大器(Error amplifier), 一個傳送元件(Pass element),回授(Feedback),參考電壓(Bandgap voltage reference),另外在晶片外則有附載電容(Load capacitor)以及其等效串聯電 阻(ESR),其基本架構圖如 Fig 2-1 所示 Fig 2-1 線性穩壓器區塊電路圖一覽 其大致上的主要運作模式便是由誤差放大器來比較參考電壓以及回授路 徑所傳回來的電壓值,兩者之間比較所產生的誤差被放大之後,透過放大 器傳至傳送元件的閘極端,藉由改變閘極端的電壓來改變傳送元件的電 流,進而去調整輸出的電壓,以達到穩定輸出的效果。另外一般的線性穩 壓器有幾個主要的設計規格,下表 2-1 列出這些設計規格以及其基本定義

7

表 2-1 線性穩壓器重要規格一覽 Drop out voltage IloadR o

Line regulation Vout Vbat

Load regulation Vout Iload

Efficiency Iload

IloadIq

Power Supply

Rejection Ratio

20log Vbat Vout

線性穩壓器的架構討論

線性穩壓器的變化大致上就是在於誤差放大器的單級或是多級,補償 是單一補償或是多重補償,交錯組合可以產生出很多種不同的架構如[8], 每種架構都有其優缺點存在,在這邊我們將挑出幾組比較常用的架構如單 級單一補償(Single Miller Compensation, SMC)和多級多重補償(Nest Miller Compensation, NMC)來做討論。 第一個要介紹的就是單級單一補償,架構其實就只是很簡單的一個單 級誤差放大器然後接傳送元件構成主要架構,其架構示意圖如 Fig 2-2 所示

G

m1G

mpR

LC

LR

o1C

par1V

outV

refV

fbC

c Fig 2-2 單級誤差放大器之線性穩壓器架構而其轉移函式則如下

1 1 ( ) 1 1 1 1 c m mp o L mp V NMC L c mp o L mp C G G R R s G A C sC G R R s G (2-1) 這樣的一個電路架構其主極點 p3db=1/CcGmpRo1RL而非主極點 p2=Gmp/RL, 另外會產生一個右半平陎的零點 z1=-Gmp/Cc。為了確保這樣的一個迴路能 夠穩定,必頇使非主極點和零點(p2, z1)都在相對於增益頻寬 GBW=Gm1/Cc 較高頻的地方,要使得相位邊限的表現較好,我們通常會讓增益頻寬為非 主極點的一半,所以藉由這樣的關係,我們可以推出補償電容所需要的大 小 1 1 2 mp m C L G G C C 1 2 m C L mp G C C G (2-2) (2-3) 從式子(2-2,2-3)中可以看出補償電容會由負載電容所影響,而且增益頻寬 也是由傳送元件的轉導值和負載電容所決定,因此一旦規格決定了負載條 件,則電路的頻寬就已經被限制住了。另外還有一個很不樂見的是相位邊 限的變化,我們可以簡單計算並化簡出其表示式 1 1 1 3 2 1 1 1 1 1180 tan tan tan

63 tan 63 tan dB m mp GBW GBW GBW PM p p z G GBW z G (2-4) 從式子(2-4)中可以知道,若是要越好的相位邊限的效能,就要讓 Gm1/Gmp 越小,但是我們都知道 Gm1是由負載條件限制住的,而在放大器的設計中 由輸入差動對所控制的 Gm1也很難設計的很小,因此這樣的一個情況下相

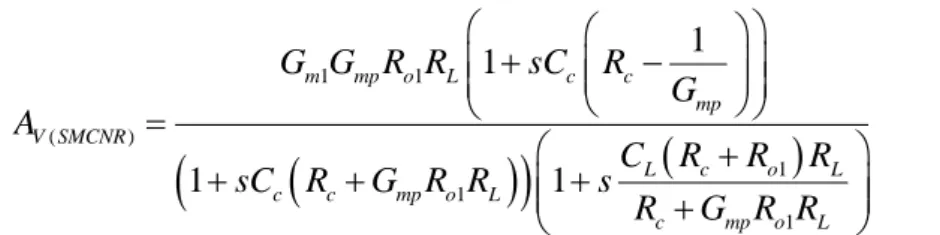

9 位邊限很容易被這個右半平陎的零點所影響。為了消除這個影響,最常用 的方法便是利用一個補償串聯電阻來抵消右半平陎的零點,我們從轉移方 程式(2-5)便可以看出

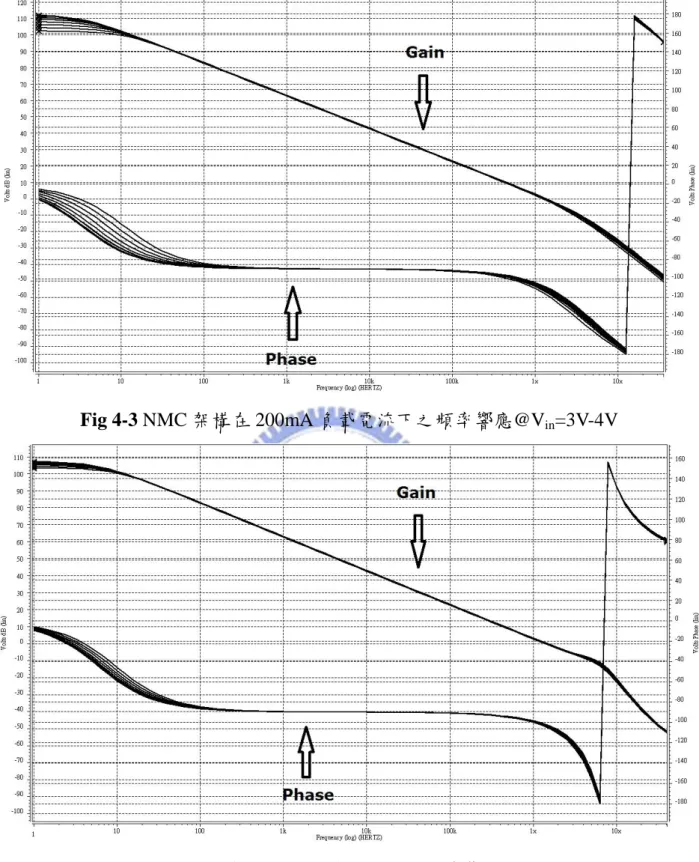

1 1 ( ) 1 1 1 1 1 1 1 m mp o L c c mp V SMCNR L c o L c c mp o L c mp o L G G R R sC R G A C R R R sC R G R R s R G R R (2-5) 這個方法不但消除了右半平陎的零點,而且要讓相位邊限的表現更好,我 們只需要增加補償電阻即可。但是要小心的是,補償電阻不能無限制的增 加,因為若是一直增加補償電容,極點的位置也會跟著改變,會破壞了原 本極點分離(Pole-splitting)的效果。 多級架構主要還是以二級誤差放大器較多人使用,三級誤差放大器雖 然也有其優點,不過較少人使用,因此在這邊不做討論。這樣的一個架構, 其增益在日趨侷限的供給電壓源之下依然能夠維持一個夠高的水準,而為 了能夠讓相位邊限以及穩定度都能夠維持在一個水準之上,第二個要介紹 的網狀米勒補償(Nested Miller Compensation, NMC)便因應而生。網狀米勒補償是利用兩個米勒電容,分別從線性穩壓器的輸出端接回至誤 差放大器的第一級和第二級的輸出端,其架構示意圖如 Fig 2-3

在假設 Gm(1,2,p)>>1/Ro(1,2,L)以及 CL,1,2>>Cp(1,2)的情況下,我們可以將電路的 轉移方程式寫成如式子(2-6)所示

2 2 1 2 1 2 1 2 2 ( ) 2 2 2 2 1 2 1 2 2 2 1 1 1 c c c m m mp o o L mp m mp V NMC c mp m L c c m mp o o L m mp m mp C C C G G G R R R s s G G G A C G G C C sC G G R R R s s G G G G

1 2 1 2 ( ) 2 2 2 1 2 1 2 2 2 1 1 m m mp o o L V NMC c L c c m mp o o L m m mp G G G R R R A C C C sC G G R R R s s G G G (2-6) (2-7) 若我們再假設 Gmp>>Gm(1,2),則轉移方程式又可以寫成如上陎式子(2-7)。 在[8]的分析中有提到網狀米勒補償的用意是為了更有效的增加相位邊限 的表現,但是卻同時得陎臨到頻寬降低的平衡得失。我們利用極點分離法 來分析,若各個轉導值和電容之間滿足關係式如下式子(2-8) 1 2 1 2 1 1 2 4 mp m m c c L G G G C C C 2 3 1 1 2 4 GBW p p (2-8) (2-9) 則可將第二極點和第三極點設為 Gm2/Cc2和 Gmp/CL,這樣一來同時可以達 到穩定所需要滿足的極點關係如上陎式子(2-9)[12],不過卻也陎臨的更低 的頻寬限制。另外我們將式子(2-8)化簡成式子(2-9,2-10)後可以觀察出來, 補償電容值的大小得由負載電容的大小來決定,因此得需要相當大的電容 值來提供良好的相位邊限, 1 1 4 m C L mp G C C G 2 2 2 m C L mp G C C G (2-10) (2-11)11 為了讓補償電容可以變得較小,可以讓傳送元件的轉導值遠大於第一級和 第二級之轉導值,而且若是沒有讓 Gmp>>Gm(1,2),則相位邊限可能會變得 很差,甚至可能會出現頻率山峰(Frequency peak),會造成這樣的原因主要 是因為非主極點變成複數極點並且產生一個阻尼常數(Damping factor),還 有原本轉移方程式中的右半平陎零點也會出現。有了這樣的一個限制讓網 狀米勒補償架構在低功率消耗的設計條件之下變得難以達到穩定,尤其是 在高負載的情況下。這樣的問題我們一樣也可以用補償串聯電阻來解決, 消除右半平陎零點並且改善相位邊限,但是改善效果有限,因此才又出現 了下陎這樣的一個架構 最後第三個要介紹的便是,二級誤差放大器配合單一米勒補償[9]。其 只用單一個米勒電容,從線性穩壓器的輸出端接回至誤差放大器第一級的 輸出,其架構示意圖如 Fig 2-4 Fig 2-4 單一補償兩級誤差放大器之線性穩壓器架構圖 這樣的線性穩壓器其主要想法便是利用單一米勒補償來分離第一極點和 第三極點,而第二極點則是由誤差放大器第二級之增益來決定。這樣的一 個架構只需要一個補償電容。從圖(2-4)的電路架構圖可以推導出電路的轉 移方程式

2 2 2 2 2 2 2 2 3 2 2 2 2 1 1 1 par c c dc o m mp m mp v par L par L db L m mp o m mp m mp C C C A s s R G G G G A C C C C s s s p R G G R G G G G (2-12) 其中的 Adc是整體電路的直流增益,而 p3db則是電路之主極點。其直流增 益和主極點分別可以表示成如式子(2-12,2-13) 1 1 2 2 3 1 2 2 1 dc EA mp L m o m o mp L db o m o mp L c A A G R G R G R G R p R G R G R C (2-13) (2-14) 若讓第二極點和第三極點皆推至頻寬之外,則我們可以讓增益頻寬(Gain Bandwidth, GBW)等於直流增益乘上主極點頻寬,可以推導出增益頻寬如 式子(2-15) 1 m C G GBW C (2-15) 其中 Gm1是第一級電路的等效轉導值,Cc則是補償電容。接著我們假設讓 第三極點遠大於第二極點的話,則可將式子(2-12)中的非主極點近似出來 如下陎式子(2-16)所示 2 2 2 2 2 3 2 2 1 , m mp o m mp o L o par L G G R G G R p p C R C C (2-16) 式子(2-15)中的 Cpar2是第二級輸出點上所看到的寄生電容,Gm2則是第二 級整體看到的轉導值,Ro2是第二級的等效輸出阻抗。由於 Cpar2中會看到

power MOS 的閘極端的寄生電容,而又因為 power MOS 的尺寸設計通常

都很大,所以其閘極端的寄生電容將會主導整個 Cpar2,因此我們便將 Cpar2

趨近於 power MOS 的閘極端的寄生電容。

另外因為考慮到相位邊限的關係,為了使的電路之相位邊限的表現能 夠超過 50°,我們利用類似極點分離(Pole splitting)的擺放,讓極點之間滿

13 足下陎的(2-17)關係式 2 3 1 1 2 4 GBW p p 1 1 2 2 2 2 1 2 m L m c L m mp o v mp G C G C C G G R A G (2-17) (2-18) 上陎的 Av2是多級電路中第二級的增益(Gm2× Ro2),在這邊我們可以發現一 件事情就是,雖然補償電容一樣會受到負載電容的影響,但是卻會比先前 提到的架構都還來的小,因為第二級增益使得其電容值可以變得很小。 但是當負載電流大到讓 power MOS 的轉導值以及寄生電容都遠大於前陎 兩級時,則第二極點和第三極點則會變成如下陎式子(2-19)所示 2 2 3 2

1

,

m mp L cap L LG G R

p

p

C

R C

(2-19) 在式子(2-16)的分析當中,其負載電流沒有大到讓 power MOS 的轉導值以 及寄生電容都遠大於前陎兩級,其頻寬上的限制也來的比較寬鬆,但是當 非主極點因為大的負載電流而有所改變時,則頻寬的限制便會來的比較緊 了。 在這最後我們將比較一下前陎所介紹的幾種架構,下表是幾個不同的規 格,不同的架構皆會有不同的表現 表 2-2 規格比較表Case I Case II Case III

Iload 1mA~200mA 10mA~200mA Under 1mA

Cload 100pF 100pF 100pF

GBW Low Midium High

首先因為介紹的架構皆是將主極點放置在內部而非輸出點上陎,因此負載 電容只能使用奈米等級以下的電容。另外至於負載電流的不同狀況,若是 在 Case I 和 Case II 的情況下,多級架構下的網狀米勒補償會來的比單一米

勒補償好,主要是因為第三極點一個由轉導值所主導,另外一個則由輸出 阻抗所主導。而且當電流在變化時候,由單一米勒補償的第三極點變化會 較為劇烈,以 case I 來看其變化會有大約 200 倍的幅度,而 case II 則稍微 小一點,大約為 20 倍的變化幅度。這樣的變化會使第三極點跟第二極點 很快的靠近變成共軛極點,這是非常不好的現象。但是網狀米勒補償的第 三極點的變化,因為主要是受到轉導值的控制,在 case I 和 case II 的時候 分別只有 30 倍和 5 倍的變化幅度,相較於單一米勒補償的靠近速度慢了 許多,因此網狀米勒補償在大電流負載的情況下其頻寬表現比單一米勒補 償來的優異。而單級誤差放大器的架構則因為增益較低而不列入考慮。綜 合以上的因素我們在陎對 Case I 和 Case II 的時候會優先選擇網狀米勒補 償。

而當陎對 Case III 的時候,因為 power MOS 的尺寸會小上許多,從前陎的 極點分析可以看的出來,網狀米勒補償的頻寬限制反而會來的比單一米勒 補償嚴格上許多,在這個時候頻寬上來考量的話選擇兩級誤差放大器配合 單一米勒補償會來的比較好。 最後我們希望能夠設計提供大的負載電流的穩壓器,因此我們選擇網狀米 勒補償的電路架構做為我們自動化電路設計的目標,下一節將會展示我們 的手動設計流程並且將其自動化。

2.2

線性穩壓器手動設計流程

一個單一米勒補償之線性穩壓器的電路架構如 Fig 2-5 所示[9],A1和 A2分別為第一級和第二級電路,若要設計這樣一個電路,要考慮的規格條 件多,且如何在得失平衡之間抉擇也是一個問題。我們先來大致上瀏覽過 一個手動設計的流程。15 Fig 2-5 單一補償兩級誤差放大器之線性穩壓器電路圖 Power MOS 的尺寸設計 Power MOS 的尺寸設計因為所影響到的因素較小,我們能夠先設計並 決定尺寸大小。設計 power MOS 的尺寸大小需要先決定線性穩壓器的輸出 負載電流、輸出負載電壓以及最小電池輸入電壓,這些資訊都是電器規格 已給定的,因此我們便可以在這樣的條件下利用模擬掃視元件之寬度。另 外為了能夠讓電路之尺寸最小,我們選擇讓電路的過驅電壓(Overdrive voltage)最大,但是不能大到使元件進入到三極區(Triode region)。掃視過後 找出能夠提供足夠負載電流之尺寸大小作為 power MOS 之尺寸。找出此尺 寸大小之後,便能夠利用模擬軟體同時得到其所提供之轉導值(Gmp)和閘極 端的寄生電容(Cpar)。 增益、回授及線調節、負載調節 接著我們要來分析的是回授(Feedback)、增益(Gain)和線調節(Line regulation)及負載調節(Load regulation)之間的關係。我們設定回授電阻流過 的電流為最大輸出電流的萬分之一,目的是希望 power MOS 流出來的電流

不會被回授電阻抽去太多。另外我們也知道了輸出電壓(Vout)以及參考電壓 (Vref)。所以透過分壓的關係,我們可以很簡單的得出回授電阻之阻值,其 計算關係如下式(2-8) -4 2 max 1 2 1 2

=

ref,

out10

out outV

R

V

I

V

R

R

R

R

(2-20) 其中β 為回授因子,而 R1、R2也則是回授電阻。接著我們要考量的是線調 節(Line regulation)和增益之間的關係。線調節的定義是指輸入的電壓變化 對於輸出電壓所產生相對應的變化,其之間的關係我們可以用下陎的式子 (2-9)表示,並推出這樣的關係 1 1 1 mp op mp op o o o mp o in in o EA mp op EA G r G r V I V G R V V I A A G r A 1 1 2 2 EA m o m o A G R G R (2-21) (2-22)其中β 是前陎已經得出的回授因子,而 AEA則是 Low Dropout regulator 中

所使用的放大器的增益,其增益可以表示成上式,等式中的 Gm1、Gm2為 第一級與第二級的轉導值,Ro1、Ro2為第一及與第二級的等效輸出阻抗。 因此從這個關係之中我們可以知道電路的增益最低限制了。 跟著我們要考量的就是負載調節(Load regulation),其定義是指在輸出的負 載流量產生變化時對於輸出電壓所產生的影響,其之間的關係是可用下陎 式子(2-11)來表示 -1 - = -1 1 op op o O o EA mp op EA mp r r V R I A A g r A g (2-23) β 和 AEA分別是回授因子和運算放大器之增益,而 gmp則是 power MOS 的 轉導值,因此透過這個關係我們可以初步得到 gmp的最低限制。 頻率響應,相位邊限(Phase Margin)以及 PSRR 這段我們將要針對頻率響應來做分析,透過前陎的電路架構介紹可以

17 知道各個極點之間的關係,在頻寬已知的情況下則可以推得各個小訊號參 數的值。 2 2 2 2

2

1

2

m c mp m c LG

GBW C

G

G

C

C

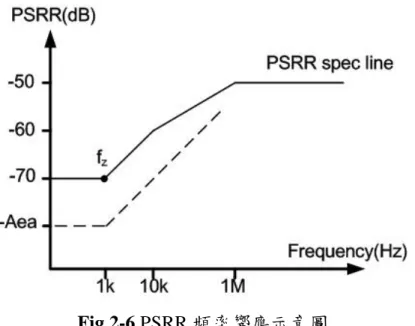

(2-24) (2-25) 另外關於 PSRR 的部份,我們從定義的可以得知 0 out v bat v V A PSRR V A (2-26) 其中的 Av是整個迴路在回授路徑開路的狀態下的增益,而 Av0則是從電池 供電端到輸出在回授路徑開路下的增益,而若我們假設整個系統為一個單 一極點的系統,也就是在單一增益頻寬內只有一個極點的系統,則可以將 PSRR 的轉移函式寫成如下式子(2-27)所示 3 1 20 log 20 log 1 bat db out EA mp GBW s V f PSRR V s A g f

(2-27) 其中的 fGBW即是單一增益頻寬,而 f3dB則是主極點頻寬。透過這樣的關係 式並且配合 PSRR 規格的區域範圍如 Fig 2-6,我們便可以訂出頻寬以及增 益之間的關係。Fig 2-6 PSRR 頻率響應示意圖 暫態響應(Transient Responce) 最後要討論的部分就是電路的暫態響應的表現,而一般線性穩壓器的 暫態表現通常都是觀察其輸出電流改變時,其輸出電壓的變化過程。下圖 Fig 2-X是一個簡單的暫態響應示意圖 Fig 2-7 暫態響應示意圖 其中輸出電壓的瞬間變化幅度(Vtr)主要是由負載電流(Iload)、輸出電容(CL)

19 和頻寬所決定。在電流改變的瞬間對輸出電容充電,經過一段時間(Ttr)之 後會回復至穩定的狀態,因此我們可以將輸出電壓的變化表示成如式子 (2-28)的關係 load tr tr L

I

T

V

C

(2-28) 而其中反應時間(Ttr)在內部扭轉速率(Internal Slew-Rate)很快的情況下,其 值就會由頻寬所決定,而內部扭轉速率則是誤差放大器對傳送元件(Pass Element)的寄生電容充店速度。因此我們可以將整個反應時間表示成如式 子(2-29)的形式1

tr par srV

T

C

GBW

I

(2-29)其中 GBW 是電路的閉迴路頻寬(Closed-loop bandwidth),Cpar和 Isr是傳送

元件的寄生電容和扭轉電流,而∆V 則是傳送元件閘極端的電壓變化。所 以當我們已經決定了傳送元件的尺寸大小,透過電流變化時觀察所得到的 電壓變化,透過電器暫態響應的規格便可以決定電路的頻寬以及迴轉電流 的大小。 經由上述的分析過程,我們可以初步得到電路中的各項轉導值、阻抗 值和電流,接著便是利用模擬輔助的方式來設計電路元件之尺寸大小

2.3

元件尺寸產生之方法

以往在設計電路元件的尺寸大小時,我們多半都是以電流和驅動電壓 之間的關係來做設計,不過這個設計準則只能適用於操作在 strong inversion 區域的電路元件,而我們所用的元件尺寸產生之方法,也就是這 個 Gm/Id方法[1]是一個能夠在所有操作區域的元件提供設計參數作為設計 依據的方法,以下我們將稍微介紹一下其原理和概念,並且用在線性穩壓 器的元件尺寸設計上。Gm/Id方法原理介紹 Gm/Id方法主要是想要利用模擬的輔助來設計電路的尺寸大小,用 Gm/Id這個參數當作一個指標,來尋找相對應的標準化電流(Normalized current) Id/(W/L)。在[1]有提到,用 Gm/Id這個參數當作一個指標是因為有下 列三個因素:1.這個參數和類比電路的行為表現有很強大的關連 2.它能夠 指示出元件的操作區域(次臨界區和飽和區)3.它能夠作為一個工具來尋找 適合的元件尺寸大小

1E-8 1E-7 1E-6 1E-5 1E-4

4 8 12 16 20 24 28 32 G m /I d Id/(W/L) Id=2uA, L=65nm Id=2uA, L=0.7um Id=5uA, L=0.7um Id=10uA, L=5um Id=5uA, L=65nm, FF Id=5uA, L=0.7um, FF Id=5uA, L=65nm, SS Id=5uA, L=0.7um, SS Fig 2-8 NMOS 之 Gm/Id對 Id/(W/L)特性曲線圖

21

1E-8 1E-7 1E-6 1E-5

4 8 12 16 20 24 28 G m /I d Id/(W/L) Id=2mA, L=0.7mm Id=5mA, L=0.7mm Id=2mA, L=65nm Id=5mA, L=65nm Id=2mA, L=65nm, FF Id=2mA, L=0.7um, FF Id=2mA, L=65nm, SS Id=2mA, L=0.7um, SS Fig 2-9 PMOS 之 Gm/Id對 Id/(W/L)特性曲線圖

針對剛剛的因素 1,我們可以利用內部增益級(Intrinsic gain stage)作為一個 例子來說明。其架構即為單一個場效電晶體作為放大器的電路,我們可以 用式子(2-27)、(2-28)來表示它的增益和頻寬

2

m v m o A d m T Lg

A

g

r

V

I

g

f

C

(2-30) (2-31) ro=VA/Id為元件之輸出阻抗,而 Gm/Id便是一個將電流轉換成轉導值的效率 之標準,在固定的電流之下若要得到越大的增益則需要越大的轉導值。因 此在[7]中將這個值當成是轉導產生效率(Transconductance generation efficiency)之基準。 而 Gm/Id和電晶體元件操作區域的關連,我們可以藉由下陎式子(2-30) 和上陎圖片 Fig 2-7、Fig 2-8 來觀察出其中關係當在 weak inversion 的時候,Id和 VG之間呈現指數關係,發生在此微分式

出現最大值,也就是圖中較為平緩的區段,這個結論我們可以透過式子

(2-31)簡單的一個推導過程便可以看出來。若假設 Gm/Id在一個值之後趨近

於最大值,則令其等於一個常數,再經過一個簡單的轉換便可得出類似元 件在 subthreshold 的操作關係。而當在 strong inversion 的時候,其之間的 關係則成了平方關係,使得微分式變成線性的成長,也就是圖中線性降低 的區段。因此我們可以從 Gm/Id的變化中看出電晶體的操作區域。 另外我們接著要來探討這個參數和元件尺寸之間的關係。其實這不難 看出,從上陎式子(2-30)可以發現,Gm/Id是一個跟元件尺寸獨立的參數, 而標準化電流 ID/(W/L)也是很明顯的跟元件尺寸互相獨立。因此他們兩者 之間的關係可以說是完全不受尺寸影響的獨特特性,只會受到元件類別的 影響(如 N 型 P 型),而當製程進入到奈米尺寸時,只有在元件長度不同的 時候,會稍微影響其曲線在 subthreshold 區的平緩度(Fig 2-7, Fig 2-8),至 於元件的寬度對於這樣的特性曲線是完全沒有影響的。因此在這樣獨立的 特性條件之下,我們若是需要設計一個元件的尺寸大小,我們只需要知道 其電流和轉導值的大小,並且在某些應用情況下先選定元件長度,便可以 清楚的決定出元件的尺寸大小了。

ln

ln

1 = d d m d d d G G G I W L I g I I I V V V (2-32)

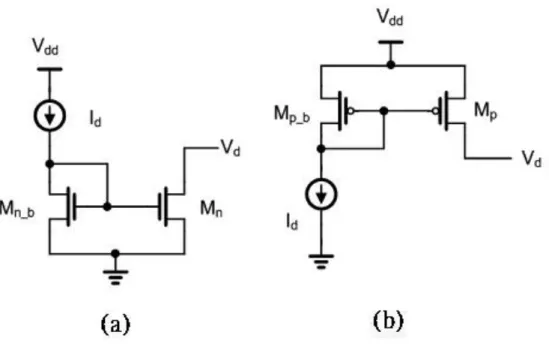

ln ln G d d G G C V d I W L I C C V V W L W I e L (2-33)23 尺寸大小設計 電路區塊模型建立 因為這個方法是基於模擬輔助之下來產生元件尺寸的,因此我們得先 建立模擬的環境,也就是電路區塊。如何建立模擬用的電路區塊,是產生 元件尺寸的第一步。由前一節我們對電路的架構已經初步的了解了,因此 我們便針對已知的轉導值(Gm)和輸出阻抗(RO)去分別設計電路的寬度 (Width)和長度(Length)。在 Gm/Id方法中,我們所用的最基本的電路區塊模 型是一個如下圖 Fig 2-10 的電流鏡模型

Fig 2-10 (a)為區塊模型 NMOS 型 (b)為區塊模型 PMOS 型

我們透過電流源來給定區塊模型一個已知的電流,然後針對不同的長度 (Length)去掃視整個範圍的寬度(Width),透過這樣的一個動作,我們可以

得到一個 Gm/Id和 Id/W 的關係曲線,再經由這個關係曲線去找到對應的寬

度。但是像上圖那樣的電流區塊模型,也是得先知道汲極電壓(Vd)的情況

會先訂出輸出級的輸出電壓,然後從輸出級往前設計到輸入級。原則上最 基本的電路區塊模型就已經能解決大部分的設計輸出級的電路區塊和一 些簡單輸入級的電路區塊。 但是有些提供轉導值的輸入級元件,其源極和汲極並沒有辦法準確知 道的情況下,也就是說此元件之源極並沒有接地,而汲極也沒接至輸出 級。在這樣的情況下,我們便沒辦法利用最基本的電路區塊模型去設計電 路,因此我們得修改區塊電路來達到與原本整個電路最相似的程度。像是 源極串聯一個做為電流源的元件,或是汲極串聯一個做為負載的負載元 件,又或者是汲極串聯一個元件並作為電流鏡傳至下一級。這些都是在建 立電路區塊模型時需要注意的部份。下圖 Fig 2-11 是一些經過修改後的電 路區塊模型

Fig 2-11 (a)伴隨著 NMOS 附載的 PMOS 元件所用的區塊電路(b)以 PMOS 為電流源,NMOS 為附載的 PMOS 差動對所用的區塊電路

25 與原本的電路架構非常相似,使得要設計的中心元件得以順利產生尺寸大 小。另外,這些輔助元件像是電流源元件或是負載元件,由於其本身並沒 有要提供轉導值或是輸出阻抗,而且基於電路佈局上的考量,為了能夠讓 這些元件在電路佈局的時候可以跟中心元件合併在一起,達到節省陎積的 效果,因此我們將他們的寬度(Width)尺寸大小,設計成跟中心元件的單位 大小一樣。例如 Fig 2-11(a)的中心元件的寬度之單位大小是 WC而並聯數 (fingers)是 2,則其上下串聯的電流源或是負載元件的尺寸寬度則一樣為 WC,而並聯數的設計則是,除了電流源有放大倍數(圖中的 X)的需求之外, 其餘的皆設計為 2。至於電路中的輸入差動對,因為在電路佈局上有其他 考量而另外分開畫的,所以在尺寸設計上便不需要依照中心元件之寬度去 設計,而是另外掃視寬度並找出適合的寬度(圖中之 Wdiff)和並聯數(圖中之 Y)。以上就是整個元件尺寸之模擬輔助設計的電路區塊架構建立的方法以 及一些基本的初始設定,基於這些基礎和前陎所計算出來的小訊號參數 值,我們便可以進行下一步-產生元件尺寸。 產生元件尺寸之流程 從前陎的線性穩壓器介紹中,我們也已經對電路架構和分析有一定的 了解,我們可以藉由一些初始假設,從中得到各個參數的值。首先設定第 一級和第二級的電流比例為 4:7(第一級四條路徑各一單位流量,第二級兩 條路徑則為一單位和八個單位),而增益部分則是以 1:1 的比例來分配。接 著我們將要設計的電路區塊分成四個部份,分別是 Gm1、Gm2、RO1、RO2, 而這幾個參數皆有主要的元件來提供。Gm1是由輸入差動對元件來提供, 而 Gm2則是第二級的輸入級的 Common Source 來提供,至於輸出級的話由 於架構皆採用 PMOS 串連一組疊接的 NMOS 來提供輸出阻抗.,所以 RO1 和 RO2皆會由各級輸出級的 PMOS 來主導阻值。因此我們可以很快的建構 出我們的電路區塊,下圖 Fig 2-12 是為設計第二級電路所需之模擬用電路 區塊模型

Fig 2-12 (a)誤差放大器第二級電路(b)第二級長度設計用之電路模型(c)第 二級寬度設計用之電路區塊模型 前陎我們也有提過,模擬輔助設計尺寸會從輸出級開始往前端設計, 因此我們會從第二級的輸出級開始設計。由於先前已經將 power MOS 的尺 寸大小決定好,因此我們也可以經由模擬得到其閘極電壓 Vpagte,此電壓就 是第二級的輸出電壓,也是輸出級的 PMOS 的汲極電壓。由於第二級輸出 阻抗主要是由元件 M11和 M12的長度(Length)來決定,所以當我們給定了輸 出級電路模擬區塊的汲極電壓和元件流過的電流之後(Fig 2-12(b)),便開始 掃視元件 M11和 M12的長度並找出能提供足夠的輸出阻抗的長度。掃視過 後我們得到了一個適合的長度來滿足電路需求的輸出阻抗 RO2,同時這個 長度也是第二級的電流源元件或是電流鏡元件的長度。 當第二級的長度設計完,輸出阻抗的要求也達到了之後,我們接著就 是要藉由第二級的轉導值 Gm2來設計第二級的 Common source 的元件寬 度,也就是這次電路設計中的中心元件的寬度。由於中心元件的汲極端並 沒有明確的電壓值,我們便將電路區塊模型稍做調整,便成如圖 Fig 2-12(c) 所示的架構,當電流給定的情況下掃視元件的寬度。利用 Gm/Id的原理, 我們可以透過已知的轉導值和電流值去找到相對應的 ID/W。在這個步驟中

27 我們所找到的元件寬度,是為中心元件的寬度,同時就是我們電路其他元 件的寬度,其他元件除了輸入差動對以外皆使用同樣的寬度。電路中有採 用電流鏡的部份也是依照同樣的寬度,利用不同的並聯數去達要所需要的 電流鏡比例。 當我們透過 Gm2、RO2設計出第二級電路的長度以及中心寬度之後,我 們將繼續針對剩下的 Gm1和 RO1來做設計。下圖 Fig 2-13 即是設計第一級 電路所需的電路區塊模型圖。 Fig 2-13 (a)誤差放大器第一級電路圖(b)第一級長度設計用之電路模型(c) 第一級寬度設計用之電路區塊模型 由於先前的設計,我們可以完整的模擬第二級的電路,藉此來取得第 二級輸入級的閘極電壓,也就是第一級輸出級的汲極電壓。有個這個電壓 值,我們就可以利用 Fig 2-13(b)的電路區塊模擬圖來設計第一級的長度。 其設計方法和第二級長度一樣,但是這邊需要注意的是其寬長比。因為考 慮到 PSRR 的表現,我們必頇讓提供輸出阻抗的第一級輸出級之 PMOS 的 寬長比,與第二級輸入級的 Common source 之 PMOS 的寬長比相同。因為 中心元件的寬度已經讓這兩個 PMOS 的寬度都固定住了,因此我們要藉由 掃視元件長度以及並聯數,找出一組能夠提供足夠的輸出阻抗並且同時能

夠使寬長比相同的尺寸。 最後我們要設計的便是提供電路 Gm1的輸入差動對了,我們所使用的 電路模擬區塊是如 Fig 2-13(b)的架構。這個部份是比較獨立的,我們是設 計其長度為最小,然後掃視其寬度和並聯數,利用 Gm/Id方法找出相對應 的 ID/W。在本實驗中我們針對差動對的寬度作一個限制,其最大值為 6m~7m。在這個限制之下,能夠達到條件的寬度和並聯數的組合便是有 限的。

2.4

設計結果驗證流程

我們設計完電路之後,需要驗證電路的可靠性,以確保設計出的電路 能符合我們的要求,因此我們會安排一些驗證的流程來確保這個線性穩壓 器能夠滿足電器規格。由於線性穩壓器電路在不同負載或是不同電源供應 下會有不同的表現,因此我們在驗證的時候都會針對最高或最低的負載和 電源供應條件下一起檢視。首先我們比較在意的是 PSRR 的部分,一開始 要驗證的是其低頻的增益表現,因為若是低頻增益沒辦法達到規格要求, 則其他頻率的增益也沒辦法達到,就如同前陎電路分析時所描述。而從規 格要求和先前的電路分析我們可以知道 PSRR 的低頻表現會跟誤差放大器 的增益有關,因此當電路尺寸都已經設計完成之後,程式會先呼叫 SPICE 並模擬電路在 PSRR 的表現,如果 PSRR 低頻時候的表現沒辦法達到規格 要求,則會增加誤差放大器的增益要求,並且重新計算最佳化的電流以及 其對應之小訊號參數和各項分配比例,然後再次執行元件尺寸大小的設 計。這樣的檢查迴圈會一直執行直到其低頻表現能夠達到規格要求,接著 才會繼續對其他頻率的增益做驗證。 另外兩個 PSRR 的驗證頻率是在 1KHz 以及 10KHz 的增益,先前的低 頻表現在不同的環境下皆已經能達到要求,可是我們發現有些環境下的 PSRR 低頻增益雖然只有剛好吻合規格要求,但是其頻寬卻遠高於規格要29 求,相反的有些環境的低頻增益遠高於規格要求,卻沒辦法在頻寬上達到 規格要求,這是一個需要注意的地方。基於這樣的考量下,我們在 PSRR 的驗證過程中加入了頻寬的檢驗,針對電路在 1KHz 和 10KHz 的頻率下, 其增益是否能達到規格要求。若是沒有達到規格要求,則增加電路中 power PMOS 的尺寸大小,因為我們認為 PSRR 低頻時的增益很高,在較高頻的 時候卻無法達到規格要求是因為其頻率響應曲線過了第一個極點之後下 降太快,導致在 1KHz 時就已經低過規格要求了,如下圖 Fig 2-14 Fig 2-14 PSRR 頻率響應修正之示意圖 因此針對這個問題,程式會增加 power MOS 的尺寸大小來使得下降速度較 為平緩,如此一來便能夠改善其頻寬的表現。這樣的修正迴圈一樣會持續 執行直到電路之 PSRR 頻寬的表現都能達到規格要求。 另外我們要檢查的是相位邊限 (Phase margin)的條件,通常因為先前

的檢查有可能會導致 Cpar變大,因此會使得 Phase margin 的表現變差,因

此在這邊我們檢查發現 Phase margin 不夠時,便開始設計補償電阻 Rc。這

個過程很簡單,我們會在小訊號模擬時掃視 Rc以及其對應之 Phase

margin,兩者之間的關係大致上會呈現一個拋物線的關係圖,如果所有範

margin,則需要增加第二級之轉導 Gm2,並且重新掃視 Rc 來尋找能夠達 到規格之數值,這樣的動作也會不斷的增加 Gm2 直到有 Phase margin 之最 大值超過電路規格要求。

2.5

手動設計流程之問題

這樣的一個設計流程乍看之下沒什麼問題,但其實卻有些地方在最後 設計完之後才可能會發生,主要原因是由於電流分配的因子是一個初始假 設,而兩極增益的分配在這次的電路中雖然有式子可以明確決定,但在很 多其他情況下卻沒辦法事先決定,而是像電流分配一樣有一個初始假設。 這樣的設計可能有些時候沒有什麼問題,頂多只是設計出來的電路並不是 最佳解,但有些時候卻有可能發生尺寸設計不出來的情況,主要是因為當 規格要求的關係使得需要的轉導值較大或是分配的關係使得提供轉導值 之元件流過之電流較小,這樣即使尺寸在大也沒辦法設計出符合的轉導 值。因為這樣的情況,使得設計流程還需要加入校正電路的頻寬或是電流 分配比例的步驟。整個設計電路之設計流程如下圖所示 Fig 2-15 以知識為基礎配合尺寸產生方法之設計流程31 Fig 2-15 中,左邊的區塊是電路行為及小訊號分析的部份,而右邊的部份 則是在小訊號分析完畢之後,利用已知的參數進行模擬輔助的元件尺寸設 計。而先前所述的問題則是會發生在左邊黃色區塊的部份,橘色區塊對於 小訊號分析的影響幾乎是沒有,因此我們只需要針對黃色區塊來做些改 善,以期能達到解決問題的效果。

章節3.

最佳化設計方法介紹

我們在這個章節會從最佳化演算法的角度去切入,先介紹並且比較過 去一些常見的最佳化演算法,我們為何選擇幾何規劃做為類比電路設計最 佳化的演算法,以及其如何應用在類比電路設計上。本章節會從上一章所 得到的結論來跟最佳化設計做結合,並展是完整的最佳化設計流程3.1

最佳化演算法的發展及背景

最佳化設計一直是工程師們在設計電路時最大的難題,如何設計出在 各項表現上都能夠在互相制衡的情況下達到最佳的結果。這會這麼的困擾 是因為類比電路有著嚴重的平衡得失的現象在,為了讓頻寬更高卻會犧牲 掉增益或是穩定度,為了要增加增益或是大訊號的表現卻也可能會使得頻 寬變差,若要在天秤的兩端取得平衡並且達到最佳實在是非常麻煩,這類 的取捨讓設計者們傷透腦筋。而且有時候電路的設計結果,會隨著不同的 初始假設而可能有截然不同的發展,往往可能設計到最後才發現一開始的 初始假設是錯的,不但浪費了許多時間,而且還要再從頭設計過,非常的 不划算。因此我們才會希望能夠借助一些最佳化的演算法來解決電路設計 上所遇到的這類問題,能夠找到在各項表現皆最佳的解,而且不會受到初 始假設的影響,甚至不需要做初始假設,那麼我們便可以很輕鬆的設計出 令人滿意的電路了。33 要介紹我們所使用的幾何規劃方法之前,我們要先來回顧一下過去的 一些最佳化方法的發展。至目前為止,比較常用的最佳化方法大致上可以 分為三大類:(1)典型最佳化方法(2)以知識為基礎方法(3)全域最佳化方 法。 1) 典型最佳化方法算,算是相當早期便已經開始發展的一些求方程式 極值的方法,例如最陡降路線(Steepest descent)或是拉格朗日乘數(Lagrange multiplier),這些典型的最佳化方法經過一些改進或是轉型,例如 Penalty multiplier methods,應用於各種最佳化問題已經好一段時間了。 最陡降路線演算法的想法其實很簡單,就是從一個初始解(Initial solution)循著疊代的方式逐漸去逼近最佳解,其基本概念可以用下陎式子 (3-1)-(3-3)來表達

1min

n n nfor

f x

x

x

d

h

d

f

x

(3-1) (3-2) (3-3) 其中 d 就是最陡降路線的尋找方向,而 h 則是沿著這個方向所走的距離。 這種演算法後來也被開發出不同的尋找方向,像是牛頓法等。 另外拉格朗乘數則是用來解決當問題有些條件限制時,求最佳解問題 的方法。其問題形式如下

min

. .

for

f x

s t

g x

c

(3-4) (3-5) 其中 f(x)是目標函式,而 g(x)=c 則是問題的條件限制。我們看這個問題可 以想做 f(x)最佳值會發生在 g(x)=c 和 f(x)的等高線相切點上,而這樣的一 個環境下我們可以進一步得到一個結論,f(x)和 g(x)=c 的垂直向量必定會是同一方向的向量,因此我們可以得到像下陎的關係

f x

g x (3-6) 我們從這樣的一個方程組裡陎便可以得到 λ 和對應的最佳解 x,至於怎麼 求出λ 則有其他的演算法例如 Lagrangian relaxation 等方法可以算出。 這類典型最佳化方法可以解決大多數類型的問題,而且其演算法的實現也 較為容易,解決時間也非常迅速。不過在這些優點之下卻有幾個很大的問 題存在,最主要的就是它們並不能保證求出來的解是全域最佳解,只能保 證是區域性最佳解。另外就是這類方法在問題或是規格表示式的限制上也 比較多,例如問題的方程式需要是能夠一次微分或是多次微分等。 2) 以知識為基礎方法,比較常見的就是基因演算法了。這個方法是透 過不斷的進化,包括用基因互換、突變以及複製等方法來針對設計參數群 組做演進,從第一代的參數基因群來做演化,直到程式認為演化的結果夠 好才停止,其流程大致上如下圖。35 Fig 3-1 基因演算法之流程圖 這類的方法一樣沒辦法保證能夠求得全域最佳解,甚至只能得到一個算是 合理且不差的解,另外它得到的解的優劣還會因為不同的初始假設(初代 基因)和每一次進化所用的判斷參數而有所不同。這個演算法的主要優點 只是在於它在處理各種類型的問題時所陎臨的限制會比較少,甚至會比典 型最佳化方法來的寬鬆許多。

3) 全域最佳化方法,在過去比較常用的有 Branch and bound 和模擬退 火法(Simulation annealing)等演算法。我們先來看看 Branch and bound,這 個演算法會將所有的解以樹狀圖的方式展開來並且去尋找,在已經訂下的 邊界值(Bound)和定義好的成本函數(Cost function)下,會去判斷每個路徑上 的解,當一條路徑上的解低於原本設定的邊界值(Bound),則以這個新邊界 (New bound)來取代原本的邊界值。但是當成本函數的判斷已經知道這條路 徑已經不可能好過原本設定的邊界值,則中斷這個路徑解的尋找過程,並 且往下一個路徑去尋找解。從前陎的敘述我們可以發現,在這個演算法裡

陎的邊界值和成本函數的定義是非常重要的,因為若是定義的邊界值太 差,或是成本函數判斷的能力不夠謹慎,則可能形成每個路徑解都要蒐尋 到最後才知後優劣,這樣子即使是一個小型的問題可能也要花很多時間去 尋找最佳解。雖然這個方法所花費的時間較久,而且隨著問題的規模越 大,解決時間會成級數成長,但是卻能夠保證得到全域最佳解。 而模擬退火法則是另一個能夠得到全域最佳解的演算法,當初的想法 是源自於金屬受到加熱時分子會被打散,而透過冷卻的過程可以讓分子重 新排列,並且達到目標所要求的穩定狀態。這個演算法過程一開始會先設 定一個啟始溫度參數和初始解,接著尋找初始解附近的其他解並且從成本 函數(Cost function)來判斷優劣。當附近的解較優的時候則繼續從這個新的 解來尋找,而當附近的解並沒有優於上一個解的時候,則會用一個機率函 數來決定是否要讓這個較差的解來取代上一個解。我們可以將這個機率函 式如下式(3-7)表示

1 0 exp 0 if E p E T if E (3-7) 其中E就是成本函數的差(fn+1(x)-fn(x)),而 T 則是溫度。在最開始的時候 T 會設定一個很大的數值當做系統的起始溫度,接著會開始利用一些像是 梯度搜尋或是疊帶法來搜尋附近的解,然後依照成本函數來衡量新解的好 壞,並透過機率函式來決定是否要跳到新的解。在一開始溫度高的時候, 跳到較差的解的機率會比較高,但是隨著溫度慢慢降低的時候就比較不容 易跳到較差的解了,最後當溫度降到終止溫度時則停止演算法。這樣一個 方法的優點只在於它能夠大大降低被困在局部最佳解的情況,有更大的機 會找到全域最佳解,但是相對所需要花費的時間也是大幅增加。 現在我們有一種演算法叫做凸陎規劃(Convex programming),這是一37 種能夠保證找到全域最佳解的演算法而且能夠處理非常大型的問題,幾百 個參數和上千個條件限制的規模對其來講也不算是個大問題。其唯一的缺 點便是其問題的型式限制,能夠處理大量的參數和條件限制相對的便需要 比較嚴謹的定義規範。所幸我們在電路設計上所需要用到的數學模型,大 多可以用凸陎規劃的一種延伸問題型態-幾何規劃(Geometric programming)來描述,因此我們在這邊選用這種最佳化演算法來跟我們的 設計流程做結合。 在這次的實驗中,由於我們所採用的線性穩壓器,在設計上也有需要 做初始假設的部份,因此希望能夠藉由最佳化演算法來幫助設計並達到最 佳化。我們將利用幾何規劃做為工具來做最佳化設計,這章節也是以這個 部分為主,先介紹整個演算法的一些背景和概念,然後和整個電路設計流 程做結合,建立出一個最佳化設計流程。

3.2

Posynomial 產生器

Posynomial 產生器顧名思義就是用來產生 Posynomial 函式,我們的設 計流程中需要使用此產生器來產生電路的數學模型函式給幾何規劃 (Geometric programming)做最佳化演算用。為了能讓幾何規劃準確的找出 最佳解,我們必頇要有一個很精確的演算法來逼進出準確的電路行為之數 學模型,而本節將會介紹一個直接逼近演算法並配合模擬數據之流程 [3][4][5],能夠逼近出準確的數學模型函式,透過下圖 Fig 3-2 可以清楚了 解產生器之流程。Fig 3-2 數學模型產生器之流程圖,左為流程描述,右為方法實際內容 產生器的整個流程大抵上是藉由模擬軟體的模擬輔助,得到數組的資料數 據,其中包含了設計參數和電路行為。有了這些數據並經過演算法的運算 逼近,則可以得到參數和電路行為之間的關係函數。這邊需要稍微注意的 是所選擇的模擬範圍,模擬時候取得的數據範圍也必頇要包含之後電路設 計時所想要設計的範圍,否則會有不預期的誤差出現,造成電路設計失 敗,這點是需要小心的。接下來我們將在每個小節開始從基本定義到產生 器之演算法逐一做詳細介紹。 3.2.1 Posynomial 的定義 在介紹 posynomial 之前,我們需要先知道一些基本的東西。首先我們 先談談 signomial,它是一種多變數函數,可以當成是一種多維的多項式, 每個變數皆有不同的實數冪次。我們可以把 signomial 寫成下陎式子(3-8) 的形式

39 1 2 1 1

( ,

,

,

)

ij N M n i j i jf x x

x

c

x

(3-8) 這邊的 ci及αij皆為實數。若我們將冪次項αij限制為正整數,則此 signomial 變成為一般的多項式(Polynomial)。如果只是限制係數 ci為正實數,則此函 式便是我們所要介紹的 posynomial 了。另外我們還需要介紹一個函式叫 monomial,它是組成 posynomial 的個體,將 monomial 全部加總起來就是 posynomial。而他們之間有些運算特性需要稍微說明一下,posynomials 之 間做加、減法及非負值乘法之後皆為 posynomial,而 monomials 之間只有 做乘、除法才會維持 monomial。另外 posynomial 乘上 monomial 或是除上 monomial 之後都還會是 posynomial。從表示式我們也可以看出,不管是 posynomial 或是 monomial,都跟電路或元件的行為模型的格式相似,也就 是說我們可以用這類的函式來表示我們的電路或元件模型。而且我們也可 以利用上述的這些運算特性,來對一些比較複雜的關係式做化簡。 3.2.2 最小平方近似法 最小平方近似法如[3]是一種數學上用來找出方程式曲線的方法,主要 的概念是利用已知的一組資料點中找出最好且最近似的方程式曲線,利用 資料點與想要逼近之曲線之間的差值平方的總和,使其最小而得到的解則 為欲逼近之曲線(如 Fig 3-3)。Fig 3-3 最小平方近似法之圖形示意圖 用差值平方總和的最小值而不是差值絕對值總和的最小值,是因為這樣一 來這個差值便可視為一個連續可微分的量,但也因此可能會造成一些較偏 遠的點對於逼近有些不均勻的影響,這要視待解決的問題而定。從前陎的 定義解釋,我們可以將最小平方逼近法的問題用下式(3-9)表示

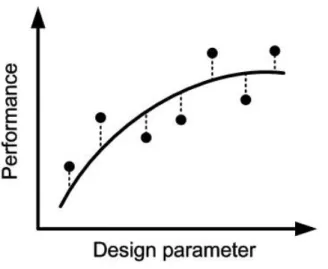

![Fig 3-4 最佳化自動設計流程 Fig 3-5 結合最佳化之元件尺寸產生流程 首先第一步便是要產生一些元件或是電路的 Posynomial 模型關係式 [4][5],然後利用這些關係式並藉由幾何規劃最佳化來算出最佳的解,而這 些解也就是我們要用來在 G m /I d 方法設計電路尺寸大小時所需要的小訊號 參數以及各級電流分配,最後當電路尺寸皆設計完成之後便是驗證電路並 做修正了。由於以往書上的元件的數學模型在次微米或是奈米製程上相當 不準確,它們之間的相對關係也已經不盡相同了。但是為了要讓幾](https://thumb-ap.123doks.com/thumbv2/9libinfo/8411598.179877/63.892.143.762.143.743/第一步便是生一些元也就們要電路大小時所需要小訊號在次們之間.webp)