整合式被動元件之特性分析與應用

全文

(2)

(3) 整合式被動元件之特性分析與應用. 指導教授:吳松茂 博士(教授) 國立高雄大學電機工程研究所. 學生:蘇炫銘 國立高雄大學電機工程研究所. 摘要. 在現今電子元件中,由於對多功能性及小尺寸的需求增加,在這樣的環境下,促使 設計者與供應商想辦法將更多的電路元件(Component)放在一個封裝中,以滿足消費者 需求。鑒於此被動元件製程技術可算是重要關鍵ㄧ環,被動元件製程不同大約分成表面 接合式(SMD)、低溫共燒陶瓷(LTCC)、薄膜式被動元件(Thin Film)等等,其中又以薄膜 製程之被動元件整合性最佳且尺寸最小。本論文內容主要是討論整合式被動元件中的電 感與電容之特性,並試著改變單一變因如圈數、線寬、線距、半徑、及電容面積,並分 別討論其反射係數、電感值、電容值及品質因數。再利用電感之等效電路去探討品質因 素的趨勢變化及影響因素,最後引用這些電感、電容被動元件,根據濾波器設計原理設 計出 900MHz 三階帶通濾波器,適用於 900GSM 通訊產品之應用,最後在 HFSS 模擬軟體 實現其濾波器模型,並比較其模型與 ADS 軟體模擬結果,並探討其影響因素。---- ------------------------------------- ------------------------------------- ------------------------------------- ------------------------------------- -------------------------------------. 關鍵字:電路元件、表面接合式、低溫共燒陶瓷、薄膜式被動元件、反射係數、等效電 路、帶通濾波器、高頻構造模擬器(HFSS), 先進設計系統(ADS) I.

(4) The Electrical Performance Analysis and Application for Integrated Passive Device Advisor: Dr. Sung Mao Wu Institute of Electrical Engineering National University of Kaohsiung. Student: Shiuan-Ming Su Institute of Electrical Engineering National University of Kaohsiung ABSTRACT Driven by the demand for smaller and more-function on the electronic components nowadays, circuit designers urge to put more components on the IC package. Passive component producing technology becomes the important part. Passive component producing technology might be classified into the Surface Mount Devices (SMD), the Low Temperature Co-fired Ceramic (LTCC), and the thin film components. Thin Film Passive Device has the superior in integrating and size. This thesis has been discussed the Integrated Passive Devices including the capacitor and the inductor characteristics, as well as one of their variables such as the circle number, the width, the space, the radius and the capacitor area has been changed to investigate their scattering parameter, inductance, capacitance and Q-factor. The trend and the effect is analyzed by equivalent circuit of inductor. With these results, the 3rd-order band pass filter is designed up to 900MHz, and suitable for 900GSM communication applications. The last part of this thesis is the filter model on High Frequency Structure Simulator, and the results of simulation of the band pass filter have been compared with the equivalent circuits in Advance Design System. Keywords: Circuit Components, Surface Mount Technology, Low Temperature, Co-Fired Ceramic, Thin Film Passive, S-parameter, Equivalent Circuit, Band Pass Filter, HFSS(High Frequency Structure Simulator), ADS(Advance Design System) II.

(5) 誌. 謝. 本文能夠順利完成首先要深深感謝指導教授 吳松茂博士,從一開始題 目的選定與修改、製程資料索得、模組模擬方向、數據的確認….等皆藉由 教授的幫忙與細心輔導,模擬過程也遇到很多瓶頸,教授總是能夠迎刃而 解且對症下藥,始終自己從中也學到很多關於整合式被動元件之特性方析。 另外,也很感謝日月光 維中處長 製程資料的分享,令小弟感激萬分 和 志斌處長 的推薦,如今也才有機會獲得碩士學位,為了不辜負大家的 眾望,毅然決然地日月光工作也先告一段落,專心在實驗室待了半年,實 驗室的漢堡、恩路、水哥、阿哲、阿德也總能在我最需要你們的時候助我 一臂之力,還有日月光的好同事學安、寶男、陳肇、膺傑。 最後,要感謝總是不斷給我支持鼓勵的孟芳、所有家庭成員,讓我能順 利度過這艱苦的兩年生活。在此,誠摯地將此論文獻給你們,並與你們分 享這份喜悅與榮耀。. 蘇炫銘 國立高雄大學 電機工程學系 民國 96 年 11 月 III.

(6) 目 錄 中文摘要………………………………………………………………………………………I 英文摘要…………………………………………………………………………………… II 誌謝……………………………………………………………………………………… III 圖目錄……………………………………………………………………………………VII 表目錄………………………………………………………………………………………X. 第一章、 1-1 1-2. 第二章、 2-1. 緒. 論………………………………………………………………………01. 研究動機與目的………………………………………………………………01 章節提要………………………………………………………………………03. 被動元件技術發展………………………………………………………04 被動元件特性與分類…………………………………………………………04. 2-1.1. 電阻 (Resistor, R) …………………………………………………………05. 2-1.2. 電容 (Capacitor, C) ………………………………………………………05. 2-1.3. 電感 (Inductor, L)…………………………………………………………07. 2-2. 被動元件分類型式……………………………………………………………08. 2-3. 被動元件種類與製程技術……………………………………………………10. 2-3.1. 表面接合式被動元件…………………………………………………………10. 2-3.2. 積層陶瓷被動元件……………………………………………………………10. 2-3.3. 低溫共燒陶瓷…………………………………………………………………12. 2-3.4. 薄膜式被動元件………………………………………………………………14. 2-4. 第三章、 3-1. 分離式與整合式被動元件之比較……………………………………………16. 整合式被動元件之製程及設計架構…………………………………18 薄膜被動元件製程探討 ……………………………………………………18. 3-1.1. 薄膜電阻 ……………………………………………………………………19. 3-1.2. 薄膜電容 ……………………………………………………………………22. 3-1.3. 薄膜電感 ……………………………………………………………………23. 3-2. 整合式被動元件之模型架構 ………………………………………………25 IV.

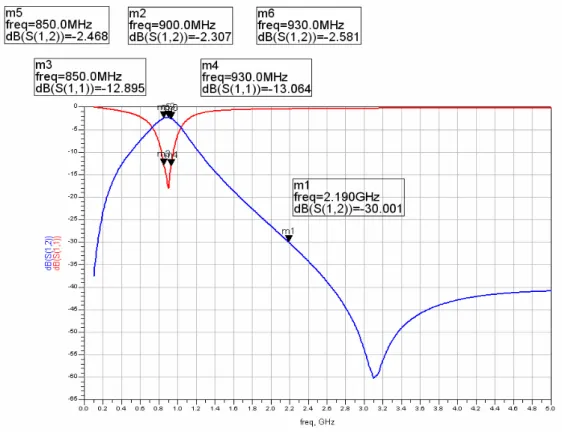

(7) 3-2.1. 電容與電感剖面尺寸 ………………………………………………………25. 3-2.2. 電感器模型…………………………………………………………………26. 3-3. 電感模擬結果比較 …………………………………………………………27. 3-3.1. 線圈圈數的影響 ……………………………………………………………27. 3-3.2. 線距的影響 …………………………………………………………………29. 3-3.3. 線寬的影響 …………………………………………………………………31. 3-3.4. 電感半徑的影響 ……………………………………………………………33. 3-4. 電容元件 ……………………………………………………………………35. 3-5. 螺旋電感等效電路模型參數之萃取與驗證 ………………………………36. 3-5.1. 等效模型推導 ………………………………………………………………36. 3-5.2. 電感等效電路最佳化步驟 …………………………………………………39. 3-5.3. 電感品質因素(Q-factor)與電感值(Leff)探討 …………………………43. 第四章、整合式被動元件應用-帶通濾波電路設計…………………………46 4-1. 濾波器設計原理 …………………………………………………………… 46. 4-1.1. 濾波器規格選定 …………………………………………………………… 46. 4-1.2. 諧振電路設計原理 ………………………………………………………… 46. 4-1.2.1 品質因素(Q-Factor) ………………………………………………………… 47 4-1.2.2 串聯諧振(series resonance) ………………………………………………… 49 4-1.2.3 並聯諧振(parallel resonance) ……………………………………………… 50 4-2. 實際濾波器之設計流程 …………………………………………………… 53. 4-2.1. 帶通濾波器規格訂定…………………………………………………………54. 4-2.2. 理想電路建立與模擬 ……………………………………………………… 54. 4-2.3. 資料庫元件電路模擬 ……………………………………………………… 55. 4-2.4. EM 模擬結果 ……………………………………………………………… 56. 4-2.5. 電磁、實際元件與理想三者之散射參數圖比較……………………………57. 4-2.6. 電磁模擬結果與濾波器規格比較………………………………………… 59. 第五章、 結論……………………………………………………………………………61. V.

(8) 5-1. 未來展望……………………………………………………………………… 61. 參考資料 ……………………………………………………………………………………62. VI.

(9) 圖 目 錄 圖 2-1: 表面黏著式與整合式電容之面積比較…………………………04 圖 2-2: 電子電路元件分類圖……………………………………………05 圖 2-3: 各種型式被動元件成品圖………………………………………08 圖 2-4: 表面接合式被動元件架構……………………………………10 圖 2-5: 積層陶瓷電容結構圖…………………………………………11 圖 2-6: LTCC 製程流程圖…………………………………………………13 圖 2 -7 : 薄 膜 製 程 流 程 圖 … … … … … … … … … … … … … … … … … … 1 5 圖 2-8: 整合式被動元件與分離式被動元件尺寸比較圖……………16 圖 3-1: 薄膜電阻製程示意圖……………………………………………20 圖 3-2: 薄膜電容製程示意圖……………………………………………22 圖 3-3: 薄膜電感製程示意圖……………………………………………23 圖 3-4: 常見的平面電感圖形設計………………………………………24 圖 3-5: 電感器與電容器剖面圖………………………………………………25 圖 3-6: EM 全波模擬 3D 圖示………………………………………………26 圖 3-7: 2D 電感模型 ……………………………………………………………26 圖 3-8: 線圈插入損耗(insertion loss,IL)與頻率關係圖 ………………27 圖 3-9: 線圈有效感值(Leff)與頻率關係圖…………………………………28 圖 3-10: 線圈品質因素(Q)與頻率關係圖 ……………………………………28 圖 3-11: 線距插入損耗(insertion loss,IL)與頻率關係圖 ………………29 圖 3-12: 線距有效感值(Leff)與頻率關係圖…………………………………30 圖 3-13: 線距品質因素(Q)與頻率關係圖 ……………………………………30 圖 3-14: 線寬插入損耗(insertion loss,IL)與頻率關係圖 ………………31 VII.

(10) 圖 3-15: 線寬有效感值(Leff)與頻率關係圖…………………………………32 圖 3-16: 線寬品質因素(Q)與頻率關係圖 ……………………………………32 圖 3-17: 內徑插入損耗(insertion loss,IL)與頻率關係圖………………33 圖 3-18: 內徑有效感值(Leff)與頻率關係圖 ………………………………34 圖 3-19: 內徑品質因素(Q)與頻率關係圖……………………………………34 圖 3-20: 電容高頻等效電路圖 ………………………………………………35 圖 3-21: 平面螺旋電感等效電路模型…………………………………………36 圖 3-22: 簡化後等效電路模型(一) ……………………………………………38 圖 3-23: 簡化後等效電路模型(二) ……………………………………………38 圖 3-24: 最佳化目標設定………………………………………………………39 圖 3-25: ADS 最佳化電感等效電路模型………………………………………39 圖 3-26: 插入損耗(insertion loss,IL)增益值………………………40 圖 3-27: 插入損耗(insertion loss,IL)相位…………………………41 圖 3-28: 反射損耗(return loss,RL)增益值 …………………………41 圖 3-29: 反射損耗(return loss,RL)相位 ……………………………42 圖 3-30: 有效感值(Leff) ………………………………………………42 圖 3-31: 品質因素(Q)……………………………………………………43 圖 3-32: 雜散電容對感值的影響趨勢圖………………………………………44 圖 3-33: 雜散電容對品質因素的影響趨勢圖…………………………………44 圖 3-34: 耦合電容對電感值的影響趨勢圖……………………………………45 圖 3-35: 耦合電容對品質因素的影響趨勢圖…………………………………45 圖 4-1(a): 儲能元件等效電路………………………………………… 48 圖 4-1(b): 儲能元件等效電路………………………………………… 48 VIII.

(11) 圖 4-2: 串聯諧振器電路圖………………………………………………49 圖 4-3: 串聯諧振電路的電流與頻率……………………………………50 圖 4-4: 並聯諧振器電路圖………………………………………………51 圖 4-5: 並聯諧振電路的電阻與頻率……………………………………51 圖 4-6: 低通(Low Pass)原型濾波器電路圖……………………………52 圖 4-7: 高通(High Pass)原型濾波器電路圖 …………………………52 圖 4-8: 二階帶通(Band Pass)濾波器電路圖 …………………………52 圖 4-9: 三階帶通(Band Pass)濾波器電路圖 …………………………53 圖 4-10: 濾波器設計流程……………………………………………… 53 圖 4-11: 理想 900MHz 三階濾波器諧振電路圖…………………………54 圖 4-12: 理想 900MHz 三階濾波器散射參數圖…………………………55 圖 4-13: 900MHz 三階帶通濾波器考慮雜散效應電路圖 ………………55 圖 4-14: 900MHz 三階濾波器考慮雜散效應散射參數圖 ………………56 圖 4-15: HFSS 濾波器模型………………………………………………56 圖 4-16: 900MHz 三階濾波器模型 EM 模擬散射參數圖………………57 圖 4-17: 900MHz 三階濾波器模型反射損耗(RL)比較圖………………58 圖 4-18: 900MHz 三階濾波器模型插入損耗(IL)比較圖………………58 圖 4-19: EM 模擬頻帶分析圖 ……………………………………………59. IX.

(12) 表 目 錄 表 1-1: 產品之被動元件與 IC 所佔比例表……………………………………02 表 1-2: 個人電腦內所含被動元件數目與種類表 …………………………… 02 表 2-1: 各類電容器之優缺點及其趨勢比較 ………………………………… 07 表 2-2: HTCC 與 LTCC 之比較……………………………………………………14 表 2-3: 各式被動元件比較表……………………………………………………17 表 3-1: 被動元件薄膜的形成方式.…………………………………………… 19 表 3-2: 常用之金屬陶瓷材料整理 …………………………………………… 21 表 3-3: 各層尺寸高度 ………………………………………………………… 25 表 3-4: ADS 最佳化前後參數值…………………………………………………40 表 4-1: 常用無線傳輸頻帶表……………………………………………………46 表 4-2: 帶通濾波器初始規格表…………………………………………………54 表 4-3: 各諧振電路 LC 值………………………………………………………54 表 4-4: 模擬前後濾波器規格比較表……………………………………………60. X.

(13) 第一章、緒 論 1-1、研究動機與目的 隨超大型積體電路製造技術進步,晶圓線路集積度不斷提升,晶片I/O引腳數量 與功率消耗急遽上升,以導線架(Lead-Frame)結構為主的封裝型式逐漸無法滿足龐 大I/O引腳與熱散逸要求,球柵陣列封裝(Ball Grid Array Package, BGA)開始被普遍 發展與應用。BGA封裝之電氣訊號傳輸利用多層微型化印刷電路基板佈線而成,各 層訊號以鍍穿孔(Via)相連接,相較於導線架封裝結構最大不同之處,在於BGA封裝 有較佳之電氣傳輸路徑及熱散逸特性,但不同封裝基板線路設計對相同晶片會產生 不同之寄生效應影響,基板佈線設計良瓠成為產品成功與否主要關鍵。高性能集積 要求下,需求更複雜且更多的模組,相對以被動元件作為阻抗匹配、電路解耦合與 旁路等電路設計一部份之需求量大增,表1-1為被動元件於4C電子產品之被動元件與 IC所佔比例表,表1-2分析PC產業被動元件個數增加趨勢;觀察表一與表二發展趨 勢,如何設計與整合被動元件於電路,以及高品質低誤差偏移之被動元件製造技術 將是一門重要課題。 混和使用金線銲線(Wire-bond)與凸塊(Bumping)之接合方式將SOC晶片或多 種功能晶片利用功能性基板封存於一構裝系統中,為SiP系統構裝之意義。系統構裝 意味著更多I/O數目、更複雜之導線接合、信號功能測試與可靠度之問題,整合晶片 -基板信號超細間距界面接合技術、功能性基板設計製造、晶圓尺寸構裝、三維空間 構裝、高精度組裝及結構發展等關鍵技術達成高密度、小型化的整合目標,以及功 能基板之選擇與設計、各種電特性分析、結構應力分析、熱傳分析與構裝材料之發 展選擇等,為構裝發展之關鍵。 隨著電子系統高效能及小型化需求,本研究之主要目標在建立整合式被動元件 (Integrated Passive Device,IPD)分析技術,提供被動元件等效模型以供設計模型建 立使用;提出濾波器設計範例,驗證被動元件等效模型於電路設計之可用性與模型 之缺失,供後續研究改進參考。. 1.

(14) 表1-1:產品之被動元件與IC所佔比例表[1]. 資料來源: Richard K. Ulrich. 表1-2:個人電腦內所含被動元件數目與種類表[1]. 個人電腦內所含被動元件數目表. 所占被動元件數目(個). 2500 2000 1500 數列1 1000 500 0 486. Pentium 120. Pentium 200. Pentium II. Pentium III. CPU 速度. 資料來源: Richard K. Ulrich 2.

(15) 1-2、章節提要 本研究共分為六章節,第一章緒論部分,概述研究動機與目的;第二章就被動 元件之種類與應用,及製程技術發展加以闡述;第三章依據整合式被動元件製程技 術實現被動元件架構、模擬分析結果做初步討論;第四章根據模擬結果,探討元件 電氣特性,為進一步瞭解影響元件特性之變因以控制與改善元件特性,建立電感元 件等效電路與探討其品質因素變化趨勢;第五章討論元件模型實用性,以900MHz 帶通濾波電路為例,討論元件等效模型、製程結構參數電磁模擬及設計原型結果差 異主因;第六章針對研究結果提出結論,並對未來研究提供方向。. 3.

(16) 第二章 被動元件技術發展 本章將針對就被動元件之種類分類與市場應用做整理與分類。以及將常見之製 程技術做討論。. 2-1、被動元件特性與分類 圖2-1為表面黏著式與整合式電容元件面積比較(以電容為例),電容值相同條件 下,表面黏著元件雜散效應明顯比整合式元件來的大,而整合式元件之雜散電感值 較低,諧振頻率亦較高;整體而言,整合式被動元件不管在電性特性上、或所佔面 積皆比表面黏著離散元件佳。. IPD type. SMT type. 元件. 電容值 (pF). 雜散電感值 (pH). 雜散直流電阻 (Ω ). 諧振頻率 (MHz). 表面黏著式. 8.5. 340. 41. 94. 整合式. 8.5. 5. 38. 760. 圖2-1:表面黏著式與整合式電容之面積比較 [2,3] 電子電路如圖2-2之分類,分為線性電路(Linear)與非線性電路(Non-linear)兩大 類。非線性電路主要應用於大訊號之波形產生、整流、定位以及截波等用途;而對 線性電路而言,傳遞不同頻率小信號波形為電路主要目的,依據「流經元件之電壓、 4.

(17) 電流是否符合歐姆定律」將元件區分為主動(Active)元件與被動(Passive)元件兩種, 這亦是構成現今電子電路之主要元件。. 線性電路 Linear Circuit. 主動性元件. 二極體(Diode)、電晶體(BJT)、. Active Device. 場效體(FET)、OP. 被動性元件. 電子電路. Passive Components 非線性電路. 電阻(Resistor)、 電容(Capacitor)、 電感(Inductor). 波形產生器、整流器、定位電路、截波電路. Non-Linear Circuit 圖2-2:電子電路元件分類圖 2-1.1、電阻 (Resistor, R) 電阻器之定義為單位電流於電阻器兩端所形成之壓降,壓降越大,代表電阻值 越大。電阻器阻值測量分為以公式(2.1)計算未加電源之測量方式,以及以外加偏壓 或電流源之方式求取阻值之方式。其單位、符號、測量方式與功率損耗如下所示: 單位:歐姆 Ω. 符號:. Æ未加電源之量測方式: A. ρ. ρ :電阻係數 Resistively R=ρ. A ·······································································(2.1). Æ加上電源之量測方式: v (t ) + v (t ) R= i (t ) ···································································(2.2) i (t ) v 2 (t ) p (t ) = i (t ) v (t ) = i 2 (t ) R = R ···············································(2.3) Æ消耗功率: 耗能量(熱能): ∫. p(t ) dt. ·········································································(2.4). 電阻器依其功能差異可區分為固定式非晶片型和固定式晶片型電阻器、可 變式電阻器以及非線性電阻器三大類,用以降壓與分壓來調整電路電壓,以及 突波吸收、溫控與感測等功能。 2-1.2、電容 (Capacitor, C) 5.

(18) 電容之定義為每外加單位伏特電壓下,兩導體電板所容納之電荷值。求取電容 之方式與電阻大致相同,亦分為加電源與不加電源之方式求取,其單位、符號、測 量方式與功率損耗如下所示: 單位:法拉 F. 符號:. Æ未加電源之量測方式: A d. ε :介電係數 Permittivity A C =ε d ·······································································(2.5). ε. Æ加上電源之量測方式 +Q. -Q. Q (t ) = C (t )V (t ) ··························································(2.6). Æ電容上,電流與電壓關係:∵ Q = CV → i (t ) =. dQ (t ) dV ··············(2.7) =C dt dt. ∫ p(t )dt = ∫ v(t ) i(t ) dt = ∫ v(t ) Æ電容儲存之能量(電能):. dv(t ) 1 dt = CV 2 (t ) 2 dt (2.8). 電容器分為可變電容器及固定電容器。電容器依材質差異性又分類為紙 質電容器、陶瓷電容器、鋁質電解電容器、塑膠薄膜電容器、鉭質電容器、鈦 質 電 容 器 、 雲 母 電 容 器 …等 種 類 。 陶 瓷 電 容 器 又 可 細 分 為 積 層 陶 瓷 電 容 器 (Multi-layer Ceramic Capacitor, MLCC)、圓板型陶瓷電容器、AC安規陶瓷電 容等,各類電容器之優缺點及其趨勢比較表如表2-1 [4]。 電容器的功能包括濾波、整流、耦合及高速充放電等主要功能。一般在 電子產品內被動元件之使用,以電容器之用量最多,約占組裝被動元件總數的 四至七成[5],當電子系統愈趨複雜,主動元件工作電壓 一再降低與功能不斷 強化的趨勢下,訊號線(Signal line)與接腳數(I/O)持續的添加,解電磁 耦合(Decoupling)消減雜訊效應所用到低容值的旁路(By-pass)電容器, 其數目上也隨之有增多的趨勢。. 6.

(19) 表2-1:各類電容器之優缺點及其趨勢比較[4]. 2-1.3、電感 (Inductor, L) 電感之定義為電感器通過單位安培電流時產生之磁通量大小。求取電感 之方式為加電源之方式求取,其單位、符號、測量方式與功率損耗如下所示: 單位:亨利 H. 符號:. Æ電感值之量測: φ :磁通量(flux) +. φ (t ). -. L=. i (t ). φ (t ) i (t ) ···········································································(2.9). Æ電感上電流電壓之關係:. φ (t ) = L i (t ). ∴ v (t ) =. dφ (t ) di (t ) =L dt dt ···················································(2.10). Æ電感儲存能量(磁能):. ∫ p(t ) dt = ∫ i(t ) v(t ) dt = ∫ Li(t ). 1 di (t ) dt = L i 2 (t ) 2 dt ··································(2.11). 電感器主要功能包括濾波、穩定電流、升降壓與去除雜訊,功能與電容 器相似,不同的是,電容器是以電場的形式來儲存電能,而電感器乃是以磁場 的 形 式 來 儲 能 , 隨 著 高 頻 技 術 的 發 展 , 電 磁 波 干 擾 ( Electro Magnetic 7.

(20) Interference, EMI) 的 問 題 備 受 重 視 , 而 電 感 器 具 有 防 制 電 磁 波 干 擾 ( EMI Shielding)之功能,所以電感器的發展在電子元件中的重要性亦愈趨重要, 電感器依產品型態,大致上可分為傳統線圈式電感與晶片電感等兩大類,由於 電子產品的輕薄短小化已成趨勢,積層晶片型電感已成電感器的主流技術。. 2-2、被動元件分類型式: 被動元件通常可以引腳型或表面接合型分離式、陣列式以及及整合式的 類型來分類,各種型式之被動元件成品如圖2-3所示。. (a)單層陶瓷/鋁質電解電容器. (b)積層陶瓷電容器. (c)晶片電容器 圖2-3:各種型式被動元件成品圖[2] 其中值得注意的是,各種不同電氣特性與功能之被動元件有著各自不同 的元件結構、材料及容許誤差,在被動元件的發展上,可概略分成以下三個方 向來觀察: 8.

(21) 1. 以被動元件之功能來看: 包含兩種型態的發展,一種是單一型被動元件製造技術發展,例如:晶片 式 電 阻 、 晶 片 式 電 感 、 積 層 陶 瓷 電 容 (Multi-Layer Ceramic Capacitors, MLCC)等,積極改良單一性功能之元件製程,另一種則是整合式被動元件 技術發展,例如:高溫共燒陶瓷(High-Temperature Co-fired Ceramics; HTCC)技術、低溫共燒陶瓷(Low-Temperature Co-fired Ceramics;LTCC) 技術、薄膜式被動元件(Thin Film Passive)及埋入式被動元件(Embedded Passive)等,提供了主動元件或模組與被動元件的整合能力。 2. 以被動元件與系統間的連接關係來看: 自1960年引腳插入接合式(Through Hole Device, THD)開始發展,之後 有 表 面 接 合 式 ( Surface Mount Device, SMD ) 與 埋 入 式 被 動 元 件 (Embedded Device)兩種技術的發展,表面接合技術發展至今已有十餘 年,近年來晶片型(Chip Type)被動元件出現後,被動元件之尺寸愈趨微 小,甚至還可將0402(1㎜×0.5㎜×0.5㎜)的電容單體製做成陣列(Array) 型態的元件,擠列30顆於CPU載板腹底中央的狹地上,且因其單價便宜又 品質優良,所以一直為當前技術之主流。 埋入式被動元件技術之發展最早商品化的是Ohmega-ply公司,其利用 線路基本之內層板面原有銅箔的毛面(Matt Side)上,形成磷鎳合金層之 薄 膜 , 當 做 電 阻 性 元 件 ( Resistive Element) 壓 合 成 為 薄 核 心 層 ( Thin core) ,再利用光阻與蝕刻的線路圖案化技術,於特定位置形成所需的薄膜” 電阻器”,當時之技術命名為Buried Resistor。1992年美國公司Zycon在高 階多層基板中之Vcc/GND內層之間,加入介質層(2-4mil)的內層板,利 用廣大面積的平行金屬銅板面,製作成為整體性的電容器,商名稱為Buried Capacitor,此後埋入式被動元件之技術成為高密度內連結(High Density Interconnect, HDI)技術的一部份[5]。 3. 以被動元件製程來看: 則可分為陶瓷共燒技術、薄膜技術與內埋製程技術三類技術發展,各自有 其特色及優勢,至今此三類技術仍持續發展並進中。. 9.

(22) 2-3、被動元件種類與製程技術: 2-3.1 表面接合式被動元件 早年的線路基板使用引腳插入型的元件,線路基板需先鑽洞,元件引腳 穿過後再加以湧錫銲接技術來接合。由於元件體積大,引腳間無法太過靠近, 線路基板背面又是銲接接點無法加以利用,致空間上造成許多浪費,至 70年 代末,出現一種新的線路基板裝配技術,名為表面接合技術(Surface Mount Technology, SMT), 這 種 技 術 是 將 元 件 上 的 引 腳 係 銲 接 在 線 路 基 板 的 表 面 上,而非貫穿線路基板,使得線路基板兩面均可設置元件,並使用表面接合迴 銲(Solder Reflow)技術銲接元件於線路基板上如圖2-4,相對於引腳插入型 元件而言,表面接合式的元件體積更是小得許多,但元件的密集程度若與積體 電路相比,仍是相差甚遠。. R. L. C. IC. Substrate 圖 2-4:表面接合式被動元件架構. 2-3.2 積層陶瓷被動元件 由於電子產品朝向輕薄短小、低耗能發展的趨勢,使得電子元件也面臨 體積縮減的壓力,近年來已漸漸被表面接合式的晶片型元件所取代,配合多層 線路的印刷電路板,兩面均可黏著晶片式電子元件,更大幅提高線路的密集程 度,而在二次世界大戰後,具有高介電係數、高壓電常數、高機電耦合常數及 良好光電效應的鐵電陶瓷材料被大量地開發及應用,在電容器的發展上,又由 於陶瓷薄膜堆疊技術越來越進步,使得所生產出來的電容值也越來越高,已逐 漸取代了習知的電解電容器和鉭質電容器,再加上可配合利用SMT技術直接 在基板上黏著,使得陶瓷電容在發展上一直受到重視[6]。 晶片電阻使用絕緣的氧化鋁陶瓷作為基板,利用網版印刷技術將含有氧 10.

(23) 化釕的電阻材料印刷上去,再印上保護用的薄層玻璃粉,經過高溫燒結後成為 晶片電阻。由於印刷時電阻材料的黏度、溶劑的比例,以及製程上其他的變因, 造成成品上電阻值的誤差,所以成品仍需要經過雷射切割,才能生產出合乎標 準的產品。 表面黏著型的電容又稱為晶片陶瓷電容,因電容量的大小與電極面積成 正比,而積層陶瓷電容的尺寸又比傳統圓板形陶瓷電容小得多,因此,電極的 排列就朝向立體化發展,同樣使用網印的技術,將導體與介電層交錯地印刷在 絕緣基材上,使得電極的總面積隨著堆疊層數增加而變大,積層陶瓷電容就是 利用疊印技術,將每一層的導體與絕緣體縮減到只有幾十微米的厚度,一個元 件裏面堆疊了數十層,甚至上百層,而元件總厚度卻只有一、二公厘而已,其 結構如圖2-5所示[7]。同樣的製作方式也可應用到積層晶片電感器。. 圖2-5:積層陶瓷電容結構圖[7] 整體而言,積層陶瓷被動元件利用網印技術來製作,所使用之材料有網 版及油墨,而油墨又包含導體油墨及介電油墨。網印使用的網版是由不鏽鋼絲 製成的網布,目前較常使用的網印解析度大約50微米,相當於一根頭髮的寬 度,而使用的油墨,不論是導體或是絕緣體,其顆粒都必須能透過網布上的網 孔,因此,除原料顆粒大小必須加以控制外,也要防止粒子過度聚集,製作環 11.

(24) 境也要管制避免灰塵雜質污染。導體油墨包含了導電粒子、樹脂、溶劑和少許 的玻璃粉,藉由樹脂和溶劑形成黏稠載體,將導電粒子及玻璃粉均勻分散其 中。導電粒子通常是直徑在一個微米左右的銀或鈀銀合金,在燒結的過程中溶 劑會揮發、樹脂會氧化,存留下的少許玻璃會將導電粒子彼此黏結形成導電通 路。貴金屬因具有不易氧化的特性,經過攝氏800度燒結後,鈀銀等貴金屬仍 能保有良好的導電性,然而鈀銀的成本太高,近年來已有用較便宜的卑金屬(例 如鎳)電極材料來取代之趨勢,但也同時產生了在燒結的過程中需控制樹脂氧 化燒除,而卑金屬不能氧化的難題,目前的解決方式為控制燒結爐的含氧量, 使其足夠氧化樹脂又不至於使金屬氧化。介電油墨包含了介電陶瓷粉體(例如 鈦酸鋇粉體)、樹脂、溶劑以及少許的玻璃粉,如同導體油墨般,樹脂和溶劑 將陶瓷粉體分散,使得網版印刷得以進行,而燒結後陶瓷粉體被玻璃所黏結, 形成介電層[8]。 燒成後的被動元件體積很小,晶片型的被動元件,其尺寸規格是以兩組 數字來表示,代表的分別是元件的長和寬(大的數字在前,如 0402、0603), 而且是以英制單位來表示。近幾年來,元件在尺寸上已從2220、1812、1210 縮小至以1206、0805、0603、0402為主,甚至於更小的0201及01005。. 2-3.3 低溫共燒陶瓷 低溫共燒陶瓷(LTCC)技術是相對於高溫共燒陶瓷(HTCC)而言,LTCC 與HTCC的區別在於陶瓷粉體配料和金屬化材料不同,LTCC在燒結上控制更 容 易 , 燒 結 溫 度 更 低 。 圖 2-6為 低 溫 共 燒 陶 瓷 製 程 流 程 圖 [8], 主 要 採 用 低 溫 (850℃~900℃)燒結瓷料與有機黏合劑/增塑劑按一定比例混合,通過流延 生成生瓷帶或生胚片,在生瓷帶送上形成通孔或電射鑽孔、金屬化佈線及通孔 金屬化,然後進行疊片、熱壓、切片、排膠、最後約900℃低溫燒結製成多層 佈線基板。 而HTCC的燒結溫度需在1500℃以上,所採用的高熔點金屬如鎢、鉬、錳 等導電性能較差,所以燒結收縮並不如LTCC易於控制,但HTCC已是一種成. 12.

(25) 熟技術,產業界已對材料和技術均已有相當的瞭解,且氧化鋁的機械強度比 LTCC介質材料的機械強度高得多,此外,氧化鋁的熱導率比LTCC介質材料的 熱 導 率 幾 乎 要 高 20 倍 。 低 溫 共 燒 陶 瓷 與 高 溫 共 燒 陶 瓷 特 性 比 較 整 理 如 表 2-2[10]。. 圖2-6:LTCC製程流程圖[7][9] LTCC利 用 陶 瓷 材 料 作 為 基 板 , 將 電 容 、 電 阻 等 被 動 元 件 埋 入 陶 瓷 基 板 中,並採用金、銀、銅等貴金屬共燒形成電極,再印刷塗佈電路,最後在攝氏 850~900度中燒結而形成整合式陶瓷元件。當整塊低溫共燒陶瓷模組黏到電路 板上時,裏面就包含了上百顆的被動元件和部分的線路,如此可大幅縮減元件 之間的空間,但仍有其限制和缺點,例如不同的材料隨著疊印層數的增加,製 作困難度就越高。其次,所有元件燒結在一起後就無法將其分割,若線路設計 有所修改,整個元件便要全部重做,因此,LTCC元件大多是為了某一個特定 功能的電路。 13.

(26) 表2-2:HTCC與LTCC之比較[10]. 2-3.4 薄膜式被動元件 關於被動元件的整合,因為受限於材料、技術以及經驗等等,發展進度 並不如預期快速,目前技術較為成熟的是利用陶瓷材料,以LTCC的技術將被 動元件整合於基板之內,雖然陶瓷材料成本並不昂貴,但是由於生產費用過 高,不易達到降低單價的目標。此外,PCB板上幾乎都採用SMT的技術生產, 隨著元件體積縮小化之後,表面黏著設備不易處理過小元件,例如0402或0201 等等,於是就有人開始研究將積體電路的薄膜技術用來整合被動元件,企圖能 解決上述之問題。 主動式與被動式元件於製造技術上最大的差異在於主動元件用的是曝 光、顯影、鍍膜、擴散、蝕刻等「薄膜製程」,每層的厚度很少超過一個微米 (0.01~1μm),而被動元件使用的是網版印刷與高溫燒結等「厚膜製程」,每 一層的厚度至少都有幾個微米( 5~10μm),在線寬的解析度上兩者更相差了 百倍以上,以晶片電阻為例,0201的晶片電阻產品外觀尺寸才0.5×0.25mm, 14.

(27) 對網印製程而言是極難跨越的技術瓶頸,相對於薄膜製程能力而言卻仍是有所 餘裕[11]。 也因製程能力上的差異,使得共燒陶瓷元件與積體電路元件很難以相同 的製程整合在同一塊基板上,只能用覆晶封裝等技術將積體電路的矽晶片直接 黏貼到主機板上,以減少封裝所占的面積。由於薄膜製程可以使被動元件所占 的體積縮得更小,在使用這些昂貴的製程之後,除了可以更縮減了被動元件體 積之外,更同時提供了一個與積體電路整合的可能性,讓主動、被動元件可以 同時設置在同一塊基板上,然而,在矽基材上用薄膜技術製造被動元件,卻容 易導致電感元件之Q值偏低,又薄膜電容之介電材料通常不屬於強介電材料, 其電容特性亦有所限制,兼之製程設備與製程環境均需相當高之成本,所以相 較於SMT及LTCC而言,仍有其待突破之不利因素。. 資料來源:工研院IEK-ITIS 圖2-7:薄膜製程流程圖. 15.

(28) 2-4、分離式與整合式被動元件之比較 國 際 電 子 製 造 業 聯 合 會 (National. Electronic. Manufacturing. Initiative,NEMI)2002年的願景中對各式被動元件之比較如表2-3所示[12],綜 合來看,整合式被動元件相較於分離式被動元件具有以下優點[13]: 1. 提高系統可靠度與元件高頻特性: 使用整合式被動元件可減少板面SMT銲點數目,提高產品可靠度,降 低因高頻所產生不必要之寄生效應(Parasitic Effects,如寄生電容或寄生 電感等) ,進而提升射頻模組在高頻電氣響應,改善電性與減少電磁波干擾。 2. 縮小產品體積: 整合式被動元件是將原本黏著於基板上的獨立電阻、電容、電感整合 於一被動元件模組或內埋於該基板中,因此而減少該基板板面之使用空 間,如此可縮小產品設計或多增設其他功能元件。整合式被動元件與分離 式被動元件尺寸比較如圖2-6[14]。 3. 增加產品的使用年限: 整合式被動元件可製於一模組或內藏於一基板中,都可減少溼度、腐 蝕對該元件的影響,增加產品的使用年限。. 圖 2-8:整合式被動元件與分離式被動元件尺寸比較圖[14]. 16.

(29) 但整合式被動元件發展並不全然順利,其仍有待解決問題如下[5]: 1. 無法完全替代具多種數值及各項用途的被動元件,目前只能提供容值較低或 阻值較低的部分用途。 2. 製程較為昂貴且有專利上的問題。 3. 單次設計之元件功能專屬性高,對於產品改變設計反應彈性不佳。 4. 尚無完整的系統設計之實用軟體與電性測試用軟體等。 5. 公差(Tolerance)不夠嚴謹,且因已製備後已整合於一元件內,無法替換或 利用後續之專用雷射之修整技術(Laser Trimming)加以調整,即便於元件製 程中可以修整,其高昂成本亦難以接受。 6. 現行分離式被動元件技術相當成熟,不但愈做愈小而且還愈做愈好,加上產 量很大,價格均可被接受,致使系統客戶更換意願不高。. 表 2-3:各式被動元件比較表[12]. 17.

(30) 第三章、整合式被動元件之製程及設計架構 3-1、薄膜被動元件製程探討 薄膜製程與厚膜技術最大的差異就在於產生的膜厚,一般所謂的厚膜其 厚 度 多在 5~10μm以 上 , 而 薄 膜 製 程 產 生 的 膜 厚 約 在 0.01~1μm之 間 。 要 利 用 薄膜製程同時形成電阻、電容、電感的元件時,需要運用不同的製程與材料來 製作,然而製程溫度都可控制在400℃以下,相較於陶瓷技術所需的燒結溫度 800~900℃而言,薄膜製程穩定度較高,且薄膜技術在半導體積體電路製程發 展已久,技術已相當成熟,所以在進行製程整合時,只需注意不同元件間材料 的相容性,即可達成製程的設計,或可以採用相同材料系統,如同屬Ta系統 的TaN與Ta 2 O 5 ,分別做為電阻與電容的材料,可避免不同材料系統間可能產 生製程整合的問題[11]。整體而言,薄膜式被動元件可因應不同的產品應用, 製作在不同的基板上,基板可選擇矽晶片、氧化鋁陶瓷基板、玻璃基板,甚至 有機材料基板上,都可製作薄膜被動元件。除了被動元件的整合,在矽晶片上 也可以結合主動式元件的製程,將被動元件與主動元件電路整合以達到多功能 化的需求。 薄膜的形成方式主要可分為乾式和濕式兩類,其方式整理如表 3-1[15]。 其中在電子工業中較為常用的方式有真空蒸鍍、濺鍍、印刷、電鍍及化學鍍等, 真空蒸鍍係在一腔體內,將鍍料加熱、蒸發,使其原子或原子團在溫度較低的 基材上析出成膜;濺鍍是將放電氣體導入真空,在放電電漿中產生的正離子加 速撞擊陰極的靶材,使轟擊出的原子沈積在基材上形成薄膜,此二法因利用物 理 現 象 達 成 薄 膜 形 成 , 故 又 稱 物 理 氣 相 沈 積 ( Physical Vapor Deposition, PVD)。相較於 PVD 而言,利用化學反應使氣態原料生成固體薄膜的沈積方 式則稱化學氣相沈積(Chemical Vapor Deposition, CVD)。印刷法則是依功 能要求將金屬氧化物、玻璃黏著劑等粉末混合有機黏著劑、表面活性劑、有機 溶劑,調製成漿料,再網印於基材上形成圖形,再燒結成膜。電鍍和化學鍍係 靠電場反應,使金屬從金屬鹽溶液中析出,惟電鍍的還原能量是由外部電源提 供形成電場,而化學鍍係利加添加還原劑,使其自分解而成,但此類方式均有 大量藥劑使用,對環境而言較有影響[15]。 18.

(31) 表3-1:被動元件薄膜的形成方式[15] 類型. 乾式. 濕式. 3-1.1. 方. 式. 真空蒸鍍. 切削. 光聚合反應. 濺鍍. 壓延軋制. 放電聚合. 離子鍍. 化學的製膜法. 蒸鍍聚合. 電漿噴塗. 熱分解法. -. 電漿噴射. 氣相反應法. -. 電鍍. 蝕刻. 溶膠-凝膠. 化學鍍. 網版印刷. L-B法. 陽極氧化. 塗敷. -. 薄膜電阻 薄膜電阻的製作方式通常利用濺鍍製程電阻材料電鍍於絕緣基材上,再. 利用光阻與蝕刻的技術,圖案化該電阻材料以獲得預期之電阻值,其製程示意 圖如圖3-1所示。 在 材料的選用上,薄膜電阻的原材料電阻率多介於 100~2000μΩ. cm, 其成膜之片電阻值多介於10~1000Ω/square間,另在材料特性上尚須考量其電 阻溫度係數(Temperature Coefficient of Resistance, TCR),TCR即該材料 於不同溫度下之電阻變化率,通常需在100 × 10 -6 /℃以下。常用於薄膜電阻 的形成方式有真空蒸鍍、濺鍍、熱分解、以及電鍍,而常用的電阻材料則包含 有單一成分金屬、合金、及金屬陶瓷三類,又以金屬陶瓷在近年來發展較為熱 門,表3-2為常用之金屬陶瓷材料整理[15]。. 19.

(32) 圖3-1:薄膜電阻製程示意圖. 20.

(33) 表3-2:常用之金屬陶瓷材料整理[15] 體積電阻率. 材料. 成膜方式. (mΩ.Cm ). TCR (10 -6 /℃). Ta 2 N. 濺鍍. 0.3~0.6. -30~-60. Ta-Si-O. 濺鍍. 1.5~30. -500~-. Ta-Ti-N. 濺鍍. 0.05~0.27. +1000~-50. Ta-Au-SiO 2. 濺鍍. 4.3~47. -480~-1390. Ta-Si-O-Ni. 濺鍍. 5~10. -500~-800. Ta-Si-N. 濺鍍. -. -. Ta-Si-C. 濺鍍. 3~15. -600~-2000. Ti-N. 離子鍍. 0.1μm時13 1μm時64. -200~-300. Ti-Si-N. 濺鍍. 0.0004. -20. Ti-Zr-Al-N. 濺鍍. 0.6~7.8. -200~+200. Ti-C-O-N. 濺鍍. 0.6~7.8. -1000~-10000. Ti-Si-O. 濺鍍. 0.1~70. -400~-2400. Ti-Al-C-O. -. 10. -. Ti-B-N-(O). 濺鍍. 15~17. -995. Ti-Al-N-(O). 濺鍍. 12~15. -931. Ti-Al-Si-C-O. 濺鍍. 10. -. Cr-Si-O. 濺鍍. 2~9. -500~-200. Cr-Ti-Si. 濺鍍. 0.06. -. Zr-N. 濺鍍. 0.05~100. +100~-1600. La-Cu-Si-O. 濺鍍. 30. -. 3. 21.

(34) 3-1.2 薄膜電容 金屬-絕緣-半導體薄膜電容由於是利用半導體為底電極,使得電容本身會 有寄生電阻的存在,造成元件的共振頻率降低,無法應用200MHz以以的頻率 範圍,所以高頻的應用就必須要選擇金屬-絕緣-金屬薄膜電容,MIM電容可降 低寄生電阻值,進而提高元件共振頻率,而共振頻率則是取決於介電材料的自 振頻率。相同於薄膜電阻,薄膜電容的電極也要考量其電阻溫度係數 (Temperature Coefficient of Resistance, TCR),且其介電材料尚有電容溫度 係數(Temperature Coefficient of Capacitance, TCC)及介電常數(k)要考 量,其製程示意圖如圖3-2。 另外要注意的是,基材的表面粗糙度應在Ra< 0.3μm以下,若粗糙度過 高,介電層容易被下底電極的突丘(Hill Lock)穿透,形成短路或是造成崩潰 電壓過低的現象[11]。. 圖3-2:薄膜電容製程示意圖. 22.

(35) 3-1.3 薄膜電感 薄膜電感製程較相似於電阻製程,但主要的設計考量在於如何降低其寄 生電容與提高元件的品質因子(Q),由於電感特性必須考慮到降低其直流阻 抗(DC Resistance, RDC),以提高Q值的需求,所以電感導線的膜厚必須要 在5~10μm之間,故製程上通常採用電鍍方式形成電感導線以符合需求。其製 程示意如圖3-3。 基材的表面粗糙度亦會影響薄膜電感的特性,尤其在高頻時,過高的表 面粗糙度容易造成雜訊的升高,造成高頻特性降低,故基材的選擇、製作、及 加工亦會影響到整個薄膜元件的效能。幾種常見的平面電感圖形設計有條狀、 環狀、曲折狀、方形螺旋狀、圓型螺旋狀等,如圖3-4所示。. 圖 3-3:薄膜電感製程示意圖. 23.

(36) 圖 3-4:常見的平面電感圖形設計. 24.

(37) 3-2、整合式被動元件之模型架構 3-2.1 電容與電感剖面尺寸 本研究設計以整合式被動元件(IPD)製程技術為基礎,藉由與國際知名封 測大廠研發與傳統製程高相容性之整合性製程,製造被動元件常見之電容與電 感,相關剖面架構圖與結構尺寸詳細資料如圖 3-5 及表 3-3 所示。. 圖 3-5: 電感器與電容器剖面圖. 表 3-3: 各層尺寸高度 Layer. Thickness. Glass. 700 um. AlCu. 1 um. Ta2O5. 0.25 um. AlCu. 1 um. BCB. 5 um. TiCuCu. 5 um 25.

(38) 3-2.2 電感器模型 研究所用之電感為螺旋線電感器,此電感器之優點為在較少層數使用 下,獲得較大之電感。為了解製程與結構對此電感之影響因素,本研究利用全 波電磁模擬軟體進行電感頻率響應模擬。設計電感器之模型分別如圖 3-6、3-7 所示。. 圖 3-6:EM 全波模擬 3D 圖示. 圖 3-7:2D 電感模型. 26.

(39) 3-3、電感模擬結果比較 3-3.1. 線圈圈數的影響. 電感元件因為圈數越多,螺旋面積越大,對玻璃基板電容效應也愈大,而造成 插入損耗(insertion loss,IL)也越大,如圖3-8,而有效感值(Leff)隨著圈數每增加一 圈,低頻時有效電感值約增加 1 到 2nH ,且電感自振頻率會逐漸變小,這些情況 都是因為寄生電容效應所致,如圖3-9。最大品質因數(Q)會隨著頻率增高有先升後 降的特性產生,影響此效應的因素是因為電感器在較低的頻率下工作時,其輸入阻 抗的虛部是由它的電抗,即電感本身去主宰,但是當工作頻率升高時,相關的寄生 電容效應隨頻率升高而逐漸變大,此電容效應主要是由電感跨接的走線與繞線圈彼 此的電容效應以及對基底的寄生電容等。因此品質因素(Q)在頻率逐漸升高時,自然 會有先上升後下降的趨勢,如圖3-10所示:. 0. (0.64 nH). S21(dB). -5. (1.18 nH). -10. (2.07 nH). N15S10W10R30 N25S10W10R30 N35S10W10R30 N45S10W10R30 N55S10W10R30. -15 -20 -25. 0. 5. (3.35 nH). (5.21 nH). 10. 15. 20. Freq(GHz) 圖 3-8:線圈插入損耗(insertion loss,IL)與頻率關係圖. 27.

(40) 100 (15.4 GHz) (21.75). Leff (nH). 50. N15S10W10R30 N25S10W10R30 N35S10W10R30 N45S10W10R30 N55S10W10R30 (32). 0 (11.4 GHz) (50.5). -50. -100 0. 10. 20. 30. 40. 50. Freq(GHz) 圖 3-9:線圈有效感值(Leff)與頻率關係圖. 40 20. Q. 0 -20. N15S10W10R30 N25S10W10R30 N35S10W10R30 N45S10W10R30 N55S10W10R30. -40 -60 0. 5. 10. 15. Freq(GHz). 圖 3-10:線圈品質因素(Q)與頻率關係圖. 28. 20.

(41) 3-3.2 線距的影響 電感元件線距越大,環繞螺旋面積越大,對玻璃基板電容效應也愈大,而造成 插入損耗也越大,如下圖3-11。線距加大時,金屬環繞而成線圈的總長度會增加, 因而增加有效電感值;若從磁通量的觀點去解釋,則為在固定電流條件下,線距加 大會使得線圈的有效迴路面積變大,因而增加磁通量造成電感器的有效電感值上 升,如圖3-12所示。改變線距時,最大品質因素(Qmax)雖然變動不大,但是還是有 一拋物線之趨勢,其原因是因為當距離較小時,線圈之間的金屬線比較近,彼此耦 合電容效應較強而導致電感的品質因素(Q)值略為變小,然而當線距變大時,線圈彼 此的耦合電容效應變小,但是線圈繞的路徑也相對變長,而使線圈有效迴路面積變 大,產生的電感與基底之間的寄生電容會比較大,在兩項平衡之下,品質因素(Q)值 受到線距影響非常微小,如圖3-13所示。. 2 N35S10W10R30 N35S20W10R30 N35S30W10R30. 0 -2. S21(dB). -4 -6 -8 -10 -12 -14 -16. 0. 5. 10. 15. 20. 25. 30. Freq(GHz) 圖 3-11:線距插入損耗(insertion loss,IL)與頻率關係圖. 29.

(42) 60 40. Leff(nH). 20 0 -20 N35S10W10R30 N35S20W10R30 N35S30W10R30. -40 -60. 0. 5. 10. 15. 20. 25. 30. Freq(GHz) 圖 3-12:線距有效感值(Leff)與頻率關係圖. 40 30 20 10 0. Q. -10 -20 -30. N35S10W10R30 N35S20W10R30 N35S30W10R30. -40 -50 -60 -70 0. 5. 10. 15. 20. 25. Freq(GHz) 圖 3-13:線距品質因素(Q)與頻率關係圖. 30. 30.

(43) 3-3.3 線寬的影響 當線寬增加時,線圈對基底的寄生電容變大,金屬線圈電阻變小,寄生電容對 於整個元件影響性遠大於電阻,所以訊號插入損耗也愈大,如圖3-14。寬度變寬會 使線圈面積變大,因此磁通量也相對變大,與磁通量與有效感值成正比,所以相對 的有效感值(Leff)也變大;又線圈加寬後,電容效應增大,也會造成自振頻率減小的 趨勢,如下圖3-15。品質因素(Q)介於28~34之間,如圖3-16得知改變線寬,品質因 素無明顯的影響。. 0. S21(dB). -10 -20 -30 N35S10W10R30 N35S10W20R30 N35S10W30R30 N35S10W50R30 N35S10W70R30. -40 -50. 0. 5. 10. 15. 20. 25. 30. Freq(GHz) 圖 3-14:線寬插入損耗(insertion loss,IL)與頻率關係圖. 31.

(44) 60 40. Leff(nH). 20 0 -20 -40. N35S10W10R30 N35S10W20R30 N35S10W30R30 N35S10W50R30 N35S10W70R30. -60 -80. 0. 5. 10. 15. 20. 25. 30. Freq(GHz) 圖 3-15:線寬有效感值(Leff)與頻率關係圖. 40 30 20 10. Q. 0 -10 -20 -30 -40. N35S10W10R30 N35S10W20R30 N35S10W30R30 N35S10W50R30 N35S10W70R30. -50 -60 -70 0. 5. 10. 15. 20. 25. Freq(GHz) 圖 3-16:線寬品質因素(Q)與頻率關係圖. 32. 30.

(45) 3-3.4. 電感內徑的影響. 電感內徑變大造就線圈繞線變長,寄生電容也會跟著變大,所以穿透損耗也會 變大,如下圖3-17。而內徑變大將會使自振頻率也變小,可能影響因素應該是當內 徑變大後,繞線總長度變長,所引發的電感與基底之間的電容效應增加,造成電感 的自振頻率的改變,如圖3-18。調整內徑大小對整體的電感元件的品質因素大小沒 有明顯的改變,(Q)值介於29~35之間,但調整內徑時,品質因素有一特性,當內徑 較大的值其(Q)值上升斜率大,(Q)值也較尖銳,效應好,如圖3-19:. 0 -10. S21(dB). -20 -30 -40. N35S10W10R30 N35S10W10R90 N35S10W10R150 N35S10W10R210 N35S10W10R270. -50 -60 0. 5. 10. 15. 20. 25. 30. Freq(GHz) 圖 3-17:內徑插入損耗(insertion loss,IL)與頻率關係圖. 33.

(46) Leff(nH). 120 100 80 60 40 20 0 -20 -40 -60 -80 -100 -120 -140 -160 -180 -200. N35S10W10R30 N35S10W10R90 N35S10W10R150 N35S10W10R210 N35S10W10R270 0. 5. 10. 15. 20. 25. 30. Freq(GHz). Q. 圖 3-18:內徑有效感值(Leff)與頻率關係圖. 50 40 30 20 10 0 -10 -20 -30 -40 -50 -60 -70 -80 -90 -100. N35S10W10R30 N35S10W10R90 N35S10W10R150 N35S10W10R210 N35S10W10R270. 0. 5. 10. 15. 20. Freq(GHz) 圖 3-19:內徑品質因素(Q)與頻率關係圖 34. 25. 30.

(47) 3-4、電容元件 當電容元件由低頻操作到高頻時,其等效電路如圖3-20所示,高頻時電容器除 了電容量以外還有雜散電感(Ls)及等效串聯電阻(r)存在,如方程式(3.1)所列,因為電 容量影響遠大於雜散電感及電阻,所以主要還是電容量所主導,所以電容量大,阻 抗小,又上下極板面積又與電容量成正比,所以面積大者因為阻抗小而穿透損耗小, 而有效電容值又與面積成正比。. 圖 3-20:電容高頻等效電路圖[16]. Zc = r + jω Ls +. 1 jωCs ································································(3.1). 整合式電容主要變數是面積大小去探討其損耗及電容值,而其等效電路也是仿 照電感方式去分析進行,由於構裝基板對於電容之製造除高介電材料因素之外,如 何於有限製程層數限制下,製造高容值之電感是一需要克服之問題。鑒於整合式被 動元件(IPD)製程特性所致,電路設計時通常以大電感為主,小電容為輔,電感通常 會利用結構換層或改變3D模組架構去增加其感值,因為其可利用感值範圍寬、設計 價值相較於電容大,本論文主要以電感為主要研究項目,電容器之研究不在此多加 贅述。. 35.

(48) 3-5、螺旋電感等效電路模型參數之萃取與驗證 被動元件特性與製程結構參數間之關係,可利用電磁模擬結果加以分析比對找 出對應關係,但電磁模擬費時甚多,且對於製程參數結構之系統化分析需建立起 Scalable 程式方可供設計者在設計之初及考慮其不完美效應。本即將以全波電磁模 擬結果為基礎,提出建立寬頻模型之方法。 3-5.1 等效模型推導 圖3-21為本研究根據實際電感製造結構,所建立起之等效模型,模型以Pi型結 構為主,並考慮電感器結構介質與導線於高頻時之集膚效應。[17]. 圖3-21:平面螺旋電感等效電路模型[17]. 其中. Ls:電感自感值。取決於電感繞的圈數。 Rs:電感器的串聯電阻,導線非理想效應所引起之能量損耗。 Cs:為螺旋線電感線圈與線圈間的耦合電容。 Cp1 與 Cp2:螺旋線對基底的寄生電容。 Rp:為元件的高頻損耗電阻值,包含集膚效應與介電質損耗效應。. 36.

(49) 以圖3-21之等效模型及電磁模擬頻率響應為基礎,推導相關公式以求取模型中 之參數值。 1.自感值(Ls)之推導: 電磁模擬結果之反射係數虛部,以公式(3.2)萃取。. Ls =. im(1/ Y (11))1e9 2π f. ································································(3.2). 2. 耦合電容(Cs)之推導: 利用共振時之諧振頻率為電感器等效模型之電容性與電感性所貢獻可求取電容 效應。但在模型之中,主要的電容效應為線圈之互容,接地電容效應先忽略不計, 以公式(3.3)萃取。. Cs =. 1 Lsω 2. ················································································(3.3). 3. 串聯電阻(Rs)與並聯電阻(Rp)之推導: 損耗之等效於模型之中並不容易準確萃取,本模型將損耗歸納為兩個主要,一 為低頻時金屬螺旋電感所造成的電阻,在低頻時,以公式(3.4)萃取;另一為信號電 流之頻率升高時,電流在導體內流通時,因集膚效性(Skin Effect)影響並不均勻地分 佈而是集中於導体之表面。當頻率升高時,導体之表面的電流密度增加,導致導體 表面之損失增加。在高頻時,將公式(3.4)所得的Rs值代入公式(3.5),得以萃取Rp。. Rs = re(. 1 ) Y (11) ··········································································(3.4). Rs + Rp = re[ Z ] = re(. 1 ) Y 11 ················································(3.5). 4. 寄生電容(Cp)之推導: 由圖3-21的等效電路分析,在低頻時將Ls視為短路,Cs視為斷路,Rs值極小視 為短路,Rp極大視為斷路,所得等效電路可近似為圖3-22,再將圖3-22簡化為圖 37.

數據

![表 2-2:HTCC與LTCC之比較[10] 2-3.4 薄膜式被動元件 關於被動元件的整合,因為受限於材料、技術以及經驗等等,發展進度 並不如預期快速,目前技術較為成熟的是利用陶瓷材料,以LTCC的技術將被 動 元 件 整 合 於 基 板 之 內 , 雖 然 陶 瓷 材 料 成 本 並 不 昂 貴 , 但 是 由 於 生 產 費 用 過 高,不易達到降低單價的目標。此外,PCB板上幾乎都採用SMT的技術生產, 隨著元件體積縮小化之後,表面黏著設備不易處理過小元件,例如0402或0201 等等,於是就](https://thumb-ap.123doks.com/thumbv2/9libinfo/8788129.218976/26.892.241.664.140.715/然陶瓷材料成本並不昂貴是由生黏著.webp)

![圖 4-3: 串聯諧振電路的電流與頻率[19] 4-1.2.3 並聯諧振(parallel resonance) 並聯諧振(parallel resonance)時的信號頻率,或稱為反諧振頻率 (antireson-ance frequency) f ,可應用圖 4-4 的電路導出。設一電路為並聯組合時, 0 原則上以導納的型式分析,計算上較為便捷。 如圖 4-4 所示,在 ab 兩端的右邊,為一電容 C、電感 L 及電導 G 的並聯組合。 可得 Yab 為: ( 1 )Y ab G j](https://thumb-ap.123doks.com/thumbv2/9libinfo/8788129.218976/62.892.349.615.106.367/諧振頻率可應用圖電路導出設一電路為兩端右邊為一電容電感及電導.webp)

![圖 4-4: 並聯諧振電路[19] 同時,自(4.10)式可以推知,當 ω ω= r 時,Yab 之值將為最小。當電路為並聯諧 振時,應可取得最大的電阻值(即最小 Yab 值),但是在高於或低於其諧振頻率時, 電阻都將隨之降低。如圖 4-5 所顯示,為並聯電路電阻的頻率響應。在電阻頻率響 應曲線兩側的陡峭程度,或稱為頻寬(即 ω 2 -ω 1 ),是以其在諧振頻率 f (或為 ω r r )兩 側,設為 f 及 1 f (或為2 ω 1 及 ω 2 )的半功率點為量測依據,半功率點(half-pow](https://thumb-ap.123doks.com/thumbv2/9libinfo/8788129.218976/63.892.232.662.103.422/推知當降低如圖所顯示為並聯電路電阻頻率響應在電率響或為ω.webp)

相關文件

Graph Algorithms Euler Circuit Hamilton Circuit.. for Sprout 2014 by Chin

Filter coefficients of the biorthogonal 9/7-5/3 wavelet low-pass filter are quantized before implementation in the high-speed computation hardware In the proposed architectures,

(2) 被動式 RFID Tag(Passive):被動式 RFID Tag 不含電池,其能量是 感應自 RFID Reader 所發射過來的 RF 無線電波能量,當 RFID

According to frequency response, filters can be divided into: (1) low-pass filter, (2) high-pass filter, (3) band-pass filter and band-stop filter.. This paper only chooses

在軟體的使用方面,使用 Simulink 來進行。Simulink 是一種分析與模擬動態

―Low-Temperature Polycrystalline Silicon Thin Film Transistor Nonvolatile Memory Using Ni Nanocrystals as Charge-Trapping Centers Fabricated by Hydrogen Plasma

Direct Digital Frequency Synthesizer has many advantages of faster frequency switching, lower memory size, lower circuit complication, lower noise, higher frequency

以簡單的電路 R、L、C 帶通濾波器(Band pass filter)為例,從李信廷 君[2]的結果發現,如果我們假設三種元件 R、L、C 它們之間的相關 係數ρ RL =0.9,ρ RC

![圖 4-6: 低通(Low Pass)原型濾波器電路圖[20] 圖 4-7: 高通(High Pass)原型濾波器電路圖[20] 如圖 4-8 為三階帶通濾波器電路圖,其轉換原理是由一低通濾波器再加上一並 聯電容和一串聯電感而成,而如圖 4-9 乃是一三階濾波器電路圖,其組成也是由一 二階濾波器再串上一組 LC 諧振器,讓整個訊號衰減更快,訊號完整性更好。根據梯 型濾波器基本架構知道階數越大,其裙擺越陡峭,其衰減越快,當設計階數越多即 需考慮面積問題,並不是階數越高就是越好的濾波器設計,最重要的乃是](https://thumb-ap.123doks.com/thumbv2/9libinfo/8788129.218976/64.892.172.668.107.300/由一低通濾上一並更快訊號完整性更好根據梯型濾波器基本知道乃是.webp)

![圖 4-9: 三階帶通(Band Pass)濾波器原型電路圖[20]](https://thumb-ap.123doks.com/thumbv2/9libinfo/8788129.218976/65.892.141.756.106.315/圖49三階帶通BandPass濾波器原型電路圖2.webp)