國 立 交 通 大 學

電信工程研究所

碩 士 論 文

無合成器之 LINC-OFDM 系統:硬體設計與 FPGA 實現

A Combinerless LINC-OFDM System:

Hardware Design and FPGA Implementation

研究生:林家彰

指導教授:吳文榕 博士

無合成器之 LINC-OFDM 系統:硬體設計與 FPGA 實現

A Combinerless LINC-OFDM System:

Hardware Design and FPGA Implementation

研 究 生:林家彰 Student:Chia-Chang Lin

指導教授:吳文榕 博士 Advisor:Dr. Wen-Rong Wu

國 立 交 通 大 學

電信工程學系碩士班

碩 士 論 文

A ThesisSubmitted to Institute of Communications Engineering College of Electrical and Computer Engineering

National Chiao Tung University In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In

Communications Engineering July 2013

i

無合成器之 LINC-OFDM 系統: 硬體設計與 FPGA 實現

研究生:林家彰 指導教授:吳文榕 博士

國立交通大學

電信工程研究所碩士論文

摘要

正交分頻多工(Orthogonal Frequency Division Multiplexing, OFDM)系統的傳送訊號 有很高的 PAPR(peak-to-average power ratio, PAPR)值,因此其功率放大器(power amplifier, PA)需有較大的線性放大區域使系統能正常操作,造成 PA 為射頻(radiofrequency, RF)電 路中最消耗功率的元件。非線性元件之線性放大(Linear amplification with nonlinear component, LINC)技術為解決此問題的方法之一,LINC 系統可使用效率較好的非線性放 大器進行線性放大。然而,在 LINC 系統中有一關鍵的元件即功率合成器(power combiner), 其設計及實現有很高的難度,為了克服此問題有研究者提出無合成器之 LINC 系統。本 篇論文利用現場可程式規劃閘陣列(Field Programmable Gate Array, FPGA)實現無合成器 之 LINC-OFDM 系統。我們先為無合成器之 LINC-OFDM 系統傳送機與接收機設計低複 雜度的架構。接著我們以硬體描述語言 VHDL 實現傳收機之運作模式,並以暫存器轉移 層級(register transfer level, RTL)模擬驗證設計的正確性。產生的電路再進一步放置和繞 線(place and route),並下載至 FPGA 平台。最後將 LINC-OFDM 訊號透過射頻(Radio Frequency, RF)傳出與收回,確認我們的設計可以正常運作。

ii

A Combinerless LINC-OFDM Systems:

Hardware Design and FPGA Implementation

Student: Chia-Chang Lin Advisor: Dr. Wen-Rong Wu

Institute of Communications Engineering

National Chiao Tung University

Abstract

It is well known that the power amplifier (PA) of OFDM systems must operate in a wide linear region to cope with the high PAPR problem, making it the most power-hungry device in the RF circuit. The linear-amplification-with-nonlinear-component (LINC) technique, allowing the use of nonlinear PAs, has been developed to solve the problem. However, a critical component in LINC transmitter, named power combiner, is difficult to design and implement. A combinerless LINC system is recently proposed to avoid the problem. This thesis considers the implementation of a combinerless LINC-OFDM system with FPGA. We first design low-complexity architectures for a combinerless LINC-OFDM transmitter and receiver. Then, we implement the operations of the transceiver with the VHDL and conduct register transfer level (RTL) simulation to verify the correctness of the design. The resultant circuit is further placed and routed, and downloaded to a FPGA platform. Finally, experiments are conducted to transmit and receive LINC-OFDM signal through radio frequency (RF), confirming that our design can function properly.

iii

誌謝

本篇論文得以順利完成,首先我要感謝我的指導教授吳文榕博士,在研究期間細心 耐心的指導我們做研究,從老師身上學習到了很多做研究的方法與態度,讓我在研究期 間獲益良多。也謝謝口試委員蘇育德教授、李大嵩教授、吳仁銘教授所提供之寶貴意見, 讓本篇論文更加完整。 其次,要感謝寬頻通訊與訊號處理實驗室的鈞陶學長、勝隆學長、汀華學姊和碩二 的同儕運凱、偉豪、侑君、萊恩,在研究及課業學習上不吝指導與鼓勵;同時也感謝實 驗室學弟妹柏豪、佳瑩、家妤、軒平的幫忙,讓這兩年的碩士生活精彩難忘。 最後我要感謝我的父母與哥哥,有你們的關心支持與栽培照顧,讓我在研究期間無 後顧之憂,得以順利完成研究。 感謝這一路上所以給予過幫助以及鼓勵的人。iv

目錄

摘要 ... i 誌謝 ... iii 目錄 ... iv 表目錄 ... vi 圖目錄 ... vi 一、簡介 ... - 1 - 二、LINC 系統介紹 ... - 3 - 2.1 調變訊號在非線性功率放大器下的失真現象 ... - 3 - 2.2 傳統 LINC 系統 ... - 4 - 2.2.1 LINC 系統之原理與架構 ... - 4 - 2.2.2 LINC 訊號拆解 ... - 6 - 2.3 無合成器之 LINC 系統 ... - 9 - 2.4 偵測方法 ... - 10 - 2.4.1 強制歸零(Zero forcing, ZF)等化器 ... - 10 - 2.4.2 修正 ZF 等化器 ... - 11 - 三、LINC-OFDM 傳送機與接收機設計 ... - 13 - 3.1 設計流程與傳收機架構 ... - 13 - 3.2 重要功能區塊 ... - 17 -3.2.1 CORDIC(Coordinate Rotation Digital Computer)演算法 ... - 17 -

3.2.2 快速傅立葉轉換(Fast Fourier transform, FFT) ... - 21 -

3.3 傳送機設計 ... - 22 -

3.3.1 提高取樣(Up-Sampling) ... - 22 -

3.3.2 振幅截切(Amplitude Clipping) ... - 25 -

3.3.3 訊號拆解器(Signal Component Separator, SCS) ... - 28 -

3.3.4 前導訊號(Preamble) ... - 31 -

3.4 接收機設計 ... - 32 -

3.4.1 降低取樣(Down-Sampling) ... - 32 -

v

3.4.3 符元起點估計(Symbol Timing Estimation) ... - 35 -

3.4.4 頻率偏移估計(Frequency Offset Estimation) ... - 36 -

3.4.5 通道響應估測(Channel Estimation) ... - 39 - 3.4.6 MZF 偵測(MZF Detection)... - 40 - 四、模擬 ... - 42 - 4.1 系統效能模擬 ... - 42 - 4.2 硬體設計模擬 ... - 47 - 五、FPGA 實現與測量 ... - 53 - 5.1 平台介紹 ... - 53 - 5.2 FPGA 實現 ... - 55 - 5.2.1 LINC-OFDM 傳送機實現 ... - 55 - 5.2.2 LINC-OFDM 接收機實現 ... - 60 - 5.3 測量結果 ... - 64 - 六、結論 ... - 70 - 參考文獻 ... - 72 -

vi

表目錄

表 3.1 二階多項式逼近: 係數表 ... - 30 - 表 4.1 LINC-OFDM 系統模擬環境參數 ... - 42 -圖目錄

圖 2.1 LINC 系統架構圖 ... - 4 -圖 2.2 Hybrid power combiner ... - 5 -

圖 2.3 Chireix power combiner ... - 6 -

圖 2.4 訊號拆解示意圖 ... - 7 - 圖 2.5 IQ 法訊號拆解圖 ... - 8 - 圖 2.6 2X1 LINC 系統架構 ... - 9 - 圖 2.7 2X2 LINC 系統架構 ... - 9 - 圖 3.1 設計流程圖 ... - 14 - 圖 3.2 傳送機架構方塊圖 ... - 15 - 圖 3.3 接收機架構方塊圖 ... - 16 - 圖 3.4 遞迴 CORDIC 架構圖 ... - 20 - 圖 3.5 平行 CORDIC 架構圖 ... - 20 - 圖 3.6 Xilinx FFT v7.1 模組 ... - 21 - 圖 3.7 Xilinx FFT v7.1 操作時序圖 ... - 22 - 圖 3.8 傳送機架構方塊圖 ... - 22 - 圖 3.9 時域平方根升餘弦濾波器 ... - 23 - 圖 3.10 頻域平方根升餘弦濾波器 ... - 23 - 圖 3.11 (a) 直接型式, (b) 轉置型式 ,(c) 混合形式 ... - 24 - 圖 3.12 多項濾波器概念圖 ... - 25 - 圖 3.13 多項濾波器架構圖 ... - 25 - 圖 3.14 振幅縮減器方塊圖 ... - 26 - 圖 3.15 範圍(Segment)判定區塊架構圖 ... - 27 - 圖 3.16 二分法線性逼近架構圖 ... - 27 - 圖 3.17 SCS:相位法方塊圖 ... - 28 -

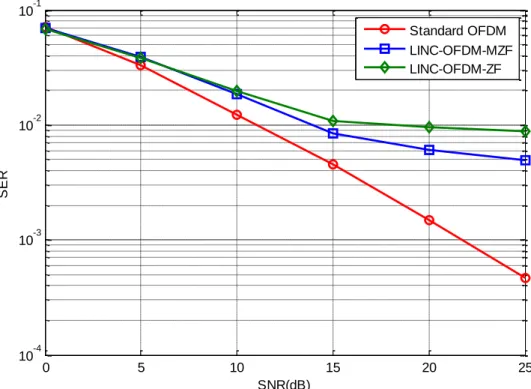

vii 圖 3.18 SCS:IQ 法方塊圖 ... - 28 - 圖 3.19 OFDM 符元之振幅統計分析 ... - 29 - 圖 3.20 SCS 錯誤向量曲線圖 ... - 30 - 圖 3.21 錯誤因子內插法架構圖 ... - 30 - 圖 3.22 SCS :改良後的 IQ 法方塊圖 ... - 31 - 圖 3.23 前導訊號 ... - 31 - 圖 3.24 接收機架構方塊圖 ... - 32 - 圖 3.25 降低取樣架構圖 ... - 33 - 圖 3.26 封包偵測基本架構圖 ... - 34 - 圖 3.27 移動窗戶架構圖 ... - 34 - 圖 3.28 改良後之封包偵測架構圖 ... - 35 - 圖 3.29 符元起點估計架構圖 ... - 36 - 圖 3.30 頻率偏移補償方塊圖 ... - 38 - 圖 3.31 Coarse/Fine Estimation 硬體架構圖 ... - 38 - 圖 3.32 Angle Accumulator 架構圖 ... - 39 - 圖 3.33 通道響應估測架構圖 ... - 40 - 圖 3.34 訊號等化架構圖 ... - 40 - 圖 4.1 DMA 架構圖 ... - 43 - 圖 4.2 LINC-OFDM 系統 ZF 與 MZF 等化器效能(PER) ... - 44 - 圖 4.3 系統封包遺失率 ... - 44 - 圖 4.4 LINC-OFDM 系統 ZF 與 MZF 等化器效能(SER) ... - 45 -

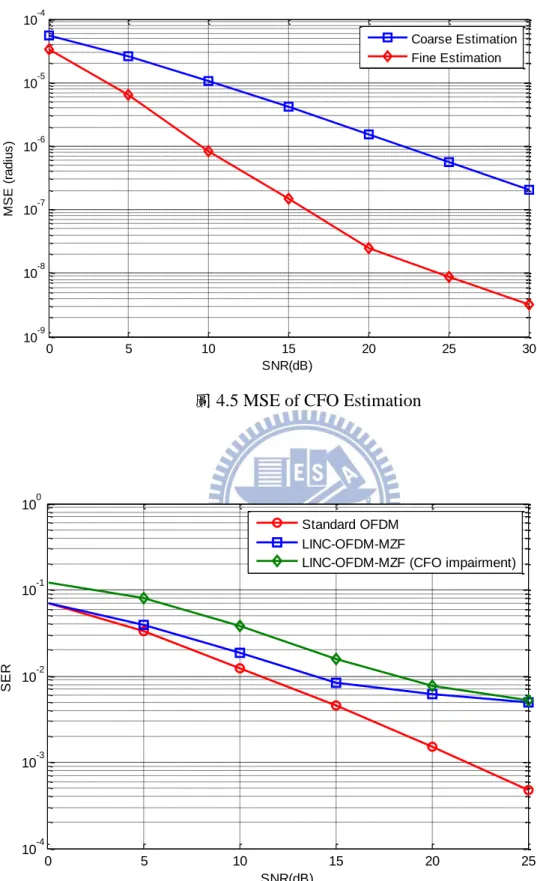

圖 4.5 MSE of CFO Estimation ... - 46 -

圖 4.6 LINC-OFDM 系統效能: 頻率偏移效應 ... - 46 -

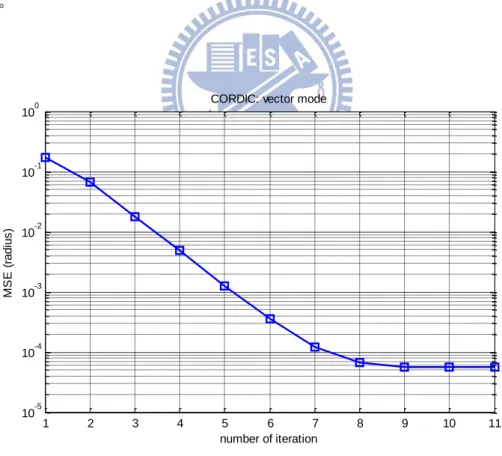

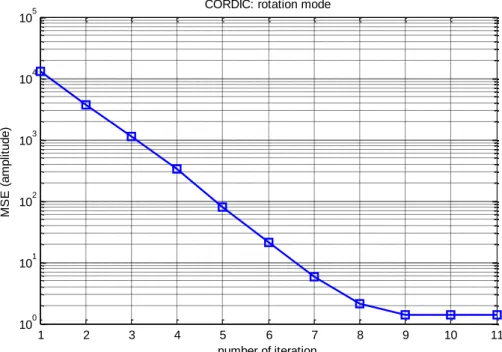

圖 4.7 MSE of CORDIC Vector mode ... - 47 -

圖 4.8 MSE of CORDIC Rotation mode ... - 48 -

圖 4.9 LINC-OFDM 系統效能: Amplitude Clipping ... - 49 -

圖 4.10 傳送端原始訊號星座圖 ... - 49 - 圖 4.11 傳送端訊號縮減星座圖(浮點數運算) ... - 50 - 圖 4.12 傳送端訊號縮減星座圖(定點數運算) ... - 50 - 圖 4.13 錯誤訊號之訊號與近似誤差比 ... - 51 - 圖 4.14 理想浮點數 SCS 輸出 ... - 51 - 圖 4.15 近似定點數 SCS 輸出 ... - 51 -

viii 圖 5.1 完整平台 ... - 53 - 圖 5.2 連結介面 ... - 53 - 圖 5.3 FPGA 開發版 ... - 54 - 圖 5.4 RF 模組 ... - 55 - 圖 5.5 傳送機控制狀態 ... - 56 - 圖 5.6 傳送機 RTL 架構圖 ... - 57 - 圖 5.7 傳送機 mapping-report ... - 58 - 圖 5.8 傳送機 timing-report ... - 59 - 圖 5.9 傳送機 static timing ... - 59 - 圖 5.10 傳送機 RTL 模擬測試 ... - 59 - 圖 5.11 RTL 模擬: 傳送機 ... - 60 - 圖 5.12 接收機 RTL 架構圖 ... - 61 - 圖 5.13 接收機 mapping-report ... - 62 - 圖 5.14 接收機 timing-report ... - 63 - 圖 5.15 接收機 static timing ... - 63 - 圖 5.16 ping-pong buffering ... - 63 - 圖 5.17 接收機 RTL 模擬測試 ... - 64 - 圖 5.18 RTL 模擬:接收機 ... - 64 - 圖 5.19 傳送機電纜測試 ... - 65 - 圖 5.20 傳送機天線測試 ... - 65 - 圖 5.21 傳送機 TX1 訊號(電纜) ... - 66 - 圖 5.22 傳送機 TX2 訊號(電纜) ... - 66 - 圖 5.23 傳送機訊號(天線)... - 67 - 圖 5.24 天線擺設位置 ... - 68 - 圖 5.25 接收機控制模組 flag 訊號 ... - 68 - 圖 5.26 接收機偵測訊號星狀圖 ... - 69 -

1

一、 簡介

隨著無線多媒體的蓬勃發展,行動裝置對資料傳輸率的需求大幅增加,頻譜的使用 效率對一個無線通訊系統而言變得格外重要,然而無線通訊系統的頻寬卻是有限的,為 了有效的使用頻寬,新一代無線通訊系統大都採用正交分頻多工(Orthogonal Frequency Division Multiplexing, OFDM)的調變技術來取代原有的單載波系統,相較於單載波系統, OFDM 在有限的頻寬下,將資料同時載在多個子載波(sub-carrier)上,每個子載波彼此互 相正交,頻譜使用效率較高。在 OFDM 調變技術中因為將通道分為多個子載波,因此可以將一頻率選擇性(frequency-selective) 衰落通道轉換成多個平坦(flat)衰落通道的集合,在接收端僅需針對每個子載波做簡單的 等化,降低接收端通道等化器之複雜度。 在 無 線 通 訊 系 統 中 , 系 統 的 功 率 消 耗 是 很 重 要 的 設 計 考 量 , 而 在 射 頻 (Radio Frequency, RF)電路中的功率放大器往往是最消耗功率的元件。功率放大器的操作點必須 落在線性區才能使的訊號不會產生失真的現象,但功率放大器其線性放大區域有一定範 圍,當訊號振幅大於某一範圍就進入飽和區,在飽和區訊號會因非線性放大而失真,為 了不讓訊號失真,線性區域就需放大,因而造成功率放大器的損耗功率變大。 雖然 OFDM 可實現大量資料傳輸,但是因為 OFDM 調變技術是由多個正交的子載 波訊號所疊加而成,使得 OFDM 發射訊號之峰均功率比(Peak-to-Average Power Ratio, PAPR)較單載波訊號大很多,高 PAPR 值會降低功率放大器的效能,使得訊號失真。若 要避免訊號失真則需要高線性度的功率放大器,高線性度的功率放大器會使得損耗功率 變大,相較於單載波系統,OFDM 的功耗高出許多,因此 OFDM 的功耗問題一直是個 有待解決的難題。

LINC(Linear amplification with nonlinear component)[1]為解決高 PAPR 系統功耗問題 的一種技術,它可以藉由高效率的非線性功率放大器來進行訊號的線性放大,使得發射 器能同時達到高效率及高線性度的效果,LINC 的基本原理是將其輸入訊號分解成兩個

2 (或兩個以上)的固定波包(constant envelope)的訊號,因為是固定振幅所以這些訊號可以 經由非線性功率放大器來放大,放大後的訊號再經由功率合成器(power combiner)加以合 成,由天線發送出去。功率合成器是影響 LINC 系統整體效能一個很重要的因素。在 LINC 系統中常用的功率合成器形式有混合合成器[2]、Chireix 合成器[3]、Wilkinson 合成器[4] 等架構。然而這些架構在實際的實現上都有缺點,造成 LINC 系統所減少的功率耗損不 如預期的多。 LINC 系統最大的挑戰即為功率合成器的實現,Abdelaal[5]因此提出了一種合成的 方法能夠完成避免使用合成器,主要的想法是讓兩個非線性功率放大器後的訊號在空中 結合,使接收端收到的是結合後的 LINC 訊號。為了訊號的接收,Abdelaal 做了一個假 設,他假設兩個傳送天線非常接近,因此兩個通道的響應可以視為相同,如此一來接收 到的訊號即為兩個訊號相加,但是在實際的情況,通道是不會完全相同的。而在 OFDM 系統中,由於多載波的特性,使得在時域的通道響應的一些微差異,也會造成子載波通 道的響應產生很大的不同。為了克服通道的差異,[6]提出利用空時編碼的作法將拆解後 的兩個訊號分做兩個時間在兩根天線傳送,如此一來即可解決[5]中通道必須相同的限制, 但其代價是傳輸率減半。[7]則針對無合成器 LINC-OFDM 系統,利用最大相似(Maximum Likelihood, ML) 的 偵 測 方 法 , 克 服 通 道 差 異 所 造 成 的 效 能 損 耗 , [8] 提 出 編 碼 的 LINC-OFDM 系統架構以及相關的偵測演算法,能改善[7]複雜度太高的缺點。本論文針 對無合成器之 LINC-OFDM 系統,設計並實現傳送機與接收機,我們將對各個功能方塊 的硬體架構提出構想,以硬體描述語言實現並使用電腦輔助設計軟體來模擬之。 本論文的章節編排如下,第二章介紹 LINC 系統,第三章為 LINC-OFDM 系統傳送 機與接收機的設計,第四章為模擬結果,包含了浮點數系統模擬以及硬體設計的模擬, 第五章為 FPGA 實現與測量結果,第六章結論。

3

二、LINC 系統介紹

2.1 調變訊號在非線性放大器下的失真現象

考慮一典型的通訊系統,其調變訊號一般可表示如下 x t( )a t( )cos[

ct

( )]t (2.1) 其中a t

( )

為訊號波包(envelope),若a t

( )

為常數 A ,則為固定波包,

c( )t 為訊號 頻率(frequency),

( )

t

為訊號相位(phase)。當調變訊號經過非線性功率放大器,變動 波包與固定波包會得到不一樣的結果,我們可以使用三階多項式來近似一非線性功率放 大器,假設其輸入輸出關係表示如下 3 2 1 ( ) 2 ( ) 1 ( ) 4 out in in in v G v t G v t G v t G (2.2) 其中vout( )t 為輸出訊號,v tin( )為輸入訊號,G1到G4為放大器係數。將固定波包調 變訊號x t

( )

帶入此功率放大器,可得輸出訊號y t

( )

如下

3 2 1 2 1 4 3 3 2 2 1 2 3 4 3 2 1 2 3 4 3 1 3 ( ) ( ) ( ) ( )cos ( ( )) cos ( ( )) cos( ( )) cos(3 3 ( )) cos( ( )) 1 cos(2 2 ( ))

4 2 cos( ( )) cos( ( ) 4 c c c c c c c LPF c y t G x t G x t G x t G G A t t G A t t G A t t G G A G A t t t t t t G A t t G G A G A t t

2 2 4 ) 2 G A G (2.3) 若此功率放大器的特性曲線通過原點,則G4 0,將經過功率放大器得到的訊號再通過 一低通濾波器(low pass filter, LPF),將高頻訊號濾掉,從(2.3)我們可以知道,輸出與輸 入訊號為線性的關係,因此固定波包的訊號經過非線性的放大不會有失真。4

3 2 1 2 1 4 3 3 2 2 1 2 3 4 3 2 1 2 3 4 3 1 ( ) ( ) ( ) ( )( ) cos ( ( )) ( ) cos ( ( )) ( ) cos( ( ))

( ) ( )

cos(3 3 ( )) cos( ( )) 1 cos(2 2 ( ))

4 2 ( ) cos( ( )) ( ) 4 c c c c c c c LPF y t G x t G x t G x t G G a t t t G a t t t G a t t t G G a t G a t t t t t t t G a t t t G G a t 2 2 3 4 ( ) ( ) cos( ( )) 2 c G a t G a t t t G (2.4) 從(2.4)我們可以知道,訊號經過低通濾波器後,輸出訊號包含 3 ( ) a t 項,與輸入訊號呈 現非線性的關係,造成輸出訊號失真。由以上兩種輸入訊號性質可知,固定波包的訊號 可以使用非線性功率放大器,而變動波包的訊號則不可。

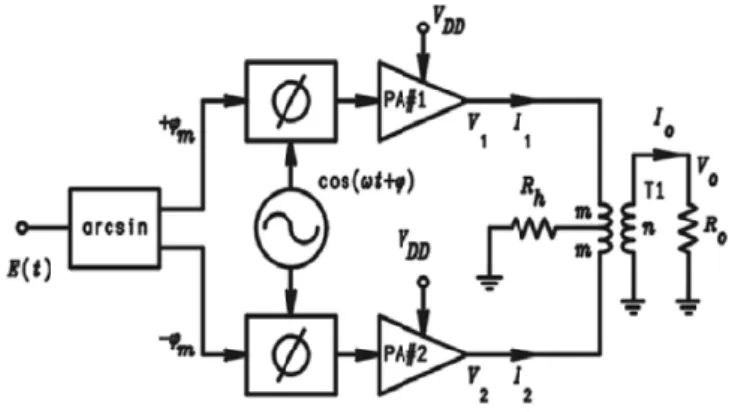

2.2 傳統 LINC 系統

圖 2.1 LINC 系統架構圖 2.2.1 LINC 系統之原理與架構 傳統的 LINC 架構圖如圖 2.1 所示。基本原理[1]是將一個波包及相位都為時變(time varying)的輸入訊號,經過訊號分解器(Signal Component Separator, SCS)拆解成兩個固定 波包之相位調製訊號,兩個固定波包的訊號之間僅存在一個相位差。因此這兩個相位調 製訊號可以經由非線性功率放大器(Non-linear Power Amplifier)進行放大,最後兩個經過 功率放大器的訊號再由功率合成器(Power Combiner)結合,重建出功率放大後具有時變 波包之射頻調製訊號。其中輸出的訊號視為輸入訊號的線性放大結果。所使用的兩個功5 率放大器為非線性放大器,利用非線性放大器而得到線性放大的輸出結果,可以有效提 升系統的效能。 LINC 系統的架構主要分為四個部分,第一部分為訊號分解器,將輸入的基頻訊號 拆解成兩個具有固定波包性質之相位調製訊號。第二部分是對相位調製訊號做調變,將 原本拆解後基頻(baseband)或中頻(IF)的訊號調變至射頻(RF)訊號。第三部分為功率放大 器,傳統的功率放大器是線性,但是效能較差,由於第一部分已將訊號拆解為固定波包, 所以在此可以使用非線性的功率放大器來提升整個系統的功率效能。第四部份為功率合 成器,將功率放大器的輸出由射頻電路做相加以重建訊號,若直接將兩路功率合成器的 輸出做連接,當其中一路的電壓改變時,造成另一路所看到的負載阻抗(load impedance) 隨之改變,因此兩路訊號必須能正確地相互抵銷,才得以重建出輸入的訊號,以下將介 紹不同的功率合成器。

第一種功率合成器為複合式功率混合器(Hybrid power combiner)[2],如圖 2.2 所示, 此類型混合器讓負載阻抗維持固定,分隔(isolate)兩個功率放大器。將兩個相位調製訊號 間的相同項合成至天線輸出,而相差項傳送至終端的負載電阻器(load resistor)以熱能的 形式釋放。雖然此混合器可以保證輸出訊號的振幅有良好的線性度,但是因為部分能量 的損失而降低了功率效能,此類型功率合成器稱為有耗能(lossy)合成器。

6

第二種功率合成器為 Chireix power combiner[3],如圖 2.3 所示,在合成前加入並聯 電抗(shunt reactance)用來避免在特定振幅發生漏電抗(leakage reactance)的情形。此機制 可以提升功率效能,又稱無耗能(lossless)合成器。但是此類型的功率合成器的兩個輸入 沒有隔離電阻,會造成耦合(couple),使得輸出訊號線性度較複合式混合器來得差。

圖 2.3 Chireix power combiner

雖然上述的幾種合成器各有其優點,但仍然存在不可忽視的缺陷例如電路損耗 (circuit losses)以及不匹配損耗(mismatch losses)的問題,要設計出高功率效能以及高線性 度的合成器仍然是一個困難的課題。因此,本篇論文討論使用無合成器(combinerless)的 LINC 系統來解決合成器的問題。 2.2.2 LINC 訊號拆解 將 LINC 訊號分解器的輸入訊號假設為一實數訊號如下 ( ) ( )cos( c ) s t A t

t (2.5) 其中波包A t

( )

0

,將A t

( )

以下式代換 ( ) msin ( ) A t A

t (2.6) 1 ( ) ( ) sin ( ) m A t t A

(2.7) 其中Am為A t

( )

的最大值,因此決定了

( )

t

,代換之後可拆解如下7

1 2 1 2 ( ) sin( ( )) sin( ( )) 2 ( ) ( ) ( ) sin( ( )) 2 ( ) sin( ( )) 2 m c c m c m c A s t t t t t s t s t A s t t t A s t t t

(2.8) 經過拆解後的s t1( )及s t2( ),可以表示為固定波包的向量,並且在順時針及逆時針 的方向分別旋轉一個角度

( )

t

,如圖 2.4 所示,因為訊號已拆解成兩固定波包訊號s t1( ) 及s t2( ),所以可以分別使用非線性放大器。假設放大器的放大增益為G

,則輸出結果可 表示如下 1( ) 2( ) msin ( )cos( c ) ( ) Gs t Gs t GA

t

t Gs t (2.9) 如(2.9)所示,可以得到線性放大的結果。 圖 2.4 訊號拆解示意圖 若將輸入訊號寫成複數訊號的通式如下 ( ) ( )cos( c ( )) s t A t w t

t (2.10) 其中波包A t

( )

0

,將A t

( )

利用(2.6)及(2.7)代換後可得

1 2 1 2 ( ) sin( ( ) ( )) sin( ( ) ( )) 2 ( ) ( ) ( ) sin( ( ) ( )) 2 ( ) sin( ( ) ( )) 2 m c c m c m c A s t t t t t t t s t s t A s t t t t A s t t t t

(2.11)8 因為輸入為複數訊號,(2.10)之輸入訊號可以改寫如下 2 2 1 ( ) ( ) ( ) ( ) ( ) tan ( ) A t I t Q t Q t t I t

(2.12) 上式中I t

( )

為訊號的實部,Q t

( )

為訊號的虛部。在座標平面中,對任一複數基頻訊號( )

( )

( )

s t

I t

jQ t

,一樣可拆解為兩個複數訊號s t1( )和s t2( ),兩個複數訊號有相同的 振幅 2 m A , 2 m A 為一個常數值,且s t( )s t1( )s t2( )。拆解訊號的方法有相位調變(phase modulation)法以及 IQ(in phase/quadrature phase)法。相位調變法即利用(2.12)求得,由(2.7) 求得相位

( )

t

,拆解後兩訊號的相位為

( )

t

( )

t

和

( )

t

( )

t

。而 IQ 法是先計算錯誤 訊號e t

( )

,再求s t1( )和s t2( ),e t( )、s t1( )、s t2( )之間的關係如圖 2.5 所示,推導結果如下 2 2 ( ) ( ) 1 ( ) m A e t js t s t (2.13) 拆解後的兩訊號可以表示為

1 1 1 2 2 2 1 ( ) ( ) ( ) ( ) ( ) 2 1 ( ) ( ) ( ) ( ) ( ) 2 s t I t jQ t s t e t s t I t jQ t s t e t (2.14) 圖 2.5 IQ 法訊號拆解圖9

2.3 無合成器之 LINC 系統

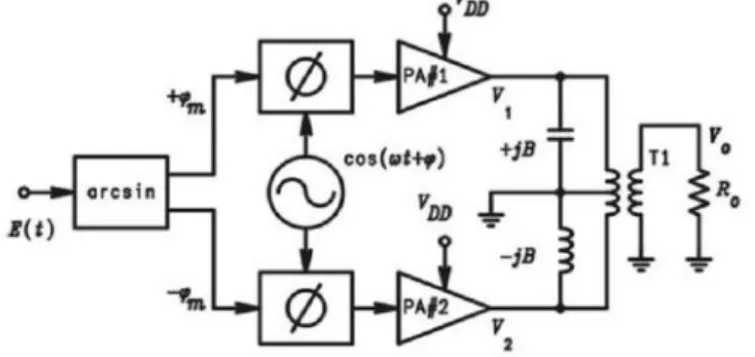

傳統的 LINC 系統是將輸入訊號拆解成兩個固定波包的訊號以克服線性功率放大器 的低效能度問題,因此 LINC 使用兩個非線性功率放大器以達到較高效能,得到線性放 大的輸出。但 LINC 系統的問題在於高效能的功率合成器不容易實現。因此[5]提出無功 率合成器的方法,在此稱之為無合成器之 LINC 系統。此系統將功率放大器的輸出視為 傳送端,兩個固定波包訊號透過兩根天線來傳送,經過兩個通道由接收端接收,因此兩 個拆解後的訊號在空間中自然合成。假設兩根天線距離非常靠近,兩個通道可視為相同, 接收到的訊號即可視為功率放大器輸出的兩個訊號經合成後再經過通道,如此可以免去 傳統 LINC 系統在功率合成器設計上的問題。在無合成器的系統中,傳送之前必須要加 入濾波器,因為兩個固定波包的訊號不一定符合傳送頻帶的限制。 圖 2.6 2x1 LINC 系統架構 圖 2.7 2x2 LINC 系統架構圖 2.6 為 2x1 無合成器 LINC 系統架構,數位訊號模組(Digital Signal Processing, DSP) 將傳送的訊號拆解後經過濾波器/調變器,再經過功率放大器放大後傳送。[5]也提出極 化天線的系統架構如圖 2.7 所示,接收端為兩根天線,形成一類似 22 的 MIMO 系統,

10 如此一來可以避免兩根傳送天線之間的干擾,並且可以允許兩個通道不必相同。[5]的模 擬結果證實 21 和 22 無合成器 LINC 的系統效能較比起傳統 LINC 系統有大幅的提 升。

2.4 偵測方法

2.4.1 強制歸零(Zero Forcing, ZF)等化器令 s 表示一 OFDM 符元在時域(time domain)上的訊號,如前所述,LINC 系統將傳

送的訊號 s 在時域拆解成s 及1 s 如下 2 1 2 1 ( ) 2 1 ( ) 2 s s e s s e (2.15) 2 2 (0) 1 ,..., ( 1) 1 0 1 T m m A A js js N s s N e ( ) ( ) (2.16) 其中 N 為子載波個數,在 LINC-OFDM 系統中,因為 OFDM 的符元定義在頻域(frequency

domain),因此在接收端會將接收到的訊號轉至頻域,令s p 及1( ) s p 為一子載波的兩個2( ) 頻域訊號,h p 及1( ) h p 為相對應的通道頻率響應, ( )2( ) y p 為接收訊號,p為載波的指標 (index),則接收訊號表示如下 1 1 2 2 ( ) ( ) ( ) ( ) ( ) ( ) y p h p s p h p s p n p (2.17) 等化器的目的是求出原始的傳送訊號s p( )s p1( )s p2( ), ZF 等化器目的是要完全補償 通道效應,在此我們假設h p 及1( ) h p 很相近但不完全一樣,因此我們取2( ) h p 及1( ) h p2( ) 的平均值做為等效的通道響應hZF( )p

h p1( )h p2( ) / 2

,利用此通道響應來作等化可得 等化後的訊號如下

1 ˆ( ) ZF( ) ( ) s p h p y p (2.18)11 ZF 等化器作通道補償因不考慮雜訊因素,所以等化後有雜訊放大的問題,另外因為h p1( ) 及h p 不完全相等,等化後會產生一干擾項,表示如下 2( )

1 2

1 2 2 1 1 2 ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) 2 2 ZF Interference y p h p s p s p h p h p h p h p s p s p n p (2.19) 值得注意的是此干擾項與雜訊無關,拆開後的訊號轉至頻域後s p 及1( ) s p 可能有很大2( ) 的振幅,意即h p 及1( ) h p 的差異即使很小也可能產生很大的干擾。 2( ) 2.4.2 修正 ZF 等化器 為了避免(2.19)所提到的干擾項嚴重影響到接收訊號,[8]提出一修正的 ZF 等化器, 將(2.16)代入(2.15)得到訊號在時域的表示式如下 1 2 2 2 1 ( ( )) 2 1 ( ( )) 2 ( ) 1 ,..., 1 (0) ( -1) T m m j j A A diag s s N s I C s s s I C s s C s (2.20) 其中 N 為子載波個數,C(s)為一對角矩陣,將一個 OFDM 符元訊號表示成矩陣的型式, 接收到的訊號(2.17)可以表示如下

1 1 2 2 1 2 1 2 signal interference 1 ( ) 2 2 H F F j F s F y H s H s n H H s H H C s n (2.21)(2.21)中 F 及F 分別代表離散傅利葉轉換(Discrete Fourier Transform, DFT)和反離散H

傅利葉轉換(Inverse Discrete Fourier Transform, IDFT),H 和1 H 為對角矩陣,對角線上2

12

時,干擾項會存在,因為C s( )項的值恆正,因此可得知(2.21)干擾項的平均值為正。當H1

與H 是兩個高相關性通道時,(2.21)有高的訊號對干擾比值(Signal to Interference Ratio, 2

SIR)。當H 與1 H 相關性降低時,(2.21)的訊號對干擾比值亦漸降低。若能將(2.21)干擾2 項的平均值扣除,可以讓干擾項變成零平均(zero-mean)訊號,則干擾項的影響將可降低。 [8]的做法是使用一參數0,假設此參數可以近似C( )s 的平均值,(2.21)可改寫如下

1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 new interference new signal 1 (s) 2 2 1 ( ) 2 2 ( (s) - ) 2 1 ( (s) - ) 2 2 2 H H H H j F F j F F j F F j j F F y H H s H H C s n H H s H H I s H H C I s n H H H H s H H C I sn (2.22) 我們將修正(modified)的 ZF 等化器縮寫為 MZF,因此定義 MZF 為

1 2

1 2

1 ( ) ( ) ( ) ( ) ( ) 2 2 MZF j h p h p h p

h p h p (2.23) 以 MZF 等化後的訊號可表示如下

1 ˆ( ) MZF( ) ( ) s p h p y p (2.24)13

三、LINC-OFDM 傳送機與接收機設計

3.1 設計流程與傳收機架構

我們使用電腦輔助工具來模擬硬體實現,設計流程如圖 4-1 所示。設計流程主要 分成硬體和軟體二部分,軟體使用 Matlab 模擬而硬體使用 ModelSim 及 Xilinx ISE 模擬。 Matlab 模擬包含了浮點數(floating point)的模擬及定點數(fixed point)的模擬。浮點數的系 統模擬可以檢查各功能方塊的正確性和設定參數,也可以評估系統的效能,而定點數的 系統模擬,用來決定各個訊號所需要的表示位元數,並試著將位元降低至容許的效能, 各個訊號表示位元數確定之後,便進入硬體實現模擬。

硬體實現模擬流程中,要先確定每個功能方塊的硬體架構,我們以硬體描述語言 VHDL 描述這些功能方塊,使用 Modelsim 或 Xilinx Isim 做硬體的行為模擬(Behavior simulation),此一步驟會參照由 Matlab 定點數的系統模擬所產生的數據,來幫助驗證 VHDL 功能方塊的正確性。當硬體的行為模擬正確之後,使用 Xilinx ISE 14.2 加入 Spartan6 XC6SLX150 的 library 將 VHDL 程式碼轉為 RTL (register transfer level),合成完 之後再做轉換(translate)、對應(map)、布置及繞線(place and route),接下來就可做時序模 擬(timing simulation),模擬電路所造成的邏輯延遲及繞線延遲是否達到我們要求的操作 速度。在此便完成了所有的硬體模擬。

14 圖 3.1 設計流程圖 Funtional Simulation Matlab Fixed point Simulation Matlab Hardware Architecture Design Behavior Simulation VHDL Modelsim/Isim Synthesis Translate、Map、 Place and route

Timing Simulation Xilinx Spartan6 XC6SLX15 0 Library

15

圖 3.2 傳送機架構方塊圖

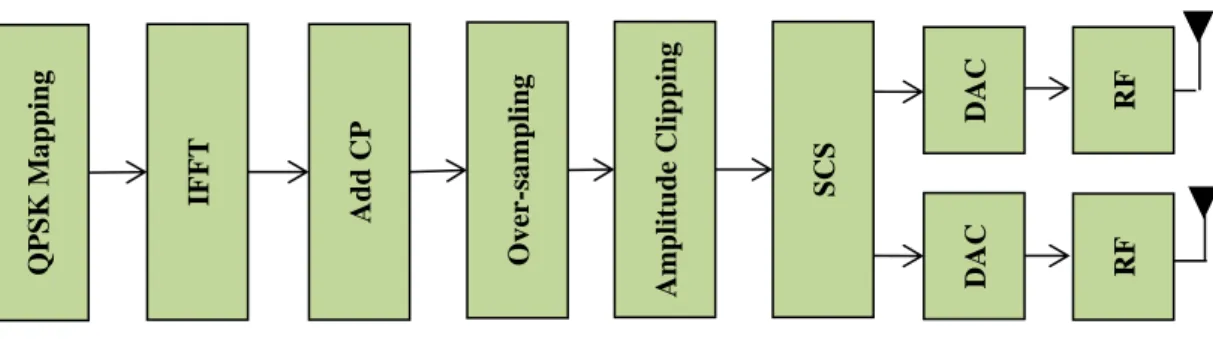

傳送機架構如圖 3.2 所示,接下來會先對傳送機架構做簡述。一開始要將位元(bit) 映射(mapping)到符元(symbol),產生 OFDM 頻域的子載波訊號,接下來做 IFFT 運算, 將訊號轉變為時域的 OFDM 符元,並在前端加上循環前綴(Cyclic Prefix, CP),以避免符 元間互相干擾(Inter Symbol Interference, ISI)。接著,透過將訊號補零(pad zero)和濾波 (filtering)來提高取樣頻率。在訊號進入 SCS 之前,我們必須訂出一個訊號的最大振福, 讓訊號進入 SCS 運算後可正常運作,超過最大振幅即保留訊號相位並縮減至規範的最大 振幅,如此也可以降低峰均功率比(Peak-to-Average Power Ratio, PAPR),因此我們需要 振幅縮減器。最後將訊號通過 SCS,將訊號由變動波包拆解成兩個固定波包訊號。由 SCS 輸出的訊號經過數位轉類比轉換器(Digital to Analog Converter, DAC),然後再將基 頻訊號載至射頻,由天線送出。 Q P SK M a pp ing IF F T Add CP Ampl it u de Clip pin g O v er -s a mp lin g SCS DAC DAC RF RF

16 圖 3.3 接收機架構方塊圖 本篇論文的接收機主要針對訊號同步的問題做處理,架構流程參考 802.11a 的系統 架構[9],接下來會先對接收機架構做簡述。OFDM 技術解決了訊號在多重路徑通道 (multipath channel)中,因通道產生的延遲所造成的困擾。但在通道效應的處理之前,我 們需要先作時間和頻率的同步。時間同步除了封包偵測之外,還需要做符元時序的估計, 確保我們將正確而不受其他符元干擾的取樣值做 FFT。而傳送機與接收機之間的頻率不 匹配,會造成載波間的相互干擾(Inter Carrier Interference, ICI),為了保持載波間的正交 性,需做頻率同步將偏移的頻率估計與補償。做完同步運算後接下來是利用 FFT 將訊號 轉至頻域,以進行通道效應估測與訊號偵測,本論文的偵測方法使用了 2.4.2 所提到改 良後的 MZF 偵測來實現。

接下來我們將介紹無合成器之 LINC-OFDM 傳收機(2x1)的硬體設計,章節 3.2 我們 會先對傳送機與接收機皆有使用到的重要功能區塊做介紹,章節 3.3 介紹傳送機架構的 硬體設計,章節 3.4 則介紹接收機架構的硬體設計。 Pa cket Det ect io n Co a rse CF O E st . F ine C F O E st . Sy mb o l Ti min g Remo v e CP FFT Cha nn el E st ima tio n M Z F Det ect io n Do wn -s a mp li ng ADC RF

17

3.2 重要功能區塊

3.2.1 CORDIC(Coordinate Rotation Digital Computer)演算法

CORDIC 是一種旋轉相關的的低複雜度演算法[10],它可以用來計算三角函數、乘 法、除法等等。在本篇論文中,主要是拿來計算反正切函數(Arctangent)和相位的旋轉。 此演算法利用反覆做角度的向量旋轉,最後以移位器和加法器來實現。CORDIC 演算法 的運作,一般說來可以分為兩種模式,一種叫做旋轉模式(Rotation Mode),另一種則是 向量模式(Vector Mode)。這兩種模式在本論文的實現中都會用到。旋轉模式是將輸入向 量旋轉一個給定的角度,向量模式則是將原本輸入的向量,反覆旋轉至 x 軸上,藉此得 到原本向量的角度。 旋轉模式 在旋轉模式中,我們先讓角度累加器 z 的初始值為欲旋轉的角度,並在每次的疊代 當中,試圖讓角度累加器的值為零。旋轉模式的數學式如下 1 1 1 1 2 2 tan (2 ) 1 0 , 1 0 i i i i i i i i i i i i i i i i i i x x y d y y x d z z d where d if z d if z (3.1) 本論文中我們會利用旋轉模式來做為頻率補償及震幅縮減的旋轉。當疊代的次數夠多時, 上式可轉變為 0 0 0 0 0 0 0 0 0 2 ( cos( ) sin( )) ( sin( ) cos( )) 0 1 2 n n n n i n n x A x z y z y A x z y z z A

(3.2)18 向量模式 在向量模式中,CORDIC 試著將輸入訊號旋轉至 x 軸上,我們可以透過這樣的機 制,得到原本輸入訊號的相位與振幅。與旋轉模式不一樣的地方在於疊代y 的值會趨近i 於 0,因此會由y 來決定旋轉的方向。向量模式的數學式如下, i 1 1 1 1 2 2 tan (2 ) 1 0 , 1 0 i i i i i i i i i i i i i i i i i i x x y d y y x d z z d where d if y d if y (3.3) 當疊代的次數夠多時,上式可轉變為 2 2 0 0 0 1 0 0 2 0 tan ( / ) 1 2 n n n i n n x A x y y z y x A

(3.4) 由(3.4)式中可知道,當我們讓z 為零時,可以利用0 z 來算出向量的角度。 n 不管是旋轉模式或向量模式,在每次的疊代中,旋轉角度都會有其最大限制,這個 限制與i的起始位置有關,最大旋轉角度的限制如下tan(2 )i rotating angle per iteration tan(2 )i

(3.5) 也就是當i起始為 0 時,每次旋轉的角度會介於 4 與 4 之間。當總旋轉角度超過最大 能旋轉的值時,就會發生錯誤。因此我們必須知道最大可旋轉的角度為多少,假設每次 疊代時的d都為 1,且i的起始值為 0,不斷相加的結果,可旋轉最大的角度為 1 0 tan (2 ) 1.7433i i

(3.6) 也就是能旋轉的角度範圍在-1.7433 與 1.7433 之間,大約在正負 100 度之間。若超過這19 個角度,我們必須先旋轉或將旋轉角度限制在能運作的範圍之內,其公式如下 0 0 0 0 0 0 0 0 0 0 _ _ 1, _ ( ) 1 ( ) i x d x i y d y i z z if d or z i sign y if d where d sign x

(3.7) 其中 _x i 、 _y i 和 _z i 表示初始值,sign( ) 代表該括號中的正負號。做完初步的旋轉之 後,再把x 、0 y 、0 z 與0 d 帶入先前的公式即可。經過這個處理之後,總旋轉角度範圍0 擴大為到之間了。 另外,從(3.6)可看出,最大能旋轉的角度為 1.733,由於之後我們可以透過(3.7)預 先旋轉角度 ,所以最大能旋轉的角度為1.7433 4.8849

279.884

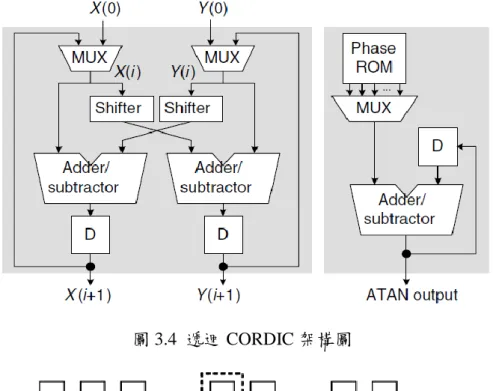

(3.8) 如果旋轉角度大於 4.8849,我們可以先扣掉2 ,也就是將範圍限定在與之間,即 可做正確的 CORDIC 運算。 CORDIC 演算法的架構[12]主要有兩種,遞迴(iterative)架構與平行(parallel)架構。 遞迴 CORDIC 架構如圖 3.4 所示,每次遞迴的反正切函數值由唯讀記憶體(Read Only Memory, ROM)讀出,只需要使用同一組電路,較節省面積,但所需運算的時脈週期(clock period)隨遞迴次數增加而遞增,因此運算所需的時間較長為此架構的缺點。平行 CORDIC 架構如圖 3.5 所示,將所有的遞迴運算層級堆疊,Arctangent 值由 ROM 取出,對每個層 級而言可視為一個常數,可在一個時脈週期完成運算,但是要考量到單一時脈周期的時 間長短,且也耗費較多硬體面積。因此,我們希望取得兩種架構優點的平衡,將兩種架 構結合使用,每次的遞迴操作二到三個層級的運算,在面積與運算時脈週期間取得平 衡。20

圖 3.4 遞迴 CORDIC 架構圖

21

3.2.2 快速傅立葉轉換(Fast Fourier transform, FFT)

本篇論文中,FFT 運算直接使用由 Xilinx IPCore 產生的模組,因此將參照 Xilinx 所

提供的數據表(Data Sheet)[13-14]加以說明。 圖 3.6 Xilinx FFT v7.1 模組 圖 3.6 是在實際電路中所使用的 FFT 模組,接下來將對模組中一些重要的輸入與輸 出訊號做說明。在輸入的訊號中,START 用來控制 FFT 運算的起始點,當此訊號升起 (rising)時,開始輸入要運算的資料,XN_RE 為輸入的訊號實部,XN_RE 為輸入的訊號 虛部,START 訊號升起只需維持一個時脈周期的時間,因此載完一個完整 OFDM 符元 的資料後,會繼續等待下一次 START 訊號的升起,才會繼續讀取下一個 OFDM 符元來 做 FFT 運算。運算過程中 BUSY 訊號會升起直到運算結束,當運算結束後,DONE 訊 號會升起,此時可以將我們所需要的輸出資料取出,XK_RE 為輸入的訊號實部,XK_RE 為輸入的訊號虛部,由於後續的處理需要一些緩衝時間,因此我們先將這些資料儲存於 自行建立的隨機存取記憶體(Random Access Memory, RAM)空間,以增加彈性做後續的 處理。圖 3.7 為此模組的操作時序圖。

22 圖 3.7 Xilinx FFT v7.1 操作時序圖

3.3 傳送機設計

圖 3.8 傳送機架構方塊圖 3.3.1 提高取樣(Up-Sampling) 為了使類比端的低通濾波器更好設計,我們通常會先在數位端做提高取樣的動作。 提高取樣可分為兩個步驟,首先將數位訊號依照超取樣因子(over-sampling factor)在訊號 點之間補零,接下來再透過數位低通濾波器濾波,如此便可提高訊號的取樣頻率,本論 文的數位低通濾波器我們使用平方根升餘弦(square root raised cosine, SRRC)濾波器,如 圖 3.9 與圖 3.10 所示,為超取樣因子等於 4 的平方根升餘弦濾波器。 Q P SK M a pp ing IF F T Add CP Ampl it u de Clip pin g O v er -s a mp lin g SCS DAC DAC RF RF23 圖 3.9 時域平方根升餘弦濾波器 圖 3.10 頻域平方根升餘弦濾波器 一般來說,數位濾波器的硬體架構有以下三種[10],如圖 3.11 所示。圖(a)為最常見 的架構,但是有最長的關鍵路徑(critical path),濾波器係數越多其關鍵路徑越長,此為 其缺點。而圖(b)雖然重要路徑較短,但卻有扇入(fan-in)太大的缺點,需要較大的驅動能 力。圖(c)可以改良圖(a)和圖(b)的缺點,在兩者之間取得一個平衡。 0 5 10 15 20 25 30 35 40 45 -0.4 -0.2 0 0.2 0.4 0.6 0.8 1 1.2 1.4 timing index am pl itu de

SRRC(time domain): over-sampling factor=4

alpha=0.2 alpha=0.5 alpha=0.8 -80 -60 -40 -20 0 20 40 60 80 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 index am pl itu de

SRRC(frequency domain) : over-sampling factor=4

alpha=0.2 alpha=0.5 alpha=0.8

24 圖 3.11 (a) 直接型式, (b) 轉置型式 ,(c) 混合形式 由於提高取樣的輸入訊號的性質,我們可以將訊號補零的部分與係數相乘的乘法器 省略。假設超取樣因子為N ,我們可以將原本的係數拆成N 組,亦即有N 組子濾波器 (sub-filter),而形成一多相位(poly-phase)濾波器,如圖 3.12 與圖 3.13 所示,如此只需一 個多工器選擇不同時脈週期所需要的濾波器係數,所使用的乘法器可降為原本 1 N ,關 鍵路徑也因此縮短,由於圖 3.13 的每個子濾波器的係數較少,我們可以直接使用圖(a) 的架構即可,這就完成提高取樣的硬體架構了。

25 圖 3.12 多相位濾波器概念圖 圖 3.13 多相位濾波器架構圖 3.3.2 振幅裁切(Amplitude Clipping) 在訊號進入 SCS 拆解成兩個固定波包訊號前,我們要先定義出最大振幅A ,如果m 訊號振幅大於A ,因為我們使用的 SCS 為 IQ 法,會造成計算錯誤訊號的根號內有負值,m SCS 運算會發生問題,所以我們需要先對振幅超過A 的訊號做處理。另外,由於我們m 計算錯誤訊號時使用多項式內插法(下一小節 3.3.3 會再做說明),為了減少儲存係數, 必須將內插曲線規範在一個限定範圍內,因此也需要定義一個振幅最小值a 。在此我們m 的方法為直接將訊號的振幅做縮減到一定的範圍內,如(3.9)所示。振幅大於A 則保留訊m

26 號相位,並將訊號振幅縮減至A 。如果振幅小於m a 則保留訊號相位,並將訊號振幅拉m 長至a 。 m ( ) ( ) ( ), ( ) , , ( )= ( ) m m j t m m j t m m x t a x A x t A e x A a e x a where t x t (3.9) 圖 3.14 振幅縮減器方塊圖 圖 3.14 為振幅裁切器方塊圖。我們要先算出訊號的振幅 2 2 I Q ,為了避免硬體上 開根號的複雜運算,參考[12]以二分法線性逼近來取代根號的運算,此方法的最大誤差 約為 2.2%,為可容許範圍。二分法線性逼近可以表示為 0 0 2 2 0 0 1 1 1 1 1 , 0 3 3 11 2 ( , , , ) (1, , , ) 1 16 4 16 , 1 2 Y a X b Y X X Y a b a b Y a X b Y X (3.10) 由(3.10)可觀察到,所有係數的分母皆為 2 的冪次方,這讓我們在硬體設計上可避免使 用乘法器,只需用到簡單的移位器與加法器。圖 3.15 與圖 3.16 為二分法線性逼近(3.10) 的架構圖。

27 圖 3.15 範圍(Segment)判定區塊架構圖 圖 3.16 二分法線性逼近架構圖 算出訊號振幅之後,經由比較器判別振幅是否大於A 或小於m a ,如果沒有則不做m 任何動作就將原本的訊號輸出,反之則將處理過的訊號輸出。訊號處理前要先求出訊號 角度,我們以 CORDIC 向量模式來實現此區塊,接下來再將純量的振幅旋轉前一步驟所 求出向量訊號的角度,此處需使用到 CORDIC 旋轉模式,旋轉完後即得到我們要的訊 號。

28

3.3.3 訊號拆解器(Signal Component Separator, SCS)

在 2.2.2 我們有提到,SCS 的實現主要有相位法[15]以及 IQ 法[16],其方塊圖如圖 3.17 與圖 3.18。由於相位法需要多次的角度運算與旋轉,以及除法和反正弦(Arcsine)運 算。因此在本論文中,我們以 IQ 法做為基本的架構。 圖 3.17 SCS:相位法方塊圖 圖 3.18 SCS:IQ 法方塊圖 Polar Converter Scalling arcsin Phase Calc ulator Polar to IQ Polar to IQ SQRT MULT ADD/SUB

29 由圖 3.18 可知,為了求出錯誤訊號,我們需要除法器以及開根號,這都是在硬體時 做我們想避免的。因此我們想簡化求出錯誤訊號的區塊。我們將錯誤訊號的根號項稱作 錯誤因子(error factor),其數學式表示如下 2 2 ( ) 1 ( ) m f A e t s t (3.11) 其中e tf( )為純量,在此我們將問題轉變成要簡化錯誤因子的運算,錯誤因子的唯一變數 為訊號振福,可以將此看成一對一的多項式對應,以高階多項式分段逼近錯誤因子的曲 線[17-18]。為了節省硬體資源,我們需要先對輸入的訊號振福做統計分析,決定逼近取 線的上界與下界,並於訊號進入 SCS 前做前置的處理,此部分上一小節 3.3.3 已介紹。 訊號振福統計分析如圖 3.19 所示,我們將上界設定在 1.85,約為訊號統計變異數的兩倍 左右,下界在訂在 0.1,由之後第四章的模擬可知,訂定此振幅範圍並不會對系統效能 造成顯著的影響。逼近曲線如圖 3.20 所示,我們使用二階多項式來逼近此曲線,經模擬 分析顯示我們需將此線分割成六個區塊,因此儲存的係數較多,不過其好處是使用的乘 法器較少,關鍵路徑也相對較小,錯誤因子內插法的架構如 3.21 所示。六個區塊的二階 多項式的係數如表 3.1 所示。 圖 3.19 OFDM 符元之振幅統計分析 -0.50 0 0.5 1 1.5 2 2.5 3 3.5 500 1000 1500 2000 2500 3000 3500 4000 4500 5000 |s(n)| S ta ti s ti c a l R e s u lt 1000 OFDM symbols (Nfft=32)

30 圖 3.20 SCS 錯誤向量曲線圖 圖 3.21 錯誤因子內插法架構圖 表 3.1 二階多項式逼近:aX2bX c係數表 a b c 0.1~0.2 623.000 -280.350 40.410 0.2~0.4 77.700 -70.190 20.195 0.4~0.75 10.314 -18.364 10.246 0.75~1.4 1.477 -5.324 5.437 1.4~1.8 -0.745 0.858 1.137 1.8~1.85 -53.842 62.161 -17.833 0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2 0 2 4 6 8 10 12 14 16 18 20 |s(n)| s q rt (A m 2/| s (n )| 2-1 ) |s(n)|=[0.1,Am]

31 經過改良後,我們的 SCS 架構如圖 3.22 所示,由(3.11)可知,在進入多項式內插前, 仍需求出訊號振福,這部份我們於 3.3.1 已提到,可以使用二分法線性逼近來完成,避 開了乘法器與開根號的使用,僅需簡單的移位器與加法器。而錯誤因子我們使用多項式 逼近,需要用到乘法器與少量的記憶空間儲存係數,取代了原本複雜的除法器以及開根 號。最後再將我們求到的錯誤因子與訊號相乘並做加減法的處理,如此就完成了我們 SCS 的架構設計。 圖 3.22 SCS :改良後的 IQ 法方塊圖 3.3.4 前導訊號 (Preamble) 圖 3.23 前導訊號 前導訊號主要用來做接收端的同步處理,需要根據目的及演算法的不同,來訂定出 符合要求的前導訊號,本論文的前導訊號為參考 802.11a 的規範[9]後自訂。如圖 3.23 所 示本論文使用的前導訊號包含六個週期的短訓練符元(training symbol),每個週期的短訓 練符元包含 8 個符元長度,主要利用其重複性,來進行封包偵測以及粗略頻率偏移估測。 接在後面的為長訓練符元,每個週期的長訓練符元包含 32 個符元長度,長訓練符元前

32 會加一段 CP,長訓練符元主要用來做符元起點估計以及精細頻率偏移估計。最後,為 了做通道估測時避免兩根天線互相干擾,我們將 SCS 拆開後的兩個長訓練符元在不同的 時間傳送,並於接收端將拆開後的長訓練符元相加並還原,如此便可有效估測出兩根傳 送天線所產生不同的通道效應。

3.4 接收機設計

圖 3.24 接收機架構方塊圖 3.4.1 降低取樣(Down-Sampling) 在降低取樣之前,我們會先將訊號經過平方根升餘弦濾波器,目的是為了與傳送端 提高取樣時的濾波做匹配,兩端濾波的效應合成即為升餘弦(Raised Cosine, RC)濾波器, 也能將訊號頻寬外的雜訊濾掉。接下來才降低取樣頻率,根據降取樣因子M ,我們只 需每M 個時脈週期輸出一個訊號,為了節省乘法器的使用,我們可利用 3.3.3 提高取樣 所提到的多相位濾波器的概念,將濾波器拆成M部分, M個時脈週期驅動一次訊號移 位暫存器,且一次移動M 個暫存器的位置,與提高取樣不同的是最後要將M 個子濾波 器輸出結果相加,得到輸出結果,本論文的M 定義為 4。架構圖如下 3.25 所示。 Pa cket Det ect io n Co a rse CF O E st . F ine C F O E st . Sy mb o l Ti min g Remo v e CP FFT Cha nn el E st ima tio n M Z F Det ect io n Do wn -s a mp li ng ADC RF33 圖 3.25 降低取樣架構圖 3.4.2 封包偵測 (Packet Detection) 封包偵測可以初步的估測前導訊號的起始位置,也可以在還沒接收到封包前,讓之 後的硬體處於休止的狀態,以節省功率。與封包偵測有關的演算法有很多,在此我們是 利用前導訊號重覆的特性來進行封包偵測。本論文的短訓練符元包含 6 個大小同為 8 的 相同區塊所組成,因此我們可以設計兩個大小同為 16(定義為 L)的視窗,兩個視窗的間 隔為 8(定義為 D),當訊號通過時,兩個視窗就互相做相關性(correlation)運算,其數學 式如下 1 * 0 8, 16 L n n n k n k D k m c r r D L

(3.12) 從(3.12)可知,在封包尚未進來之前,m 只會是一個很小的值,而當封包一進到窗戶之n 中,借由前導訊號所存在的關連性,m 也會隨著變大,當大於我們所設的門檻值時,n 則判定已接收到封包。這種方法簡單且易實現,不過會有m 分佈範圍過大的問題,造n 成門檻值的設定相當困難。 為了解決門檻值的設定變動過大的問題,改善的方法就是對之前求到的c 做正規n 化(normalization),數學式如下34 1 * 0 1 * 0 2 2 L n n k n k D k D n n k D n k D k n n n c r r p r r c m p

(3.13) 將c 除上視窗的能量,我們就可以把n m 的範圍控制在 0 與 1 之間,在設定門檻值時就n 方便多了。不過正規化會造成在硬體設計方面,得多付出除法器的代價。 圖 3.26 封包偵測基本架構圖 如圖 3.26 所示,訊號進來後會分兩路進行,為了降低硬體之面積與複雜度,透過 移動視窗(sliding window)遞迴算出c 與n p ,其數學式表示如下 n * * 1 1 1 1 1 2 2 1 1 1 n n n n D n L n L D n n n D n L D c c r r r r p p r r (3.14) 移動視窗運算架構圖如下所示 圖 3.27 移動窗戶架構圖35 另外,由圖 3.26 可看到,除若干乘法器與加法器外,我們還需要一個除法器,這是 我們所不樂見的。除法器除了會佔去不少的面積,也會有時間的延遲,為了避免除法器 的使用,我們將門檻值訂亦為 0.75,此門檻所造成的封包遺失率為可接受範圍(見第四 章模擬部分),但可大大的增加在硬體上實作的便利性,我們只需將圖 3.26 中的c'透過 移位器處理,再經過一個比較器,當 ' 3 ' 4 c p ,我們判定偵測到封包。改良後的封包偵 測硬體架構如圖 3.28 所示。 圖 3.28 改良後之封包偵測架構圖

3.4.3 符元時序估計 (Symbol Timing Estimation)

在 OFDM 接收機中,通常要有一個好的符元起點估計,才能取到正確的訊號做後 面的 FFT。一般來說符元起點估計的做法,都是利用匹配濾波器(matched filter),將接收 到的訊號與已知的前導訊號做匹配,其數學表示如下 2 1 * 0 ˆ arg max L s n k k n k t r t

(3.15) 其中rn k 為接收訊號,t 為已知用來匹配的前導訊號,由上式可知,時序偵測與封包偵k 測不同,在做完匹配之後,不是經過一個門檻值,而是取出一個最大值,這樣才有辦法 做更準確的時序控制,也就是說要在我們所決定的偵測時間長度內決定出一個最大值當 作符元起點。36 而我們選用來匹配接收訊號的前導訊號取自短訓練符元區塊的最後八個取樣點與 長訓練符元區塊的最前面八個取樣點,因為這兩組前導訊號的相關性不大,有較為明顯 的界線,會更容易偵測出符元起點的位置。在此我們採用 3.3.2 介紹過的混合形式的匹 配濾波器,以有效的降低關鍵路徑之長度,並在輸出的地方比較並記錄最大值的位置 (index),如圖 3.29 所示,這就完成了我們符元起點估計的硬體架構了。 圖 3.29 符元起點估計架構圖

3.4.4 頻率偏移估計與補償 (Frequency Offset Estimation/Compensation)

傳送端與接收端的震盪器(crystal oscillator)頻率通常不會相同,若不進行頻率偏移 補償,將使子載波間的正交性被破壞,造成子載波間的相互干擾,而對系統效能造成嚴 重的影響。本論文使用[9]之頻率偏移估計的方法,主要是利用前導訊號的週期性特性(令 週期為 D),對兩個時間不同但數值相同的複數訊號而言,當有頻率偏移時,兩點會因 為時間的差異而產生一相位差,於是由已知間距是 D,因此可以容易估算出傳送端與接 收端的頻率偏移。 假設傳送的時域基頻訊號為s ,載到載波上的訊號為n y ,則傳送端的訊號可以表示n 如下 2 tx s j f nT n n y s e (3.16) 其中,f 為傳送端的載波頻率,tx T 為每個子載波的取樣週期,而接收端將射頻訊號降到s

37 基頻的載波頻率為 f ,不同震盪器所產生的載波頻率不會完全相同,也就是說rx f 與tx frx 會有差異,在忽略雜訊的情況下,解調訊號可表示如下 2 2 2 ( ) 2 tx s rx s tx rx s s j f nT j f nT n n j f f nT n j f nT n r s e e s e s e (3.17) 其中 f ftx frx,為傳送端與接收端載波頻率的差值,D 為兩個重複區塊中兩點相同 取樣值的延遲,令

z

為: 1 * 0 1 2 2 ( ) * 0 1 2 2 ( ) 0 1 2 2 0 ( ) s s s s s L n n D n L j f nT j f n D T n n D n L j f nT j f n D T n n D n L j f DT n n z r r s e s e s s e e e s

(3.18) 我們因此可得頻率偏移估計值如下 1 ˆ 2 s f z DT

(3.19) 由於z

的角度 2 f DTs必須定義在與之間,所以頻率偏移所能估測的範圍有所限 制: 1 2 s 2 s f DT DT

(3.20) 由(3.20)可知,D 越大所能估測的範圍越小,因此我們先使用 D 較小的短訓練符元做粗 略(coarse)估計,如此補償後所剩的頻率偏移角度變小,為了得到更可靠的結果,再以 D 較大長訓練符元做細部(fine)估計,也就是我們在補償頻率偏移時,必須對接收到訊號以 兩次估計得到的角度和做倍數的旋轉。基本的架構圖如圖 3.30 所示。38

圖 3.30 頻率偏移補償方塊圖

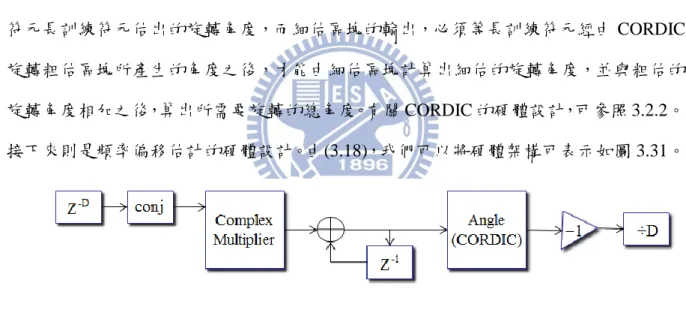

圖 3.30 中,粗估(Coarse Estimation)與細估(Fine Estimation)兩區塊分別是由短訓練 符元長訓練符元估出的旋轉角度,而細估區塊的輸出,必須等長訓練符元經由 CORDIC 旋轉粗估區塊所產生的角度之後,才能由細估區塊計算出細估的旋轉角度,並與粗估的 旋轉角度相加之後,算出所需要旋轉的總角度。有關 CORDIC 的硬體設計,可參照 3.2.2。 接下來則是頻率偏移估計的硬體設計。由(3.18),我們可以將硬體架構可表示如圖 3.31。 圖 3.31 Coarse/Fine Estimation 硬體架構圖 其中 D 在粗略估計時為 8,在細估計時為 32。角度的求取利用 CORDIC 向量模式得到, 至於D的方塊,因為D是 2 的次方,所以只需要一個移位器即可。而角度累加(Angle Accumulator)區塊為一固定角度的累加器,其功能為對每個取樣值旋轉固定角度的倍數, 其架構如下 Fine Estimation Coarse Estimation CFO Compensation Angle Accumulator Generator

39 圖 3.32 Angle Accumulator 架構圖 上圖中的輸入只是一個最小的旋轉角度a,給第一個輸入的取樣值做旋轉,而之後的旋 轉角度分別為 2 ,3 ...a a 。角度累加大於或小於時,為了避免超過 CORDIC 所能操作 的範圍,所以要做減2 與加2 的動作,這是圖 3.28 中比較器(Comparator)的運作方式。 將以上元件連結起來以後,就是我們所使用的頻率補償區塊了。 3.4.5 通道響應估測 (Channel Estimation) 在通道估測中,3.3.5 前導訊號已介紹,我們將由 SCS 拆開後的長訓練符元,由第 一根天線先後傳送,第二根天線則不送資料,於接收端做 FFT 之前,先將拆開後的時域 長訓練符元相加再做轉換,轉換後再透過運算得到第一根天線的通道響應,至於要求第 二根天線的通道響應做法與第一根相同,只要在傳送端改成第一根天線不送訊號,第二 根天線則傳送由 SCS 拆開後的時域長訓練符元。通道估測的數學表示式如下 k k k k R H X W (3.21) * * 2 * * ˆ ( ) k k k k k k k k k k k k k k H R X H X W X H X W X H W X (3.22) 其中,R 為接收端接收到的子載波訊號,k X 為傳送端傳送的子載波,k H 為影響子載波k 的通道效應,W 為雜訊。k Hˆk則表示運算後估測出來的通道效應。由於長訓練符元頻域 是由一堆+1 與-1 所組成,所以乘法器可用簡單的查表與判斷就可取代,在硬體實現上 相當容易。

40 由於本論文的偵測方法使用 MZF 偵測,因此我們得到兩根天線的通道係數後,再 做 MZF 通道係數的運算(2.23),由[8]可知道,參數在 0.7 倍左右的最大振幅效能最好, 我們選擇相差不多的 0.75,如此可以用移位器取代乘法器的使用。運算完後將通道係數 存在記憶體中,當後端的訊號等化要執行時,就直接將通道係數輸出給 MZF 等化器作 運算,進而解決訊號延遲的問題。通道響應估測的硬體架構如圖 3.33 所示。 圖 3.33 通道響應估測架構圖 3.4.6 MZF 偵測 (MZF Detection) 訊號等化部分,我們利用 3.4.5 通道估測得到要用來做 MZF 偵測的通道係數做處理, 因為我們使用 OFDM 技術傳輸,訊號的等化可簡化為對每個子載波分別做處理,也就 是說通道效應對頻域上每個子載波可視為平緩衰減(flat fading),如此我們只需把相對應 子載波位置的通道效應除掉,即可完成訊號的等化。由於通道效應為複數,訊號等化的 數學表示式如下 x x a bi a bi a bi a bi (3.23) 架構如下圖 3.34 所示 圖 3.34 訊號等化架構圖

41 由上圖可知,我們仍需要一個除法器,而此除法器是無法避免的,在此我們使用的除法 器為恢復式除法(restoring division)[19],概念上與直式除法相同,接下來我們以一個簡 單的範例做說明,可以更容易理解。假設我們所要得到的商數整數位元為 5,小數位元 為 3,範例如下 4 3 2 1 0 1 2 3 dec. Example : 29 3 29 2 3 17 0 restore 29 2 3 5 1 5 2 3 7 0 restore 5 2 3 1 0 restore 5 2 3 2 1 1 2 2 3 1 2 1 1 2 3 0 restore 2 4 1 1 2 3 1 2 8 Ans. 01001.101 9.625 首先,我們要先決定商數的位元大小m,接下來只需重複m次的移位減法與比較,即可 完成除法的硬體架構。由於我們所設定的商數位元較大(為 12),會造成關鍵路徑太長, 影響系統最大操作頻率,因此我們將其做一次的管線化(pipelining)處理,以解決除法器 的重要路徑太長的缺點。

![圖 2.6 為 2x1 無合成器 LINC 系統架構,數位訊號模組(Digital Signal Processing, DSP) 將傳送的訊號拆解後經過濾波器/調變器,再經過功率放大器放大後傳送。[5]也提出極 化天線的系統架構如圖 2.7 所示,接收端為兩根天線,形成一類似 22 的 MIMO 系統,](https://thumb-ap.123doks.com/thumbv2/9libinfo/8592269.189819/19.892.160.772.512.972/系統架器再經過放大器放大後傳送提出化天線系統架構一類似系統.webp)