國 立 交 通 大 學

電信工程學系

碩 士 論 文

馬爾尚分合波器之混頻器與利用除頻器與

振盪器之訊號產生電路

Mixers with Different Type Marchand Baluns and Signal

Generation by Frequency Dividers and Oscillators

研究生:欉冠璋

指導教授:孟慶宗

馬爾尚分合波器之混頻器與利用除頻器與振盪

器之訊號產生電路

Mixers with Different Type Marchand Baluns and Signal

Generation by Frequency Dividers and Oscillators

研究生:欉冠璋 Student: Kuan-Chang Tsung

指導教授:孟慶宗 博士 Advisor: Dr. Chin-Chun Meng

國 立 交 通 大 學

電信工程學系碩士班

碩士論文

A Thesis

Submitted to Department of Communication Engineering College of Electrical and Computer Engineering

National Chiao Tung University In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In

Communication Engineering

July 2007

Hsinchu,Taiwan, Republic of China

馬爾尚分合波器之混頻器與利用除頻器與振盪器

之訊號產生電路

學生:欉冠璋 指導教授:孟慶宗 博士 國立交通大學 電信工程學系碩士班摘 要

本篇論文主要是研究在射頻積體電路中的二大主題。第一個主題為 被動馬爾尚分合波器,並將其與主動式混頻器結合;第二個主題為訊號 產生電路包含除頻器與振盪器。 我們使用 TSMC 0.35µm CMOS 與 TSMC 0.18µm CMOS 製程來實作 不同類型的馬爾尚分合波器測試元件,接著將馬爾尚分合波器與主動式 的微混頻器整合,當成混頻器本地振盪端的輸入,整合電路則是使用 TSMC SiGe 0.35µm BiCMOS 製程來實作。 在除頻器部分,探討了常見的數位式與類比式除頻電路,在數位式 的除頻電路上我們利用 TSMC SiGe 0.35µm BiCMOS 來實作產生 50%工 作週期之除 5 電路;而適合於高頻操作的類比式除頻器,我們則利用 Win 0.15µm HEMT 高截止頻率的製程技術來實現。在振盪器部分,使用 雙變壓器(Trifilar)這個元件來達成訊號的耦合作用,不管是透過串接 式電晶體訊號耦合或直接訊號耦合方式皆可以使輸出為正交相位的訊 號,振盪器的實作則是利用 TSMC 0.18µm CMOS 與 TSMC 0.13µm CMOS 二種製程技術。Generation by Frequency Dividers and Oscillators

Student:Kuan-Chang Tsung Advisor: Chin-Chun Meng Department of Communication Engineering

National Chiao Tung University

Abstract

In this thesis, we focus on two topics of Radio Frequency Integrated Circuits. The first is Marchand baluns and combination of Marchand baluns and active mixers. The second is signal generation by frequency dividers and oscillators.

We implement different type Marchand baluns by using TSMC 0.35µm CMOS technology and TSMC 0.18µm CMOS technology. Then Marchand baluns are integrated into active micro-mixers as LO input element, and it is demonstrated in TSMC 0.35µm SiGe BiCMOS technology process.

Conventional analog and digital frequency dividers are discussed in this thesis. We use TSMC 0.35µm SiGe BiCMOS technology process to implement truly 50% duty cycle divide-by-5 digital frequency dividers. Analog frequency dividers are more adaptable for high speed operation than digital ones, and they are implemented in high cut-off frequency Win 0.15µm HEMT technology process. In Oscillator circuits, we utilize trifilar to couple output signals. Direct coupling and series coupling by transistors both can generate quadrature signals. Finally, Quadrature Oscillators are implemented in TSMC 0.18µm CMOS technology process and TSMC 0.13µm CMOS technology process.

誌謝

二年來的研究所生活即將落幕,其間受到了許多人的幫助與扶 持,使得這本論文可以從無到有,讓小弟順利畢業。首先很感謝孟慶 宗老師的指導,讓我能在研究過程中得到許多寶貴的經驗得以克服種 種困難進而增進學識涵養,不僅如此,生活上亦受益良多,著實令我 成長了不少。並感謝林育德教授與張志揚教授在百忙之中能參加論文 口試並給予寶貴的建議,使得本論文內容能更加完整。 研究生活中,因為有 lab 918 的各位,讓這兩年的生活充滿了回 憶。感謝宗翰、聖哲、珍儀、宏儒、樺輿、家宏與英杰學長姐們在研 究上的指導與量測上的幫助,讓我解決各種疑難雜症。同時要感謝勝 文、柏誼與約廷的砥礪與協助,使得我在課業上和體能上皆能持續不 斷地精進。此外,感謝學弟妹們金詳、宜蓁、揚鮮、雅惠、宜珊與威 宇幫忙與陪伴,為實驗室帶來不少活力與歡樂。 最後特別感謝我的父、母親與弟弟以及詩雯在求學過程中,給予 我最大的支持及關懷,在此僅把此論文的榮耀獻給我的家人以及身邊 所有關懷我的朋友們。

目錄

中文摘要 i 英文摘要 ii 誌謝 iii 目錄 iv 表目錄 vii 圖目錄 viii 第一章 導論 1 1.1 研究動機 2 1.2 論文組織 3 第二章 不同類型 Marchand balun 特性比較與混頻器設計 4 2.1 前言 5 2.2 不同類型 Marchand balun 比較與實作 5 2.2.1 耦合傳輸線 5 2.2.2 二種 Marchand balun 與二種 0o,0o分波器 72.2.3 Type I 與 Type IV Marchand balun 實作 9

2.2.4 Type V 與 Type VI 0o,0o分波器實作 15 2.3 結合 Marchand balun 混頻器設計與實作 21 2.3.1 研究動機 21 2.3.2 實作電路架構 22 2.3.3 實測結果 25 2.3.4 結論與討論 32 第三章 除頻電路 34 3.1 前言 35 3.2 除頻電路的應用-頻率合成器 36 3.2.1 頻率合成器(Synthesizer)在收發機上的應用 36

3.2.2 直接頻率合-Carrier Frequency Generator 38

3.3 除頻電路的應用-收發機上正交訊號的產生 41

3.3.1 鏡像消除接收機與單頻帶升頻器 41

3.3.2 正交訊號的產生方法 42

3.4 高速除頻電路架構 46

3.4.1 高速 Flip-Flop 除二電路 46

3.4.2 訊號再生式除二電路(Regenerative Frequency Divider) 原理與架構 48

原理與架構 51 3.4.5 其它除數注入鎖住式除頻電路 56 3.5 實作一 產生 50%工作周期的除五電路 58 3.5.1 研究動機 58 3.5.2 實作電路架構 59 3.5.3 實測結果 62 3.5.4 結論與討論 67 3.6 實作二 訊號再生式除二電路 68 3.6.1 研究動機 68 3.6.2 實作電路架構 68 3.6.3 實測結果 70 3.6.4 結論與討論 73 3.7 實作三 正交訊號輸出訊號再生式除二電路 73 3.7.1 研究動機 73 3.7.2 28GHz IQ RFD 電路架構 74 3.7.3 28GHz IQ RFD 實測結果 75 3.7.4 35GHz IQ RFD 電路架構 79 3.7.5 35GHz IQ RFD 實測結果 79 3.7.6 結論與討論 82 3.8 實作四 注入鎖住式除二電路 83 3.8.1 研究動機 83 3.8.2 實作電路架構 83 3.8.3 實測結果 84 3.8.4 結論與討論 86 3.9 實作五 注入鎖住式除三電路 87 3.9.1 研究動機 87 3.9.2 實作電路架構 87 3.9.3 實測結果 88 3.9.4 結論與討論 90 第四章 正交相位壓控振盪器 91 4.1 前言 92 4.2 相位雜訊 92 4.2.1 何謂相位雜訊 92 4.2.2 相位雜訊模型 94 4.3 正交相位壓控振盪器理論 100

4.4.3 模擬結果 107

4.4.4 結論與討論 109

4.5 實作二 Trifilar Coupling Quadrature VCO 109

4.5.1 研究動機 109 4.5.2 實作電路架構 110 4.5.3 實測結果 111 4.5.4 結論與討論 114 第五章 結論 115 參考文獻 117

表目錄

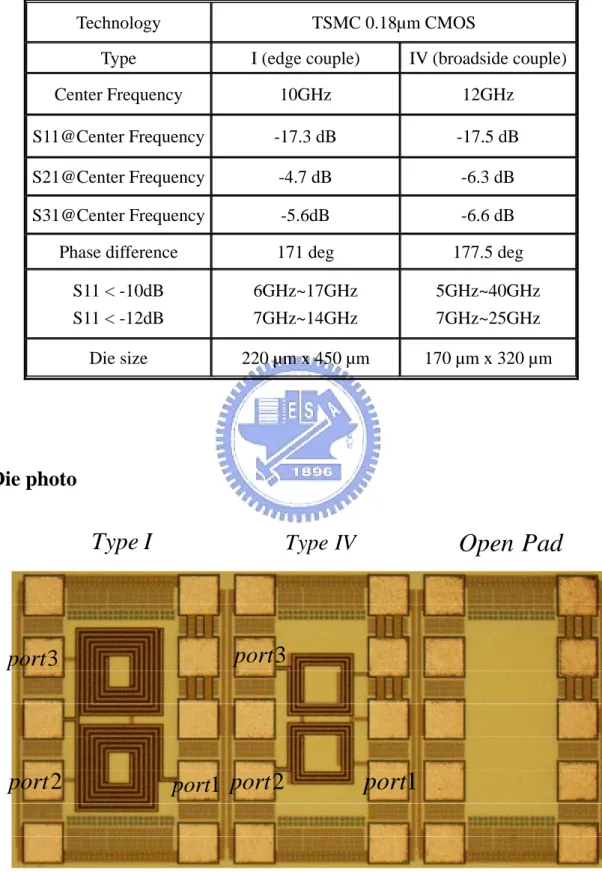

表 2.1 Type I and Type IV Marchand balun summary 14

表 2.2 Type V and Type VI 0o,0o分波器 summary 20

表 2.3 Marchand balun 混頻器 performance summary 32

表 3.1 電流交換式 D flip-flop 真值表 59 表 3.2 SHSHH 與 SSHSH 接線方式 60 表 3.3 SHSHH 與 SSHSH performance summary 67 表 3.4 RFD performance summary 72 表 3.5 28GHz IQ RFD performance summary 78 表 3.6 35GHz IQ RFD performance summary 81

表 3.7 除 2 ILFD performance summary 86

表 3.8 除 3 ILFD performance summary 90

表 4.1 3D series trifilar QVCO 預計規格表 108

圖目錄

圖 2.1 耦合傳輸線結構圖 6

圖 2.2 四種類型 Marchand balun 7

圖 2.3 二種類型 0o ,0o分波器 8

圖 2.4 螺旋型線圈式 Type I 與 Type IV Marchand balun 示意圖 9

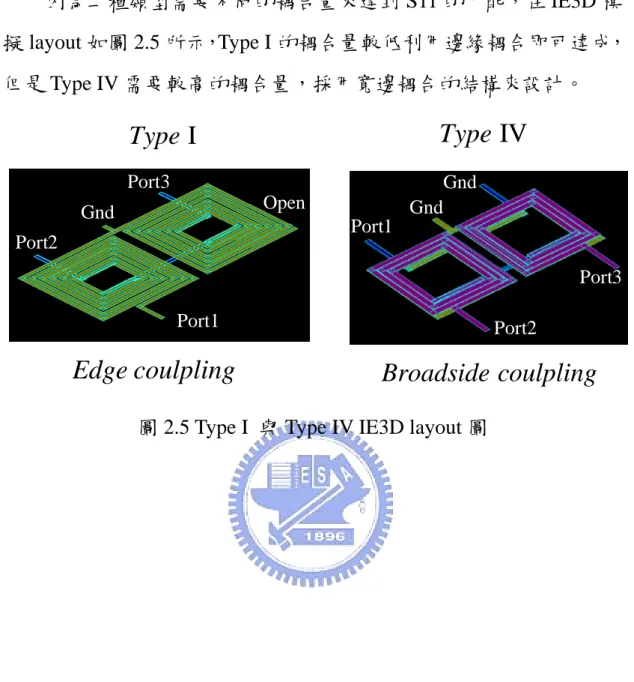

圖 2.5 Type I 與 Type IV IE3D layout 圖 10

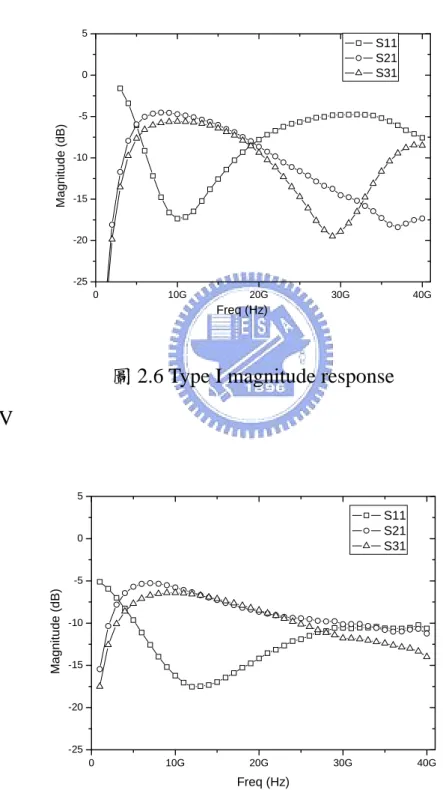

圖 2.6 Type I magnitude response 11

圖 2.7 Type IV magnitude response 11

圖 2.8 Type I phase response 12

圖 2.9 Type IV phase response 12

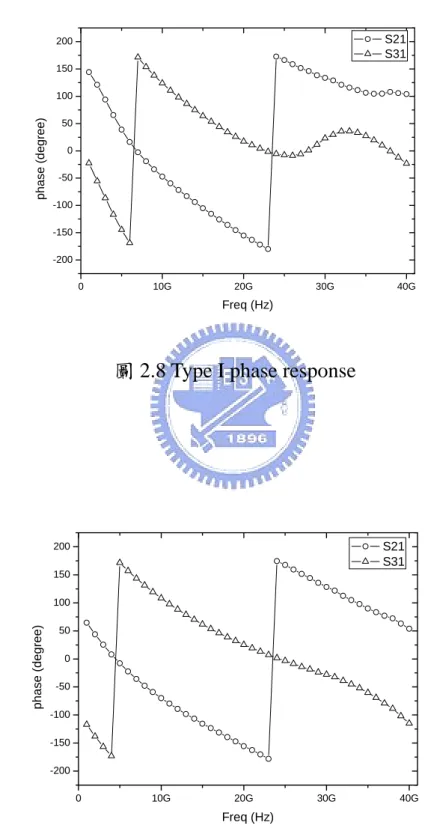

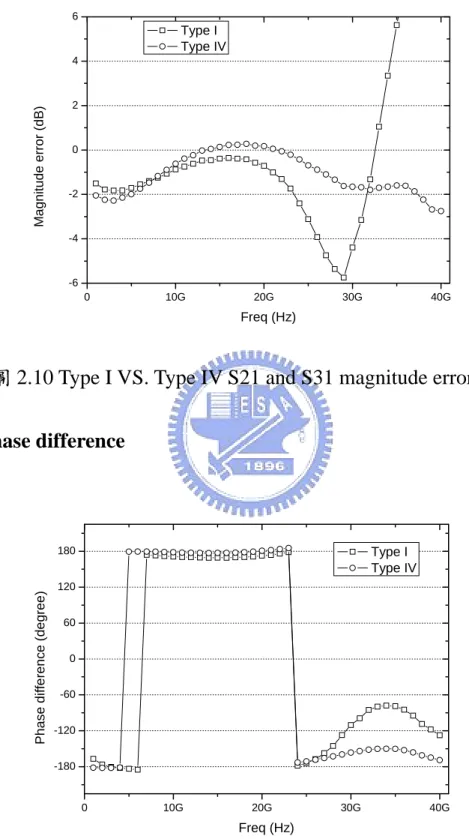

圖 2.10 Type I VS. Type IV S21 and S31 magnitude error 13

圖 2.11 Type I V.S. Type IV S21 and S31 phase difference 13

圖 2.12 Type I and Type IV Marchand balun die photo 14

圖 2.13 螺旋型線圈式 Type V 與 Type VI IE3D layout 16

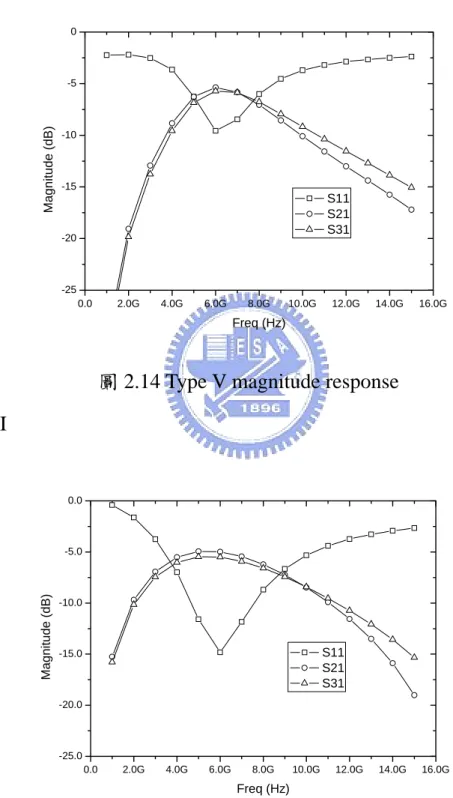

圖 2.14 Type V magnitude response 17

圖 2.15 Type VI magnitude response 17

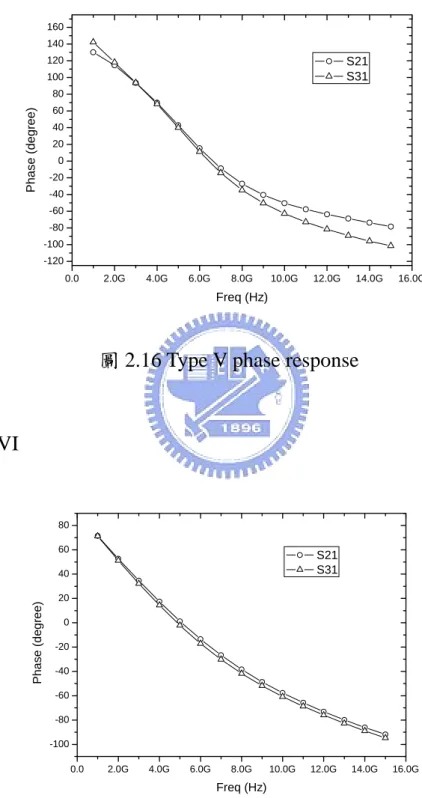

圖 2.16 Type V phase response 18

圖 2.17 Type VI phase response 18

圖 2.18 Type V VS. Type VI S21 and S31 magnitude error 19

圖 2.19 Type V VS. Type VI S21 and S31 phase difference 19

圖 2.20 Type V and Type VI 0o,0o分波器 die photo 20

圖 2.21 混頻器本地振盪源輸入端偏壓電路 22 圖 2.22 微混頻器射頻輸入端電路 23 圖 2.23 結合 Marchand balun 混頻器整體電路圖 24 圖 2.24 Type I 轉換增益 VS. LO 功率 25 圖 2.25 Type IV 轉換增益 VS. LO 功率 25 圖 2.26 轉換增益 VS. RF frequency 26 圖 2.27 轉換增益 VS. IF frequency 26

圖 2.28 Type I P1dB and IIP3 @ RF 7GHz 27

圖 2.29 Type IV P1dB and IIP3 @ RF 7GHz 27

圖 2.30 P1dB and IIP3 27

圖 2.31 Type I isolation 28

圖 2.32 Type IV isolation 28

圖 2.36 Type IV noise figure 30

圖 2.37 結合 Marchand balun Type I 混頻器 die photo 31

圖 2.38 結合 Marchand balun Type IV 混頻器 die photo 31

圖 3.1 頻率合成器在收發機上的應用 36

圖 3.2 Spur 對接收訊號的影響 36

圖 3.3 頻率合成器跳頻時 VCO 輸出頻率變化 37

圖 3.4 頻率合成器 settling time 對接發頻道的影響 38

圖 3.5 除二電路在頻率合成器上的應用-前置除頻器 38

圖 3.6 Frequency of operation for a mode 1 device 39

圖 3.7 Direct frequency synthesizer for UWB mode 1 application 40

圖 3.8 Frequency of operation for a mode 2 device 40

圖 3.9 Direct frequency synthesizer for UWB mode 2 application 40

圖 3.10 單頻帶升頻器 41

圖 3.11 RC phase shifter 42

圖 3.12 N 級環型 VCO 43

圖 3.13 Cross-coupled VCO with parallel coupling 44

圖 3.14 除二輸出正交訊號波形 44 圖 3.15 輸入工作週期對輸出正交相位準度的影響 45 圖 3.16 將 spur 分為 AM 和 PM sideband 45 圖 3.17 除二輸入與輸出的波形 46 圖 3.18 Master-slave flip-flop 除二電路圖 47 圖 3.19 單一 D-latch 電路圖 47 圖 3.20 Regenerative modulator 48

圖 3.21 Second-order regenerative modulator 49

圖 3.22 除 2 RFD block diagram 49

圖 3.23 除 2 RFD 低頻操作限制 50

圖 3.24 除 3 RFD 電路架構 51

圖 3.25 除 RFD 電路架構 51

圖 3.26 一般 free running VCO 模型 52

圖 3.27 Common ILO 模型 52 圖 3.28 二種架構 ILFD 54 圖 3.29 Unified ILO 模型 55 圖 3.30 除 N ILFD 電路圖 57 圖 3.31 除 3 ILFD 電路圖 58 圖 3.32 除三與除五電路輸出波形 58 圖 3.33 電流可交換式 D flip-flop 59 2N −1

圖 3.36 前置輸入級電路圖 61

圖 3.37 輸出緩衝級電路圖 61

圖 3.38 SHSHH sensitivity 62

圖 3.39 SSHSH sensitivity 62

圖 3.40 SHSHH input and output waveform 63

圖 3.41 SSHSH input and output waveform 63

圖 3.42 SHSHH input return loss 64

圖 3.43 SSHSH input return loss 64

圖 3.44 SHSHH input and output phase noise 65

圖 3.45 SSHSH input and output phase noise 65

圖 3.46 SHSHH 除 5 die photo 66 圖 3.47 SSHSH 除 5 die photo 66 圖 3.48 RFD 實作電路 schematic 69 圖 3.49 RFD 輸入 7GHz 頻譜圖 70 圖 3.50 RFD 輸入 19GHz 頻譜圖 70 圖 3.51 RFD input sensitivity 71

圖 3.52 RFD input and output phase noise 71

圖 3.53 RFD die photo 72

圖 3.54 正交訊號輸出 RFD 架構圖與訊號波形 74

圖 3.55 28GHz IQ RFD 電路圖 74

圖 3.56 Passive SSB up-converter 75

圖 3.57 Rejection ratio with amplitude / phase mismatch 75

圖 3.58 28GHz IQ RFD input sensitivity 75

圖 3.59 28GHz IQ RFD 輸入 22GHz 頻譜圖 76

圖 3.60 28GHz IQ RFD 輸入 28GHz 頻譜圖 76

圖 3.61 28GHz IQ RFD input and output phase noise 77

圖 3.62 28GHz IQ RFD output waveform 77 圖 3.63 28GHz IQ RFD die photo 78 圖 3.64 35GHz IQ RFD 電路圖 79 圖 3.65 35GHz IQ RFD input sensitivity 79 圖 3.66 35GHz IQ RFD 輸入 35GHz 頻譜圖 80 圖 3.67 35GHz IQ RFD side-band rejection 80 圖 3.68 35GHz IQ RFD die photo 81 圖 3.69 除 2 ILFD 電路圖 83

圖 3.70 除 2 ILFD input sensitivity 84

圖 3.74 除 3 ILFD input sensitivity 88

圖 3.75 除 3 ILFD 輸入 30.6GHz 頻譜圖 89

圖 3.76 除 3 ILFD die photo 89

圖 4.1 VCO 頻譜 92 圖 4.2 發射機 LO 相位雜訊對 adjacent channel 訊號的影響 93 圖 4.3 接收機 LO 相位雜訊造成 reciprocal mixing 94 圖 4.4 RLC 振盪器 94 圖 4.5 相位雜訊(Leeson) 95 圖 4.6 Current pulse 訊號注入至 LC 振盪器 97 圖 4.7 振幅與相位 impulse response 97 圖 4.8 Hajimiri 模型相位雜號產生過程示意圖 99 圖 4.9 注入訊號至 VCO 小訊號模型 100 圖 4.10 耦合 VCO 小訊號模型 101

圖 4.11 Anti-phase coupling VCO 101

圖 4.12 Cross couple 回授方法 103

圖 4.13 Series coupling QVCO 104

圖 4.14 利用 trifilar 之 series coupling QVCO 105

圖 4.15 Trifilar 106 圖 4.16 平面式 trifilar layout 106 圖 4.17 3D trifilar layout 106 圖 4.18 Tuning range 模擬圖 107 圖 4.19 Output power 模擬圖 107 圖 4.20 Phase noise 模擬圖 107 圖 4.21 Sideband rejection 模擬圖 107

圖 4.22 3D trifilar series QVCO die photo 108

圖 4.23 QVCO based on trifilar coupling 電路圖 110

圖 4.24 主動式 balun 電路圖 111

圖 4.25 QVCO based on trifilar coupling tuning range 111

圖 4.26 QVCO based on trifilar coupling output power 111

圖 4.27 QVCO based on trifilar coupling phase noise 112

圖 4.28 QVCO based on trifilar coupling side band rejection 112

第一章

1.1 研究動機

近年來無線通訊科技的蓬勃發展,包含2G與3G手機、無線區域 網路(Wireless LAN:WLAN)、Bluetooth、Wimax等無線通訊系統, 無線通訊已完全融入我們的生活之中成為人與人之間不可或缺的溝 通方式。同時,要求具備高通訊品質、高資料傳輸率,以及在單位頻 寬內能有更多的頻道可供多人同時使用已成為迫不及待的目標。 總體而言,無線通訊的前端電路是整個系統電路的瓶頸,必須將 基頻訊號加以調變再經由發射機發送射頻訊號至接收端,期間必須抗 拒環境的各種干擾;而在接收機上需要處理極微弱的射頻訊號,並調 變至基頻再進一步做數位訊號的處理。因為射頻電路需要考慮許多參 數,包含了雜訊指數、線性度、功率消耗、阻抗匹配、操作頻率、信 號振幅……等,以符合通訊系統規格的要求,各種參數相互地影響使 得設計上更為困難。 另一方面,由於半導體技術不斷的進步,電晶體的單位電流增益 頻率(fT)與最大振盪頻率(fmax)亦不斷的提升,使得射頻電路朝向 整合至積體電路中以達到成本降低、體積縮小、消耗功率降低及可高 重覆性製作的目標前進;然而,隨著電路操作頻率的升高,電晶體模 型只能描述部份現象,就算做了Layout上寄生效應的萃取,並不能保 證設計電路正常運作,為了可以得到更正確的電路行為,訊號的走線 與被動元件都需經過EM模擬以估測高頻訊頻的耦合效應,如此一來 使得射頻積體電路在設計上的困難度更加提升數倍。 而在射頻晶片製程技術上,由於CMOS技術的成本較低且有極佳 的系統整合能力,使用CMOS製程技術在單一晶片上同時實現射頻前

端電路及基頻電路已是最新的趨勢。但從特性觀點來看,PHEMT、 MHEMT與SiGe BiCMOS之製程技術有更高的截止頻率、更高的轉導 值,用來實現射頻前端電路相對CMOS消耗較少的功率,所以這類技 術非常適合高速電路之應用。而本篇論文將採用上述之技術來設計混 頻器、除頻器與振盪器等電路來展示其製程的特色。

1.2 論文組織

本論文分為五個章節,第一章為導論,說明研究動機及論文組 織。第二章介紹寬頻被動元件Marchand balun與其衍生應用,並實作 在損耗的矽基版上,接著與主動式混頻器結合,將balun整合至積體 電路中,並比較其特性。第三章為除頻電路的設計與實作,介紹除頻 電路在接發機上的應用與不同類型除頻電路的架構與原理。第四章為 正交相位壓控振盪器,將介紹振盪器的基本原理與振盪器重要的規格 相位雜訊,接著介紹正交相位振盪器的原理與種類。第五章對於電路 設計與實作結果做一結論。第二章

不同類型Marchand balun

特性比較與混頻器設計

2.1 前言

近年來,由於無線通訊的普及,使得無線通訊系統的需求量大 量成長,對於單晶微波積體電路(MMIC)與射頻積體電路(RFIC)的通 訊元件需求量也持續地增加,而射頻積體電路的設計,從電感、變壓 器等被動元件的整合,逐漸到各種微波被動電路都得整合在單一晶片 中。在大部分的電路運作中都是以差動(differential)訊號為主,但 是射頻訊號的傳送卻是以單端訊號(single ended)為主,因此balun 在 無 線 系 統 中 為 一 個 不 可 或 缺 的 電 路 原 件 ( balun 為 balance to unbalance的縮寫),提供單端訊號與差動訊號之間的互相轉換,單端 的訊號經過理想的被動式balun後會產生-3dB的能量衰減與相位差 180度的輸出訊號,而balun可用的工作頻寬是最常被用來評斷balun 特性好壞的依據,如何設計一個寬頻的balun是一項挑戰。寬頻被動 Balun中最常見的為Marchand balun,這種類型的balun又可細分為不同 類型,本章節將討論不同類型的Marchand balun的特性與優劣,接著 將不同類型的Marchand balun與主動式的混頻器結合,由混頻器所表 現的特性間接來探討不同類型Marchand balun特性對電路的影響。2.2 不同類型Marchand balun比較與實作

2.2.1 耦合傳輸線

Marchand balun為二組四分之一波長的耦合傳輸線所組成,耦合 傳輸線即是將二條傳輸線互相靠近,讓二條傳輸線之間做電磁場的耦 合,耦合線大略可分為二類,一為邊緣耦合(edge couple)傳輸線, 為最常見的耦合線結構,二為寬邊耦合(broadside couple)傳輸線,其結構為圖2.1所示,S=耦合線的間距,d=基板的厚度,W=傳輸線的 寬度。傳統微波電路要製作寬邊耦合有物理結構上的困難,然而在IC 製程上提供多層金屬供設計者選擇,可輕易地實現寬邊耦合的結構。 S W GND d S W GND ( )a ( )b d 圖2.1 (a)邊緣耦合傳輸線 (b)寬邊耦合傳輸線 耦合線在中心頻長度為

λ

/ 4

時,耦合係數 C 與傳輸係數 T 兩者 滿足: 2 2 2 21 without loss

1 with loss

C

T

C

T

⎧

+

=

⎪

⎨

+

<

⎪⎩

,

,

透過奇偶模(odd mode,even mode)分析,假設奇偶模的特性 阻抗分別為Z0o與Z0e,則耦合線的耦合系數C定義成: 0 0 0 0 e o e o Z Z C Z Z − = + ………… (式2.1) 一般而言,量測微波網路的特性阻抗是 50Ω,給定Z0 = Z Z0e 0o 根 據式(2.1),可以得到: 0 0 1 1 e C Z Z C + = − …………(式 2.2) 0 0 1 1 o C Z Z C − = + …………(式 2.3) 由上式可發現,當耦合量足夠大的時候,偶模的阻抗 Zoe會比奇 模的阻抗 Zoo大很多,在傳統微波電路設計上耦合傳輸線通常只能實 現邊緣耦合傳輸線,若要得到較大的耦合量,兩條傳輸線的距離必須

十分靠近,可能無法實作。

2.2.2 二種 Marchand balun 與二種 0

o,0

o分波器

從傳統式的 Marchand balun 可以延伸出四種類型的 Marchand balun(圖 2.2)[4],利用傳輸線理論來推導這四種 Marchand balun 之 散射參數(scattering parameter)[6],發現 Type II 為窄頻的電路,Type III 達到輸入匹配時需要 C > 1 是無法實現的,所以我們有興趣的為 Type I 與 Type IV 之 Marchand balun,Type I 為一般常見的 Marchand balun,而 Type IV 另一類型的 Marchand balun。

O/C

Port1

Port 2 Port 3

O/C

Port1

Port 2 O/C O/C Port 3

O/C Port1 Port 2 Port 3 O/C O/C Port1 Port 2 Port 3 I Type Type II III Type Type IV 圖 2.2 四種類型 Marchand balun Type I (0o,180o)散射矩陣 [ ] 2 [ ] 2 2 2 4 3 3 2 2 2 2 2 2 2 3 2 2 2 2 2 2 2 2 2 2 2 2 2 1 1 1 3 2 2 2 2 2 2 2 2 2 1 3 2 1 2 1 1 1 1 1 1 1 2 1 1 2 1 1 1 1 1 1 1 1 lossless st T j C st C C C C C T CT CT j j C CT CT C C C C C C CT C T C T C C C S CT T C S j C C C C C CT C T C T CT C T C C C =− − − − − ⎡− + − + − ⎤ − ⎢ + + + ⎥ + + + ⎢ ⎥ − − ⎢ ⎥ = −⎢ + − + − ⎥⎯⎯⎯⎯⎯→ = + + + + + ⎢ ⎥ ⎢ − − − + ⎥ ⎢ + + + ⎥ ⎣ ⎦ 2 2 2 2 2 2 2 2 1 2 1 2 1 1 1 1 C C C C C C j C C C ⎡ ⎤ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ + ⎢ ⎥ ⎢ − − ⎥ ⎢− ⎥ ⎢ + + + ⎥ ⎣ ⎦ 無耗損情況下, 1 3 C= 時,S11 會達到完美的匹配。

Type IV(0 ,180 )散射矩陣 2 2 2 2 4 3 3 2 2 2 2 2 2 2 3 2 2 2 2 2 2 2 2 4 2 2 2 1 4 2 3 2 2 2 2 2 2 2 2 2 2 3 2 1 2 1 2 2 2 1 1 1 2 1 [ ] [ ] 1 1 1 2 2 1 1 1 lossless th T j C th C j C C j C C C C T TC T TC TC C C C T T T C T C T T C j C C C S TC C T S T T T C C T T C T C TC T C T T T =− − − − − − ⎡ ⎤ − − − − + ⎢ − − − ⎥ − − − ⎢ ⎥ − − ⎢ ⎥ = −⎢ − − − + ⎥⎯⎯⎯⎯⎯→ = − − − − − ⎢ ⎥ ⎢ + + − − ⎥ ⎢ − − − ⎥ ⎣ ⎦ 2 2 2 2 2 2 2 2 2 2 2 2 2 1 2 2 2 2 2 C C C j C C C C C C C ⎡ ⎤ ⎢ ⎥ ⎢ ⎥ ⎢ − ⎥ ⎢ ⎥ − ⎢ ⎥ ⎢− − − − ⎥ ⎢ ⎥ ⎢ − − − ⎥ ⎣ ⎦ 無耗損情況下, 2 3 C= 時,S11 會達到完美的匹配。 觀察圖 2.2 可以發現一個有趣的現象,若將 Type I 的 Marchand balun 開路端變短路端,短路端變開路端,則形成如圖 2.3 Type V 的 分波器,若將 Type IV 的 Marchand balun 開路端變短路端,短路端變 開路端,則形成如圖 2.3 Type VI 的分波器。

O/C

Port1

Port 2 Port 3 O/C

Port1 Port 2 Port 3 / O C / O C / O C

V

Type

Type

VI

圖 2.3 二種類型 0o ,0o分波器 Type V (0o, 0o)散射矩陣 [ ] 2 [ ] 2 2 2 4 3 3 2 2 2 2 2 2 2 3 2 2 2 2 2 2 2 2 2 2 2 2 2 2 5 1 5 3 2 2 2 2 2 2 2 2 2 3 1 2 1 2 1 1 1 1 1 1 1 2 1 1 2 1 1 1 1 1 1 1 1 1 lossless th T j C th C C C C C T CT CT j j C CT CT C C C C C C CT C T C T C C C C S CT T C S j C C C C C CT C T C T CT C T C C C =− − − − − ⎡ ⎤ − − − − − ⎢ + + + ⎥ + + + ⎢ ⎥ − − ⎢ ⎥ =⎢ − − − ⎥⎯⎯⎯⎯⎯→ = − + + + + + ⎢ ⎥ ⎢ − − − ⎥ ⎢ + + + ⎥ ⎣ ⎦ 2 2 2 2 2 2 2 2 1 2 1 1 1 1 C C C C C j C C C ⎡ ⎤ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ ⎢ ⎥ + ⎢ ⎥ ⎢ − − ⎥ ⎢− ⎥ ⎢ + + + ⎥ ⎣ ⎦ 無耗損情況下, 1 3 C = 時,S11 會達到完美的匹配。Type VI(0o,0o) 2 2 2 2 4 3 3 2 2 2 2 2 2 2 3 2 2 2 2 2 2 2 2 6 2 2 2 1 6 2 2 3 2 2 2 2 2 2 2 2 2 3 2 2 1 2 1 2 2 2 1 1 1 2 1 2 [ ] [ ] 1 1 1 2 2 1 1 1 lossless th T j C th C j C C j C C C C T TC T TC TC C C C T T T C T C T T C j C C C C S TC C T S T T T C C C T T C T C TC T C T T T =− − − − − − ⎡ + + + ⎤ − ⎢ − − − ⎥ − − − ⎢ ⎥ − ⎢ ⎥ =⎢ + + + ⎥⎯⎯⎯⎯⎯→ = − − − − − − ⎢ ⎥ ⎢ + + + ⎥ ⎢ − − − ⎥ ⎣ ⎦ 2 2 2 2 2 2 2 2 2 2 2 1 2 2 2 2 2 C j C C C C C C C ⎡ ⎤ ⎢ ⎥ ⎢ ⎥ ⎢ − ⎥ ⎢ ⎥ − ⎢ ⎥ ⎢− − − ⎥ ⎢ ⎥ ⎢ − − − ⎥ ⎣ ⎦ 無耗損情況下, 2 3 C= 時,S11 會達到完美的匹配。

2.2.3 Type I與Type IV Marchand balun實作

(TSMC 0.18µm CMOS)

Marchand balun 二對耦合線在中心頻的長度為

λ

/ 4,以微帶線式 的耦合線來實作的話,低頻電路尺寸會非常大,難以整合至積體電路 中;以螺旋型線圈型式之耦合線來設計的話,可以有效地縮小 layout 面積,Type I 與 Type IV 的 layout 如下圖所示。Port1 O/C Port 2 Port 3 Port1 O/C Port 2 Port 3 Type I Port1 Port 2 Port 3 Type IV Port1 Port 2 Port 3 /C S /C S

因為二種類型需要不同的耦合量來達到 S11 的匹配,在 IE3D 模 擬 layout 如圖 2.5 所示,Type I 的耦合量較低利用邊緣耦合即可達成, 但是 Type IV 需要較高的耦合量,採用寬邊耦合的結構來設計。 Port1 Port2 Port3 Gnd Gnd Port1 Port2 Port3 Open Gnd

Edge coulpling

Broadside coulpling

I

Type

Type

IV

量測結果 (1) Magnitude Response Type I 0 10G 20G 30G 40G -25 -20 -15 -10 -5 0 5 Magn it ude (d B) Freq (Hz) S11 S21 S31

圖 2.6 Type I magnitude response Type IV 0 10G 20G 30G 40G -25 -20 -15 -10 -5 0 5 M a g n it ud e ( d B ) Freq (Hz) S11 S21 S31

(2) Phase Response Type I 0 10G 20G 30G 40G -200 -150 -100 -50 0 50 100 150 200 phase ( d egree) Freq (Hz) S21 S31

圖 2.8 Type I phase response

Type IV 0 10G 20G 30G 40G -200 -150 -100 -50 0 50 100 150 200 ph ase (deg ree) Freq (Hz) S21 S31

(3) Magnitude difference 0 10G 20G 30G 40G -6 -4 -2 0 2 4 6 Ma gnitu de e rror (d B) Freq (Hz) Type I Type IV

圖 2.10 Type I VS. Type IV S21 and S31 magnitude error (4) Phase difference 0 10G 20G 30G 40G -180 -120 -60 0 60 120 180 P ha s e di ff er e nc e ( d eg re e) Freq (Hz) Type I Type IV

表 2.1 Type I and Type IV Marchand balun Summary

Die photo1

port

2

port

3

port

Type I

Type IV

Open Pad

3

port

2

port

port

1

圖 2.12 Type I and Type IV Marchand balun die photo

Technology TSMC 0.18µm CMOS

Type I (edge couple) IV (broadside couple)

Center Frequency 10GHz 12GHz

S11@Center Frequency -17.3 dB -17.5 dB

S21@Center Frequency -4.7 dB -6.3 dB

S31@Center Frequency -5.6dB -6.6 dB

Phase difference 171 deg 177.5 deg

S11 < -10dB S11 < -12dB 6GHz~17GHz 7GHz~14GHz 5GHz~40GHz 7GHz~25GHz Die size 220 µm x 450 µm 170 µm x 320 µm

結果與討論

實測結果顯示,Type IV Marchand balun 不管是在 port2 與 port3

的 magnitude error 上或是在 phase difference 上的特性皆比傳統式的 Type I Marchand balun 佳。由輸入匹配來看,在二個 type 的中心頻率, Type I 的 return loss S11 為-17.3dB 而 type IV 的 return loss S11 為 -17.5dB。一般而言,可用頻率為 S11 在-10dB 以下之操作頻寬,但因 為 Type IV 高頻表現較大損耗,使得 S11 在高頻皆小於-10dB,無法 代表其真正操作頻寬,所以我們以 S11 小於-12dB 來比較二者的頻 寬,在此條件下 Type I 頻寬為 7GHz~14GHz 而 Type IV 為 7GHz ~ 25GHz,操作頻寬明顯地為 Type IV 較寬,與理論相符。此外,因為 Type IV 為寬邊耦合的結構,故其電路尺寸相對於 Type I 而言比較 小;但是訊號在高頻的損耗,Type IV 寬邊耦合結構較嚴重。

2.2.4 Type V 與 Type VI 0

o,0

o分波器實作

(TSMC 0.18µm CMOS)Type V 與 Type VI 只是在 Type I 與 Type IV 上將開路改成短路, 短路改成開路,需要的耦合係數並沒有改變,故 Type V 依舊為邊緣 耦合的結構而 Type VI 依舊為寬邊耦合的結構。在電路的佈局上,只 是將 2.2.3 節的實作之開路改成短路,而短路改成開路。佈局示意如 圖 2.13。

Port1 O/C Port 2 Port 3 Port1 O/C Port 2 Port 3 Type V Port1 Port 2 Port 3 Type VI Port1 Port 2 Port 3 O/C O/C

O/C O/C O/C

O/C O/C O/C Port1 Port 2 Port 3 Open GND Port1 Port 2 Port 3

Edge coupling Broadside coupling

圖 2.13 螺旋型線圈式 Type V 與 Type VI IE3D layout

量測結果 (1)Magnitude Response Type V 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -25 -20 -15 -10 -5 0 Magnitude (dB) Freq (Hz) S11 S21 S31

圖 2.14 Type V magnitude response Type VI 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -25.0 -20.0 -15.0 -10.0 -5.0 0.0 Magni tude (dB) Freq (Hz) S11 S21 S31

(2)Phase Response Type V 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -120 -100 -80 -60 -40 -20 0 20 40 60 80 100 120 140 160 Ph ase (d egr ee) Freq (Hz) S21 S31

圖 2.16 Type V phase response

Type VI 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -100 -80 -60 -40 -20 0 20 40 60 80 P h as e ( de gr ee ) Freq (Hz) S21 S31

(3)Magnitude difference 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -6 -4 -2 0 2 4 6 Mag n it ude er ror (dB ) Freq (Hz) Type V Type VI

圖 2.18 Type V VS. Type VI S21 and S31 magnitude error

(5) Phase difference 0.0 2.0G 4.0G 6.0G 8.0G 10.0G 12.0G 14.0G 16.0G -50 -40 -30 -20 -10 0 10 20 30 40 50 Ph ase dif fe renc e (deg ree ) Freq (Hz) type5 type6

表 2.2 Type V and Type VI 0

o,0

o分波器 Summary

Die photo

Type V

Type VIOpen Pad

1

Port

Port

2

Port

1

2

Port

3

Port

3

Port

圖 2.20 Type V and Type VI 0o

,0o分波器 die photo

Technology TSMC 0.18µm CMOS

Type V(edge couple) VI(broadside couple)

Center Frequency 6GHz 6Hz

S11@Center Frequency -9.4 dB -14.8 dB

S21@Center Frequency -5.3 dB -5 dB

S31@Center Frequency -5.7dB -5.5 dB

Phase difference 4 deg 3.6 deg

S11 < -10dB NO 4.5GHz~7.5GHz

結果與討論

實測結果顯示,Type VI 不管是在 port2 與 port3 的 magnitude error

上或是在 phase difference 上的特性皆比 Type V 要。雖然傳輸線的結 構與 2.2.3 節實作一樣,只是開路與短路互換的不同,但我們可以發 現 Type V 與 Type VI 在 port 2 與 port 3 的 magnitude 的差異大多在 1dB 以內,而相位差 Type VI 都在 3 度以內,Type V 的相位差則不盡理想, 只有窄頻在相位差 3 度以內。輸入匹配並不如預期有達到寬頻的匹 配,可能是因為電路結構負戴的不同導致寄生效應也不一樣,使得原 本設計的耦合量離開我們所需的值,這是此次設計上的一大缺失。不 由相位差的響應看來,利用理想無損耗四分之一波長的耦合傳輸線來 推導 Marchand 式 0o,0o分波器的散射矩陣是正確的,但傳輸線在矽 基板上的損耗所造成的非理想效應,在 0o,0o分波器上影響很大,散 射參數推導中必須考慮耗損效應才能描述切確 magnitude 響應特性。

2.3 結合Marchand balun混頻器之設計與實作

2.3.1 研究動機

由上一節可以發現,Type IV Marchand balun 的頻寬較傳統式 Type I Marchand balun 的頻寬更寬,是因為 Type IV 為了輸入阻抗匹 配需要較高的耦合係數,接著我們將這二類的 balun 與混頻器結合, 比較這二種類型 balun 與主動電路結合時主動電路特性的優劣。為了 顯現出 balun 的影汱,在主動混頻器電路設計完全一樣,而且使用最 簡單的電路結構。

2.3.2 實作電路架構

本地震盪源輸入極

LO 端我們採用 Marchand balun 產生 differential 訊號,其理論在 上一節已做分析,而佈局結構如圖 2.5 所示,Type I 為邊緣耦合,Type IV 為寬邊耦合,訊號由 port 1 進去到另一端為開路,耦合到 port 2 和 port 3 出去,且為差動訊號輸出。Type 1 之 port 2 與 port 3 中間為 Common ground,在整合於混頻器時,我們將 common ground 節點利 用電容讓 LO 較高頻訊號在此點看到 ground,而 LO 所需要的 DC 訊 號由 Common ground 那一點注入混頻器內,如圖 2.21(a)所示;而 Type IV 之 port 2 與 port 3 之中心點為一傳輸線,我們使用大電阻當 成 choke 把 DC 訊號由此節點灌入,如圖 2.21(b)。 O/C LO

2

Port

3 Port LO input Type IV LOPort

2

3 Port Bias Bias LO input Type I( )

a

( )b 圖2.21 混頻器本地振盪源輸入端偏壓電路因為放在 Gilbert 混頻器的 LO 端,如果 Marchand balun 所產生 的信號 Port2 與 Port3 不夠平衡,埠對埠的隔離度會變差,但對於 Magnitude 誤差的要求並不嚴格,只要 LO 的輸入功率夠大,足夠讓 Gilbert cell 的電晶體產生電流交換的效果,即可達到混頻的效果。

射頻輸入極

Gilbert mixer 射頻輸入極為一個 differential pair 放大器,將 RF 訊號由電壓轉為電流,而電流經過上面 LO 四個電晶體電流的切換來 達成混頻,但此架構在 RF 端需要做阻抗的匹配, L-type 匹配網路 會佔較大的面積,此外,我們還需要一個 balun 將 RF 單端訊號轉成 差動訊號,被動的 balun 在低頻所佔面積將會很大;但射頻輸入極若 以微混頻器為主體的話[7]如圖 2.22,在輸入端的轉導放大器由 Q1、 Q2 和 Q3 構成,它是一個 Single to Differential 之電路,Q2 為共射極 (common emitter)轉導放大器,將輸入電壓轉換成反相電流,而另 一端 Q3 為共基極(common base)轉導放大器,會產生與共射極反 相之電流,則可得到 RF 差動電流訊號,所以只需要單端輸入訊號即 可。輸入阻抗匹配部分,可設計電阻 r1、r3 和電晶體的 1/gm 提供輸 入電阻匹配: 1 3 1 3 1 1 // 50 r r gm gm ⎛ ⎞ ⎛ ⎞ + ⎜ + ⎟= Ω ⎜ ⎟ ⎝ ⎠ ⎝ ⎠ 。使用微混器的好處在於 RF 輸入端不需要額外的被動式 balun 與輸入阻抗匹配,可以減少電路所 佔面積,而且在量測考量上,單端訊號輸入較易量測。 1 Q Q2 3 Q Q4 1 r r2 3 r r4 in V in R m in g R + m in g R − Mixer core 圖2.22 微混頻器射頻輸入端電路

整體電路圖 IF RF 1 VCC Micromixer Bias Type I or Type IV Marchand balun LO 2 VCC 圖 2.23 結合 Marchand balun 混頻器整體電路圖 射頻輸入端與本地振盪源輸入端的電路如同上述,在輸出緩衝極 的電路採用共集極(common collector)與共射極作為中頻訊號(IF) 輸出端的緩衝器,將差動輸出訊號做功率合成轉換成單端輸出,以方 便量測。

2.3.3 實測結果

(1) 轉換增益 VS. LO 功率 -15 -10 -5 0 5 10 15 20 -20 -15 -10 -5 0 5 10 Conversion G a in (dB) LO power (dBm) RF 2GHz RF 3GHz RF 5GHz RF 7GHz RF 9GHz RF 11GHz RF 13GHz Type I CG VS. LO power 圖 2.24 Type I 轉換增益 VS. LO 功率 -15 -10 -5 0 5 10 15 20 -20 -15 -10 -5 0 5 10 Conversion G a in (dB) X Axis Title RF 1GHz RF 3GHz RF 5GHz RF 7GHz RF 9GHz RF 11GHz RF 13GHz RF 15GHz Type IV CG VS. Lo power 圖 2.25 Type IV 轉換增益 VS. LO 功率(2) 轉換增益 VS. RF frequency(RF bandwidth) 0 2 4 6 8 10 12 14 16 18 20 -10 -5 0 5 10 15 Conversio n G ain (dB) RF frequency (GHz)

Type 1 Marchand balun Type 4 Marchand balun RF Bandwidth 圖 2.26 轉換增益 VS. RF frequency (3) RF@7GHz-轉換增益 VS. IF frequency(IF bandwidth) 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 -4 -2 0 2 4 6 8 10 Conversion G a in (dB) IF frequency (GHz)

Type I Fixed LO6.9GHz~8dBm Type IV Fixed LO6.9GHz~6dBm

(4) P1dB / IIP3(線性度) -24 -22 -20 -18 -16 -14 -12 -10 -8 -6 -4 -2 0 2 -60 -50 -40 -30 -20 -10 0 10 P1dB = -9 dBm IIP3 = -2 dBm TYPE I RF=7G Pout (dBm ) RF power (dBm) IF IM3 -24 -22 -20 -18 -16 -14 -12 -10 -8 -6 -4 -2 0 2 -60 -50 -40 -30 -20 -10 0 10 P1dB =-10 dBm IIP3 = -2 dBm TYPE IV RF=7G Pout (dBm ) RF power (dBm) IF IM3

圖 2.28 Type I P1dB and IIP3 @ RF 7GHz 圖 2.29 Type IV P1dB and IIP3 @ RF 7GHz

2 4 6 8 10 12 14 -14 -12 -10 -8 -6 -4 -2 0 2 4 P1dB/II P3 (dBm) Frequency (dBm) Type I P1dB Type I IIP3 Type IV P1dB Type IV IIP3 P1dB/IIP3 圖 2.30 P1dB and IIP3

(5) Isolation 0 2 4 6 8 10 12 14 16 -55 -50 -45 -40 -35 -30 -25 -20 -15 -10 -5 Is olati on (dB ) Frequency (GHz) LOtoIF LOtoRF RFtoIF Type I 圖 2.31 Type I isolation 0 2 4 6 8 10 12 14 16 -55 -50 -45 -40 -35 -30 -25 -20 -15 -10 -5 Is olati on (dB ) Frequency (GHz) LOtoIF LOtoRF RFtoIF Type IV 圖 2.32 Type IV isolation

(6) RF and LO 輸入返回損耗 0.0 5.0G 10.0G 15.0G 20.0G -25 -20 -15 -10 -5 0 Inpu t retrun lo ss (dB ) Frequency (Hz) RF Port LO Port Type I 圖 2.33 Type I 輸入返回損耗 0.0 5.0G 10.0G 15.0G 20.0G -25 -20 -15 -10 -5 0 Inpu t return lo ss (dB ) Frequency (Hz) RF port LO port Type IV 圖 2.34 Type IV 輸入返回損耗

(7) Noise Figure 0.0 500.0M 1.0G 1.5G 0 5 10 15 20 25 30 35 NF (dB) IF Frequency (Hz) RF 3G RF 5G RF 7G RF 9G RF 11G RF 13G RF 15G Type I

圖 2.35 Type I noise figure

0.0 500.0M 1.0G 1.5G 0 5 10 15 20 25 30 35 NF (dB) Frequency (Hz) RF 3G RF 5G RF 7G RF 9G RF 11G RF 13G RF 15G Type IV

Die photo

GND

DC

DC

DC

LO

RF

IF

圖 2.37 結合 Marchand balun Type I 混頻器 die photo

GND

DC

DC

DC

LO

RF

IF

Chip performance

Process TSMC 0.35μm SiGe BiCMOS

Marchand Balun Type I IV

Supply Voltage 3.3V 3.3V

Supply Current 2.54mA 2.5mA

RF/LO/IF Frequency 7GHz/6.9GHz/0.1GHz 7GHz/6.9GHz/0.1GHz Conversion Gain 4.9dB 4.8dB P1dB / IIP3 -9dBm /-2dBm -10dBm/-2dBm RF Bandwidth 3GHz~13GHz 1GHz~15GHz IF Bandwidth 20MHz~900MHz 20MHz~900MHz S11(RF match) <-10dB <-10dB NF 14.2dB 13.8dB LO-to-IF isolation <-25dB <-25dB LO-to-RF isolation <-20dB <-25dB RF-to-IF isolation <-20dB <-20dB Power consumption 8.4 mW 8.3mW Chip Size 0.95 x 0.86 mm2 0.86 x 0.71 mm2

表 2.3 Marchand balun 混頻器 performance summary

2.3.4 結論與討論

我們可以發現除了 RF 操作 3dB 頻寬 Type IV 1GHz ~ 15GHz 比 Type I 3GHz ~ 13GHz 明顯還要寬,除此之外,其它特性皆差不多: RF 在中心頻率 7GHz 的轉換增益分別為 Type I 4.9 dB 與 Type IV 4.8 dB,僅相差 0.1dB;IF 寬頻二者皆為 0.2MHz ~ 900MHz;在 RF 輸入 返回損耗,透過微混頻器的特性,在所有頻率皆小於-10dB,為非常 好的匹配;因為主動電路設計皆相同,消耗功率亦差不多。在晶片的 大小方面,是被 Marchand balun 大小所限制,因為 Type IV Marchand balun 為寬邊耦合(without offset)面積較小;而 Type I Marchand balun在此 IC 製程技術上需要的耦合量,利用邊緣耦合結構無作實現,也 是採用寬邊耦合(with offset)故面積較大。從這二個電路的實作結 果可發現 RF 操作頻寬是被本地振盪源的元件特性所限住,且 RF 工 作頻寬結果顯示與 Marchand balun 的測試件得到相同的結果,即為 Type IV Marchand balun 需要較大的耦合量,故有較寬的操作頻率。

第三章

3.1 前言

在通訊系統之中,不管是在發送端或是接收端都需要有一個穩 定的本地端信號,本地端信號常常需要利用頻率合成器或是鎖相迴 路,將壓控振盪器的輸出信號穩定後,降低相位雜訊以符合通訊系統 的需求才能運用,故接收機中所用到的VCO通常會嵌入在頻率合成器 中 , 使 輸 出 頻 率 更 為 隱 定 。 頻 率 合 成 器 大 致 可 分 為integer-N 和 fractional-N架構,在這二種架構中通常需要除頻器來將VCO振出的訊 號降至低頻,與石英振盪器或其他準確度高的振盪訊號作相位比較。 除頻器的電路設計可區分為二類:(1) 數位電路,利用數個D-type Flip-Flop(DFF)做邏輯的推算形成計數器(counter)設計方式,可實 現高除數的除頻器。(2)類比電路,適合於高頻、低消耗功率的設計, 常見有訊號再生式除頻電路(Regenerative frequency divider)與注入 鎖住式除頻電路(Injection locked frequency divider)二種架構。不同 架構有個別的優缺點,可依系統需求擇一使用。 除頻電路除了在頻率合成器中被廣泛的運用之外,在鏡像消除 的接收機架構下,需要利用正交相位的本地訊號來達成鏡像消除的功 用,因為除頻電路的輸出訊號本身具有多相位的特性,所以除頻電路 常 被 拿 來 做 為 正 交 相 位 訊 號 的 產 生 電 路 ; 鏡 像 消 除 比 例 (Image rejection ratio)和本地訊號正交相位準度相關之外,和本地訊號的工作 週期(duty cycle)也有相關,如何使數位式奇除數的除頻電路可以輸 出50 %工作週期的訊號也是一重要的研究重點。3.2 除頻電路的應用-頻率合成

3.2.1 頻率合成器(Synthesizer)在收發機上的應用

在一般的無線通訊系統會要求振盪頻率移動數十kHz來做接傳訊 號的頻段切換,所以必須借重頻率合成器來完成符合系統要求的跳頻 動作,架構如圖3.1所示。 LNA PA Selection Channel Filter Duplexer Synthesizer Frequency 圖3.1 頻率合成器在收發機上的應用 除了上述的要求外,頻率合成器還需要考慮spur (sideband)以及 locking time(settling time)、phase noise,這些因素都會影響收發機的 特性。一般獨立的VCO輸出訊號不會有spur產生,不過置入到頻率合 成器後就會有spur出現。Spur對接收訊號的影響可以由圖3.2來說明。 Input RF Output r Synthesize Output IF Interferer Signal Desired LO Sideband ω ω ω LO ω ωS RF ω ωint IF ω 圖3.2 Spur對接收訊號的影響當頻率合成器的輸出除了

ω

LO外還有spur在ω

s,若接收機的接收 的訊號除了ω

RF還有干擾源ω

int,當ω ω

s−

LO=

ω

int−

ω

RF關係成立, 在ω

LO把ω

RF的訊號降到IF band(ω

IF )的同時ω

s也把干擾源ω

int降到IF

ω

,造成訊號的損毀。所以一般的系統會要求spur要比carrier低 60dB,不然就是將ω ω

s−

LO的間隔變大,讓干擾源ω

int可以用duplexer 或band pass filter來抑制。從頻域觀察頻率合成器的settling time可清楚地說明settling time 對接發機系統的影響。圖3.3為VCO輸出的頻率變化在頻率合成器從 有某一channel頻率跳到

ω

O channel時的示意圖: ω oω

ω

oω

ω

oω

t

cont V 圖3.3 頻率合成器跳頻時VCO輸出頻率變化 可以發現在VCO的控制電壓Vcont未達到穩定時,VCO輸出的頻率一 直在變化,在接收訊號時會將adjacent channel之訊號給接收到系統 中;在傳發訊號時將會把adjacent channel的訊號給發送到傳送頻道 上,對於接發機的特性造成影響如圖3.6所示。ω

Adjacent Channel Desired Channel Received Channelω

Adjacent Channel Desired Channel Transmitted Channel( )

a

( )

b

圖3.4 頻率合成器settling time對接發頻道的影響 因為除二的速度比高除數的除頻器還要快,所以被用來接在頻率 合成器的VCO之後當成前置除頻器(prescaler),將頻率降到可程式 除頻器可用的範圍(圖3.5)。 PD LPF VCO M ÷ REF f fout Programmable divider 2 ÷ Prescaler 圖3.5 除二電路在頻率合成器的應用-前置除頻器3.2.2 直接頻率合成-Carrier Frequency Generator

Ultra-Wide-Band (UWB) 系統跳頻需求為了達到高速的無線通訊需求,UWB通訊系統為目前廣受大家研 究的題目,其頻譜位於3.6GHz~10.1GHz,在7.5GHz的頻譜中可分為 14個頻帶的運用,而每個頻帶有528MHz的頻寬,根據不同模組 (mode1 and mode2)而運用不同的頻帶群。因為UWB為MB-OFDM (multi-band orthogonal frequency division multiplexing)系統,一般的 頻率合器並不適用在UWB的系統上,主要的原因有二項,一是因為

頻率合成器很難達到寬頻的頻率合成,以mode 2為例,mode 2包含7 個頻帶,頻率合成器很難達到3.1GHz~8.2GHz的頻率合成;二是因為 一般頻率合成器跳頻速度約在數十µs,而系統要求要少於9 ns,這顯 示在UWB的收發機上,不同頻率的產生與合成需要透過別的方式來 達成,透過frequency planning,direct frequency synthesizer被用來達到 產生寬頻的載波(carrier frequency generation)。

UWB Mode 1和Mode 2 載波頻率產生器架構

Mode 1的頻帶如下圖3.6所示: 在mode 1下的運作,需要在3.4GHz~4.5GHz的頻譜裡產生三個載 波分為3.432GHz、3.96GHz與4.488GHz。因為要做頻率的合成,載波 產生電路必定包含可轉換頻率的電路:倍頻器、混頻器與除頻器。在 設計上首先做頻譜規畫而決定輸入的載波,頻率合成的方式會根據頻 譜規畫的方式不同而不同。

f

#1 Band # 2 Band #3 Band 3432 MHz 3690 MHz 4488 MHz圖3.6 Frequency of operation for a mode 1 device

圖3.7為mode 1載波產生電路的一個例子,輸入訊號為3.96GHz, 經過一個除3電路(一個SSB混頻器與一個除電路所組成)與除2.5電 路(一個SSB混頻器與二個除2電路所組成)後再與電路輸入訊號做 混頻,利用SSB混頻器的頻帶選擇交換,可得到upper band訊號、本 身輸入訊號和lower band訊號輸出三個載波訊號,這個方式的頻率交 換速度可以小於9ns。

/ @3.96PLL VCOGHz ÷2 ÷2 2 ÷ mixer SSB SSBmixer 528MHz

3

÷

÷2.5 3.432GHz/ 3.96GHz/ 4.488GHz圖3.7 Direct frequency synthesizer for UWB mode 1 application Mode 2的頻帶如下圖3.8 所示 在mode 2下的運作,在3.4GHz~8GHz頻譜中有七個頻帶在運用,頻帶 的中心頻率如圖上所示。

f

#1 Band # 2 Band #3Band 3432 MHz 3690 MHz 4488 MHz #6 Band #7 Band #8 Band 6336 MHz 6864 MHz 7392 MHz #9 Band 7920 MHz圖3.8 Frequency of operation for a mode 2 device

頻率合成方式也是由不同的頻率規畫而由所不同。圖3.9為產生7 個頻帶輸出的例子。輸入頻率為16.896GHz,電路中包含二組SSB混 頻器、八個除二電路與二組switched buffer選擇輸出頻率。 / @16.896PLL VCOGHz ÷2 SSB mixer 2 ÷ ÷2 2 ÷ ÷2 2 ÷ ÷2 2 ÷ Switch buffer Freq Out Switch buffer SSB mixer

我們可以發現不管是頻率合成器或者是直接頻率合成電路,只要 是電路中有需要頻率轉換的動作,除頻器是不可或缺的一個子電路, 特別是在寬頻的頻率合成中,除二電路的運用是不可避免的。

3.3 除頻電路的應用-收發機上正交訊號的產生

3.3.1 鏡像消除接收機與單頻帶升頻器

Homodyne 接收機在降頻時直接把 RF 訊號降到基頻,所以被稱為 zero-IF 或直接降頻。Zero-IF 與 Low-IF 是目前被廣泛運用的接收機架 構,由於此架構不需使用外接的被動元件(濾波器),可用單一積體 電路來實現,所以在無線收發機設計時常會使用該架構。但為了避免 傳收訊號的不完全,此架構需正交相位的本地振盪器訊號來傳收訊 號。目前廣泛使用的鏡像消除接收架構為Hartley 架構與 Weaver 架 構,二者皆需要使用到正交相位的本地振盪器。 單頻帶升頻器中,需要輸入正交的基頻訊號,透過一組正交相位 的LO訊號將基頻訊號升頻到高頻,而單頻帶的操作原理可由下式來 說明:Output

=

cos

ω

IFt

cos

ω

LOt

±

sin

ω

IFt

sin

ω

LOt

=

cos(

ω

IF∓

ω

LO)

t

只要將升頻後的二路訊號做適當的加減則可以得upper或lower單一頻 帶的訊號。 Output sinωLOt cosωIFt sinωLOt cosωLOt 圖3.10 單頻帶升頻器

上述接收機的兩種架構與單頻帶升頻器都需要正交相位的LO 訊 號,LO 的相位準確度、振幅不一致都會影響到整個架構的 image rejection 與 side band rejection ration 的效果。通常 image rejection ratio 與side band rejection ration 需達到 30 ~ 40dB,LO 只能存在 0.2 ~ 0.6dB 的振幅誤差或是1 ~ 5 度的相位誤差,因此如何產生準確的正交相位 訊號一直廣受大家的研究與討論。 3.3.2 正交訊號的產生方法 正交訊號的產生方式最常見可有三類分別為:被動RC元件組成 的電路、輸出為正交相位的VCO與利用除二電路得到正交相位的輸 出。以下將介紹每種電路的原理與其優缺點。 (1)RC-Network in V 1 out V 2 out V 圖3.11 RC phase shifter 如果我們將一訊號分別經過一個RC與CR的電路如圖3.11(a)所 示,對圖3.11(a)作推導: RC j RC j V sRC sRC V Vout in in ω ω + = + = 1 1 1 → 1 tan 1

(

)

2 RC π − ω ∠ = − 2 1 1 1 1 out in in V V V sRC j RCω = = + + →(

)

1 2 tan− ωRC ∠ = −我們可得到在 1 RC ω= 此頻率輸出二個訊號的相位角度相差90度且振 幅相同,故我們可以利用RC來組成正交相位的產生電路如圖3.11(b) 這個電路雖然簡單,但在積體電路的實作上存在很大的缺點,就是無 法實作出精確的電阻值,而且電路本身振幅的頻率響應是窄頻,當電 阻飄移時,設計中心頻率跟著飄移使得此電路無法使用。若要增加這 個電路的頻寬,則要串接多級的RC-network,但是因為電阻為損耗性 的元件,串接多級的RC-network後訊號的衰減量將相當可觀,可能需 要放大器將訊號損失補償回來,則會增加功率消耗。此外若輸入訊不 是弦波,則輸入訊號存在有諧波項都會通過RC-network,因為不同頻 率的相位與振幅響應都不一樣,會造成輸出訊號工作週期(duty cycle) 的失真。 (2)正交相位輸出VCO 環型VCO是由多級delay cells所組成的(圖3.12),如果N級delay cells串接,每級的相位差等於: N ) 180 360 ( 0− 0 = θ ,所以環型VCO可以 用來產生多相位的輸出。但是因為環型VCO的架構中並沒有頻率選擇 的電路,使得輸出訊號的相位雜訊太差而不適用於現今的收發機。 圖3.12 N級環型VCO 若只是要得正交相位的訊號並考量相位雜訊下,可以使用二組 LC-tank cross-coupled的VCO耦合來得正交相位的輸出,最簡單的架 構如圖3.12 所示。但是這個架構中存在有相位雜訊與相位誤差(phase error)之間的trade off,這會在第4.3節做說明。當VCO的元件中存有

mismatch,則輸出訊號的工作週期也可能失真而非50%工作週期。 VDD M1 M2 A M5 M6 B VDD M3 M4 C M7 M8 D

圖3.13 Cross-coupled VCO with parallel coupling (3)利用除二電路產生正交訊號輸出 利用除二產生正交訊號這種方法為目前較為被廣泛使用的,設計 一個VCO操作在需要正交訊號頻率的兩倍頻,再經過除頻電路後得到 正交相位的訊號(圖3.14)。此方法最大的缺點在於除頻器輸入為二倍 頻訊號,若數位式除頻器要達到高頻操作,則電晶體的current density 必須提高到讓 fT達極值,則增加電路的功率消耗;為了功率的考量, 高速操作的除頻器一般是採用類比方式來設計,所以利用類比式的除 二電路來產生正交訊號也是目前研究的趨勢。 Latch D− Latch D− CLK CLK + I − I + Q − Q CLK I+ I− Q+ Q− 圖3.14 除二輸出正交訊號波形 利用除二電路來產生正交訊號需要二倍頻的輸入訊號,二倍頻的

VCO雖然很難達到50%工作週期的訊號輸出,但非50%工作週期的訊 號經過除二電路後可以達到50%工作週期的輸出,不過除二輸出正交 訊號的精確度會受到VCO輸入訊號的工作週期影響如圖3.15 CLK I+ Q+ CLK

t

Not perfect quadrature

圖3.15 輸入工作週期對輸出正交相位準度的影響

但利用此方法產生正交訊號還有一好處:VCO輸入訊號含有其它 spurs時,spurs經過除二電路會被降低[11]。當輸入訊號頻率為

ω

1,有 相對輸入訊號很小的spur在ω

2=

ω

1+ ∆

ω

處,大小為ε

,如圖3.16 所 示。將spur分為AM與PM二組sideband,大小為1

2

ε

,flip-flop只會對 輸入訊號threshold crossing有反應(假設輸入的differential threshold為 0),而非輸入訊號的大小,故只有PM sideband對flip-flop有影響。 1 ω ω2 ω ∆ 1 ε 1 ω ω2 ω ∆ 1 1 2ε 1 2ε 1 2ε ω ∆ 1 2 2ω ω− 1 ω +∆ 1 ω +∆ ω −∆ ω −∆ ε 1 2ε 圖3.16 將spur分為AM和PM sideband 由時域來看的話(圖3.17),flip-flop輸出的變化只在輸入訊號大於differential threshold且是positive trigger時產生變化,我們可以發現因 為輸出頻率為輸入頻率的一半,所以在

ω

12

頻率的相位變化量相對 於輸入ω

1頻率只有一半,則輸出的PM sideband大小變成輸入的一半 為1

4

ε

,但輸出spur與輸出頻率的間隔不變仍為∆

ω

,即sideband位 於ω

12

± ∆

ω

處。 2 I n p u t ÷ 2 O u t p u t ÷ 1 ω ω +∆ ω −∆ 1 2ε 1 1 2ω ω +∆ ω −∆ 14ε 1 1 2ω ω ∆ 1 1 4ε ω ∆ 圖3.17 除二電路輸入與輸出的波形 因此,輸入訊號的spur經過除二電路後,spur會在輸出頻率的兩 邊頻帶距離相同的頻率偏移量處出現,但大小變成原來的1

4

,故spur 經過除二電路後可以被降低。3.4 高速除頻電路架構

3.4.1 高速Flip-Flop除二電路

簡單來說,除二電路就是利用一個主從式(master-slave)的 flip-flop作正回授(圖3.18),使每個latch的訊號可以操作在high與low二 種狀態。1 Master L Q Q D D 2 Slave L Q Q D D CLK CLK out V 圖3.18 Master-slave flip-flop 除二電路圖 為了達到最高的運作速度,必須採用最快速的電路架構:在BJT 上稱為ECL(emitter coupling logic)或在MOS上稱為CML(current mode logic)。在ECL架構下實現出來的latch電路是由一組differential pair加 上regenerative pair形成(圖3.19),而驅動該電路需要用一組differential 的clock訊號。單一D-latch的運作過程如下:當CLK為high時,訊號由 Vin端讀入differential pair中,此時的regenerative pair處於off狀態;當 CLK為low時,differential pair停止讀取動作,regenerative pair開始將 訊號鎖在該cross-coupled的latch架構中。 VDD in V CLK CLK Differential Pair Regenerative Pair 圖3.19 單一D-latch電路圖 數位式主從式D型存鎖器所組成的除頻電路最高可操作的速度, 就FET而言大約在其1/5到1/4的

f

T(GHz)之間,就BJT而言大約在其1/4到1/3的

f

max(GHz)之間,因此這類的電路若操作在高速,除 了需要較大的功率消耗外還可能需要更先進的製程技術才能達成。3.4.2 訊號再生式除二電路(Regenerative Frequency

Divider)原理與架構

RFD是以regenerative modulation的概念來運作的,regenerative modulation的操作原理我們利用圖3.20來作說明:一個regenerative modulator 架 構 包 含 三 個 部 分 modulatorK

、filter networkN

1與 amplifierµ

並將輸出訊號回授到modulator。 K Balanced Modulator 1 N Filter Network AMPµ in f fout in out nf mf ± ± out f 圖3.20 Regenerative modulator 假設K

為二階的modulator,那麼輸入f

in訊號與輸出f

out訊號經 過modulator作訊號調變後的輸出為f

in±

f

out,當amplifier提供足夠的放大效果補償調變時訊號的損耗和訊號經過filter network的損耗,加 上

f

in±

f

out=

f

out這個關係成立時,f

out訊號便可在迴路中維持與輸 出。只要f

in為一有限的值,則可得到 out=

in2

f

f

關係,即頻率除二的效果。進一步對圖3.19作普遍的分析,即

K

為高階的modulator,可以得到以下的關係式:

n -m

f

inf

out=

f

out(n > m

f

inf

out)………(式3.1)簡化上述二個式子可以得到 out

=

n

inm 1

f

f

±

………(式3.3) 當K

為三階的modulator,可能得到n=1,m=2

為頻率除三的效果。 以上的分析是在networkN

1與amplifierµ

皆不會產生諧波項的 情況下才成立,若我們在迴路中加入產生諧波項電路做分析如圖3.21 所示,可以得到更一般的式子: out=

n

inrm 1

f

f

±

K Balanced Modulator 1 N Filter Network AMPµ in f ±nfin±mfx fout fout Frequency Multiplier R 2 N Filter Network x= out f rf x f圖3.21 Second-order regenerative modulator

圖3.22表示除2 RFD的block diagram,包含Mixer、low-pass filter 以及amplifier,Mixer的功能即作為訊號modulator使用。Mixer的一端 輸入f頻率的輸入訊號,另一端則由輸出端拉回f/2頻率的訊號作混 頻。理想對稱的Mixer只會混出f/2的odd harmonic項,如3f/2、5f/2…, 而這些不要的訊號會被low-pass filter濾掉,只有f/2會被amplifier放 大,藉此也減少conversion loss。 in f =f 12 f,32 f.... 1 2 f

mixer Low pass filter amplifier

1 2 out f = f 圖3.22 除2 RFD block diagram

此電路最高的操作頻率fmax是由loop的upper cutoff frequency決 定,而該cutoff frequency是由mixer和amplifier所限制;相對的,數位 式flip-flop frequency divider的fmax則是受loop delay決定,所以RFD可 以比數位式除頻哈更高頻操作。不過RFD的最低操作範圍fmin=fmax/3 不像數位式可到很低頻,因為當輸入訊號低於該頻率時,3f/2項諧波 就不會被low-pass filter濾掉,會進入mixer與輸入訊號混頻,產生不要 的輸出頻率(fmax/3*3/2=fmax/2)如圖3.23所示。 max f min max ( / 3) f f max/ 2 f max/ 6 f freq o A max/ 3*3 / 2 max/ 2 f =f 圖3.23 除2 RFD的低頻操作限制 因此整個迴路的LPF的corner frequency fLPF需要落在f/2到3f/2 之間。這個電路除了最低操作頻率有限制這個缺點外,因為輸出同時 存 f/2和 3f/2頻率的訊號,f/2訊號的波型在每半週期波型的中間會有 deep notch會降低輸出訊號high和low之間margin。

3.4.3 其它除數訊號再生式除頻電路

RFD最常見的是除2電路架構,但如果要達到其它除數的話,在 迴路裡面則需要加入倍頻器或是除頻器來達成其它頻率的輸出。圖 3.24是除三的RFD架構,可以發現它的電路架構比除2的架構在迴路 裡多了一個除2電路,而且使用的混頻器為SSB架構,利用SSB混頻器 來選擇混頻之後輸出lower sideband之頻率,因為SSB架構需要利用而 二組的正交訊號,所以要正交訊號的輸入,增加了電路的複雜度。2

÷

SSB Mixer inf

Vin_I outf

_ in V Q _ out V I _ out V Q 2 in out out f f f − = 3 in out f = f 圖3.24 除3 RFD電路架構 在回授路徑裡增加了N級的除2電路,則可以達到除2

N−

1

的效 果,如圖3.25所示,若除數愈高所需要的除2電路愈多造成消耗功率 的增加。2

÷

_ in f I N stages of divide-by-2 divider2

÷

÷

2

_ in f Q 2 1 in N I f − 2 1 in N Q f − 2 2 1 N in N f − 1 , 2 2 1 N in N I Q f − − 2 , 2 2 1 N in N I Q f − − SSB Mixer 圖3.25 除2

N−

1

RFD電路架構3.4.4 注入鎖住式除頻電路(Injection Locked Frequency

Divider)原理與架構

ILFD的工作原理是注入訊號到VCO,讓VCO訊號與注入訊號同 步化來達成除頻的動作,此電路的核心為一injection locked oscillator (ILO),以下將先討論free running的VCO模型,接著介紹二種模型 來解擇ILO的操作機制。