國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

利用氟摻雜前處理技術應用於高介電常數

閘極介電層薄膜電晶體之研究

Study on the Electrical Properties of

Fluorine-Incorporated Poly-Si TFTs with

High-

κ Pr

2O

3Gate Dielectric

研 究 生:張宏仁

指導教授:羅正忠 博士

邱碧秀 博士

利用氟摻雜前處理技術應用於高介電常數

閘極介電層薄膜電晶體之研究

Study on the Electrical Properties of

Fluorine-Incorporated Poly-Si TFTs with

High-

κ Pr

2O

3Gate Dielectric

研 究 生:張宏仁 Student:Hong-Ren Chang

指導教授:羅正忠 博士 Advisor:Dr. Jen-Chung Lou

邱碧秀 博士 Dr. Bi-Shiou Chiou

國 立 交 通 大 學

電子工程學系 電子研究所碩士班

碩 士 論 文

A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical and Computer Engineering

National Chiao Tung University in Partial Fulfillment of the Requirements

For the Degree of Master of Science in

Electronics Engineering June 2007

Hsinchu, Taiwan, Republic of China

利用氟摻雜前處理技術應用於高介電常數

閘極介電層薄膜電晶體之研究

學生:張宏仁 指導教授:羅正忠 博士

邱碧秀 博士

國立交通大學

電子工程學系 電子研究所碩士班

摘要

在本論文中,首先,我們在成長複晶矽薄膜電晶體通道之後,運用氟離子佈 值在複晶矽通道上,再整合氮化鈦金屬閘極與高介電常數材料三氧化二鐠,以形 成低溫複晶矽薄膜電晶體(poly-Si TFTs)。使用三氧化二鐠可達到比目前常見的高 介電常數材料還要高的介電常數,且其還有較低的閘極漏電流和卓越的熱穩定 性。利用氮化鈦金屬閘極取代傳統複晶矽閘極可降低閘極片電阻。此外,氟離子 佈值會鈍化捕陷狀態與消除應力鍵結去產生較強的氟鍵結,進而改善元件的特 性。與未離子佈值的複晶矽薄膜電晶體比較之下,適量的離子佈值過後的複晶矽 薄膜電晶體可提高導通電流,降低閘極漏電流,與改善可靠度。 另外,取代氟離子佈值,我們導入新穎的技術。即,在成長複晶矽薄膜電晶 體通道之後,使用電漿增強化學蒸鍍系統(PECVD)在通道表面上打四氟化碳電漿 (CF4 plasma),再結合氮化鈦金屬閘極與三氧化二鐠,形成低溫複晶矽薄膜電晶 體(poly-Si TFTs)。同理,與未打四氟化碳電漿的傳統複晶矽薄膜電晶體做比較, 有打四氟化碳電漿的複晶矽薄膜電晶體擁有較高的導通電流,較低的閘極漏電流的提升等等。然而過強的四氟化碳電漿會造成電漿傷害,進而造成元件劣化。 最後,我們分別對電漿處理與氟離子佈值過後的複晶矽薄膜電晶體進行熱載 子應力測試之研究。實驗結果顯示,有經過電漿處理與氟離子佈值過後的複晶矽 薄膜電晶體,其可靠度有明顯改善,這是由於氟會取代在複晶矽通道之中和矽與 二氧化矽的界面處,較弱的矽氫鍵結,去形成較強的矽氟鍵結,進而提高對應力 的免疫力。

Study on the Electrical Properties of

Fluorine-Incorporated Poly-Si TFTs with High-

κ

Pr

2O

3Gate Dielectric

Student:Hong-Ren Chang Advisor:Dr. Jen-Chung Lou

Dr. Bi-Shiou Chiou

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

ABSTRACT

In this thesis, first, after being deposited the poly-Si channel of the thin-film

transistors, we use fluorine ion implantation on the poly-Si channel incorporated with TiN metal gate and high-κ praseodymium oxide (Pr2O3) material to obtain low

temperature poly-silicon TFTs. The dielectric constant value of high-κ Pr2O3 material

is higher than the common high-κ materials and the poly-Si TFT with Pr2O3 gate

dielectric exhibits lower gate leakage current and perform the superior thermal stability. Instead of conventional poly-silicon gate electrode, TiN metal gate can decrease the gate sheet resistance. In addition, fluorine ion implantation can passivate the trap state and relax the strain bonds to form stronger fluorine bonds, and then improve the performance of thin-film transistors. Comparing with no ion-implanted poly-Si TFTs, the poly-Si TFTs with appropriate dosage of ion implantation can raise the driving current, decrease the gate leakage current, and improve the reliability.

introduced and the processing fabrication is as follows, after being deposited poly-Si channel, utilizing CF4 plasma treatment on the poly-Si surface of the channel in the

plasma-enhanced chemical vapor deposition (PECVE) and incorporating with TiN metal gate electrode and Pr2O3 gate dielectric obtain the low temperature poly-silicon

thin film transistors. The mechanism for the improvement of performance is the same as fluorine ion implantation, and the poly-Si TFTs with CF4 plasma treatment own the

higher driving current, lower gate leakage current and gate-induced-leakage current (GIDL), improve the subthreshold swing, and raise the reliability compared to the poly-Si TFTs without CF4 plasma treatment. However, the excess RF power of CF4

plasma treatment would cause plasma damage, and then create the degradation of device.

Finally, we examine the treated poly-Si TFTs on the hot-carrier stress test. Experimental results have shown that the poly-Si TFTs with CF4 plasma and fluorine

ion-implanted treatment would improve the reliability. This is due to fluorine pile-up in the interface between poly-Si channel and gate dielectric, and it can be in place of the weak Si-H bonds to form a strong Si-F bond. Thereby, it can raise the immunity against the hot carrier stress.

誌謝

首先要向我的指導教授羅正忠博士與邱碧秀博士致上無限的謝意。感謝老師 在知識上的啟發與生活上的關心,讓我在兩年的碩士生活,不僅僅學到作為一個 研究生應有的學習態度與精神,在做人處事方面,也有更深層的感受。 這兩年的碩士生活,發生了很多大大小小的事情,有好的,有壞的,有令人 心痛的,也有令人煩悶的。一切的一切,都因為有你們大家,不管是照應也好, 歡樂也好,幫助也好,都是這麼的讓人感動,謝謝你們大家。在這裡,首先要感 謝的是上屆畢業的學長,國源學長、伯翰學長、文煜學長、佳寧學長,帶領我走 進電子的領域,教導我實驗上應該注意的細節。接下來,要特別感謝雷老師實驗 室的家文學長,幫助我完成實驗以及論文,同時也帶給我很多知識上重要的觀 念。此外,由於柏村博士的加入,使實驗室更加團結,更加有規模,更加溫馨。 永裕博士帶給我實驗上寶貴的意見以及生活上的關心。也感謝世璋學長,以及雷 老師實驗室的伯儀學長、志揚學長、俊嘉學長,另外,鄧天王,孟翰學長、祝哥, 非常感謝你們的幫助。感謝同窗好友,正凱、大峰、信智、德安、建宏、智仁, 以及俐婷、睿龍、勝凱、彭彭與雷老師實驗室的貓貓、久騰、哲綸、廷圍和文偉。 與你們相處的時光,真的好快樂。最後,要感謝實驗室的學弟們,信富、佳樺, 國洲,元愷,嘉宏、晨修、岳展。 最後要感謝我最親愛的家人,感謝我的父母張金城先生,林鑾嬌女士,總是 一直關心我,一直在為我打氣加油,讓我不用顧慮的在外地求學。也很感謝我可 愛的女友慧雅,不斷的關心與體貼,讓我甩開煩悶或生活上的低潮。 謝謝你們大家,僅此論文獻給所有我身邊的人。Contents

Abstract (Chinese)

………..………IAbstract (English)

………...……….IIIAcknowledgements

………..……….VContents

………...……….VIFigure Captions

...IXTable Lists

...XIIChapter 1 Introduction

….….………..……….………11.1 Brief Overview of Poly-Si Thin-Film Transistors …….………….…..1

1.2 The Techniques of Performance Improvements ………..2

1.3 Incorporating High-κ Gate Dielectric ………..………3

1.4 Motivation ………...……3

1.5 Method of Device Parameter Extraction ………..…….…...5

1.5.1 Determination of Threshold Voltage ……….5

1.5.2 Determination of Subthreshold Swing ………..6

1.5.3 Determination of Field Effect Mobility …....……....……….6

1.5.4 Determination of ON/OFF Current Ratio ………..…...7

1.5.5 Extraction of Grain Boundary Trap State Density ………....8

1.5.6 Extraction of interface State Density ………....…9

1.5.7 Extraction of Active Energy ………….………...10

1.6 Organization of the Thesis ………...10

References ………..12

Gate Dielectric

………...192.1 Introduction ……….….………19

2.2 Experimental ……….21

2.3 Result and Discussion ………...23

2.4 Summary ………..……….26

Reference ………27

Chapter 3 Fluorine-Ion Implanted Poly-Si TFTs with High-

κ Pr

2O

3Gate Dielectric

...413.1 Introduction ……….……….41

3.2 Experimental ………....42

3.3 Result and Discussion ………..43

3.4 Summary ……….………..49

Reference ……….………...50

Chapter 4 Poly-Si TFTs with High-

κ Pr

2O

3Gate Dielectric under

CF

4Plasma Treatment

………....674.1 Introduction ……….……….67

4.2 Experimental ………..………...68

4.3 Result and Discussion ………..….………69

4.4 Summary ………..………….74

Reference ………75

Chapter 5 Conclusions and Future Works of the Thesis

..…………...905.2 Future Works ………...….91

5.2.1 Integrate Various Device Structures in Pr2O3 TFT …...……...91

Figure Captions

Chapter 2

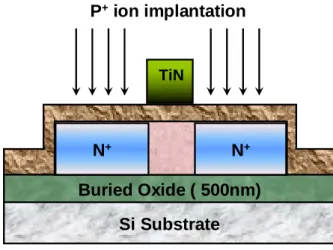

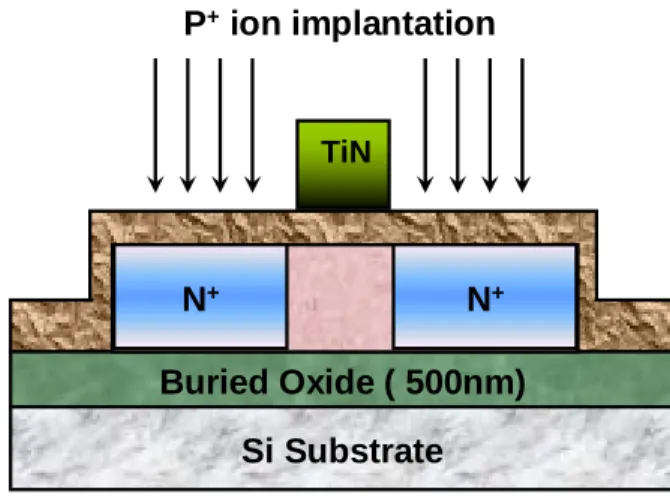

Fig. 2.1 Schematic diagram of the combined TiN gate and Pr2O3 gate dielectric

TFT.

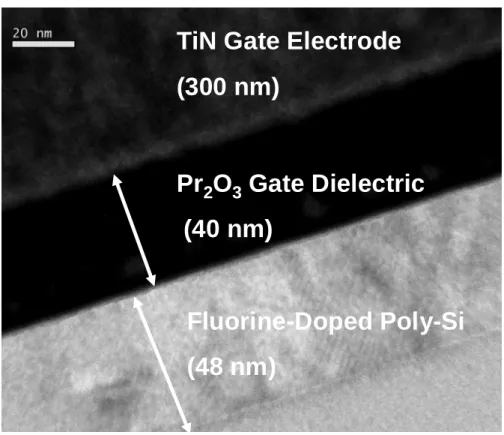

Fig. 2.2 TEM image of the proposed gate stack structure.

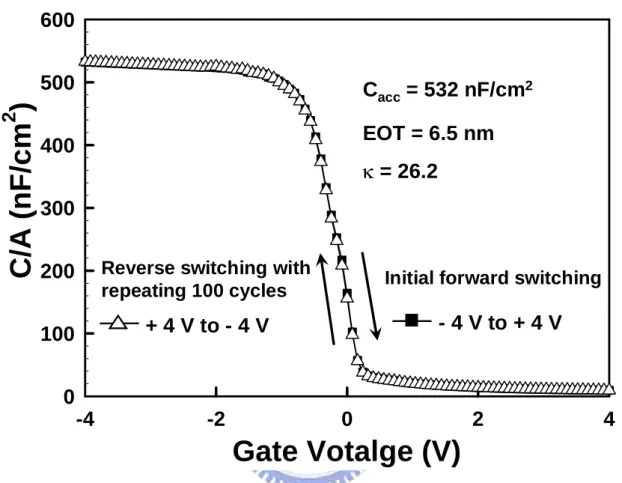

Fig. 2.3 Typical C–V characteristics of the Pr2O3 gate dielectric demonstrating

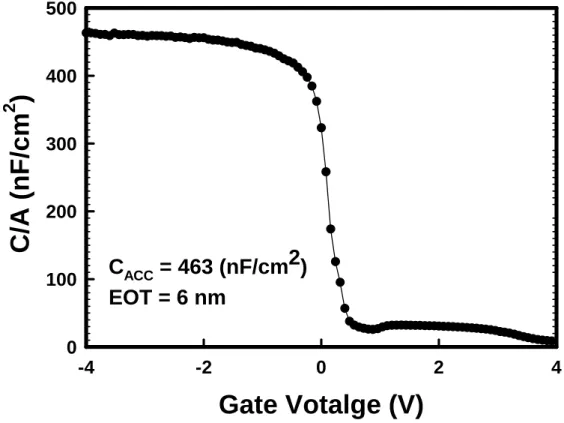

the negligible hysteresis characteristics after repeating 100 forward and reverse cycles.

Fig. 2.4 J-E characteristic of the capacitors with Pr2O3 gate dielectric.

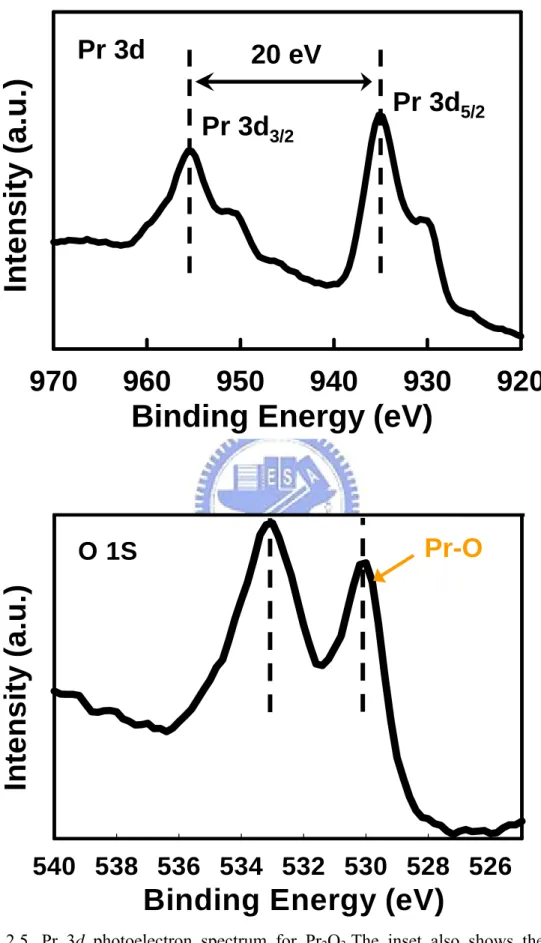

Fig. 2.5 Pr 3d photoelectron spectrum for Pr2O3.The inset also shows the O 1s

photoelectron Spectrum which clearly indicates the presence of Pr2O3.

Fig. 2.6 Typical transfer characteristics (IDS-VGS) and (b) mobilityof the

proposed TiN metal gate and high-κ Pr2O3 gate dielectric poly-Si TFT.

(W/L=2µm/2µm).

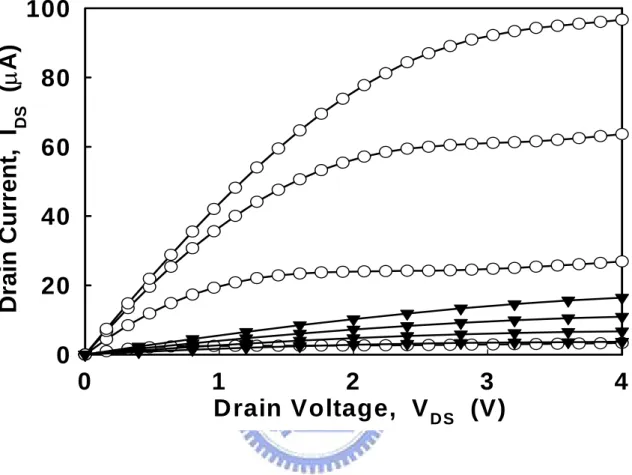

Fig. 2.7 Typical output characteristics (IDS-VDS) of the proposed TiN metal gate

and high-κ Pr2O3 gate dielectric poly-Si TFT. (W/L=2µm/2µm).

Fig. 2.8 Threshold-voltage rolloff of poly-Si TFTs with Pr2O3 and TEOS at

VDS=0.1V.

Chapter 3

Fig. 3.1 Fabrication process of the combined TiN gate and Pr2O3 gate dielectric

TFT with Fluorine ion implantation.

Fig. 3.2 Corss-section TEM image of the proposed high-κ Pr2O3 gate dielectric

TFT structure.

Fig. 3.3 C-V measurement of Pr2O3 capacitor.

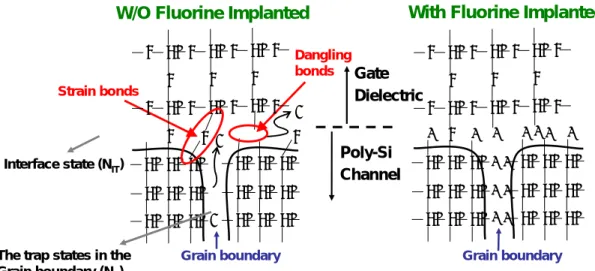

Fig. 3.4 Schematic cross-sectional view of SiO2/poly-Si interface (a) without

Fluorine implanted and (b) with Fluorine implanted treatment.

Fig. 3.5 Comparison of ID−VG characteristics for control TFTs and Fluorine

Fig. 3.6 Field-effect mobility of the control and fluorinated SPC poly-Si TFTs

with VDS=0.1.

Fig. 3.7 Comparison of ID−VD characteristics for control TFTs and Fluorine

implanted treated TFTs (W/L=10µm/5µm).

Fig. 3.8 (a) Differential (IDS,VDS) versus Drain voltage (b) Kink-point of the

control and fluorinated SPC poly-Si TFTs extracted from Fig. 3.9.

Fig. 3.9 ln[ID/(VGS-VFB)] versus 1/(VGS-VFB)2 curves at VDS=0.1V and high VGS

for control and fluorinated SPC poly-Si TFTs.

Fig. 3.10 Activation energy versus gate voltage of the control and fluorinated

SPC poly-Si TFTs

Fig. 3.11 Threshold voltage variation versus stress time for the control and

Fluorine implanted treated TFTs.

Chapter 4

Fig. 4.1 Schematic diagram of the combined TiN gate and Pr2O3 gate dielectric

TFT with CF4 plasma treatment.

Fig. 4.2 Cross-section TEM image of the proposed high-κ Pr2O3 gate dielectric

TFT structure.

Fig. 4.3 C-V measurement of Pr2O3 dielectric capacitor.

Fig. 4.4 FTIR spectra of the conventional and the CF4 plasma-treated high-κ

gate dielectric poly-Si films.

Fig. 4.5 Comparison of IDS−VGS characteristics and mobility for control TFTs

and CF4 plasma treated TFTs (W/L=10µm/5µm).

Fig. 4.6 Comparison of ID−VD characteristics for control TFTs and CF4 plasma

treated TFTs (W/L=1µm/1µm).

Fig. 4.7 (a) Differential (IDS,VDS) versus Drain voltage (b) Kink-point of the

control and fluorinated SPC poly-Si TFTs extracted from Fig. 4.7.

Fig. 4.8 ln[ID/(VGS-VFB)] versus 1/(VGS-VFB)2 curves at VDS=0.1V and high VGS

for control and fluorinated SPC poly-Si TFTs.

Fig. 4.9 Comparison of IDS−VGS characteristics for control TFTs and CF4

(W/L=1µm/1µm).

Fig. 4.10 Activation energy versus gate voltage of the control and fluorinated

SPC poly-Si TFTs.

Fig. 4.11 Threshold voltage variation versus stress time for the control and CF4

plasma treated TFTs.

Fig. 4.12 On-current degradation versus stress time for the control and CF4

Table Lists

Chapter 2

Table 2.1 Comparison of device characteristics of the HfO2, LaAlO3, TEOS and

Pr2O3 gate dielectric SPC poly-Si TFTs.

Table 2.2 Improvement of device characteristics of theTEOS and Pr2O3 gate

dielectric SPC poly-Si TFTs.

Chapter 3

Table 3.1 Key device characteristics of the CF4 plasma treated TFTs and control

TFTs.

Chapter 4

Table 4.1 (a) Key device characteristics of the CF4 plasma treated TFTs with 10W

and control TFTs (W/L=10µm/5µm) (b) Comparison of 10W, 20W and control sample. (W/L=1µm/1µm)

Chapter 1

Introduction

1.1 Brief Overview of Poly-Si Thin-Film Transistors

A thin-film transistor (TFT) is that a field-effect transistor is deposited on insulating substrate, and it utilizes a semiconductor thin film as its channel. For the channel using Silicon thin films, they are divided into amorphous silicon (α-Si) TFTs and polycrystalline silicon (poly-Si) TFTs.

Amorphous silicon (α-Si) TFTs have some issues. For example, their mobility are extremely low because the low temperature process results in mobile leaking from source to gate or scatters at the interface, and the grain boundaries cause mobile scattering during transport. In recent years poly-Si TFTs are considered that they are better candidates than α-Si TFTs due to their higher mobility (ranging from 10 to 300cm2/V-s) [1]. Therefore, polycrystalline silicon (poly-Si) thin film transistors (TFTs) have been widely used in a active-matrix liquid crystal displays (AMLCDs)[2]. The major application of poly-Si TFTs in AMLCDs lies in integrating the peripheral driving ICs, and the pixel switching elements on the glass substrate to realize system-on-panel (SOP) purpose[3]. Pixel TFTs need to operate at high voltages with low gate-leakage currents to drive the liquid crystal. In contrast, high-speed display circuits require that TFTs operate at low voltages and high driving currents with a low threshold voltage (Vth).

degradation of electrical performance. In the ON state, the grain boundary traps capture carriers and form potential barriers, resulting in reduction of the carrier mobility. The effect will increase the threshold voltage and degrade the ON current as compared with single-crystalline Si MOSFET. In the OFF state, the grain boundary traps assist the carrier in generating in the depletion layer, and increase the leakage current. Therefore, reduction of trap states density in poly-Si channel is essential for fabricating high performance TFTs.

1.2 The Techniques of Performance Improvements

In order to obtain desirable characteristics of polysilicon TFTs, the major techniques had been employed to improve the device performance by reducing the trap state density or increasing the grain size of the polysilicon.. There are several methods to increase the grain size through SPC (solid phase crystallization)[4], ELA (excimer laser annealing)[5-6] and MILC (metal induced lateral crystallization)[7]. Furthermore, there are also many ways to reduce the trap-state density, such as plasma treatments or ion implantation. Various plasma such as H2[8], NH3[9], N2O[10], O2[11]

and CF4 plasma[12] have been intensely investigated in recent years. Besides, ion

implantation, such as F+[13], N+[14], are incorporated into TFT poly-Si channel to terminate the poly-Si defects and then improve the performance.

Moreover, novel structure design is another approach to fabricate high-performance poly-Si TFTs. These techniques focus on reduction of the electrical field near the drain junction, and thus suppress the device's Off-state leakage current. Many structures including multiple channel structures [15], offset drain/source [16-17], lightly doped drain (LDD) [18], gate-overlapped LDD [19-21], field induced drain [22] and vertical channel [23] have been proposed and investigated intensively.

1.3 Incorporating High-

κ Gate Dielectric

Generally speaking, using a thin gate oxide can increase the driving current of TFTs. Unfortunately, for a conventional gate dielectric (i.e., SiO2 or Si3N4), a thinner

gate dielectric may induce higher gate-leakage current and degrade the TFT characteristics significantly [24]. To preserve the physical gate-dielectric thickness while increasing the gate capacitance density and then improving the mobile carrier density in the channel region, high-κ gate-dielectric materials were suggested, such as Al2O3 [25], Ta2O5 [26], HfO2 [27].

The relation between gate capacitance and dielectrics constant and equivalent oxide thickness (EOT) is shown:

ox k high ox t t C = κε0 = ε0 − ………...(Eq.1.1)

where Cox is the gate capacitance/unit area, ε0 is the permittivity of free space, κ is

the relative permittivity of high-κ, tox is the oxide thickness, thigh-κ is the high-κ

dielectric thickness.

Using the high-κ materials replace conventional oxide gate dielectric, attempts have been made to maintain these material amorphous even after post-deposition high temperature processing, in order to avoid surface roughness and grain boundary induced leakage current. In this thesis, we choose the excellent alternative which is the praseodymium oxide films[28].

1.4 Motivation

We choose the high-κ Pr2O3 material as the gate dielectric due to the high gate

channel region which is discussed in Chapter 2.

The trap states which are in the poly-Si TFT's channel and on the Si/poly-Si interface can trap carriers to form potential barriers, and thuss affect the current transport [29]. Moreover, the Off-current in poly-Si TFTs is associated with the amount of trap states in the drain depletion region. It can be attributed to thermionic emission at a low electric field and the field-enhanced emission (i.e. F-P emission or trap-assisted band-to-band tunneling) at a high electric field [30]. Hence trap states can lead to a poor device performance, such as low field-effect mobility, large leakage current, bad subthreshold slope and high threshold voltage.

Plasma treatments are believed to be the most effective methods to reduce trap states in the poly-Si. Many kinds of plasma such as H2/N2 mixture plasma [31],

nitrogen implantation with H2 plasma [32], pre-oxidation NH3 annealing with H2

plasma [33], NH3 plasma [34] and H2/O2 plasma [35] have been proposed. Generally,

hydrogen-based plasma is mostly adopted, because the hydrogen atoms can easily restore the trap states at the poly-Si/SiO2 interface and in the grain boundaries.

However, it is known that hydrogenated poly-Si TFTs have a troublesome issue in the device reliability [36-37]. The device performance degrades seriously under a long-term electrical stress. It is known that the poor device reliability of the hydrogenated TFTs is due to the weak Si-H and Si-Si bonds, which might be broken easily during the electrical stress and thus cause the creation of trap states in the poly-Si channel [38]. Recently, fluorination and technique has been proposed. It can improve both the device performance and also reliability, because the Si-F bonds are stronger than Si-H bonds [39-44]. So fluorine ion implantation (FII) technique is mostly adopted to introduce fluorine atoms into the poly-Si. Besides, the incorporation of nitrogen into the gate-dielectrics by different process has been widely

investigated to improve reliability [45-50]. The improved reliability is mainly due to the fact that most of the incorporated nitrogen can pile up at the gate-SiO2/Si interface

to make the interface more robust and then to improve the hot-carrier immunity. Moreover, the incorporation of nitrogen can also suppress boron penetration from the p+-polysilicon gate due to the formation of gate oxynitrides. In Chapter 3, we investigate the improvement by fluorine implantation incorporated Pr2O3 high-κ gate

dielectric and TiN metal gate.

However, the method of ion implantation may be not suitable for large-area electronics. Moreover, a subsequent high temperature process, required to activate implanted atoms and recover the damage created by implantation, is an issue for the current AMCLD fabrication process. Therefore, effective and process-compatible techniques introduce fluorine atoms into the poly-Si channel are needed to be developed. In Chapter 4, an effective and process-compatible fluorine incorporated technique is proposed by fluorine-based plasma treatment. We have successfully combined TiN gate, Pr2O3 high-κ gate dielectric, and CF4 plasma to fabricate

high-performance poly-Si TFTs.

1.5 Method of Device Parameter Extraction

In this thesis, we use HP 4156B-Precision Semiconductor Parameter Analyzer to measure the electrical characteristics of proposed poly-Si TFTs. Furthermore, we utilize FIB and TEM to see the cross-section view. The methods that we extract the characteristic parameters of poly-Si TFTs are described in this section.

length-width and series resistance measurements. However, VTH is not uniquely

defined. Various definitions have been proposed and the reason can be found in IDS-VGS curves. In this thesis, we use a simple method to determinate the Vth called

constant drain current method. The voltage at a specified threshold drain current is taken as the Vth. This method is adopted in the most studied papers of poly-Si TFTs. It canbe given a threshold voltage close to that obtained by the complex linear extrapolation method. Typically, the threshold current is specified at ID=(W/L)×100nA for VDS=0.1V and IDS=(W/L)×100nA for VDS=5V, where W and L

is channel width and channel length, respectively.

1.5.2 Determination of Subthreshold Swing

Subthreshold swing (S.S) is a typical parameter to describe the control ability of gate toward channel, which reflects the turn on/off speed of a device. It is defined as the amount of gate voltage required to increase/decrease drain current by one order of magnitude.

The S.S. should be independent of drain voltage and gate voltage. However, in reality, the S.S. increase with drain voltage due to channel shortening effect such as charge sharing , avalanche multiplication and punch through effect. The subthreshold swing is also related to gate voltage due to undesirable and inevitable factors such as the serial resistance and interface states.

In this thesis, the S.S is defined as one-third of gate voltage required to decrease the threshold current by two order of magnitude. The threshold current is specified to be the drain current when the gate voltage is equal to threshold voltage.

The field-effect mobility is usually extracted from the maximum value of transconductance (Gm) at low drain bias (VD=0.1V). The drain current in the linear

region (VDS < VGS-VTH) is expressed as the following equation

(

)

⎥⎦⎤ ⎢⎣ ⎡ − − = 2 2 1 ) ( G th D DS ox eff DS V V V V L W C I µ ..………..(Eq.1.2)The transconductance Gm is gived by

D ox FE G DS m V L W C V I g ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = ∂ ∂ = µ ..………..(Eq.1.3)

Therefore, the field-effect mobility is

( ) DS m DS ox eff

g

V

V

WC

L

max=

µ

………..(Eq.1.4)1.5.4 Determination of ON/OFF Current Ratio

On/off current ratio is one of the most important parameters of poly-Si TFTs since a high-performance device exhibits not only a large on-current but also a small off-current (leakage current). The leakage current mechanism in poly-Si TFTs is not like that in MOSFET. In MOSFET, the channel is composed of single crystalline Si and the leakage current is due to the tunneling of minority carrier from drain region to accumulation layer located in channel region. However, in poly-Si TFTs, the channel is composed of poly-Si. A large amount of trap state densities in grain structure attribute a lot of defect states in energy band gap to enhance the tunneling effect. Therefore, the leakage current is much larger in poly-Si TFTs than in MOSFET. When the voltage drops between gate voltage and drain voltage increases, the band gap width decreases and the tunneling effect becomes much more severe. Normally we can find this effect in typical poly-Si TFTs’ IDS-VGS characteristics where the

There are a lot of ways to specify the on and off-current. In this thesis, take n-channel poly-Si TFTs for examples, the on-current is defined as the drain current when gate voltage at the maximum value and drain voltage is 1V. The off-current is specified as the minimum current when drain voltage equals to 1V.

V V at Plot V I of Current Minimum V V at Plot V I of Current Maximum I I DS GS DS DS GS DS OFF ON 1 1 = − = − = ………….(Eq.1.5)

1.5.5 Extraction of Grain Boundary Trap State Density

The Trap State Density (Nt), which can be determined by the theory established

by Levinson et al. [51], which is based on Seto’s theory [52]. For poly-Si TFTs, the drain current IDS can be given as following:

⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = GS ox Si c t GS DS ox FE DS V kTC L N q V V L W C I

ε

µ

8 exp 2 3 ………(Eq.1.6) Where,µFE : field-effect mobility of carriers

q : electron charge k : Boltzmann’s constant

εSi : dielectric constant of silicon

T : temperature

Nt : trap-state density per unit area

Lc : channel thickness

This expression, first developed by Levinson et al., is a standard MOSFET’s equation with an activated mobility, which depends on the grain-boundary barrier height. Levinson et al. assumed that the channel thickness was constant and equal to the thickness of the poly-Si film (t). This simplifying assumption is permissible only

for very thin film (t < 10nm). The trap-state density can be obtained by extracting a straight line on the plot of ln(IDS/VGS) versus 1/VGS at low drain voltage and high gate

voltage.

Proano et al. [53] thought that a barrier approximation is to calculate the gate induced carrier channel thickness by solving Poisson’s equation for an undoped material and to define the channel thickness (Lc) as a thickness in which 80% of the

total charges were induced by the gate. Doing so, one obtains

(

GS fb)

SiO Si ox c V V q kTt L − = 2 8ε

ε

……….(Eq.1.7)which varies inversely with (VGS−Vfb). This predicts, by substituting Eq.1.7 into

Eq.1.6, that ln[IDS/(VGS−Vfb)] versus 1/(VGS−Vfb)2. We use the gate voltage at which

minimum leakage current occurs as flat-band voltage (Vfb). Effective trap-state

density (Nt) can be determined from the square root of the slope.

| | slope q

C

Nt = ox ………...(Eq.1.8)

1.5.6 Extraction of interface State Density

The effective interface trap states densities near (NT) the SiO2/Poly-Si

interface were calculated from S.S. By neglecting the depletion capacitance in the active layer, the Nt can be expressed as [54]:

) )( 1 10 ln . ( q C KT q S S NT = − ox ………(Eq.1.9)

Where the Cox is the capacitance of the gate oxide and the S.S is subthreshold swing. The Nt value reflect both interface states and grain boundary trap states near the SiO2/poly-Si interface.

1.5.7 Extraction of Active Energy

First, we measure the drain current versus the gate voltage for temperatures varying from 25 to 105℃. Then, we draw a plot of nature logarithm of drain current versus 1/KT at a fixed gate voltage and extract the absolute value of slope, i.e. the active energy EA. In this case, the thermal dependence of drain current is given by:

⎟ ⎠ ⎞ ⎜ ⎝ ⎛ − ∝ kT E I A DS exp ………...(Eq.1.10) Thus, we can plot the variations of EA versus the gate voltage, for the whole

gate-voltage range [55].

1.6 Organization of the Thesis

This thesis is organized as follow:

In Chapter 1, the overview of poly-Si TFTs, the method of device parameter extraction, the reason for high-κ extraction and motivations of this thesis are described.

In Chapter 2, we discuss the advantage of Pr2O3 high-κ material and TiN

metal gate. Furthermore, Pr2O3 high-κ gate dielectric perform significant

improvements in the device performance, such as lower threshold voltage, improved subthreshold swing, enhanced field effect mobility, and higher ON/OFF current ratio can be achieved as compared to the TEOS TFT even without other hydrogenation treatment.

In Chapter 3, the fabrication process of poly-Si TFTs combined with Pr2O3

gate dielectric, TiN gate and fluorine ion implantation will be proposed. Then, we research into the improvement degree of electrical characteristic and reliability.

solid-phase-crystallized (SPC) poly-Si TFTs with CF4 plasma treatment combined

with Pr2O3 gate dielectric and TiN gate will be proposed. Also we explore its

performance and reliability.

Reference

[1] S. Zhang, C. Zhu, J. Sin, J. Li and P. Mok, "Ultra-thin elevated channel poly-Si TFT technology for fully-integrated AMLCD system on glass," Electron Devices, IEEE Transactions on, vol. 47, pp. 569-575, 2000.

[2] T. Nishibe, “Low-temperature poly-Si TFTs by excimer laser annealing,” in Proc. Mater. Res. Soc. Symp., 2001, vol. 685E, pp. D6.1.1–D6.1.5.

[3] B.-D. Choi, H.-S. Jang, O.-K. Kwon, H.-G. Kim, and M.-J. Soh, “Design of poly-Si TFT-LCD panel with integrated driver circuits for an HDTV/XGA projection system,” IEEE Trans. Consum. Electron., vol. 21, no. 3, pp. 100–103, Mar. 2000. [4] Nakamura, F. Emoto, E. Fujii, A. Yamamoto, Y. Uemoto, H. Hayashi, Y. Kato and K.

Senda, "A high-reliability, low-operation-voltage monolithic active-matrix LCD by using advanced solid-phase-growth technique," Electron Devices Meeting, 1990.Technical Digest., International, pp. 847-850, 1990.

[5] G. Giust, T. Sigmon, J. Boyce and J. Ho, "High-performance laser-processed polysilicon thin-film transistors," Electron Device Letters, IEEE, vol. 20, pp. 77-79, 1999.

[6] N. Kusumoto, T. Inushima and S. Yamazaki, "Characterization of polycrystalline-Si thin film transistors fabricated by excimer laser annealing method," IEEE Trans. Electron Devices, vol. 39, pp. 1876–1879, 1994.

[7] S. W. Lee, T. H. Ihn, S. K. Joo, S. Co and K. Do, "Fabrication of high-mobility p-channel poly-Si thin film transistors by self-aligned metal-induced lateral crystallization," Electron Device Letters, IEEE, vol. 17, pp. 407-409, 1996.

[8] A. Yin and S. Fonash, "High-performance p-channel poly-Si TFTs using electron cyclotronresonance hydrogen plasma passivation," Electron Device Letters, IEEE, vol. 15, pp. 502-503, 1994.

[9] C. K. Yang, T. F. Lei and C. L. Lee, "The combined effects of low pressure NH 3-annealing and H 2 plasma hydrogenation on polysilicon thin-film transistors," Electron Device Letters, IEEE, vol. 15, pp. 389-390, 1994.

[10] J. W. Lee, N. I. Lee, J. I. Kan and C. H. Han, "Characteristics of polysilicon thin-film transistor with thin-gate dielectric grown by electron cyclotron resonance nitrous oxide plasma," Electron Device Letters, IEEE, vol. 18, pp. 172-174, 1997. [11] K. C. Moon, J. H. Lee and M. K. Han, "Improvement of polycrystalline silicon thin

film transistor using oxygen plasma pretreatment before laser crystallization," Electron Devices, IEEE Transactions on, vol. 49, pp. 1319-1322, 2002.

[12] C. S. Lai, W. C. Wu, K. M. Fan, and T. S. Chao , “Effects of Post CF4 Plasma

Treatment on the HfO2 Thin Film”, Jpn. J. Appl. Phys. Part1, 2005, Vol. 44, No. 4B, 2307-2310.

[13] H. N. Chern, C. L. Lee and T. F. Lei, "The effects of fluorine passivation on polysilicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 41, pp. 698-702, 1994.

[14] C. K. Yang, T. F. Lei and C. L. Lee, "Characteristics of top-gate thin-film transistors fabricated on nitrogen-implanted polysilicon films," Electron Devices, IEEE Transactions on, vol. 42, pp. 2163-2169, 1995.

[15] T. Unagami and O. Kogure, "Large on/off current ratio and low leakage current poly-Si TFTs with multi-channel structure," Electron Devices, IEEE Transactions on, vol. 35, pp. 1986-1989, 1988.

[16] B. H. Min, C. M. Park and M. K. Han, "A novel offset gated polysilicon thin film transistor without an additional offset mask," Electron Device Letters, IEEE, vol. 16, pp. 161-163, 1995.

polysilicon TFTs," IEEE Trans. Electron Devices, vol. 51, pp. 1304-1308, 2004. [18] P. S. Shih, C. Y. Chang, T. C. Chang, T. Y. Huang, D. Z. Peng and C. F. Yeh, "A

novel lightly doped drain polysilicon thin-film transistor withoxide sidewall spacer formed by one-step selective liquid phase deposition," Electron Device Letters, IEEE, vol. 20, pp. 421-423, 1999.

[19] K. Y. Choi and M. K. Han, "A novel gate-overlapped LDD poly-Si thin-film transistor," Electron Device Letters, IEEE, vol. 17, pp. 566-568, 1996.

[20] A. Bonfiglietti, M. Cuscuna, A. Valletta, L. Mariucci, A. Pecora, G. Fortunato, S. Brotherton and J. Ayres, "Analysis of electrical characteristics of gate overlapped lightly doped drain (GOLDD) polysilicon thin-film transistors with different LDD doping concentration," Electron Devices, IEEE Transactions on, vol. 50, pp. 2425-2433, 2003.

[21] Y. Mishima and Y. Ebiko, "Improved lifetime of poly-Si TFTs with a self-aligned gate-overlapped LDD structure," Electron Devices, IEEE Transactions on, vol. 49, pp. 981-985, 2002.

[22] H. C. Lin, C. M. Yu, C. Y. Lin, K. L. Yeh, T. Y. Huang and T. F. Lei, "A novel thin-film transistor with self-aligned field induced drain," Electron Device Letters, IEEE, vol. 22, pp. 26-28, 2001.

[23] C. S. Lai, C. L. Lee, T. F. Lei and H. N. Chern, "A novel vertical bottom-gate polysilicon thin film transistor with self-aligned offset," Electron Device Letters, IEEE, vol. 17, pp. 199-201, 1996.

[24] A. Takami, A. Ishida, J. Tsutsumi, T. Nishibe and N. Ibaraki, "Threshold voltage shift under the gate bias stress in low-temperature poly-silicon TFT with the thin gate oxide film," Proc.Int.Workshop AM-LCD, pp. 45–48,

transistors using Al2O3 gate insulators," Electron Device Letters, IEEE, vol. 19, pp.

502-504, 1998.

[26] M. Y. Um, S. K. Lee and H. J. Kim, "Characterization of Thin Film Transistor using Ta 2 O 5 Gate Dielectric," Proc.Int.Workshop AM-LCD, pp. 45–46,

[27] Chia-Pin Lin, Bing-Yue Tsui, Ming-Jui Yang, Ruei-Hao Huang, and Chao-Hsin Chien,” High performance poly-silicon thin film transistors using HfO2 gate dielectrics” Electron Device Letters, IEEE, vol. 27, 2006.

[28] H. Osten, J. Liu, P. Gaworzewski, E. Bugiel, P. Zaumseil and F. IHP, "High-κ gate dielectrics with ultra-low leakage current based on praseodymium oxide," Electron Devices Meeting, 2000.IEDM Technical Digest.International, pp. 653-656, 2000. [29] G. Y. Yang, S. H. Hur and C. H. Han, "A physical-based analytical turn-on model of

polysilicon thin-film transistors for circuit simulation," Electron Devices, IEEE Transactions on, vol. 46, pp. 165-172, 1999.

[30] K. Olasupo and M. Hatalis, "Leakage current mechanism in sub-micron polysilicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 43, pp. 1218-1223, 1996.

[31] M. J. Tsai, F. S. Wang, K. L. Cheng, S. Y. Wang, M. S. Feng and H. C. Cheng, "Characterization of H2/N2 plasma passivation process for poly-Si thin film transistors (TFTs)," Solid State Electronics, vol. 38, pp. 1233-1238, 1995.

[32] C. K. Yang, T. F. Lei and C. L. Lee, "The combined effects of low pressure NH 3-annealing and H 2 plasma hydrogenation on polysilicon thin-film transistors," Electron Device Letters, IEEE, vol. 15, pp. 389-390, 1994.

[33] C. K. Yang, T. F. Lei and C. L. Lee, "The combined effects of low pressure NH 3-annealing and H 2 plasma hydrogenation on polysilicon thin-film transistors," Electron Device Letters, IEEE, vol. 15, pp. 389-390, 1994.

[34] H. C. Cheng, F. S. Wang and C. Y. Huang, "Effects of NH 3 plasma passivation on N-channel polycrystalline silicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 44, pp. 64-68, 1997.

[35] H. N. Chern, C. L. Lee and T. F. Lei, "H 2/O 2 plasma on polysilicon thin-film transistor," Electron Device Letters, IEEE, vol. 14, pp. 115-117, 1993.

[36] C. Lin, M. Yang, C. Yeh, L. Cheng, T. Huang, H. Cheng, H. Lin, T. Chao and C. Chang, "Effects of plasma treatments, substrate types, and crystallization methods on performance and reliability of low temperature polysiliconTFTs," Electron Devices Meeting, 1999.IEDM Technical Digest.International, pp. 305-308, 1999. [37] H. Momose, T. Morimoto, Y. Ozawa, K. Yamabe and H. Iwai, "Electrical

characteristics of rapid thermal nitrided-oxide gate n and p-MOSFET's with less than 1 atom% nitrogen concentration," Electron Devices, IEEE Transactions on, vol. 41, pp. 546-552, 1994.

[38] M. Hack, A. Lewis and I. W. Wu, "Physical models for degradation effects in polysilicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 40, pp. 890-897, 1993.

[39] H. N. Chern, C. L. Lee and T. F. Lei, "The effects of fluorine passivation on polysilicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 41, pp. 698-702, 1994.

[40] S. Maegawa, T. Ipposhi, S. Maeda, H. Nishimura, T. Ichiki, M. Ashida, O. Tanina, Y. Inoue, T. Nishimura and N. Tsubouchi, "Performance and reliability improvements in poly-Si TFT's by fluorine implantation into gate poly-Si," Electron Devices, IEEE Transactions on, vol. 42, pp. 1106-1112, 1995.

[41] J. W. Park, B. T. Ahn and K. Lee, "Effects of F Implantation on the Characteristics of Poly-Si Films and Low-Temperature n-ch Poly-Si Thin-Film Transistors,"

Jpn.J.Appl.Phys, vol. 34, pp. 1436-1441, 1995.

[42] C. L. Fan and M. C. Chen, "Performance Improvement of Excimer Laser Annealed Poly-Si TFTs Using Fluorine Ion Implantation," Electrochemical and Solid-State Letters, vol. 5, pp. G75, 2002.

[43] C. H. Kim, S. H. Jung, J.S. Yoo, and M. K. Han, “ poly-Si TFT fabricated by laser-induced in-situ fluorine passivation and laser doping,” IEEE Electron Device lett.,vol. 22,pp. 396-398, Aug. 2001.

[44] C. A. Dimitriadis, P. A. Coxon, L. Dozsa, L. Papadimitriou, and N. Economou, “Performance of thin-film transistors on polysilicon films grown by low-pressure chemical vapor deposition at various pressures,” IEEE Trans. Electron Devices, vol. 39, pp. 598-606, Mar. 1992.

[45] G. Yoon, A. Joshi, J. Kim and D. L. Kwong, "MOS characteristics of NH3-nitrided

N2O-grown oxides," Electron Device Letters, IEEE, vol. 14, pp. 179-181, 1993.

[46] H. Momose, T. Morimoto, Y. Ozawa, K. Yamabe and H. Iwai, "Electrical characteristics of rapid thermal nitrided-oxide gate n and p-MOSFET's with less than 1 atom% nitrogen concentration," Electron Devices, IEEE Transactions on, vol. 41, pp. 546-552, 1994.

[47] Y. Okada, P. Tobin, P. Rushbrook and W. DeHart, "The performance and reliability of 0.4 micron MOSFET's with gate oxynitrides grown by rapid thermal processing using mixtures of N 2 O and O 2," Electron Devices, IEEE Transactions on, vol. 41, pp. 191-197, 1994.

[48] H. Hwang, W. Ting, B. Maiti, D. L. Kwong and J. Lee, "Electrical characteristics of ultrathin oxynitride gate dielectric prepared by rapid thermal oxidation of Si in NO," Appl. Phys. Lett., vol. 57, pp. 1010, 1990.

through-silicon-gate nitrogen ion implantation," Electron Device Letters, IEEE, vol. 8, pp. 58-60, 1987.

[50] T. Kuroi, T. Yamaguchi, M. Shirahata, Y. Okumura, Y. Kawasaki, M. Inuishi and N. Tsubouchi, "Novel NICE (Nitrogen Implantation into CMOS Gate Electrode and Source-Drain) Structure for High Reliability and High Performance 0.25 µm Dual gate CMOS," IEDM Tech.Dig, pp. 325–328, 1993.

[51] J. Levinson, F. Shepherd, P. Scanlon, W. Westwood, G. Este and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," J. Appl. Phys., vol. 53, pp. 1193, 1982.

[52] J. Y. W. Seto, "The electrical properties of polycrystalline silicon films," J. Appl. Phys., vol. 46, pp. 5247, 1975

[53] R. Proano, R. Misage and D. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistors," Electron Devices, IEEE Transactions on, vol. 36, pp. 1915-1922, 1989.

[54] T. Noguchi, H. Hayashi, and T. Ohshima, “Low temperature polysilicon super-thin-transistor (LSFT),” Japan. J. Appl. Phys., vol. 25,p. L121, 1986.

[55] J. Y. Steo, “The electrical properties of polycrystalline silicon films,” J.Appl. Phys., vol.46,pp.5247-5254,1975

Chapter 2

High-Performance Poly-Si TFTs with High-

κ

Pr

2O

3Gate Dielectric

2.1 Introduction

Polycrystalline silicon thin-film transistors (poly-Si TFTs) have attracted much attention in active-matrix liquid crystal displays (AMLCDs) for the sake of realizing the integration of driving circuits and pixel elements on glass substrate to accomplish the system-on-panel (SOP) purpose [1]-[3]. For approaching the low power display driving circuits, high-performance poly-Si TFT with low operation voltage, low subthreshold swing, high driving capability, and low gate leakage current are required. A traditional solid-phase crystallized (SPC) poly-Si TFT with continued gate dielectric (i.e., SiO2 or Si3N4) scaling is utilized to increase the gate capacitance

density for driving current enhancement to reach the level of display driving circuits. However, employing a thinner gate dielectric would induce higher gate leakage current and degrade the TFT performance significantly [4]. In order to address these issues, integrating metal gate on high-κ gate dielectric with poly-Si TFT is urgently required for maintaining not only a higher gate capacitance density but also a lower gate leakage current with keeping thicker physical gate dielectric thickness [5]. Besides, the trap states at poly-Si grain boundaries also could be filled up quickly to improve the subthreshold swing even without additional hydrogenation treatment [6].

LaAlO3 have been proposed to increase the gate capacitance density and reduce the

gate leakage current for better gate controllability with keeping thicker physical gate dielectric thickness [7].

We generalize a summary of the needs for the selection of appropriate materials for gate dielectric applications. First, the suitable k value is about 12~60. In general, those materials with too large k-value almost have poor thermal stability. Second, the high-κ layer must act as an insulator. Higher energy band gap with conduction band offset (△Ec >1eV) or valence band offset (△Ev >1eV) in order to

inhibit conduction by the Schottky emission of electrons or holes through the gate dielectric band. Lower energy band gap will lead to unacceptably gate leakage current. Third, the high-κ materials must not react with Si as far as possible during high temperature process. Since most high-κ materials reported that its oxygen would react with Si to form an undesirable interfacial layer in the interface and the high-κ material would react with Si to form the silicide. The formations of interfacial layer and sillicide result in lower k-value and consequently reduce the effective dielectric constant of the gate capacitor. Fourth, we must choose to use a crystalline or an amorphous structure because of the amorphous morphology has smaller leakage current than polycrystalline morphology. Fifth, the high-κ dielectric must have the excellent quality which has low density of intrinsic defect at Si/high-κ interface and in the bulk materials. For this reason, an amorphous gate dielectric could configure its interface bonding to minimize the number of interface defects. Hence, using an amorphous dielectric has many advantages over a polycrystalline dielectric.

According to the conclusion given above, we believe that the praseodymium oxide (Pr2O3) [8] is an outstanding gate dielectric because it has a high dielectric

offset larger 1eV respect to Si [11]. On the other hand, Pr2O3 exhibits lower leakage

current density below 10-8A/cm2 at Vg = ±1V than HfO2 and ZrO2 at the same

equivalent silicon oxide thickness of 1.4nm [12][13], and it can suffer annealing of up to 1000℃ for 15 seconds with no structural changes and no degradation in electrical properties [14], in other words, Pr2O3 perform the superior thermal stability against

degradation of crystalline dielectric.

CMOS devices with PVD TiN metal-gate have recently received lots of attention owing to the low resistivity of metal layers, the capability of eliminating the poly depletion effect (PDE) encountered in poly-gate counterparts and low temperature deposition process[15-17]. However, many process-related issues, such as the thermal stability and plasma damage may limit practical applications of metal-gate CMOS [18-19]. Because of the low temperature fabrication processing of poly-Si TFTs, we can reduce the degradation of TiN during high temperature process. Hence, TiN metal gate is an admirable metal gate for poly-Si TFTs.

In this paper, integration of TiN metal gate on high-κ Pr2O3 gate dielectric

with SPC poly-Si TFT is successfully demonstrated for the first time. The proposed Pr2O3 gate dielectric poly-Si TFT show outstanding electrical characteristics as

compared to tetraethoxysilane (TEOS) gate dielectric poly-Si TFT; hence, it may satisfy the needs of low power display driving circuit applications.

2.2 Experimental

For a start, in order to know the Pr2O3 k-value and its breakdown voltage, we

built a capacitor structure and using Pr2O3 as its gate dielectric. The process follows:

min in N2 ambient to improve the gate dielectric quality. In the end, a 500-nm

aluminum film was deposited and patterned as the gate electrode.

On the other hand, the device of poly-Si TFTs with conventional gate dielectric tetraethoxysilane (TEOS) and high-κ Pr2O3 gate dielectric was described as

follows. The cross section of the proposed self-aligned TiN gate and Pr2O3 gate

dielectric TFT is depicted in Figure 2.1. First, a 100-nm undoped amorphous silicon (α-Si) layer was deposited on 500-nm thermally oxidized Si wafers by dissociation of SiH4 gas in a low-pressure chemical vapor deposition (LPCVD) system at 550 oC, followed by a solid-phase crystallization (SPC) process at 600 oC for 24 h in N2

ambient for the phase transformation from amorphous to polycrystalline silicon. Individual device active region was patterned and defined. After the clean process, a 33.6-nm Pr2O3 thin film was deposited by e-gun evaporation system as gate dielectric,

followed by a furnace treatment at 600 οCfor 30 min in N2 ambient to improve the

gate dielectric quality. Then, a 200-nm TiN film was deposited and a Cl2 based

plasma etching process capable of stopping on the Pr2O3 layer was used to pattern the

gate electrode. Next, a self-aligned phosphorous ion implantation was performed at the dosage and energy of 5 x 1015 cm-2 and 90 keV, respectively. The dopant activation was performed at 600℃ furnace annealing at nitrogen ambient for 30 min, followed by deposition of the 300-nm passivation layer in PECVD chamber at 300 οC. Next, a two-step wet-etching process is used to open the contact holes. The passivation SiO2 and Pr2O3 film were etched away by buffered oxide etch (BOE) and

H2SO4/H2O2 solution separately. Finally, a 400-nm aluminum film was deposited and

patterned as the metal pad and sintered at 400o

C for 30min. For comparison, poly-Si TFTs with a 35-nm tetraethoxysilane (TEOS) as gate dielectric deposited by PECVD was prepared with the same process flow. Note that no hydrogenation treatment was

performed after the Al formation.

2.3 Result and Discussion

The cross-sectional transmission electron microscopy (TEM) image of the proposed TiN gate and Pr2O3 gate dielectric TFT structure is depicted in Figure 2.2,

which shows a physical thickness of Pr2O3 film around 33.6-nm and the interfacial

SiO2 –like layer is about 1.5-nm [20].

A high gate capacitance density of 532 nF/cm2 is obtained from capacitance-voltage (C-V) measurement of the capacitor structure, as shown in Figure 2.3. Moreover, forward sweeping (-4V to 4V) and reverse sweeping (4V to -4V) on Vg with repeating 100 cycles display the negligible C-V hysteresis characteristics for

Pr2O3 gate dielectric. Such low charge-trapping phenomenon reveals an excellent gate

dielectric property of Pr2O3 thin film [21][22]. From the TEM image and the C-V

measurement, the equivalent-oxide thickness (EOT) and the effective dielectric constant (εr) of Pr2O3 gate dielectric are 6.5 nm and 26.2, respectively.

Figure 2.4 shows the J-E characteristic of the capacitor structure with Pr2O3

gate dielectric, and the J-E curves can be calculated from I-V curves, where J=I/(area of the capacitors) and E=V/(physical thickness of the high-κ gate dielectric). As can be seen, the Pr2O3 high-κ gate dielectric performs a high breakdown field (~7MV/cm)

and a low leakage current (~5.9224×10-8A/cm2 at VG=1V). The breakdown filed of

Pr2O3 is slightly smaller than TEOS (~10MV/cm). Therefore, this is high enough to

drive a liquid crystal display.

To confirm the chemical composition of Pr2O3 gate dielectric on poly-Si

Pr2O3 are in good agreement with previous experimental and theoretical data [23].

Besides, the binding energy of the Pr 3d5/2 core level for Pr2O3 and the difference

between the binding energy of Pr 3d5/2 and the Pr 3d3/2 core level was typical to previously reported data on Pr2O3.

Figure 2.6 (a) shows the typical transfer characteristics (IDS-VGS) and

maximum transconductance for the proposed Pr2O3 TFT and TEOS TFT with a

dimension of Width/Length (W/L) = 2µm/2µm at VDS = 0.1V and 1V, respectively.

The ON/OFF current ratio is defined as that ratio of the maximum on-state current to the minimum off-state current at VDS = 1 V. The threshold voltage (VTH) is defined as

the gate voltage required to achieve a normalized drain current of IDS = (W/L)×100 nA

at VDS = 0.1 V. The Pr2O3 TFT exhibited improved electrical performance, including

threshold voltage decreased from 2.28 V to 1.27 V, subthreshold swing improved from 1.08 V/dec. to 0.22 V/dec., and ON/OFF current ratio increased from 3.5×106 to 10.6× 106, as compared to TEOS TFT. However, the undesirable gate-induced drain leakage (GIDL) current of the Pr2O3 TFT is higher than that of the TEOS TFT,

especially under a continuously decreasing gate bias. This inferior GIDL current may be ascribed to the higher vertical electric field near the drain junction owing to the thin EOT of Pr2O3 gate dielectric. The issue could be relaxed by utilizing lightly

doped drain (LDD) or field-induced drain (FID) structure [24], [25]. Figure 2.6 (b) shows the mobility for the proposed Pr2O3 TFT and TEOS TFT with a dimension of

Width/Length (W/L)=2µm/2µm at VDS = 0.1 V. The field-effect mobility (µFE)

enhance from 23 cm2/V-s to 44 cm2/V-s under the gate voltage range between 0 to 8 V. Because of the subthreshold of TEOS is more slope than Pr2O3 high-κ , the mobility

of TEOS is smaller than Pr2O3.

TFT are illustrated in Figure 2.7. The device has a drawn channel length (L) and channel width (W) of 2 µm and 2 µm, respectively. As can be seen, the driving current of Pr2O3 TFT (around 97 µA) is approximately six times larger than that of TEOS TFT

(around 16 µA) at VDS = 4 V and common gate drive of VGS – VTH = 4 V, respectively.

This driving current enhancement results from the high capacitance density induced higher mobility and smaller threshold voltage for the Pr2O3 TFT compared with the

TEOS TFT. Hence, this large driving capability is attractive for high-speed peripheral driving IC’s application. Note that obvious improvements in device characteristics were achieved even without the implementation of NH3 plasma passivation [26] or

advanced phase crystallization technique such as excimer-larser annealing (ELA). The measured and extracted device parameters are summarized in Table 2.1, where the data value from TFT devices with other gate dielectrics, such as HfO2,

LaAlO3, and PECVD TEOS oxide from this work are also shown for comparison. It

was found that the electrical characteristics of the poly-Si TFT with the implementation of TiN metal gate on high-κ Pr2O3 gate dielectric were comparable to

other reported data [5], [6]. Besides, we summarized the improved degree of this experimental result in Table 2.2. The enhancement of substhreshold is 86%, mobility is 91% and ON/OFF current ratio is 2 twice.

To examine the short-channel effect of TFTs with different gate dielectrics, the threshold-voltages (VTH) rolloff of Pr2O3 and TEOS ploy-Si TFTs are compared in

Figure 2.8. For poly-Si TFTs, the threshold-voltage rolloff is dominated by the decreasing of number of grain boundary as the devices scale down [27]. For the long-channel poly-Si TFTs, the large number of grain boundaries in the channel raises the threshold voltage and degrades the effective mobility [28]. The Pr2O3 TFTs with

grain boundary and turn on the devices fast; therefore, not only release the grain-boundary effect but also lower the threshold voltage effectively.

2.4 Summary

High performance SPC poly-Si TFT integrated with Pr2O3 gate dielectric and

TiN metal gate has been successfully demonstrated for the first time. This work provides the thinnest EOT of 6.5-nm from the high gate capacitance density of Pr2O3

film. The electrical characteristics of Pr2O3 TFT can be effectively improved

compared to those of TEOS TFT, including lower threshold voltage, steeper subthreshold swing, higher field-effect mobility, and higher driving current capability, even without additional hydrogenation treatment or advanced phase crystallization techniques. Therefore, the proposed Pr2O3 TFT is a good candidate for high

Reference

[1] H. Ohshima and S. Morozumi, “Future trends for TFT integrated circuits on glass substrates,” in IEDM Tech. Dig., 1989, pp. 157–160.

[2] K. Yoneda, R. Yokoyama, and T. Yamada, “Development trends of LTPS TFT LCDs for mobile application,” in Symp. VLSI Circuits, Dig. Tech. Papers, 2001, pp. 85–90.

[3] T. Serikawa, S. Shirai, A. Okamoto, and S. Suyama, “Low-temperature fabrication of high-mobility poly-Si TFTs for large-area LCDs,” IEEE Trans. Electron Devices, vol. 36, no. 9, pp. 1929–1933, Sept. 1989.

[4] Takami, A. Ishida, J. Tsutsumi, T. Nishibe, and N. Ibaraki, in Proc. Int. Workshop AM-LCD, Tokyo, Japan, 45, (2000)

[5] C. Jahan, O. Faynot, M. Cassé, R. Ritzenthaler, L. Brévard, L. Tosti, X. Garros, C. Vizioz, F. Allain, A.M. Papon, H. Dansas, F. Martin, M. Vinet, B. Guillaumot, A. Toffoli, B. Giffard and S. Deleonibus, “ FETs transistors with TiN metal gate and HfO2 down to 10nm,”

[6] F.-S. Wang, M.-J. Tsai, and H.-C. Cheng, “The effects of NH3 plasma

passivation on polysilicon thin-film transistors,” IEEE Electron Device Lett., vol. 16, no. 11, pp. 530–505, Nov. 1995.

[7] B. F Hung, K.C. Chiang, C. C. Huang, Albert Chin, Senior Member, IEEE, and S.P. McAlister, Senior Member, IEEE “High-performance poly-silicon TFTs incorporating LaAlO3 as the gate dielectric,” IEEE Electron device Letters, vol.

26, NO.6, June 2005

[8] H. J. Osten et al, “Epitaxial Praseodymium Oxide: A New High-κ Dielectric,” Solid-State Electron., 47, 2161 (2003).

Based On Praseodymium Oxide,” Tech. Dig. - Int. Electron Devices Meet., 653 (2000).

[10] G. Adachi , N. Imanaka, “The Binary Rare Earth Oxides,” Chem. Rev., 98, 1479 (1998).

[11] H. J. Osten et al, “Band Gap And Band Discontinuities At Crystalline Pr2O3/Si(001) Heterojunctions,” Appl. Phys. Lett. 80, 297 (2002).

[12] J. C. Lee et al, “Ultrathin Hafnium Oxide With Low Leakage And Excellent Reliability For Alternative Gate Dielectric Application,” Tech. Dig. Int. Electron Devices Meet., 133 (1999).

[13] J. C. Lee et al, “MOSCAP and MOSFET Characteristics Using ZrO2 Gate Dielectric Deposited Directly On Si,” Tech. Dig. - Int. Electron Devices Meet., 145 (1999).

[14] H. J. Osten, J. P. Liu, “ High-κ Gate Dielectrics with Ultra-low Leakage Current Based on Praseodmium Oxide” IEEE (2000)

[15] B. Maiti, P. J. Tobin, C. Hobbs “ PVD TiN metal gate MOSFETs on bulk silicon and fully depleted silicon-on-insulator substrates for deep sub-quarter micron CMOS technology,” in Int, Electron Devices Meeting (IEDM) tech, Dig., 1999, pp.253-256.

[16] H. Wakabayashi, Y. Saito, K.Takeuchi, “ A novel W/TiNx metal gate CMOS technology using nitrogen-concentration-controlled TiNx film,” in Int, Electron Devices Meeting (IEDM) tech Dig., 1999, pp.95-96.

[17] K. Nakajima, Y. Akasaka, M. Kaneko, “Work function controlled metal gate electrode on ultrathin gate insulators,” in proc.symp. VLSI tech. Dig., 1999, pp.253-256

contact hole (PRETCH): A new method for high-κ/ metal gate and multi-oxide implementation on chip,” in Int, Electron Devices Meeting (IEDM) tech Dig., 2004, pp.291-294.

[19] M. Vinet, T. Poiroux, J. Widiez, “ Planar double gate CMOS transistors with 49 nm metal gate for multipurpose applications,” in Ext, Abstr. Int. Conf. SSDM, 2004, pp.76-769.

[20] J. R. Hauser and K. Ahmed, “Characterization of ultrathin oxides using electrical C-V and I-V measurements,” in proc. AIP Conf. Charact. and Merol. ULSI Technol.,1998, vol.449, pp.235-239.

[21] H. J. Osten, J. P. Liu, P. Gaworzewski, E. Bugiel, and P. Zaumseil, in IEDM Tech. Dig. 653, (2000).

[22] U. Schwalke, K. Boye, K. Haberle, R. Heller, G. Hess, G. Müller, T. Ruland, G. Tzschöckel, J. Osten1, A. Fissel, H.-J. Müssig, ESSDERC, 407 (2002).

[23] H. Ogasawara, A. Kotani, R. Potze, G. A. Sawatzky, and B. T. Thole, Phys. Rev. B 44, 5465 (1991)

[24] “Novel self-aligned LDD/offset structure for poly-Si thin film transistors,” in Proc. SID, 2001, pp. 1250–1253.

[25] H. C. Lin, C. M. Yu, C. Y. Lin, K. L. Yeh, T. Y. Huang and T. F. Lei, "A novel thin-film transistor with self-aligned field induced drain," Electron Device Letters, IEEE, vol. 22, pp. 26-28, 2001.

[26] I. W. Wu, W. B. Jackson“Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation,” IEEE Electron Devices lett., vol.12, pp. 181-183, May 1991

[27] S. Chopra and R. S. Gupta, “An analytical model for current–voltage characteristics of a small-geometry poly-Si thin-film transistor,” Semicond. Sci.

Technol., vol. 15, no. 11, pp. 1065–1070, Nov. 2000.

[28] Physical mechanisms for short channel effects in polysilicon thin film transistors,” in IEDM Tech. Dig., 1989, pp. 349–352.

High-k process

● 500-nm thermal oxidation at 980oC

● 100-nmα-si deposition at 550oC by LPCVD ● SPC at 600oC for 24h in N

2 ambient (α-Si Î poly-Si)

● Define active region

Buried Oxide ( 500nm) Si Substrate

Undoped Poly-Si (100nm)

● 33.6-nm Pr

2O3film deposition by e-gun evaporation system

● Furnace annealing at 600oC for 30 min in N

2ambient

● 200-nm TiN film by PVD ● Define gate electrode

Pr2O3gate dielectric (33.6nm)

TiN gate electrode (200nm)

Buried Oxide ( 500nm) Si Substrate

● Self-aligned source/drain implantation (P+ 5x1015 90keV) ● Dopant activation at 600oC for 30min in N

2 ambient P+ion implantation Buried Oxide ( 500nm) Si Substrate N+ N+ TiN

● 300-nm passivation oxide SiO

2by PECVD

● Define contact hole, two-step wet-etching process ● 400-nm Al pads

● N

2/H2sintering at 400oC for 30min

Passivation (300nm) Al (400nm) Buried Oxide ( 500nm) Si Substrate TiN N+ N+

T iN G a te E le c tr o d e

P r

2O

3(3 3 .6 n m )

P o l y -S i (9 7 n m )

In t e r f a c ia l la y e r ( 1 .5 n m )

Gate Votalge (V)

-4

-2

0

2

4

C/A (nF/cm

2)

0

100

200

300

400

500

600

κ = 26.2

EOT = 6.5 nm

C

acc= 532 nF/cm

2Reverse switching with

repeating 100 cycles Initial forward switching

- 4 V to + 4 V

+ 4 V to - 4 V

Fig. 2.3 Typical C–V characteristics of the Pr2O3 gate dielectric demonstrating the

Gate Field (MV/cm)

0 2 4 6 8 10 12 14 16Gate Current

Densit

y (

A

/cm

2)

10-10 10-9 10-8 10-7 10-6 10-5 10-4 10-3 10-2 10-1 Area = 1.52X10-3cm2 Physical thickness = 33.6nm T=25oCBinding Energy (eV)

920

930

940

950

960

970

Inte

ns

ity

(a

.u.)

Pr 3d

Pr 3d

3/2Pr 3d

5/220 eV

Fig. 2.5. Pr 3d photoelectron spectrum for Pr2O3.The inset also shows the O 1s

photoelectron Spectrum which clearly indicates the presence of Pr2O3.

526

528

530

532

534

536

538

540

In

te

ns

ity

(a

.u

.)

Binding Energy (eV)

-2 0 2 4 6 8 10-13 10-12 10-11 10-10 10-9 10-8 10-7 10-6 10-5 10-4 0 1 2 3 4 5 6

Dra

in Curr

ent, I

DS(A)

Gate Voltage, V

GS(V)

g

m

(

µS)

Pr2O3TFT TEOS TFT W/L = 2µm/2µm VDS= 0.1V, 1V (a) W / L= 2µm / 2µm VDS = 0.1VGate Voltage V

G(V)

-2 0 2 4 6 8M

obili

ty

(c

m

2/V

-s

)

0 10 20 30 40 50 Pr2O3 TFT TEOS TFT (b)Fig. 2.6 (a) Typical transfer characteristics (IDS-VGS) and (b) mobilityof the proposed

Fig. 2.7 Typical output characteristics (IDS-VDS) of the proposed TiN metal gate and

high-κ Pr2O3 gate dielectric poly-Si TFT. (W/L=2µm/2µm)

Pr

2O

3TFT

TEOS TFT

(V

GS- V

TH) = 1V to 4V

Step = 1V

W/L = 2 m/2

0

1

2

3

4

0

20

40

60

80

100

Drain Cur

rent, I

DS(

µA)

Drain Voltage, V

DS(V)

35 nm/ 42.6 nm 50 nm/ 8.7 nm 27.7 nm/ 7.3 nm 33.6 nm/ 6.5 nm TPhysical/ EOT 2/2 100/4 0.1/1 2/2 W/L (µm) 1.5 40 0.31 1.2 LaAlO3 [6] 9.7 39 0.28 0.3 HfO2 [5] 3.5 23 1.08 2.28 PECVD TEOS [This work] 10.6 44 0.22 1.27 Pr2O3 [This work] ION/IOFFratio (106) (max ION@VDS=1V) µEF(cm2/V-s) S.S. (V/decade) VTH(V) SPC poly-Si TFT with various gate

dielectrics

Table 2.1 Comparison of device characteristics of the HfO2, LaAlO3, TEOS and Pr2O3

gate dielectric SPC poly-Si TFTs.

X 35 nm/ 42.6 nm 33.6 nm/ 6.5 nm TPhysical/ EOT X 2/2 2/2 W/L (µm) 3.5 23 1.08 2.28 PECVD TEOS [This work] 203% 91% 86% 1.01 Enhancement 10.6 44 0.22 1.27 Pr2O3 [This work] ION/IOFFratio (106) (max ION@VDS=1V) µEF(cm2/V-s) S.S. (V/decade) VTH(V) SPC poly-Si TFT with various gate

dielectrics

Table 2.2 Improvement of device characteristics of the TEOS and Pr2O3 gate