低電壓互補式金氧半導體高頻壓控振盪器與鎖相迴路設計

全文

(2) 低電壓互補式金氧半導體高頻壓控振盪器與鎖相迴路設計 Low Voltage CMOS RF Voltage-Controlled Oscillator and Phase-Locked Loop Design. 研 究 生:邱顯鴻. Student : Hsien-Hung Chiu. 指導教授:鍾世忠. Advisor : Shyh-Jong Chung. 國立交通大學 電機學院 電信學程 碩士論文. A Thesis Submitted to College of Electrical and Computer Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Master of Science in Communication Engineering January 2007 Hsinchu, Taiwan, Republic of China. 中華民國 九十六 年 一 月.

(3) 低電壓互補式金氧半導體高頻壓控振盪器與鎖相迴路設計. 研究生:邱顯鴻. 指導教授:鍾世忠. 國立交通大學 電機學院 電信學程碩士班. 摘要 無線通訊射頻晶片在收發機的應用裡,低功率消耗為一個重要的課題,本論文以壓 控振盪器與鎖相迴路兩個部份來探討低電壓操作的電路設計,藉以降低功率消耗,並利 用 TSMC 0.18μm RF CMOS 製程完成可應用於超寬頻 UWB 系統之低電壓 CMOS 高頻壓 控振盪器與鎖相迴路電路和 WiFi 系統的低電壓 CMOS 雙頻段壓控振盪器設計。 第一部份設計三種不同電路特性的低電壓壓控振盪器;第一個設計為應用於超寬頻 0.6V 低電壓之壓控振盪器,採用 NMOS 交連耦合對的 LC 調諧壓控振盪器加上交聯電 容架構設計,藉由在主動埠並聯電容改善品質因數。量測結果,功率消耗僅有 0.54mW, FOM 值為 185。第二個振盪器採用四相位正交輸出的設計,利用基底串連高阻抗電阻來 降低輸出相位雜訊,改善一般低電壓正交輸出壓控振盪器的相位雜訊率,在 0.65V 操作 下量測功率消耗為 2.67mW, FOM 值為 181.7。第三個振盪器為雙頻段四相位正交輸出 的設計,利用簡化雙頻帶 VCO 及電流再利用方式設計,降低一般雙頻段正交輸出壓控 振盪器耗功率的缺點。在低頻段 1.3V 及高頻段 1.5V 電壓操作下,量測功率消耗為 5.46mW 及 6.75mW,FOM 值皆為 171。 第二部份設計可應用於超寬頻 UWB 系統之低電壓鎖相迴路。鎖相迴路設計在 1V 的低電壓操作,輸出頻率為 5.016GHz,採用的除頻器為使用位準偏移的主樸式偶合閘 (CML divider)電路,配合預先充放電式的相位比較器,改良單相時脈除頻器(TSPC divider) 的設計,整個迴路模擬結果功率消耗為 5.58mW。 I.

(4) Low Voltage CMOS RF Voltage-Controlled Oscillator and Phase-Locked Loop Design. Student : Hsien-Hung Chiu. Advisor : Shyh-Jong Chung. Degree Program of Electrical Engineering and Computer Science National Chiao Tung University ABSTRACT. The low power consumption plays an important role in RFIC’s for wireless communication transceiver. RFIC usually consists of Mixer, Voltage-Controlled Oscillator (VCO), Filter, Power Amplifier, etc. One of important component is VCO in power consumption issue. In this thesis a low voltage operation circuit for VCO and Phase-Locked Loop (PLL) is developed. The TSMC 0.18μm RF CMOS manufacture Technology is used for ultra low voltage VCO and low voltage phase-locked loop which can be applied to UWB system and dual band quadrature phase voltage-controlled oscillator which can be applied to WiFi system. There are three kinds of low voltage VCOs be implemented with different circuit characteristics. The first kind of VCO uses LC tank with NMOS cross-coupled pair and cross-paralleled capacitor improving the quality factor in the active port. The measured power consumption of VCO core circuit draws only 0.54mW and FOM value is 185. The second kind of VCO connects serial high impedance resister to bulk to decreasing noise induce. That improves traditions quadrature phase VCO phase noise. The measured power consumption of VCO core circuit is 2.67mW and FOM value is 181.7 under 0.65V supply. The third kind of dual band low power QVCO simplify traditions dual band VCO circuit and adopts current-reuse topology. The measured power consumption of DB-QVCO core circuit is 5.46mW and 6.75mW under 1.3V and 1.5V supply for low band and high band. FOM value is both 171 . The second part designs low voltage PLLs that can be applied to UWB system. PLLs output frequency is 5.016GHz and including I/Q signals. The low voltage PLL adopts level shift current mode logic (LS-CML) divider at the 1st stage divider. Using reform pre-charge phase frequency detector (PFD) and refine true single phase clock (TSPC) divider. The whole loop simulated power dissipation is 5.58mW. II.

(5) 誌謝 完成這篇論文首先要感謝指導老師鍾世忠教授的教導及愛護,讓我學習到研究之方 法與解決問題之能力,而口試委員邱煥凱、孟慶宗、黃天偉教授在畢業口試時對論文內 容需要在改進的地方提出他們寶貴的意見,在此表達致謝。 其次要感謝的是電資 810 實驗室,感謝博士班佩宗、清標在我遇到問題時,總能夠 提出辦法解決,並提供意見跟我分享討論,在量測時從旁協助指導,實在讓我受益良多; 感謝 810 實驗室夥伴天建、敦智、煥能、郁娟、源哥、竣義、淑君、永旭、威聰、智偉, 有你們在一起努力研究,一起熬夜等待陽光的日子是種享受,感謝大家陪我度過研究所 的美好時光,相信實驗室在各位共同努力下,一定能越來越強。 最後要感謝的是我的家人,爸爸、媽媽、姊妹們,感謝你們提供我生活上的幫助, 感謝我的老婆舒凱及兒子奕瑋還有老婆肚子裡的寶貝給了我精神上的支持,讓我在工作 之餘,可以完成碩士班學業。 在這三年多的期間,歷經我生命中最重要的求學結婚生子,承蒙許多人的提攜和照 顧,對曾經關心幫助過我的人,至上萬分的謝意,並祝福你們。. 顯鴻. 2007 歲初 新竹 風城. III.

(6) 目錄 中文摘要 ...................................................................................................................Ⅰ 英文摘要 ……………………………………………………………………….......Ⅱ 誌謝............................................................................................................................Ⅲ 目錄............................................................................................................................Ⅳ 表目錄 .......................................................................................................................Ⅵ 圖目錄 .......................................................................................................................Ⅶ 第一章 緒論 … … … … … … … … … … … … … … … … … … … … … … … … … … … . 1 1-1 研 究 動 機 … … … … … … … … … … … … … … … … … … … … … … … … … … … . . . 1 1-2 研 究 方 法… … … … … … … … … … … … … … … … … … … …… … … … … … … … . 2 1-3 研 究 成 果 … … … … … … … … … … … … … … … … … … … …… … … … … … … … . 3 1-4 章 節 概 序… … … … … … … … … … … … … … … … … … … …… … … … … … … … . 4. 第二章 相位雜訊及壓控振盪器……………………………………………5 2-1 相位雜訊的定義………………………………………………………………….5 2-2 相位雜訊對通訊系統的影響…………………………………………………….7 2-3 振盪器的相位雜訊……………………………………………………………….8 2-4 壓控振盪器理論基礎及設計方法………………………………………………18 2-4-1 重要規格參數……………………………………………………………...18 2-4-2 CMOS 壓控振盪器架構…………………………………………………..22 2-5 壓控振盪器正交輸出方法………………………………………………………25 2-6 低電壓壓控振盪器設計方法………….…………………………………………27 2-6-1 低電壓壓控振盪器考量…………………………………………………...27 2-6-2 低相位雜訊壓控振盪器考量……………………………….……………..30 2-6-3 低功率低相位雜訊壓控振盪器考量……………………………………..31 2-6-4 低電壓 CMOS 壓控振盪器架構………………………………………...31. 第三章 低電壓壓控振盪器………………………………………………..36 3-1 應用於超寬頻 0.6V 低電壓壓控振盪器………………………………………36 3-1-1 設計方法…………………………………………………………………...36 3-1-2 模擬及量測結果……………..……………………………………………...38 3-1-3 討論………………………………………………………………………...44 3-2 應用於超寬頻低電壓低功率四相位壓控振盪器設計…………………………46 3-2-1 設計方法…………………………………………………………………...46 3-2-2 在主動埠電晶體加基底電阻和交聯電容比較結果….…..…..…………...47 3-2-3 模擬及量測結果………..………..………………………………………...48 IV.

(7) 3-2-4 討論………….............………………..……………………………………..…...55 3-3 應用於 WiFi 低功率雙頻段四相位壓控振盪器設計…………………………57 3-3-1 設計方法…………………………………………………………………...57 3-3-2 模擬及量測結果……………..……………………………………………...63 3-3-3 討論………………………………………………………………………...68. 第四章 應用於 UWB 系統之低電壓鎖相迴路…….………………………………70 4-1 鎖相迴路架構與基本原理………………………………………………………70 4-1-1 壓控振盪器概論……………………………………........…….............71 4-1-2 除頻器………………………………....……………………….............72 4-1-3 相位頻率檢測器……………………………………………....………..….72 4-1-4 電流幫浦與迴路濾波器…………...……………….……….……….........74 4-2 低電壓鎖相迴路設計…………………………………………………………………...76 4-2-1 正交輸出壓控振盪器………..……………………….….…………………77 4-2-2 除頻器……………………………………………………….….…………..78 4-2-3 頻率相位檢測器……………………………………………………………..79 4-2-4 電流幫浦…………………………………………………………………..80 4-2-5 迴路濾波器………………………………………………………………..82 4-2-6 其他設計考量……………………………………………………………..82 4-2-7 模擬結果………………………………………………………………......90 4-2-8 討論…………………………………………………………...………...91. 第五章 結論 …………………………………………………………………….…93 參考文獻....................................................................................................................95. V.

(8) 表目錄 表 表 表 表 表 表 表 表 表 表 表 表 表. 1.1 2.1 2.2 2.3 3.1 3.2 3.3 3.4 3.5 3.6 3.7 4.1 4.2. 本論文完成之射頻電路設計..……………………………………………….....3 低功率振盪器設計考量……..……..………..………………………………....30 低相位雜訊振盪器設計考量.......…...………………………………………....31 低功率低相位雜訊振盪器設計對策.......…………….…………….…………31 【電路 1】 應用於超寬頻 0.6V 低電壓之壓控振盪器模擬與量測總表……......45 【電路 1】 電路之效能與其他低電壓之壓控振盪器的比較表.......………….....45 【電路 2】 應用於超寬頻之低電壓低功率四相位壓控振盪器規格表…............56 【電路 2】 應用於超寬頻之低電壓低功率四相位壓控振盪器重調後比較表…56 【電路 2】 電路之效能與其他低電壓之壓控振盪器的比較表.......………….....57 【電路 3】 低功率雙頻段四相位壓控振盪器設計模擬與量測規格表……........69 【電路 3】 電路之效能與其他雙頻段四相位壓控振盪器的比較表........……....69 【電路 4】 低電壓鎖相迴路規格表…....................................................................91 【電路 4】 電路之效能與其他低電壓鎖相迴路的比較表....................................91. VI.

(9) 圖目錄 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖. 1.1 1.2 2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.9 2.10 2.11 2.12 2.13 2.14 2.15 2.16 2.17 2.18 2.19 2.20. 超寬頻頻率合成器架構………….…………..…………………………………2 直接降頻接收機架構………….………………………………………………..3 振盪器輸出訊號頻譜圖…………………..…………………………………….6 相位雜訊定義……………………………..…………………………………….7 相位雜訊在接收端的影響………………………………………………………..7 電感電容振盪器等效單端電路…………….……….…………………………….8 雜訊電流轉換為相位雜訊邊帶的頻譜示意圖...…………………………….10 Lesson’s 相位雜訊模型……………………………………………………….11 電流脈衝注入 LC 振盪器…………………….………………….…………...12 脈衝注入造成振盪訊號的改變……………………………………………….13 LC 振盪器與環形振盪器典型的脈衝響應函數曲線………………………14 電流雜訊對相位雜訊的貢獻成分….……….………………………………17 基本壓控振盪器…….………………………………………………………18 基本壓控振盪器理想輸出的波形和頻譜…………...……………………...18 振盪器輸出訊號頻譜圖...…………………………………………………...19 相位雜訊在接收端的影響……………………………………………..……20 頻率漂移示意圖…..……………………………….…………………..……22 使用負阻消除 LC 諧振腔的寄生電阻示意圖………….……..…………..23 串並聯轉換.…………………………………………….……………………23 等效簡易模型.….……………………………………….……………………23 NMOS 交錯耦合對……….....………………………….…..……………..24 互補式交錯耦合對….….………...………………………………………….24. 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖. 2.21 2.22 2.23 2.24 2.25 2.26 2.27 2.28 2.29 2.30 2.31 2.32 2.33 2.34 3.1. 單端式環型振盪器示意圖…………….……………………………………..25 四級差動環型振盪器示意圖………...………………………………………..25 數位除頻器方法……………………………………………………………..26 多相位濾波器方法…………………………………………………………..26 雙交叉耦合方法……………………………………………………………..27 低損耗的 LC 被動電路..……………………………………………………..27 包含負電導的低損耗的 LC 被動電路.……………………………………...28 交錯耦合的晶體形成的壓控振盪器…………….…………………………..29 基本的 LC 諧振腔....…………..……………….…………………………..30 LC 調諧壓控振盪器主動埠種類………..…..…………………………..32 加入負電導 G N 後 LC 諧振腔的示意圖…………...……………….…..33 外加 C N 負電導組態的型態………….……………………………………..33 緩衝放大器….…………………………………………..……………………..34 完整的緩衝放大器考量設計圖..………………..…….…………………....35 0.6V 低電壓 7.92GHz 壓控振盪器….…......……………………………..40 VII.

(10) 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖. 3.2 0.6V 電路模擬及量測結果.….…………………………………………....40 3.3 0.62V 電路模擬及量測結果…..………..…….…………………………....41 3.4 0.65V 電路模擬及量測結果…..………..……….………………………....43 3.5 諧波信號量測結果…….....…..…………………..……….……………………43 3.6 應用於超寬頻 0.6V 低電壓之壓控振盪器佈局圖及實際電路…...........…...43 3.7 應用於超寬頻 0.6V 低電壓之壓控振盪器測試板佈局圖及實際電路…..…..44 3.8 超寬頻低電壓四相位壓控振盪器…………………..………………………….47 3.9 外加 Cs 及 Rsi 電路特性改善比較結果…….……………………………..48 3.10 0.6V 超寬頻低電壓四相位壓控振盪器 7.92GHz 模擬結果…………..49 3.11 整體四相位模擬輸出………………………………………………………..49 3.12 VQ+及 VI+正交訊號的輸出….………………………………………..50 3.13 VQ+及 VQ- 對稱訊號的輸出.………………………………………....50 3.14 0.6V 調整後四相位壓控振盪器模擬及量測結果.….…………….…..52 3.15 0.62V 調整後四相位壓控振盪器模擬及量測結果.….………………..53 3.16 0.65V 調整後四相位壓控振盪器模擬及量測結果.….………………..54 3.17 諧波信號量測結果..………………..……………..…….…………………54 3.18 應用於超寬頻之低電壓低功率四相位 壓控振盪器佈局圖及實際電路..54 3.19 應用於超寬頻之低電壓低功率四相位壓控振盪器測試板佈局圖及實際電路. 55. 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖. 3.20 3.21 3.22 3.23 3.24 3.25 3.26 3.27 3.28 3.29 3.30 3.31 3.32 3.33 3.34 4.1 4.2 4.3 4.4 4.5 4.6. 互補式交連耦合對電路…………………………………………..........58 一般雙頻帶壓控振盪器……….………………………..………...........59 傳統雙頻帶壓控振盪器…………………………..…………...............59 簡化型之壓控振盪器……………………………….….…………........60 簡化型壓控振盪器重整後之電路圖…………………….……............60 低功率雙頻帶壓控振盪器之電路………..…..……….………...........61 四相位產生概念圖………………..………..….…...………………….62 一般的四相位壓控振盪器………………….…………………………...62 低功率雙頻段四相位壓控振盪器電路………….………….……….……63 低 功 率 雙 頻 段 四 相 位 壓 控 振 盪 器 模 擬 低 頻 段 2 . 4 G H z 特性 … . . … . … 6 4 低 功 率 雙 頻 段 四 相 位 壓 控 振 盪 器 模 擬 高 頻 段 5 . 2 G H z 特性 … … . . … . 6 5 低 功 率 雙 頻 段 四 相 位 壓 控 振 盪 器 量 測 低 頻 段 2 . 4 G H z 特性 … . . … … . 6 7 低 功 率 雙 頻 段 四 相 位 壓 控 振 盪 器 量 測 高 頻 段 5 . 2 G H z 特性 … . . . … … 6 7 低功率雙頻段四相位壓控振盪器設計佈局圖及實際電路……….......67 低功率雙頻段四相位壓控振盪器測試板佈局圖及實際電路.….……..68 鎖相迴路基本架構圖………..…………….…….………….….……...70 壓控振盪器特性圖………………………….…….……….…………..71 相位頻率偵測器運作示意圖….….……….……….……….…………73 相位頻率偵測器三態狀態圖..…………….………..…….…………..73 相位偵測與電壓輸出……………………….……….…………………74 相位頻率偵測器與電荷幫浦之示意與時序圖…….…….….….……..76 VIII.

(11) 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖 圖. 4.7 4.8 4.9 4.10 4 . 11 4.12 4.13 4.14 4.15 4.16 4.17 4.18 4.19 4.20 4.21 4.22 4.23 4.24 4.25 4.26 4.27 4.28 4.29 4.30 4.31. 鎖 相 迴 路 架 構 … … … … . … … … … . … … … … … …… … … … … … … … . . 7 7 低電壓 5.016GHz 正交壓控振盪器……..……………………………..77 位準偏移主僕式耦合閘預除器電路...…………………………………..78 改良式真單相時脈(TSPC)除二電路…..………………………………...79 除 64 電路……………………………………….…….………………..79 傳統相位頻率檢測器…….………………………..…………………...80 預先充電型相位頻率檢測器…..……………………………………....80 傳統電流幫浦電路架構.………….…………………………………....81 電流幫浦..……………………………………………………….……...81 二階迴路濾波器…..……………………..…….…….………………....82 緩衝放大器….……..…….……………..…………..……….……….82 佈局考量.…………………………………………….……...…..…...83 PA D 等 效 模 型 … … … … … … … … … … … … … … … … … … … … … . . . 8 3 鎊線等效模型……………………….…………………………………84 正交輸出壓控振盪器模擬結果……….………….……………………85 位準偏移主僕式耦合閘除 2 電路頻域輸出………………..……...85 除 64 電路輸出時域波形圖………………..……………………...86 參 考 信 號 ( Vr ) 相 位 領 先 回 授 信 號 ( V d ) … … … . . … … … … … … . … . . 8 7 迴 授 信 號 ( V d ) 相 位 領 先 輸 入 信 號 ( Vr ) … . . … … … … … … … … … … . 8 7 迴路頻寬..………..………………………………………..…….....88 A D S Tr a n s i e n t Re s p o n s e 安 置 時 間 模 擬 結 果 … … . … … … … . . . 8 8 壓控振盪器控制電壓時域波形圖……….……………………………89 壓控振盪器控制電壓在穩態下時域變化….…………………………89 迴路穩定下時域波形圖……….…………………….…………….....90 低電壓鎖相迴路佈局平面圖…………….……………..………….….90. IX.

(12) 第一章. 緒論 §1-1 研究動機 超寬頻(UWB)技術自從 2002 年二月美國聯邦通訊委員會(FCC)核准 3.1GHz 至 10.6GHz 的頻帶共 7.5GHz 頻寬作為商業用途後,相關技術研發便在產業界及學術界上 蓬勃的發展,目前由 MBOA 聯盟所提出的多頻帶正交頻率多工超頻寬( Multi-band OFDM UWB)系統為目前業界多數廠商所支持的方案。其中最重要應用的子頻帶在於最 低的三個頻率,中心頻率分別為 3432MHz、 3960MHz、 4488MHz,因為位於較佳的 通道效應中,此三個頻帶構成了 MB-OFDM 系統的第一模態傳收系統[1],在實際超寬 頻收發機電路設計的頻率合成器(Frequency Synthesizer)為收發機(Transceiver)中切換 頻率最主要的元件,其目的主要做為訊號產生,此訊號可視為本地振盪(Local Oscillation) 訊號,而在頻率合成器架構中壓控振盪器(Voltage Control Oscillation, VCO)和鎖相迴路 (Phase Lock Loop, PLL)為一不可缺少之元件,故將以此方向來做相關研究。 目前在無線通訊設計上,多頻帶與多模態系統之整合射頻傳收模組為發展的趨勢, 在傳統的互補式壓控振盪器(Complementary VCO),其設計架構擁有較高的增益及較大 的輸出功率,因而可得到相位雜訊較佳的表現。但此種架構在佈局走線上會較複雜,對 於高頻電路來說,線與線之間跨線所產生的耦合效應及這些拉線所造成的寄生電阻及寄 生電容都會對晶片設計產生影響。因此針對傳統架構的壓控振盪器來做簡化而得到簡化 型壓控振盪器,用來減少佈局上的跨線,相對的減少了不必要之跨線及拉線本身之寄生 效應,而會得到較好的特性,其中利用電流再使用的方式降低功率的損耗,配合一顆開 關電晶體和電感即可達到雙頻帶的效果,再加上四相位耦合的電晶體交錯編排使用直接 耦合(direct couple)及交錯耦合(cross couple)的連接方式來連接兩個雙頻帶振盪器,即可 產生四相位訊號之輸出。此方式不僅簡化了雙頻帶正交壓控振盪器的設計,更因此減少 電感的使用量,可減少面積的使用,及降低功率的損耗。. 1.

(13) §1-2 研究方法 為設計低消耗功率的頻率合成器在超寬頻 MBOA 系統中可攜式無線傳輸系統的收 發機應用,首先考量操作在低電壓低耗能的壓控震盪器,接著配合加上作為四相位耦合 的電晶體交錯編排的連接方式來連接兩個振盪器,用以設計一組產生四個相位的低電壓 正交輸出壓控振盪器。最後依實驗室超寬頻架構需求,設計 1V 低電壓鎖相迴路電路。 本研究將以低功率消耗為方向來設計一低電壓低功率壓控震盪器( Low Voltage Low Power VCO ),使其應用在超寬頻MBOA 系統中頻率合成器的鎖相迴路設計。由於主要 應用在直接降頻接收機如圖1-1的架構,構想上利用頻率合成器產生一組固定的頻率 7920 MHz輸出,其中一路為經過除二電路後產生3960MHz透過選擇器擇一輸出到單一 側頻混波器(SSB-Mixer),另一路經過除法器分別產生適當頻率並搭配著多工器選擇其中 之一輸出到另一端單一側頻混波器( SSB-Mixer )的輸入,混頻後可產生在超寬頻MBOA 系統中模態A (Group A),模態B (Group B),模態C (Group C)三個模態中的頻段,為實現 於可攜帶式的應用,以低電壓低耗能壓控震盪器( Low Voltage Low Power VCO )操作頻 率設計在7920 MHz做研究,最後並依照實驗室需求設計操作頻率在5016 MHz的1V低電 壓鎖相迴路。. 圖1.1 超寬頻頻率合成器架構 應用WiFi方面,主要是針對直接降頻接收機(direct-conversion receiver)架構,其操 作頻率分別為2.4 GHz、5.2GHz,如圖1-2所示。其優勢在於降低功率損耗、縮小晶片及 PCB面積(減少外部元件使用),並且減少系統廠商所需整合的時間及具有適應不同頻寬 和標準的靈活性。不過,直接降頻接收機在電路設計上需解決時變的直流偏移(DC offset)、本地訊號洩流(LO leakage)、增益/相位不匹配以及閃爍雜訊(flicker noise)等問 題,必須經由額外的電路來消除這些現象,但此架構極適合高度整合成系統單晶片 2.

(14) ( System on a Chip:SoC ),故以此為方向來設計一雙頻帶四相位壓控震盪器( Dual-Band Quadrature VCO ),使其應用在WiFi系統( 802.11 a/b/g )上,針對消耗功率及佈線面積做 改良設計。. 圖1.2 直接降頻接收機架構. §1-3 研究成果 如表 1.1 所列,為本論文完成之射頻電路設計,其中【電路 1】為低電壓壓控振盪 器(Ultra Low Voltage VCO) 架構設計, 【電路 2】為低電壓正交輸出壓控振盪器(Ultra Low Voltage Quadrature VCO) 架構設計, 【電路 3】低功率雙頻段正交輸出壓控振盪器(Low power Dual Band QVCO)架構設計, 【電路 4】為低電壓鎖相迴路( Low Voltage PLL) 架 構設計,而各電路之詳細設計內容,分別會在第三、四章中被敘述。 表 1.1 本論文完成之射頻電路設計 頻率. 面積. (GHz). (mm2). 應用於超寬頻 0.6V 低電壓之 壓控振盪器. 7.92. 0.68x0.53. 2. 應用於超寬頻之低電壓低功率 四相位壓控振盪器. 7.92. 1.03 x 0.636. 3. 低功率之雙頻帶四相位壓控振 盪器. 2.4/5.2. 1.10 x 0.89. 4. 應用於超寬頻系統之低電壓鎖 相迴路. 5.016. 1.360 x 1.125. 電路編號. 電路名稱. 1. 3.

(15) §1-4 章節概述 本論文共分五個章節,第一章:敘述論文之研究動機與成果。第二章:針對振盪器 的相位雜訊、工作原理和低電壓壓控振盪器的考量加以討論。第三章:介紹所設計的低 電壓壓控振盪器【電路 1】【電路 2】【電路 3】。第四章:介紹鎖相迴路工作原理以及所 設計應用於超寬頻 MBOA 系統的低電壓鎖相迴路【電路 4】,第五章:本章為結論,說 明本論文之研究成果。. 4.

(16) 第二章. 相位雜訊及壓控振盪器 在近代數位通訊中大量使用相位調變的技術,如 QPSK,QAM 調制等方式,使得 對整個通訊系統對雜訊要求日益趨緊,尤其在相位雜訊的要求上,因不佳的相位雜訊會 劣化星座佈置圖導致誤碼率升高,使得接收品質不良,而在多頻道接取的個人行動通訊 系統中頻道的間隔非常緊密,本地訊號源必需避免過大的相位雜訊引入旁波信號而干擾 主信號,造成接收靈敏度不良,因此相位雜訊對近代數位通訊系統而言是一個重要的參 數。 壓控振盪器是鎖相迴路中最重要的電路部份,在積體電路上的應用,主要有環形振 盪器(Ring Oscillator )及 LC 調諧振盪器(LC tank Oscillator),在環形振盪器方面,因不需 要電感被動元件,採用主動放大電路來組成,可節省面積,且容易整合和設計,且輸出 的訊號振幅較大(full swing)及可以有多相位的輸出等優點,但因使用較多主動電路, 所以相位雜訊較差,而 LC 調諧壓控振盪器是在高頻段的相位雜訊和低耗能表現上皆優 於環形振盪器,雖然 LC 調諧壓控振盪器有較佔面積以及較小的調整範圍等缺點,但基 於使用在固定頻率的頻段以及要求低的相位雜訊和耗能的考量下,採取 LC 調諧壓控振 盪器來做為應用於低電壓之壓控振盪器的設計。. §2-1 相位雜訊的定義 一個理想的振盪器輸出頻譜如圖2.1(a)所示,通常在時域軸以一個完美的弦波來表 示:. V ( t ) = V o sin( ω 0 t ). (2-1). 其中V0為輸出振幅,ω0為振盪中心頻率,由於振盪器對於周遭環境及雜訊相當敏 感,當溫度,電源電壓變化或雜訊存在將使振盪器的輸出訊號在振幅、相位及頻率上發 生改變,即形成所謂的 AM、PM 及 FM 雜訊。通常振盪器輸出振幅被溫度,電源電 壓變化及雜訊影響產生的改變量不大且會在極短瞬間趨於穩度或被非線性的主動元件 特性所限制著,因此 AM 雜訊影響較小可忽略,至於輸出相位的變動( PM及FM雜訊), 即形成相位雜訊來源。而實際的振盪輸出信號在頻譜上的功率分佈,如圖2.1(b)所示, 還包含了振盪頻率的諧波,寄生雜波(spurious tone)等,實際振盪輸出信號瞬間的輸. 5.

(17) 出如下式所示:. V ( t ) = V o [1 + A (t )] sin( ω 0 t + φ ( t )) + 高階諧波. (2-2). 其中A(t)及ψ(t)分別表示為信號振幅及相位的誤差,且分別在振盪時對頻譜造成兩 種相位變化,前項涉及到寄生雜波(spurious tone)或信號的變化,而後者有隨機相位 及頻率的誤差造成所謂的相位雜訊[2]。. 圖2.1振盪器輸出訊號 (a)理想頻譜圖 (b)實際頻譜圖. 在振盪器中常見的雜訊來源為本質雜訊來源(internal noise source)如熱雜訊(thermal noise)和主動元件雜訊來源(active device noise source)來源如散射雜訊(shot noise)、閃 爍雜訊(flicker noise)等,通常振盪器相位雜訊是由本質雜訊來源所引起的,而寄生雜波 (spurious tone)大多由外部的雜訊所引起,如外加控制電壓的雜訊,電源供應的雜訊 或電流源耦合訊號等等。因此我們將討論電路內部的雜訊所形成的相位雜訊,且將相位 雜訊定義為 L(Δf ) ,並簡略說明相位雜訊的定義:振盪器在中心頻率偏移固定頻率下,. 1Hz頻寬的總雜訊功率對應中心頻率功率的比值,如圖2.2所示,可看到訊號頻譜的形狀 在中心頻率周圍形成〝裙帶〞(skin)狀。相位雜訊亦可看為頻率的瞬間穩定度,因有 相位雜訊的存在,造成在中心頻率兩邊有連續的調制邊帶產生,形成頻譜的延展,而相 位雜訊定義式如下[3]:. L(Δf ) = 10 log(. f O + Δf在1Hz頻寬內之總雜訊功率 ) 中心頻率之總功率. (2-3). 其中 L(Δf) 為在單波帶( sing sideband )雜訊頻譜密度正規化下的相位雜訊,單位為. dBc/Hz,而f0 為振盪器的中心頻率。. 6.

(18) 圖2.2 相位雜訊定義. §2-2 相位雜訊對通訊系統的影響 在無線通訊系統中通常都須要維持較高的SNR (信號雜訊比),而本地振盪訊號源之 相位雜訊的好壞會影響到接收訊號或是發射訊號的品質,進而降低SNR的數值。考慮一 接收系統如圖2.3所示,本地振盪器為真實振盪器包含非理想的相位雜訊如圖2.3 (a),假 如無線收發機除了欲接收的訊號(wanted signal)外,也可能同時接收到鄰近頻帶的干擾訊. 圖2.3 相位雜訊在接收端的影響. 7.

(19) 號(unwanted signal) 如圖2.3(b)。假設其功率大於欲接收的訊號,兩個訊號經過本地振盪 器轉換後的重疊訊號頻譜如圖2.3(c)所示,此時鄰近頻帶干擾訊號將可能〝淹沒〞欲接 收的訊號,直接造成接收機靈敏度下降,造成SNR下降,故需要降低本地振盪器的相位 雜訊的設計來符合需求。因而在確認接收端的SNR後,振盪器的相位雜訊必須滿足下式. [3]:. L(Δf ) < 接收信號 (dBm)− 干擾信號 (dBm)− 10 log10 (通道頻寬) − SNR. (2-4). 其中減去 10log(通道頻寬),是因為相位雜訊的單位為 Hz,而在接收時頻道寬等於中頻 頻寬。. §2-3 振盪器的相位雜訊 雜訊在不同的時間的有著不同的變化,因而振盪器的相位雜訊理論也區分為非時變 與時變的理論模型,以下分別來討論。. (1) 非時變模型(time invariant) [3][4] 以下以非時變概念來分析相位雜訊的形成原因,非時變指的是雜訊源不論任何時候 注入壓控振盪器所得到的相位雜訊都是相同的;或是說不論在任何輸出波形的時間點 上,雜訊造成壓控振盪器相位偏移的效果都是一樣的。因此不需要考慮雜訊是在壓控振 盪器輸出波形的那個時間點進入壓控振盪器電路。假設振盪器是由主動埠與諧振腔. (resonator)組成如圖2-4,而其諧振腔中等效並聯電阻的熱雜訊是唯一的雜訊來源,其可 以用一個電流源來模擬,所表示的電流源均方根密度為. in2 = 4 kTG L Δf. (2-5). 其中GL是諧振腔的並聯寄生電導,此電流源與諧振腔的阻抗相乘,就是雜訊的電壓。相 對於諧振腔的中心頻率ω0偏移一個很小的頻率Δω,RLC諧振腔的阻抗. 圖2.4 電感電容振盪器等效單端電路 8.

(20) 可以近似為:. Z (ω 0 + Δ ω ) ≈ − j. ω0 L 2( Δω / ω 0 ). (2-6). 而電感與品質因素的關係如下式:. QL =. L ω0 RL. (2-7). 1 1 G L 1 + j 2Q L ( Δ ω / ω 0 ). (2-8). 利用上式轉換式(2-6)為下式:. Z (ω 0 + Δ ω ) ≈. 為維持振盪,RLC諧振腔所造成的損耗需由主動元件提供給諧振腔的平均功率來補 償,因此主動元件就像是等效並聯負電導-Gm(Vo),其中諧振腔振幅決定負電導的值, 當在穩態時,必須滿足 Gm (Vo ) = G L ,而此時在電感電容振盪器等效單端電路的端點 阻抗可以被表示為:. Z ( Δω ) =. ω0 vout (ω 0 + Δ ω ) 1 =−j iin (ω 0 + Δ ω ) G L 2Q L Δ ω. (2-9). 由式(2-5)和式(2-9)可以得到雜訊電壓均方根值的頻譜密度如下:. v n2 in2 ω0 1 2 )2 = Z ( Δ ω ) = 4 kTG L ( Δf Δf G L 2Q L Δ ω = 4 kTR L (. ω0. 2Q L Δ ω. (2-10). )2. 由上式可以看出,諧振腔本身的濾波作用使得偏移頻率與雜訊有著反比平方的關 係,隨著偏移頻率越接近ω0,雜訊電壓均方根值的頻譜密度也越趨近無限大,而雜訊電 壓均方根值與阻抗也呈正比,式中也說明較高的品質因素(Quality factor, Q值)也可抑制 熱雜訊。接著針對雜訊與載波信號作比較,將均方根雜訊電壓密度對均方根載波信號進 行正規化處理,以dB值表示,如下式:. ⎡v 2 L{Δ ω } = 10 × log ⎢ noise 2 ⎢⎣ v sig. 2 ⎡1 2 ⎤ ⎢ 2 Z ( Δ ω ) × in / Δ f ⎥ = 10 × log ⎢ 1 2 ⎥⎦ ⎢ Vo ⎣ 2. ⎡ 2 kT ⎤ ω0 ( )2 ⎥ = 10 × log ⎢ ⎣ Ps 2Q L Δ ω ⎦ 9. ⎤ ⎥ ⎥ ⎥ ⎦. (2-11).

(21) 此方程式說明距離振盪頻率Δω處,單位頻率內的單邊帶(single sideband)雜訊對訊號 比,也就是相位雜訊,其中 Ps 為振盪器輸出訊號功率,所以從以上的公式可看出相位雜 訊與頻率的偏移量呈現反比,因諧振腔的阻值呈現1/QΔω關係來減少,而雜訊電壓均方 根值與阻抗成正比。若要得到較好的相位雜訊表現則必需要增加訊號功率與諧振腔的品 質因素。增加訊號功率也意謂增加振盪器等效模型中主動埠的功率,使主動埠的雜訊指 數下降,如此可達到增加抑制相位雜訊的能力,由雜訊電流轉換為相位雜訊邊帶的頻譜 示意圖,如圖2.5所示。. 圖2.5 雜訊電流轉換為相位雜訊邊帶的頻譜示意圖 由式子(2-11)可對相位雜訊得到一概略性的了解,但是式子所描述的頻譜與 壓控振 盪器實際量測到的有很大的差異。因實際上除了熱雜訊外還有其它雜訊來源,壓控振盪 器頻譜如圖2.6所示,在相當大的偏移頻率(frequency offset)壓控振盪器頻譜會趨於水平 而非如式子(2-11)預測持續以二次方倒數下降,而在極小的偏移頻率時,壓控振盪器頻 譜是以三次方倒數下降而不是如式子(2-11)所預測。 10.

(22) L(Δw). 1/ f. 3. 1/ f Δw1 / f 3. 2. ⎡ 1 FkT ⎤ 10 log ⎢ ⎥ ⎣ 2 Ps ⎦. log(Δ w ). w0 / 2Q. 圖2.6 Lesson’s 相位雜訊模型 因此在相位雜訊的描述上必需要修正為. ⎡ 2 FKT L( Δω ) = 10 log⎢ ⎢⎣ PS. ⎧⎪ ⎛ ω ⎞ 2 ⎫⎪⎛ ω1 / f 3 0 ⎟⎟ ⎬⎜1 + ⎨1 + ⎜⎜ Δω ⎪⎩ ⎝ 2QΔω ⎠ ⎪⎭⎜⎝. ⎞⎤ ⎟⎥ ⎟⎥ ⎠⎦. (2-12). 上式即所謂的 Leeson’s 模型,它是一個由量測壓控振盪器頻譜後修正曲線的相位雜訊 模型,用來描述其輸出頻譜。此模型中有些參數如必需要經過量測才能得到,如F是元 件雜訊附帶的指數,或說是個單純的雜訊指數,用來計算在1 /( Δ ω ) 2 區域增加的雜訊, 不同的振盪器有不同的值,括號中加1用來表示雜訊的最低值,末項表示 1/(Δω )3 在極小 的偏移頻率時的關係, 2 經由上式可以觀察到要降低相位雜訊,可以增加信號功率Ps,且Ps ∝ V peak ,在實際. 的振盪器設計中,Vpeak通常被操作電壓所限制住,另外在諧振腔中提高品質因素,或提 升L/Rs的比率,亦能使相位雜訊降低。在非時變分析中壓控振盪器頻譜成水平的轉角頻 ωo 率(corner frequency)其值並不一定是 2Q 。再者在非時變分析中無法對壓控振盪器頻譜 有 1/(Δω )3 範圍提出合理的解釋,雖然我們都知道是閃爍雜訊( 1/f noise)造成的,但閃爍 雜訊是如何升頻至中心頻率的附近? 以下將介紹另一種分析方式(時變分析),此分析可 以解釋 1/(Δω )3 的成因,並應用其結論,提供除了增加諧振腔品質因素及訊號大小外的 其它方式,用於壓控振盪器設計來降低相位雜訊。. (2) 時變模型(time variant)[3][5][6] 任何的實際的振盪器都是非線性時變系統,因而非時變模型假設雜訊在任何時候被 11.

(23) 產生並影響壓控振盪器輸出得到的結果都是一樣的在事實並不是如此。考慮如圖2.7 所 示的理想LC諧振電路。. i(t) δ (t −τ ). i(t). L. C. t 圖2.7 電流脈衝注入 LC 振盪器 假設振盪器處於諧振的穩態,瞬間的脈衝注入可視為頻率無窮大的輸入信號,在此 頻率下電容的阻抗為零而電感的阻抗為無窮大,因而脈衝電流只注入電容而不影響電感 中的電流,形成電容兩端的電壓發生改變,如下式:. ΔV =. ΔQ Ctotal. (2-13). 其中△Q為電流脈衝注入的電荷總量,Ctotal為電路內的總電容,而振盪器的輸出可 表示為. Vout (t ) = A(t ) cos[ϖ 0 t + φ (t )]. (2-14). 其中A(t)及Φ(t)都是時間的函數,分別表示為振幅與相位,對上式做微分處理. ∂Vout ∂A(t ) ∂φ (t ) cos[ϖ 0 t + φ (t )] + A(t ) sin[ϖ 0 t + φ (t )](ϖ 0 + ) = ∂t ∂t ∂t. (2-15). ΔV = ΔA cos[ϖ 0 t + φ (t )] + A(t ) sin[ϖ 0 t + φ (t )](ϖ 0 + Δφ ). (2-16). 即. 當ϖ 0τ + φ (τ ) = 2nπ 時,即在振盪波形的波峰時,後一項為零可得 當ϖ 0τ + φ (τ ) =. π 2. ΔV = ΔA. (2-17). ± 2nπ 時,即在振盪波形的零交越(zero crossing),前一項為零可得 ΔV = ΔA(ϖ 0 + Δφ ). (2-18). 上式表達在振盪波形的波峰處所產生的擾動,僅影響輸出振幅大小,而不影響相位,在 零交越處所產生的擾動,僅影響輸出相位,因而改變瞬間振幅,但不影響振盪的最大振 12.

(24) 幅,如圖 2.8所示,一個脈衝(impulse)電流注入一個理想的LC 諧振電路,假設此系統 正振盪於某一頻率及固定的振幅。若脈衝注入時正好是訊號振幅最大的時候,此時電壓 振幅將瞬間被提升 ΔV = ΔQ / C ,但因為注入的脈衝正好疊在最大振幅處,此脈衝不會造 成訊號相位有任何的改變,如圖 2.8(a) 所示。反之,若脈衝注入時正好是訊號振幅為 零交越的時候,如圖2.8(b) 所示訊號的相位造成了改變,且相位改變量與注入脈衝大小 有關。. V out. ΔV t. τ (a ). V out. τ. ΔV. t. (b ) 圖2.8 脈衝注入造成振盪訊號的改變 因此對於一個振盪器而言雜訊造成的相位改變是與雜訊注入的時間有關,對於相位 雜訊的分析,顯然非時變模型是不足以完全地描述,而需採用時變的觀念。如圖2.7 所 示,當一個脈衝在時間τ時注入,訊號將產生相位改變,其相位改變的脈衝響應(impulse. response)可表示成. hφ (t ,τ ) =. Γ (ωoτ ) u (t − τ ) qmax. (2-19). 其中 u(t)為單位步階函數(unit step function), qmax 為 LC 振盪器最大儲存的電荷量。Γ ( x ) 稱為靈敏度函數(impulse sensitivity function ,ISF),它的週期為 2π,且與訊號頻率及 最大振幅無關,而與訊號波形有極大的關係。此函數表示一個振盪器對於一個脈衝在. ω oτ 注入的敏感度。一般來說 Γ ( x ) 是可以透過模擬的方式來獲得,如圖2.9所示為LC 振盪器與環形振盪器典型的脈衝響應函數曲線。. 13.

(25) Vout (t ). Vout (t ). Γ(ωot ). Γ(ωot ). 圖2.9 (a)LC振盪器與(b)環形振盪器典型的脈衝響應函數曲線. 若 ISF 已知則可算出相位經由脈衝注入的改變量為:. φ (t ) =. ∞. ∫. hφ (t ,τ )i (τ )dτ =. −∞. 1 qmax. t. ∫ Γ(ω τ )i(τ )dτ o. −∞. (2-20). 因為 ISF 為一週期函數所以可由傅立葉級數( Fourier series)展開. c0 ∞ + ∑ cn cos(nωoτ + θ n ) 2 n=1. Γ(ωoτ ) =. (2-21). 因為雜訊源的無關連( uncorrelated)特性,雜訊來源各不相關,因此雜訊間的相對相位也 是無關的,所以式子(2-21)中 θ n 可忽略以簡化之後的討論,將式子(2-21)代入式子(2-20) 得到. φ (t ) =. 1 ⎡ c0 ⎢ qmax ⎣ 2. t ∞ ⎤ ( ) ( ) cos( ) τ τ τ ω τ τ + i d c i n d ⎥ ∑ n o ∫ ∫ n=1 −∞ −∞ ⎦ t. (2-22). 其中 cn 為 ISF 的傅立葉係數(Fourier coefficient)。當 cn 為已知時,就可以使用上式計 算輸入電流雜訊所引起的相位偏移。 假設有一雜訊為弦波電流源形式其頻率在 mωo + Δω ,其中m為一常數,則此電流可 表示成. i(t ) = I m cos [ (mωo + Δω )t ]. 14. (2-23).

(26) 若 ω0 >> Δω ,將式子(2-23)代入式子(2-22)則可得到. φ (t ) =. t ∞ 1 ⎡ c0 t ⎤ (2-24) [ ] + + Δ i ( τ ) d τ c { I cos ( m ω ω ) t } cos( n ω τ ) d τ ∑ ∫ ∫ 0 0 n m ⎥⎦ qmax ⎢⎣ 2 − ∞ n =1 − ∞. 忽略n≠m的項後簡化為. φ (t ) ≈. I m cm sin(Δωt ) 2qmax Δω. (2-25). 將此式代入(2-26),可得輸出信號. Vout (t ) = cos [ωot + φ (t )]. (2-26). I m cm 假設 2 q Δω < 1,則式子(2-24)的雜訊將造成輸出訊號頻譜在 ωo 附近有二個等功 max 率的訊號其頻率與中心頻差 Δω ,大小各為. ⎛ I c ⎞ PSBC (Δω ) ≈ 10 log ⎜ m m ⎟ ⎝ 4qmax Δω ⎠. 2. (2-27). in 2 若電流雜訊源為白色高斯雜訊,功率頻譜密度為 Δf ,則其在振盪頻率附近造成壓. 控振盪器輸出頻譜展開的單頻帶雜訊功率除以訊號功率比為. ⎛ in 2 ∞ 2 ⎞ cm ⎟ ⎜ ∑ f Δ m = 0 ⎟ CSSB ( Δω ) ≈ 10 log ⎜ 2 ⎜ 4qmax Δω 2 ⎟ ⎟⎟ ⎜⎜ ⎝ ⎠. (2-28). 由 Parseval’s 關係式可得 ∞. ∑c m =0. 2 m. =. 1. π. 2. 2π. ∫ Γ( x). dx = 2Γ 2 rms. 0. (2-29). 因此白色高斯雜訊造成的相位雜訊為. ⎛ in 2 2 ⎞ Γ rms ⎟ ⎜ Δf ⎜ ⎟ L(Δω ) ≈ 10 log ⎜ 2q 2 max Δω 2 ⎟ ⎜⎜ ⎟⎟ ⎝ ⎠ 15. (2-30).

(27) 又 qmax = CVmax , Vmax 為壓控振盪器最大振幅;. in 2 4kT = Δf R. 。代入式子(2-30)可得到. ⎛ 4kT 2 ⎛ ω ⎞ 2 ⎞ Γ rms ⎜ o ⎟ ⎟ L (Δω ) ≈ 10 log ⎜ ⎜ Ps ⎝ QΔω ⎠ ⎟⎠ ⎝. (2-31). 上式與式子(2-11)只差一個常數項,但在非時變分析時式子(2-11)中的F通常為一個 在壓控振盪器頻譜量測以後得到的經驗參數,而在式子(2-31)中卻可將由尋找 ISF 後計 算而得,且由式子(2-31)也可知道除了增加訊號大小及增加諧振腔品質因素外,也可以 經由改變波形,即降低 ISF 的 RMS值 ( Γ rms ) 來抑制白色雜訊造成的相位雜訊。 若輸入壓控振盪器的雜訊為閃爍雜訊(1/f noise),其功率頻譜密度為:. i 2 n,1/ f = in 2. ω1/ f Δω. (2-32). 其中 ω1/ f 為閃爍雜訊的1/f 轉角頻率(corner frequency)。將式子(2-32)代入式子(2-30)可以 得到閃爍雜訊所引起的相位雜訊。. ⎛ in 2 2 ⎞ c0 ⎜ ⎟ ω f Δ f 1/ ⎟ L(Δω ) ≈ 10 log ⎜ 2 ⋅ ⎜ 8qmax Δω 2 Δω ⎟ ⎜⎜ ⎟⎟ ⎝ ⎠. (2-33). 相位雜訊 1/(Δω )3、1/(Δω )2 範圍之間的轉角頻率可經由比較式子(2-30)及式子(2-33)得到:. Δω1/ f 3 = ω1/ f. c02 ⋅ 2 ≈ ω1/ f 4Γ rms. ⎛c ⎞ ⋅⎜ 0 ⎟ ⎝ c1 ⎠. 2. (2-34). 因此,若要減少 1/(Δω)3 範圍的相位雜訊及降低,則必需要降低 c0 ,也就是 ISF的 DC 成份。要降低 c0 必須使得壓控振盪器的 Γ ( x ) 函數輸出波形愈對稱愈好,採取透過電路 結構的設計或元件特性的選擇來達到此要求,而應用在CMOS製程中,此規則對高閃爍 雜訊的元件相對地重要,因為經由壓控振盪器設計時注意訊號波形則可抑制元件的閃爍 雜訊造成相位雜訊表現嚴重惡化。 綜合上述,白色雜訊及閃爍雜訊以電流源的形式注入壓控振盪器,造成壓控振盪器的 相位產生變化,而相位變化的大小與雜訊大小及訊號波形有關。雜訊造成的相位變化經. 16.

(28) 由相位調變(phase modulation)在壓控振盪器輸出訊號頻譜的週圍展開成裙帶狀相位雜 訊,相位雜訊形成的示意圖如圖2.10 所示。 在時變模型分析中,解釋了相位雜訊 1/(Δω )3、1/(Δω )2 範圍形成的原因並可對相位雜 訊做一精確的預測。對於壓控振盪器中任何一個雜訊源都可以依它的雜訊等效模型及訊 號波形對應此雜訊源的 ISF 來求出相位雜訊。要找出 ISF 可以將雜訊源以一個脈衝訊 號代替,並找出壓控振盪器對此脈衝訊號的脈衝響應即是壓控振盪器對應此雜訊源的. ISF。但有時壓控振盪器的雜訊來源很多或是雜訊模型不完整,所以利用ISF分析相位雜 訊將變得複雜。. 圖2.10 電流雜訊對相位雜訊的貢獻成分. 時變模型除了比非時變模型更準確的來預測相位雜訊外,更指引設計者除了增加壓 控振盪器的諧振腔的品質因素及訊號大小(非時變模型的結論),或採用閃爍雜訊較小的. PMOS元件外,波形也是一個相當重要的考量,尤其是閃爍雜訊的抑制,壓控振盪器的 Γ ( x ) 函數輸出波形愈對稱愈好,特別是對於高閃爍雜訊的 CMOS 元件。. 17.

(29) §2-4 基礎壓控振盪器理論及設計方法 壓控振盪器可視為一種能量轉換元件,如圖 2-11 ,輸入為 Vtune 而產生週期性的輸出. Vout(t),能將直流功率轉換為交流功率[7]。. 圖2.11 基本壓控振盪器. 當接上電源後,產生單端或對稱的週期信號Vout(t)輸出為. Vout (t ) = Vo sin(ωc t + ϕ ). (2-35). 其中φ為相位,Vo為振幅,負載角頻率則定義為:. ϖ c (Vtune ) = 2πf c (Vtune ). (2-36). 由上式可看出調整控制電壓Vtune即可輸出需要頻率。理想輸出的波形和頻譜如圖2.12所 示:. 圖2.12 基本壓控振盪器理想輸出的波形和頻譜. §2-4-1 重要規格參數[2] [6] [7] [8] 在壓控振盪器電路設計上,一般考量的重要特性為:相位雜訊、輸出功率、頻率調 整範圍、壓控振盪器增益(VCO Gain)、推頻 ( Pushing ) 、負載拉頻 ( Load Pulling )、 熱穩定性(thermal stability)、FOM (Figure of Merit )等等,接著分別來探討。 1. 相位雜訊 理想壓控振盪器的輸出頻譜應該為單一脈衝型式如圖2.12所示, 因為元件的非 線性與電路所引入雜訊的影響,實際上輸出頻譜如圖2.13所示。雜訊所引入的額外裙. 18.

(30) 帶(skirts),表示有存在著相位雜訊,亦可以看成訊號在時域上週期或是零交越點不 固定所造成。裙帶高度越高表示相位雜訊越差,一個週期性的載波訊號可以表示為:. S t = Ac (t ) cos(ωc t + θ (t )). (2-37). Ac (t ) 表示雜訊源對於振幅的影響,即所謂AM雜訊,而 θ (t ) 表示相位和頻率改變所 形成雜訊源所造成的相位變化,即所謂PM及FM雜訊,一般來說振幅雜訊對於載波 信號的影響較小,可將 Ac (t ) 以常數看待,接著說明相位雜訊對頻譜的影響,首先假 設 θ (t ) 為隨時間變化的單頻正弦波 θ (t ) = θ m sin(ω m t ),θ m 為最大偏移角,ωm 為調變頻 率。帶入(2-37)式. S t = A c cos (ω c t + θ m sin (ω m t )) = Ac {cos(ω c t ) × cos[θ m sin (ω m t )] − sin (ω c t ) × sin[θ m sin (ω m t )]}. (2-38). 假設 θ m <<1,上式可改寫為. θ θ ⎧ ⎫ S t = Ac ⎨cos(ω c t ) − m cos(ω c + ω m )t + m cos(ω c − ω m )t ⎬ 2 2 ⎩ ⎭. (2-39). 由此式可得知,在載波中心頻率信號兩旁距離 ωm 會有一大小相等而相位相反的兩個 旁波,即表示在與載波中心頻率信號相距頻偏量 ωm ( offset ),其雜訊電壓強度. Vn = θ m A / 2 ,對信號 Ac 來做比較,如下式: Vn θ m = Ac 2. (2-40). 由此式可以得知利用頻譜振幅 Ac 的相對比值可求得相位偏移 θ m ,實際上 θ (t ) 為隨機 產生,包含各種頻率成分,因而會在頻譜上形成旁波帶。. 圖2.13 振盪器輸出訊號頻譜圖 19.

(31) 相位雜訊的好壞會影響到整體接收訊號的品質,如圖2.14 所示。當一個很強的 鄰進波道干擾和一個很弱的接收訊號同時出現時,多餘的相位雜訊會和很強的干擾 交互調變到中頻,使得原本很弱的中頻訊號可能因此被干擾。故降低相位雜訊為設 計振盪器者的重要考量之一。. 圖2.14 相位雜訊在接收端的影響 2. 輸出功率 振盪器的操作模式是在大信號模式進行的,因而會有諧波失真,此乃操作在非 線性區所致,要減少失真就需減少非線性操作進行,大致有元件選取,直流偏壓設 計,諧振電路設計等方向改善,其中輸出功率的規劃牽引著CMOS元件與直流偏壓 的設計,其目標是以提升振盪器大信號操作能力為主,因此在CMOS電晶體元件設 計上儘量操作在合適的P1dB下與偏壓在線性的工作區,直流偏壓與諧振電路則以控制 輸出功率和提供適當負阻用以減少諧波失真。而此輸出功率最大不會超過其電晶體 在大訊號分析時所得的輸出功率。因此可在選擇振盪器主動元件的同時,利用此主 動元件的已知參數,來規劃振盪器的輸出功率。 3. 頻率調整範圍 頻率調整範圍為振盪器設計所需考量的規格之一,而其往往都是利用一些可調 元件來實現,如:二極體變容器(Diode Varactor)、電晶體變容器(MOS Varactor)…等, 除了設計具有頻率調整功能外,其餘設計則應避免額外因素影響振盪器的輸出頻 率。壓控振盪器的頻率調整範圍定義為. 頻率調整範圍 =. f max − f min ( f max + f min ) / 2. 或者採用壓控振盪器所能調整的頻寬範圍來表示。. 20. (2-41).

(32) 4. 壓控振盪器的增益 壓控振盪器的增益(VCO Gain)一般以Kvco來表示,其與調整範圍成反比,定 義為. K VCO =. df c dVtune. (2-42). 5. 推頻效應 一般振盪器造成頻率變動的主要原因可分為控制訊號部分與輸出負載部分。 就控制訊號部分而言,當主動元件所使用的控制訊號發生變動時,電晶體的偏壓也 會改變,因為電晶體的 S參數與 Γin 會隨直流偏壓變動,而造成振盪器輸出頻率產 生變化,此情況又稱推頻效應(Pushing Effect)。可表示為:. pushing =. dfc dVdd. (2-43). 避免推頻效應的發生,可使用高品質因數的諧振腔以減低推頻效應對振盪頻率 的影響,因為較高的品質因數可以使共振電路與主動元件接面電容的變化有較好的 隔離。另外,亦可利用穩定性較高的偏壓電路,如:能隙型(Band Gap)偏壓電路,使 主動元件所需的偏壓訊號,不因訊號產生器本身的不穩定,造成推頻效應的發生。 6. 負載拉頻效應 振盪器輸出頻率變動的另一因素為輸出的負載造成。當輸出負載變動時,其等 效的阻抗也發生變化,此時電晶體從輸入端看入的阻抗已不再符合當初設計的數 值,進而造成整個輸出頻率變動,此情況又稱負載拉頻效應(Load Pulling Effect),可 表示為:. pulling =. Δfc Δload. (2- 44). 若欲避免負載拉頻效應,可在電路輸出級與輸出負載間,插入緩衝器(Buffer), 以改善負載與電晶體之間的隔離度,且增加此緩衝器亦可提升振盪器輸出功率位準。 7. 熱穩定性 振盪器元件會因溫度改變而產生特性變化,這將造成振盪頻率與輸出功率發生 變化,甚至停止振盪或寄生振盪,因此考量上以簡化振盪電路的結構及電源電路加. 21.

(33) 上適當的濾波電路處理來改善,若將主動元件的偏壓電路和被動元件的諧振電路, 設計成具有溫度補償效應的功能,便可改善電路特性受到溫度影響的問題[6]。 8. 頻率漂移 振盪器在頻率變動時,需經過一段時間才會達到穩定的頻率輸出,等電路達到 穩定後,實際的輸出振盪頻率會與預期的振盪頻率有一些差距,其稱為穩態的調整 後漂移(Long-Term Post Tuning Drift, Δf L ),如圖2.15 所示。通常造成調整後漂移發 生的主要原因,乃是變容器熱能損耗的變化所形成的,故藉由選擇熱消散快速的頻 率調整元件即可改善此現象的發生。. f1. Δf L. f2 t 圖2.15 頻率漂移示意圖 9. FOM 振盪器在不同的頻率、功率損耗及相位雜訊下較難比較其特性,因而有其量化 的參數FOM(Figure of Merit)來做比較,其定義為. ⎛ f ⎞ ⎛ p ⎞ FOM = L( f m ) − 20 log⎜⎜ 0 ⎟⎟ + 10 log⎜ diss ⎟ ⎝ 1mW ⎠ ⎝ fm ⎠. (2-45). 其中L(fm)為單邊帶頻譜的中心頻率fo 偏移頻率fm所得到的相位雜訊,Pdiss為功率損 耗。由上式可觀察出相位雜訊的影響最大,其次為取對數的中心頻率和偏移頻率之 比值,而在式子中並未將頻率調整範圍和輸出的型態納入計算。. §2-4-2 CMOS壓控振盪器架構 目前在CMOS RFIC電路設計振盪器的方法主要有兩種型式:第一種為LC諧振(LC. tank)振盪器及另一種為環形振盪器(ring oscillator)。前者利用被動元件組成的諧振腔來 產生頻率,有較低的相位雜訊,但其可調頻率範圍較小;後者採主動元件設計,有較寬 的可調頻率範圍且可產生多相位的功能,不過有較高的相位雜訊。其設計原理的方式約 22.

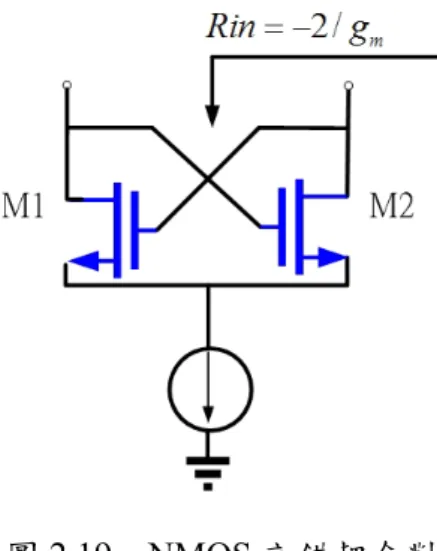

(34) 略可分為符合巴克豪森準則(Barkhausen criterion)的回授觀點以及應用負電阻的觀點。 以下將簡介此兩種振盪器的工作原理[6][9][10][11]。. 1.. LC 調諧振盪器 此振盪器常使用負電阻(-Rb)的概念來消除 LC 諧振腔的寄生電阻(Ra),如圖 2.16 所示,而 LC 諧振腔(包含寄生電阻)可由串並聯轉換圖 2.17 等效成圖 2.18 之簡易並 聯型式。. 圖 2.16 使用負阻消除 LC 諧振腔的寄生電阻示意圖. 圖 2.17 串並聯轉換. L. R. C. 圖 2.18 等效簡易並聯模型. 負電阻的產生是利用電晶體交錯耦合對(cross-coupled pair)產生回授,使得輸入阻抗 為 Rin = − 2 g ,用以補償諧振腔的損耗,當 Rin 小於或相等諧振腔的損耗時,就能產 m. 生振盪,圖 2.19 即為常使用的 NMOS 交錯耦合對。. 23.

(35) 圖 2.19 NMOS 交錯耦合對 圖 2.20 為互補式交錯耦合對(complementary cross-coupled pair)互,上半部二個電 晶體,將振盪器與供應電壓隔離降低推頻效應,可使得輸出振盪頻率更對稱,增加 負電阻阻抗和輸出電壓有接地電位到操作電壓的擺幅,避免了下半部二個電晶體的 汲極接面電容會隨著供應電壓變化的缺點,且具有較大的轉導,使得電晶體較快速 的切換,輸出電壓波形的上升時間(rise-time)及下降時間(fall-time)也較對稱,由於輸 出波形愈對稱, Δω1/ f 愈小,因此有較低的相位雜訊。 3. 圖 2.20 互補式交錯耦合對. 2. 環型振盪器 此振盪器工作原理如圖2.21 所示,利用奇數組反相器串接回授環路造成振盪, 振盪週期由總時間延遲來決定。有奇數個反相器串接,振盪頻率為:. 24. f0 =. 1 2 NTd ,因.

(36) 此改變單級延遲時間 Td 即可改變振盪頻率,進而達成電壓控制振盪頻率的功能。環 型振盪器不需要被動元件電感,因而可節省晶片面積並有較寬的調整範圍,且容易 與鎖相迴路(PLL)電路整合。其缺點在於主動元件使用量較多,因此相位雜訊較大。 另外,若使用N為偶數階的差動電路架構,可藉由在最後一級配置一個差動組態交 叉反接來反轉使用偶數組態,如圖2.22 所示,當電路動作時其四極環路為符合巴克 毫森準則,每個輸出端會形成正交的波形輸出。. 圖2.21 單端式環型振盪器示意圖. 圖2.22 四級差動式環型振盪器示意圖. §2-5 正交輸出的方法 在現今數位通信應用中,傳輸接收信號在振幅及相位均含有調變訊息,因此需要配 合正交輸出的本地振盪信號來調制發射或分解接收含有I與Q訊息的信號,另外在鏡像拒 斥混波器的本地振盪器也需要有正交輸出的能力,因此設計有正交輸出的壓控振盪器, 以應用在現代數位通信射頻晶體中是迫切需要的。在射頻積體電路中,常用來產生四相 位訊號的方法有四種:一是數位除頻器,二是RC-CR或多相位濾波器,三是雙交叉耦合. LC振盪器,四是使用四級環型振盪器,其中第四種在上述已有初步的討論,底下將介紹 前三種產生正交的方法[6][11]。. 25.

數據

LC p10≈ϖ (2-49) 為了確保振盪能夠產生,負電導 G](https://thumb-ap.123doks.com/thumbv2/9libinfo/8143803.166779/39.892.179.758.118.353/來決生諧振頻率時實部虛部值為零而諧振頻率可由此來確保振盪能夠.webp)

相關文件

Let T ⇤ be the temperature at which the GWs are produced from the cosmological phase transition. Without significant reheating, this temperature can be approximated by the

油壓開關之動作原理是(A)油壓 油壓與低壓之和 油壓與低 壓之差 高壓與低壓之差 低於設定值時,

This design the quadrature voltage-controlled oscillator and measure center frequency, output power, phase noise and output waveform, these four parameters. In four parameters

Abstract - A 0.18 μm CMOS low noise amplifier using RC- feedback topology is proposed with optimized matching, gain, noise, linearity and area for UWB applications.. Good

This can be used to guide small and medium construction industry to setup occupational safety and health management.. The checklists can be used to build and evaluate

In the second phase, the optimization design of the dot pattern of the light guide plate can be launched to categorize the light guide plate into 31 areas and used the

According to frequency response, filters can be divided into: (1) low-pass filter, (2) high-pass filter, (3) band-pass filter and band-stop filter.. This paper only chooses

The scenarios fuzzy inference system is developed for effectively manage all the low-level sensors information and inductive high-level context scenarios based