國 立 交 通 大 學

電信工程研究所

碩 士 論 文

應用於 24 GHz 連續調頻雷達之

低功耗壓控振盪器與

低閃爍雜訊次諧波混頻器

Low Power VCO and Low Flicker Noise

Sub-Harmonic Mixer

for 24GHz FMCW Radar Applications

研究生:林郁凱

(Yu-Kai Lin)

指導教授:鍾世忠 教授

(Dr. Shyh-Jong Chung)

應用於 24 GHz 連續調頻雷達之

低功耗壓控振盪器與低閃爍雜訊次諧波混頻器

Low Power VCO and Low Flicker Noise Sub-Harmonic Mixer

for 24GHz FMCW Radar Applications

研究生:林郁凱

Student: Yu-Kai Lin

指導教授:鍾世忠 教授

Advisor: Dr. Shyh-Jong Chung

國立交通大學

電信工程研究所

碩士論文

A Thesis

Submitted to Institute of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

For the Degree of

Master of Science

In

Communication Engineering

July 2010

Hsinchu, Taiwan, Republic of China

i

應用於 24 GHz 連續調頻雷達之

低功耗壓控振盪器與低閃爍雜訊次諧波混頻器

研究生:林郁凱

指導教授:鍾世忠 博士

國立交通大學電信工程研究所

碩士論文

中文摘要

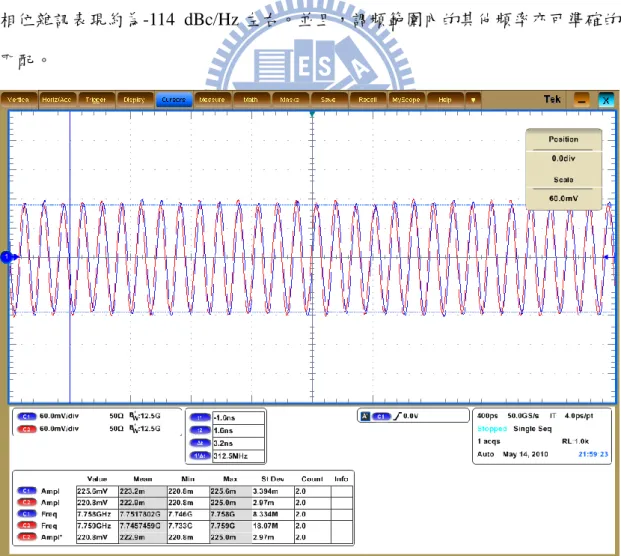

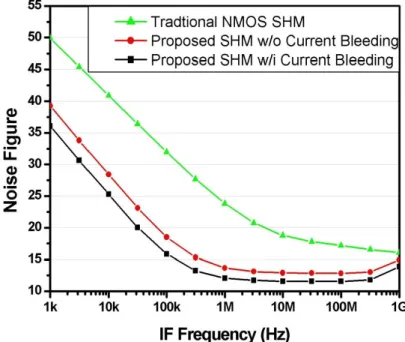

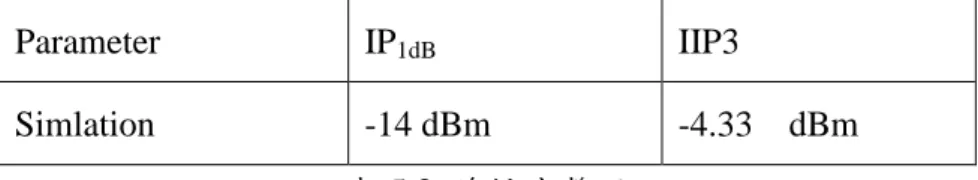

本論文提出兩個應用在 24 GHz 車用雷達系統收發機中的射頻前端電路: 8 GHz 新式壓控振盪器與 16 GHz 低閃爍雜訊次諧波混頻器,均以 TSMC 0.18 μm 1P6M CMOS 製程實現。 8 GHz 新式壓控振盪器,是以電流再利用為主要架構,透過串疊型式的交連 耦合對以及額外引入的可調式小尺寸交連耦合對,將差動兩端的電晶體各別給予 不同的偏壓電壓以及偏壓電流,藉此平衡差動兩端不匹配的電晶體轉導,改善原 本電流再利用架構之差動兩端輸出振幅不匹配的問題,可以將差動振幅精準匹配 至僅有 0.15%的誤差。其相位雜訊在 1 MHz 位移時為-114 dBc/Hz,輸出功率最 高為-2dBm,調頻範圍從 7.707 GHz 至 8.047 GHz,功耗為 2.995 mW,FoM 可達 -187.1 dBc/Hz。 16 GHz 低閃爍雜訊次諧波混頻器,以水平式次諧波混頻器為基礎電路架 構,採取大尺寸 PMOS 電晶體組成開關級,並利用折疊架構將轉導級與開關級 之偏壓電流分開設計,得以降低次諧波混頻器中開關級電晶體的直流電流大小, 最後再加入電流補償技術,使開關級直流電流可以進一步縮小,將閃爍雜訊轉角 頻率由原本 8 MHz 降低至 200 KHz。其轉換增益為 6.573 dB,IP1dB為-14 dBm, IIP3 為-4.08 dBm,白色雜訊指數為 12.7 dB,直流功耗 17.02 mW。ii

Low Power VCO and Low Flicker Noise Sub-Harmonic Mixer

for 24GHz FMCW Radar Applications

Student:Yu-Kai Lin Advisor:Dr. Shyh-Jonh Chung Institute of Communication Engineering

National Chaio Tung University

Abstract

The thesis proposes two RF front-end circuits: a 8GHz novel VCO and a 16 GHz low flicker noise sub-harmonic mixer (SHM). Both can apply to 24GHz FMCW radar applications and were fabricated with TSMC 0.18μm 1P6M process.

The proposed VCO adopts current-reused structure with a cascode cross-coupled pair and an additional tunable small size cross-coupled pair, giving different bias voltage and current to the differential MOSFETs, to reduce the inherently differential transconductance mismatch with current-reused VCO. This strategy can exactly balance the differential amplitude with only 0.15% error. The phase noise equals to -114 dBc/Hz at 1MHz offset while consuming 2.995 mW and achieving a tuning range from 7.707 to 8.047GHz.

The proposed SHM is based on SHM structure with PMOS switch stage, applying folded skill to separately design the DC current in switch stage form transconductance stage, to reduce the DC current in switch stage. In the end, this chip uses the current bleeding technique to more reduce the DC current. The flicker noise corner then could be restrained to 200 kHz from original 8 MHz. The Conversion Gain is 6.573 dB with IP1dB of -14 dBm, IIP3 of -4.08 dBm and White Noise Figure

iii

誌謝

首先,也是最重要的,我要感謝我的家人,不遺餘力地栽培我,亦毫無怨言。 在大學過後加上研究所,我已離家七年了,七年的外地生活讓我知道想念家鄉的 滋味,辛苦爸媽了!也非常感謝弟弟承軒替我分擔家務,爸媽不時的關心,妹妹 師岑的問候,外婆的慈藹,再再讓我能夠無所旁顧的努力於課業。 感謝鍾世忠博士,我的指導教授,在他嚴格的要求下,讓學生能夠了解老師 對學術的堅持,進而能以老師為模範來學習,使學生受益良多。進入老師麾下後, 電資 810 即是我在交通大學的家。佩宗淺淺微笑地引領,使我萌發出國念雙聯學 位的動機,沒有佩宗,我也許就沒有這麼精采的碩士第三年生活。專業方面,清 標不遺餘力地傾囊相授,使我順利下出兩顆晶片,更帶我量測出相當美好的晶片 量測結果。健談的峻義一直為我人生解惑,上至找工作,下至紓壓閒聊,峻義都 是我第一個想到的學長。實驗室伙伴,明緯,從一進實驗室的業界計畫,到論文 的研究主題,一起合作努力,謝謝他的耐心以及專業,是我研究上的榜樣。 在宜蘭的麻吉們,阿斗,阿博,宇倫,康馬,謝謝你們在我回鄉時的陪伴, 為我加油充電打氣,受用無窮。永遠不會忘記的還有不離不棄 2611 群,雲天、 韶麟、宗龍,我好懷念與你們大學四年的相處,那段時光總是鼓舞我激勵我,謝 謝你們帶給我的美好大學回憶。 另外感謝交通大學給我機會,讓我能夠到比立時魯汶大學念雙聯學位,我們 一起奮鬥的魯汶幫,博堯小客恕平水哥小米吃吃要加,感謝你們在異國生活對我 的照顧,每次的旅行每堂的授課,都留下我們八人的蹤跡。感謝我的指導學長, 皓名,嚴格且耐心的指正使我能夠完成第二次論文口詴。還要感謝親切的瑋智所 帶領的台灣魯汶同學會,以及 TSAL 幹部們:達叔、欣儀、宛稚等等,謝謝你們 對新生的照顧,就好像顧小孩一樣的體貼。 最後謹以此論文,獻給宜娟,一個最了解林郁凱這個小孩的人。 2011 年 7 月 26 日 郁凱,於新竹真摯感謝各位iv

目錄

中文摘要... i Abstract ... ii 誌謝... iii 目錄... iv 表目錄... vii 圖目錄... viii 第一章... 1 序論... 1 1.1 研究動機... 1 1.2 研究方法與成果... 2 1.3 章節概述... 3 第二章... 4 24 GHz 車用雷達系統接收機 ... 4 2.1 車用雷達系統... 4 2.2 車用雷達接收機文獻回顧... 6 2.3 新式 24 GHz 車用雷達接收機 ... 7 第三章... 10 射頻晶片設計基礎... 10 3.1 壓控振盪器... 10 3.1.1 壓控振盪器基本操作原理... 10 3.1.1.1 LC 共振腔振盪器 ... 11 3.1.1.2 環形振盪器... 14 3.1.1.3 注入鎖定式振盪器... 15 3.1.2 壓控振盪器參數介紹... 17 3.1.2.1 相位雜訊... 17 3.1.2.3 調頻範圍... 19 3.1.2.4 功率消耗... 20 3.1.3 相位雜訊模型... 21 3.1.3.1 非時變模型... 22 3.1.3.2 時變模型... 24 3.2 混頻器... 30 3.2.1 混頻器基本操作原理... 30 3.2.1.1 單平衡式吉伯特混頻器... 31 3.2.1.2 雙平衡式吉伯特混頻器... 32v 3.2.2 混頻器參數介紹... 34 3.2.2.1 轉換增益... 34 3.2.2.2 線性度... 35 3.2.2.3 隔離度... 36 第四章... 37 新式壓控振盪器設計... 37 4.1 新式壓控振盪器電路簡介... 37 4.2 電流再利用壓控振盪器... 38 4.3 振幅輸出不對稱之影響... 40 4.4 文獻回顧... 42 4.4.1 三頻器應用時振幅不對稱之錯誤累積... 42 4.4.2 源級退化電流再利用壓控振盪器... 43 4.5 差動振幅平衡設計... 44 4.6 低電壓操作設計... 45 4.6.1 轉導提升設計... 45 4.6.2 額外交連耦合對... 46 4.7 電路新穎性與全電路架構... 47 4.8 模擬與量測結果... 48 4.8.1 電路佈局與晶片照片... 48 4.8.2 振幅精準匹配... 49 4.8.3 低電壓操作模擬... 50 4.8.4 相位雜訊... 51 4.8.4.1 轉導提升的相位雜訊改善... 51 4.8.4.2 相位雜訊量測與模擬... 52 4.8.5 輸出功率... 53 4.8.6 調頻範圍... 53 4.8.7 直流功率消耗... 54 4.9 電流再利用壓控振盪器之比較... 55 第五章... 56 低閃爍雜訊次諧波混頻器之設計... 56 5.1 低閃爍雜訊次諧波混頻器電路簡介... 56 5.2 次諧波混頻器... 57 5.2.1 堆疊式次諧波混頻器... 57 5.2.2 並列式次諧波混頻器... 58 5.3 閃爍雜訊成因... 59 5.4 文獻回顧... 59 5.4.1 閃爍雜訊與混頻器... 59 5.4.2 閃爍雜訊轉角頻率 5 MHz 的接收機 ... 61

vi 5.4.3 靜態電流補償... 62 5.4.4 動態電流補償... 63 5.5 低閃爍雜訊次諧波混頻器設計... 64 5.5.1 電晶體與電路架構之選擇... 64 5.5.2 提升轉換增益... 65 5.5.3 電流補償... 66 5.6 電路新穎性與全電路架構... 67 5.7 模擬數據... 68 5.7.1 電路佈局... 68 5.7.2 雜訊指數與閃爍雜訊轉角頻率... 69 5.7.3 轉換增益... 70 5.7.4 返回損耗... 70 5.7.5 隔離度... 71 5.7.6 線性度... 71 5.7.7 直流功率損耗... 72 5.8 次諧波混頻器之比較... 73 第六章... 74 壓控振盪器與混頻器整合設計... 74 6.1 壓控振盪器與混頻器整合設計... 74 6.2 模擬數據... 76 第七章... 79 結論... 79 參考文獻... 81

vii

表目錄

表 1.1 本論文之研究成果... 2 表 4.1 理想移相器輸入與輸出整理... 41 表 4.2 相移器不匹配輸入與誤差輸出整理... 41 表 4.3 低系統電壓下各電路起振電壓及相位雜訊(dBc/Hz @1MHz offset) ... 50 表 4.4 相位雜訊與消耗功率整理... 51 表 4.5 近年國際期刊電流再利用壓控振盪器效能比較表... 55 表 5.1 100 KHz 以及 1MHz 時的雜訊指數整理 ... 69 表 5.2 各端隔離度整理... 71 表 5.3 線性度整理... 72 表 5.4 直流功率損耗... 72 表 5.4 混頻器效能比較表... 73 表 6.1 新式振盪器電路特性... 75 表 6.2 低閃爍雜訊次諧波混頻器電路特性... 75 表 6.3 壓控振盪器與次諧波混頻器整合設計之電路特性比較... 78viii

圖目錄

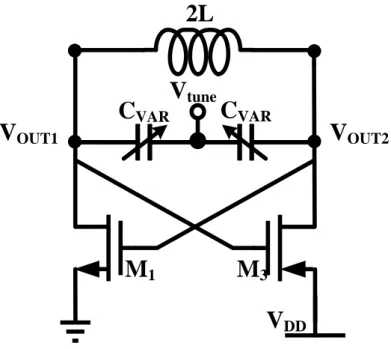

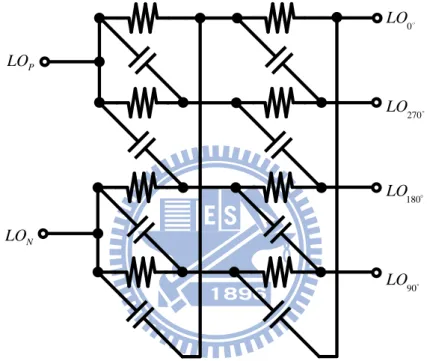

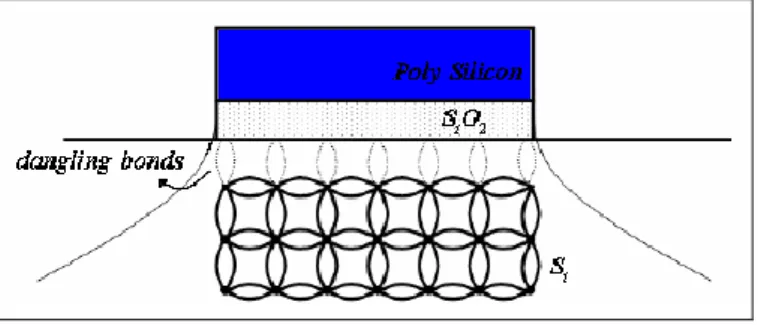

圖 2.1 雷達裝置圖... 4 圖 2.2 雷達感應器模組的 Functional Diagram ... 5 圖 2.3 直接降頻接收機架構圖... 6 圖 2.4 雙降頻式超外差接收機架構圖... 7 圖 2.5 單一本地振盪源之雙降頻視接收機... 7 圖 2.6 單一本地振盪源之雙降頻式接收機產生問題示意圖... 8 圖 2.7 本論文提出之新式單一振盪源之雙降頻接受機架構圖... 9 圖 3.1 壓控振盪器於 24GHz 車用雷達系統中之角色示意圖 ... 10 圖 3.2 使用負阻消除 LC tank 的寄生電阻示意圖... 11 圖 3.3 電感串並聯轉換... 11 圖 3.4 LC 共振腔等效模型 ... 11圖 3.5(a) NMOS Cross-Coupled Pair ... 12

圖 3.5(b) 計算圖 3.5(a)阻抗之等效電路 ... 12 圖 3.6 NMOS LC 共振腔振盪器 ... 12 圖 3.7 PMOS 交聯耦合對 ... 13 圖 3.8 互補式交聯耦合對... 13 圖 3.9(a) 基本五級環型振盪器示意圖 ... 14 圖 3.9(b) 四級差動環型振盪器 ... 14 圖 3.10 注入鎖定式振盪器(以三頻器為例) ... 16 圖 3.11(a) 理想振盪器輸出頻譜 ... 17 圖 3.11(b) 實際振盪器輸出頻譜 ... 17 圖 3.12(a) 受干擾訊號之示意圖 ... 18 圖 3.12(b) 混頻器降頻後結果 ... 18 圖 3.13 偏壓電流與相位雜訊及輸出振幅關係... 20 圖 3.14 實際電路之相位雜訊頻譜... 23 圖 3.15 在無損共振腔中注入脈衝雜訊電流... 24 圖 3.16 雜訊脈衝電流注入時相位不同之影響... 25 圖 3.17 閃爍雜訊與白色高斯雜訊貢獻至相位雜訊示意圖... 29 圖 3.19 單平衡式吉伯特混頻器及其工作原理... 31 圖 3.20 雙平衡式吉伯特混頻器... 33 圖 3.21 IP1dB示意圖 ... 35 圖 3.22 IIP3 示意圖 ... 35 圖 4.1 本論文所提出之新式壓控振盪器... 37 圖 4.2(a) 互補式交連耦合對壓控振盪器. ... 38 圖 4.2(b) 互補式壓控振盪器演化 ... 39 圖 4.3 電流再利用壓控振盪器... 39

ix

圖 4.4 電流再利用 VCO 之輸出差動振幅不匹配 ... 39

圖 4.5 RC-CR 四相位 Poly Phase Filter ... 40

圖 4.6(a) 理想的相移器輸入 ... 40 圖 4.6(b) 理想的相移器輸出 ... 40 圖 4.7(a) 不匹配的相移器輸入 ... 41 圖 4.7(b) 嚴重誤差的相移器輸出 ... 41 圖 4.8 需高度匹配本地振盪源訊號之三頻器架構與子電路圖... 42 圖 4.9 不匹配的本地振盪源累積放大於輸出端程度... 42 圖 4.10 源極退化電流再利用壓控振盪器與其差動輸出... 43 圖 4.11 本論文應用的調整差動轉導之電路架構 ... 44 圖 4.12 利用耦合電容提升轉導能力之電路架構... 45 圖 4.13 額外交連耦合對... 46 圖 4.14 新式壓控振盪器電流流向示意圖... 47 圖 4.15 新式壓控振盪器電路佈局圖... 48 圖 4.16 新式壓控振盪器電路照片圖... 48 圖 4.17 萃取電路佈局走線... 48 圖 4.19 新式壓控振盪器差動振幅輸出波形... 49

圖 4.20 Normal Cascode Type 在 1.5V 以及 1.3V 系統電壓之相位雜訊 ... 50

圖 4.21 具耦合電容 C2之電路在 1.5V 以及 1.2V 系統電壓之相位雜訊 ... 50 圖 4.22 具耦合電容 C2及 M5M6電路在 1.5V 以及 1V 系統電壓之相位雜訊 ... 50 圖 4.23 提升轉導能力可改善相位雜訊... 51 圖 4.24 相位雜訊量測圖... 52 圖 4.25 相位雜訊模擬與量測比較圖... 52 圖 4.26 輸出功率實測圖以及與模擬比較圖... 53 圖 4.27 調頻範圍的最低頻率與最高頻率輸出... 53 圖 4.28 調頻範圍量測與模擬比較表... 54 圖 5.1 低閃爍雜訊次諧波混頻器... 56 圖 5.2(a) 傳統式吉伯特混頻器 ... 57 圖 5.2(b) 堆疊式次諧波混頻器 ... 57 圖 5.3 堆疊次諧波混頻器等效開關轉換方程... 57 圖 5.4 水平式次諧波混頻器... 58 圖 5.5 水平式次諧波混頻器等效電路... 58

圖 5.6 CMOS 製程之 Dangling Bonds 示意圖 ... 59

圖 5.7 包含閃爍雜訊與本地振盪源的開關轉換方程... 60

圖 5.8 [19]中接收機以及其次諧波混頻器架構 ... 61

圖 5.9 [19]接收機之雜訊指數 ... 62

圖 5.10 靜態電流補償混頻器... 62

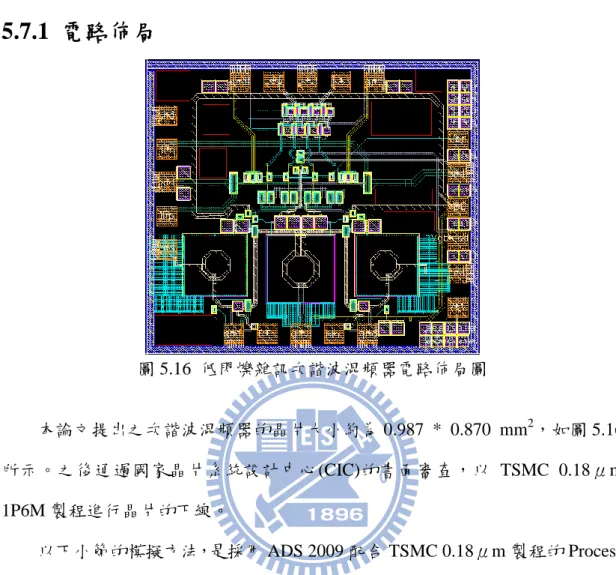

x 圖 5.12 PMOS 折疊水平式次諧波混頻器 ... 65 圖 5.13 使用電感抵消開關級共源點寄生電容... 66 圖 5.14 引入電流補償機制... 66 圖 5.15 低閃爍雜訊次諧波混頻器全電路圖... 67 圖 5.16 低閃爍雜訊次諧波混頻器電路佈局圖... 68 圖 5.17 萃取電路佈局走線... 68 圖 5.18 匯入走線效應後的電路設計圖... 68 圖 5.19 閃爍雜訊轉角頻率改善圖... 69 圖 5.20 IF 頻率與轉換增益 ... 70 圖 5.21 本地振盪源功率與轉換增益... 70 圖 5.22 射頻端返回損耗... 70 圖 5.23 中頻端返回損耗... 70 圖 5.24 IP1dB模擬圖 ... 71 圖 6.1 新式壓控振盪器... 74 圖 6.2 低閃爍雜訊次諧波混頻器... 74 圖 6.3 緩衝放大器與相移器設計... 76 圖 6.4 整合設計後 8 GHz 之相位雜訊 ... 76 圖 6.5 緩衝放大器之輸入與輸出功率... 77 圖 6.5 Transient 模擬後時域轉頻域之頻譜圖 ... 78

1

第一章

序論

1.1 研究動機

世界各國科技的進步伴隨著快速龐大的交通網絡演化,道路複雜度提升的同 時,各國車輛數也相對應地急速成長,車用道路逐漸變得壅塞以及混亂,使得大 小車輛交通意外頻傳。交通安全的議題在世人心中越來越被重視,同時也凸顯出 安全可靠的車輛安全系統研發的急迫性與必要性。 幸運的是,近年電子與通訊等科技的高度發展,恰恰媒合車輛安全系統的研 發條件,使得車輛安全系統可以達到監控駕駛人精神狀態、加強用路人行車時之 視野、防止車輛碰撞等特定功能,以增進交通安全性。在車輛安全系統中,汽車 防撞雷達即為一非常重要的部分,在瞬息萬變的道路上,汽車防撞雷達可以強化 駕駛員原本薄弱的感測能力,提供駕駛員雷達所偵測到的車輛周遭動態狀況,包 含駕駛之汽車與其他車輛、行人、障礙物的相對位置、速度、加速度等訊息,並 且防撞雷達還可以適時警示駕駛人採取必要措施,例如加速、減速或保持車身於 相同車道等,避免車輛碰撞意外發生,增加車輛駕駛員的安全性與舒適性。 汽車防撞雷達系統的作用,即為利用雷達偵測技術配合先進的電子設備,為 駕駛員爭取意外發生時的反應時間。研究指出,駕駛員如能多 0.5 秒反應時間則 車輛追撞意外的發生機率可以降低 60%;而如能再多出 0.5 秒反應時間,則追撞 機率可減少至 10%。根據美國聯絡車隊(US fleets of tractor-trailers)的四年資料, Eaton-Vorad 的防撞警告系統總計降低了可防止事故平均值的 50%(美國國家高速 交通安全管理局,National Highway Safety Administration, NHTSA),甚至可達 70%(Eaton-Vorad 資料)。汽車防撞雷達系統若要更進一步達到面積微型化、省電以及高效能,勢必需 要將防撞雷達系統 SoC(System on a Chip)化,也就是將原本 PCB 板的各別電路

2

設計,微型縮小整合至單晶片。目前最適當也最有希望達到省電、低成本及高效 能,則非互補金氧半導體(Complementary Metal Oxide Semiconductor, CMOS)製程 莫屬。縱然相較於其他先進製程而言,CMOS 製程目前依舊有較高基板雜訊、低 電流驅動轉導等缺點[1],但國際晶圓大廠對 CMOS 製程研發的快速縮小化使得 操作頻率及效能節節向上攀升,且與數位電路的高整合度也是其最大優勢之一。

本論文即提出利用台灣積體電路公司(Taiwan Semiconductor Manufacturing Company, TSMC) 0.18μm CMOS 製程,設計操作於射頻(Radio-Frequency, RF)頻 率之前端電路(Front-End)之兩關鍵電路:

1. 電壓控制振盪器(Voltage Control Oscillator, VCO)。 2. 混頻器(Mixer)。 並將此二關鍵電路應用在本論文提出的單本地振盪源之雙降頻接收機架構中,預 期未來能進一步結合其他關鍵子電路,將 24 GHz 車用防撞雷達接收機完整以單 晶片整合(SoC)實現。

1.2 研究方法與成果

本論文參考近幾年來發表有關 24GHz 以及 77GHz CMOS 雷達系統的期刊 論文,提出一新式 24 GHz 車用雷達系統接收機架構。接著參考近年來發表有關 壓控振盪器與混頻器兩關鍵電路的期刊論文,以 TSMC 0.18μm RF CMOS Technology 為使用 製 程,利用安捷倫公 司 的電路模擬軟體 Advance Design System(ADS),設計出適用於本論文提出之接收機架構的壓控振盪器與混頻器, 並採用 Cadence Virtuoso 軟體進行晶片佈局。 研究成果如表一所示。 下線晶片名稱 晶片面積 新式壓控振盪器 0.63 x 0.57(mm2) 低閃爍雜訊次諧波混頻器 0.99 x 0.87(mm2) 表 1.1 本論文之研究成果3

1.3 章節概述

本論文在第二章中會回顧適合應用在 24 GHz 雷達系統的接收機架構文獻, 並提出本論文預計採用的 24 GHz 雷達系統接收機架構,為一可將本地振盪源操 作在較低頻率,8GHz,之 24 GHz 單一本地振盪源雙降頻接收機。 之後,在第三章會對壓控振盪器以及混頻器等二關鍵電路,做適合應用於 24 GHz 雷達系統接收機的文獻回顧,並從中探討壓控振盪器以及混頻器兩電路 的基本操作原理,以及在各別電路設計時需特別考量的參數介紹、設計準則與取 捨考量。 緊接著,在第四章中,本論文提出一新式電流再利用壓控振盪器。此一新式 電流再利用壓控振盪器能改善傳統電流再利用壓控振盪器天生的差動振幅不匹 配的問題,可透過電路技巧,將差動輸出的兩端振幅精準匹配,並且透過新式架 構的優點,可以將系統電源 VDD降低,藉此達到低電壓操作、低功耗、高性能以 及差動振幅匹配等優點。 而在第五章中,本論文提出一低閃爍雜訊之次諧波混頻器。透過引進並改良 以往應用在傳統混頻器的電流補償技術(Current Bleeding),以及將電流轉導放大 級與開關級分離設計,得以有效抑制次諧波混頻器因 CMOS 矽製程而影響甚巨 的閃爍雜訊(Flicker Noise),使得混頻器在工作時,能確保由 RF 頻率降頻至直流 附近的訊號,不被閃爍雜訊影響。 第六章中,本論文將上述二電路壓控振盪器與混頻器,進行整合成單晶片的 模擬。在此章中,本論文著重於兩個子電路間的連接匹配以及壓控振盪器的緩衝 放大器設計。在考量兩個子電路互相影響的部分並加以設計後,壓控振盪器與混 頻器兩者皆能夠維持在單一電路設計時的電路特性。再透過時域模擬,觀察以壓 控振盪器產生之本地振盪源訊號,經由混頻器來跟理想射頻訊號所混頻後得到之 基頻訊號,由此驗證經由統整設計過後的兩電路皆可順利工作。 最後,第七章為本論文的結論。4

第二章

24 GHz 車用雷達系統接收機

2.1 車用雷達系統

本論文所採用的車用雷達系統為短距雷達系統。當雷達所發射出的 FMCW (Frequency Modulation Continuous Wave)調變波,碰到了前方或側後方的物體 時,會產生反射、散射等現象,而車用雷達接收機會根據所接收到的回波,與發 射初的 FMCW 調變波作比較,以得到我們想要的資訊。完整的車用雷達裝置共 有三個車用雷達系統,如圖 2.1 所示。其中一個前視車用雷達系統在車體前方的 保險桿內,用來偵測前方可能發生追撞的物體,另外兩個側視車用雷達系統將裝 置在左右後照鏡的位置附近,分別傾斜往左右後方偵測,目的在於偵測旁邊車道 較近距離的車輛,避免轉彎或變換車道時可能造成後方來車追撞。 圖 2.1 雷達裝置圖 為了達到預防碰撞的功能,車用雷達系統必頇能夠偵測出自身車體與周圍物 體之間的距離以及相對速度,有時甚至需要能夠同時偵測多個物體。在目前所有 的研究中,各個不同頻段的雷達 (如 10, 18, 24, 38, 77 GHz) 皆被採用在車輛不同

5 的應用領域中,其中短距離偵測的部份以 24 GHz 為主流,24 GHz 短距雷達感測 器相較於其他較低頻的雷達系統 (如 10 GHz),此頻率由於波長較短,射頻元件 (如天線)所需要的空間較小,所設計出來的雷達體積也較小,有機會裝置在小型 車輛上;而相較於更高頻的系統(如 38 與 77 GHz),此系統在電路設計製作上有 相當低的成本以及技術門檻,且模組化後組裝良率較高,適合做一般大眾化的推 廣。 24 GHz 車用雷達系統之系統方塊,可分成以下幾個部分:電源供應部份、 雷達感應器模組 (Radar sensor)、數位信號處理器、記憶體以及其他介面。下圖 是上述的雷達感應器模組的 Functional Diagram,主要是負責雷達波的產生發射 與接收。其中包含了一個微控制器(MCU)、車用雷達射頻發射機(RF Transceiver ) 與車用雷達射頻接收機(RF Receiver)以及天線(Antenna)。MCU 接受數位信號處 理器(DSP)的指令,產生一個隨著時間而改變的三角鋸齒波(Linear Ramp),用來 調變本地振盪源(Local Oscillator, LO)所振盪出來的頻率;車用雷達射頻發射機以 及車用雷達射頻接收機則用來發射所應用的 24GHz FMCW 調變波形,並對所接 受到的雷達回波做濾波、放大、降頻,最後將雷達回波送入 DSP 分析,產生所 對應出的物體距離以及速度關係。24 GHz 車用雷達系統方塊圖如下圖 2.2 所示。 24 GHz FMCW Antenna RF Transmitter Block RF Receiver Block Local Oscillator MCU Linear Ramp Controler DSP 24 GHz FMCW Filter Antenna Filter 圖 2.2 雷達感應器模組的 Functional Diagram

6

2.2 車用雷達接收機文獻回顧

本論文以24 GHz車用雷達系統為設計方向,目標完成一可應用於本系統的 24 GHz車用雷達接收機。此接收機可將物體所反射的FMCW調變回波,降頻至 DC - KHz之附近頻帶,使回波訊號可進入ADC、DSP等後級數位電路做訊號分 析。下述之文獻回顧,將探討兩種目前廣泛應用之接收機架構,一是直接降頻式 (Direct– Conversion )接收機,一為雙降頻超外差式(Super Heterodyne)接收機[2]。 本論文將透過分析此二種接收機架構優點與問題,於下一小節2.3來進一步提出 本論文所要的設計24 GHz車用雷達接收機架構。一、直接降頻式接收機

LNA

Down

Mixer

LO

ω

IFω

LOChannel

Selection

Filter

ω

RF 圖 2.3 直接降頻接收機架構圖 如圖 2.3 所示,直接降頻式接收機為迄今廣泛被應用的接收機架構之一,其 最大優點是複雜度低,功率消耗也低。但是此電路架構存在本地訊號溢漏(LO Leakage)、直流偏移(DC Offset)等問題,會使後級 OP 放大器、ADC 與 DSP 等電 路飽和,將會造成雷達系統距離偵測功能失準。基於以上考量,雖然複雜度與功 率消耗表現良好,但雷達系統最重要的偵測,卻會因此架構的問題而被限制住偵 測之最遠距離,故本論文不採用此架構來實現 24 GHz 車用雷達接收機。7

二、雙降頻超外差式接收機

LNA DownMixer

LO1 ωIF1 ωLO1 Channel Selection Filter Down Mixer LO2 ωIF2 ωLO2 Image Reject Filter Channel Selection Filter IF Amplifier 圖 2.4 雙降頻式超外差接收機架構圖 如圖 2.4 所示,雙降頻式超外差接收機為超外差接收機的進階版本。優點在 於藉由兩次混頻,來減緩原本超外差接收機之鏡像濾波器與頻帶濾波器的衝突。 雙降頻式超外差接收機可將 24 GHz FMCW 訊號,透過第一次混頻降至中頻,再 將中頻訊號透過第二次混頻降至 IF 來使用。此接收機架構缺點是需要兩組本地 振盪源與混頻器,造成系統複雜度提高,功率消耗也提高。 倘若透過適當的頻率選擇,以及利用一組二階諧波混頻器(Sub-Harmonic Mixer),則可以單獨使用一組本地振盪源來進行兩次混頻。本論文在下一小節將 此想法具體化,提出一新式 24 GHz 車用雷達接收機。

2.3 新式 24 GHz 車用雷達接收機

根據上小節提出的想法,本論文將之具體化,提出一新式 24 GHz 車用雷達 接收機,如圖 2.5 所示。 24 GHz LNA Sub-harmonic Mixer 8 GHz VCO 8 GHz 8 GHz 圖 2.5 單一本地振盪源之雙降頻視接收機8 本論文提出之接收機架構最大優點在於可以使用單一本地振盪源,進行兩次 混頻,使得本地振盪源操作頻率可以從原本的 24 GHz 降至 8 GHz。由於 CMOS 製程關係,頻率越高時 VCO 所使用被動元件(LC tank)之 Q 值越差,所能振盪出 來的本地振盪源之相位雜訊(Phase Noise)也隨之越差。反之,若將本地振盪源之 操作頻率往低頻移動,如此一來可以提升本地振盪源的相位雜訊(Phase Noise), 使整體車用雷達系統可以偵測功率更小的訊號,提昇雷達偵測距離。 然而若接收機架構的子電路設計如圖 2.5 所示,則可能衍生出其他的問題。 其衍生問題可能發生途徑,如圖 2.6 所示。

24 GHz

LNA

Sub-harmonic

Mixer

8 GHz

VCO

8 GHz

8 GHz

8 GHz 8 GHz DC-offset LO-IF leakage Self-mixingTraditional

Mixer

圖 2.6 單一本地振盪源之雙降頻式接收機產生問題示意圖 假使此處將二階諧波混頻器放在第一次混頻的地方,也就是第一次降頻後的 中頻頻率即被選擇成為8 GHz。故此處可以發現,接收機的第二次混頻機制,與 直接降頻式接收機完全相同,同樣為8 GHz RF訊號與8 GHz LO訊號相混,將會 有直流偏移(DC offset)的情形。第二個問題存在於第一次混頻時,本地訊號源之 漏波(Leakage)至中頻8 GHz路徑時,由於LO頻率與中頻頻率太相近,將會直接干 擾到所要解調的訊號。 故本論文提出將二階諧波混頻器放在第二次混頻的單一本地振盪源之雙降 頻式接收機,如圖2.7所示。9 24-GHz LNA 8 GHz VCO Sub-Harmonic Mixer 24-GHz 16-GHz Traditional Mixer DC-kHz 圖 2.7 本論文提出之新式單一振盪源之雙降頻接受機架構圖 此新式24 GHz車用雷達接收機,完整解決上述接收機之直流偏移(DC offset) 以及本地振盪源漏波干擾中頻訊號等問題。可以使用操作在低頻的本地振盪源以 獲取較佳相位雜訊表現本地訊號。種種考量皆優於之前所提出之電路架構。是故 本論文將採用此架構來應用至24 GHz車用雷達系統。以下章節將針對應用在此 新式24 GHz 車用雷達接收機架構之關鍵電路:壓控振盪器與次諧波混頻器,做 更進一步的研究以及設計。

10

第三章

射頻晶片設計基礎

3.1 壓控振盪器

壓控振盪器(Voltage Control Oscillator, VCO)是一種電子式振盪器,乃藉由輸 入直流電壓的改變,在輸出端產生可被控制的振盪頻率訊號。而在車用雷達系統 應用裡,壓控振盪器在收發機中扮演本地振盪源(Local Oscillator)的角色。在車 用雷達系統工作時,MCU對壓控振盪器的直流輸入的改變,促使本地振盪源訊 號具有FMCW調變訊息,透過發射與接收機,讓FMCW調變波往返於車用雷達 系統與雷達待測物之間,最後使DSP解出我們所要的避撞資訊,如圖3.1所示。 24 GHz FMCW Antenna RF Transmitter Block RF Receiver Block Local Oscillator MCU Linear Ramp Controler DSP 24 GHz FMCW Filter Antenna Filter 圖 3.1 壓控振盪器於 24GHz 車用雷達系統中之角色示意圖

3.1.1 壓控振盪器基本操作原理

一般分析振盪器的方式約略可分為: 一、 應用負電阻與頻率選擇觀點。 二、 符合巴克豪森準則(Barkhausen Criterion)之正回授觀點。 其中巴克豪森準則為滿足以下二條件:(a) 放大器與其回授電路之迴路增益(Loop Gain)等於 1。 (b) 迴路整體之相位偏移為振盪頻率的 2π 整數倍。

11

當兩個條件同時滿足時,該迴路會產生振盪。以下小節分析時,將分別以直觀的 原則各別採用之。

現今 CMOS RFIC 電路中常採用的兩種振盪器型式為 LC 共振腔(LC Tank)振 盪器及環形振盪器(Ring Oscillator)。前者有較優之相位雜訊,但其可調頻率範圍 較小;後者有較寬的可調頻率範圍且可產生多相位的功能,不過有較差的相位雜 訊。進一步利用 LC 共振腔振盪器之架構,可發展出注入鎖定式振盪器,常應用 於多接收機架構通訊系統或 N 倍頻器之使用中,使得輸出頻率得以準確與本地 振盪源頻率匹配。

3.1.1.1 LC 共振腔振盪器

設計壓控振盪器(VCO)常使用負阻的概念來消除 LC 共振腔的寄生電阻,如 圖 3.2 中的 R1所示。在振盪條件成立時,圖中之 R1=-R2 (R2<0),寄生電阻被主 動電路之負阻並聯後抵消掉,故 LC 共振腔可以持續振動產生訊號。而 LC 共振 腔之電感電容與其寄生電阻,可由串並聯轉換(圖 3.3)等效成圖 3.4 之簡易型式。 Negative Resistance LC Tank Resonator 2R

1R

圖 3.2 使用負阻消除 LC tank 的寄生電阻示意圖 2 P S S P S S S S R Q R L L L Q R P L S L S R P R L RP C 圖 3.3 電感串並聯轉換 圖 3.4 LC 共振腔等效模型12 負阻的產生,是利用電晶體交連耦合對(Cross-Coupled Pair)產生正回授迴 路,圖 3.5(a)即為常使用的 NMOS 交連耦合對,其輸入阻抗為

R

IN2

gm

。 推導電路圖如圖 3.5(b)所示。 2 gm 1 M M2 X V 1 M 2 M X I 1 V 2 V 圖 3.5(a) NMOS Cross-Coupled Pair 圖 3.5(b) 計算圖 3.5(a)阻抗之等效電路2 1 X

V

V

V

(3.1) 2 2 1 1 X m mI

V g

V g

(3.2) 1 2 1 22

m m X IN X m m mg

g

V

R

I

g g

g

(3.3)一般而言,NMOS 交連耦合對為容易實現的負阻(Negative Resistance)電路組 態,具有電流轉導值大的優點,使得負阻值亦大。將其與 LC 共振腔並聯後,即 成為一完整的 LC 共振腔振盪器,如圖 3.6 所示。 1 M M2 DD V L L C C 圖 3.6 NMOS LC 共振腔振盪器

13

而另一方面,使用 PMOS 交連耦合對所設計的壓控振盪器,如圖 3.7 所示, 則因 PMOS 較 NMOS 電晶體具更低之閃爍雜訊(Flicker Noise),其表現之相位雜 訊的結果能優於 NMOS 交連耦合對。但若 PMOS 要維持高轉導值,則在設計上 必頇選取大尺寸之 PMOS,其寄生電容 CGS會較 NMOS 的來的大,不利於高頻

使用。

此外,圖 3.8 為互補式交連耦合對(Complementary Cross-Coupled Cair),相對 於 NMOS 交連耦合對或 PMOS 交連耦合對而言,在相同電流消耗之下,互補式 交連耦合對具有更大的轉導,可以等效出更大的負阻阻抗值。其觀念如同電流再 利用,使得電晶體較快速的切換,輸出電壓波形的上升時間(Rising - Time)及下 降時間 (Falling - Time)也較對稱,由於較對稱的波形有較低的 ISF 係數,因此能 有更佳的相位雜訊(將於之後小節詳細討論)。缺點則為使用電晶體數量多,寄生 電容不容忽視,較不利於高頻設計。 1 M M2 DD V L C C L 1 P M MP2 DD V L C C 1 N M MN2 L 圖 3.7 PMOS 交聯耦合對 圖 3.8 互補式交聯耦合對

14

3.1.1.2 環形振盪器

環形振盪器(Ring Oscillator)[2]工作原理是利用奇數組反相器串接回授(如圖 3.8),或是偶數級差動放大器最後一即反接回授(圖 3.9(a))造成振盪,振盪周期由 總時間延遲來決定。如圖 3.9(b)所示,有奇數個反相器串接,振盪頻率為 01

2

Df

NT

,因此透過改變單一級反相器之延遲時間 TD,即可改變振盪頻率, 進而達成電壓控制振盪頻率的功能。環型振盪器的好處在於電路需要的晶片面積 較小,且易與鎖相迴路(Phase Locked Loop, PLL)電路整合。又因為直流準位相 同,故輸出訊號振幅較大(Full Swing)。其缺點在於主動元件使用量較多,因此相 位雜訊較大。不過在多相位的輸出上,環型振盪器顯得較有彈性,電路中一個迴 圈為 360∘,N 級環形振盪器之中間每一級的輸出即為振盪頻率的 360∘/N 相位。圖 3.9(a) 基本五級環型振盪器示意圖

15

3.1.1.3 注入鎖定式振盪器

在車用雷達系統設計考量中因應用所需,若欲設計出接收機含有兩套以上相 同電路的接收機,低頻段時可以將之全部設計在同一晶片中,但在若頻率為 38GHz 或 77GHz 等高頻段使用時,多組接收機整合在同一晶片中是不明智的選 擇。主因為在 77 GHz 此頻段中,電磁訊號在電路板中損耗極高,若是訊號在不 同的天線接收下來後,還需經由傳輸線傳送訊號至單一接收機晶片,則訊號將在 傳輸線上會有相當可觀的損耗。因此若有此應用考量,較佳做法應配合不同接收 天線,在各別天線後端,立即接上一接收機晶片進行接收混頻。又,即便是先進 製程,亦無法保證相同設計的 VCO 操作頻率特性會完全相同。因此,本地訊號 源同步化的問題是一關鍵。透過注入式壓控振盪器(Injection-Locking Oscillator), 可有效解決此同步問題。我們可將單一本地振盪源訊號各別注入至各晶片中,使 每 一 晶 片 中 的 本 地 振 盪 源 頻 率 完 全 匹 配 相 同 。 而 諧 波 注 入 鎖 定 式 振 盪 器 (Sub-Harmonic Injection-Locking Oscilator)的使用,可將本地振盪源頻率設計成為 原本射頻頻率的二分之一頻,甚至是四分之一頻率,因此在訊號電路板傳輸線輸 時,衰減量遠遠低於高頻的訊號衰減。 如上所述,諧波注入鎖定式振盪器可以注入輸出頻率的諧波型式來鎖定,若 注入訊號若是為輸出頻率的整數倍數,稱為注入鎖定式除頻器(Injection Locking Divider);若是為輸出頻率的 1/N 倍數,則可稱為注入鎖定式 N 倍頻器。而在未 來考量中,由於本論文提出的新式 24GHz 車用雷達接收機架構,所使用的本地 振盪源設計為 8 GHz,是故對應到未來要發展的 24 GHz 車用雷達收發機架構 中,勢必需要一個 RF 三頻器(Tripler),將本地振盪源 8 GHz 的訊號提升至 24 GHz,當作發射訊後由發射機端輸出。在此,我們可以利用注入鎖定式三頻器 (Injection Locking Tripler)來達成這樣的功能。另外注入鎖定式三頻器的相位雜 訊,是以注入訊號的相位雜訊,再扣上 20logN,N=3 的理論代價值[3],約為 9.5dB。計算此代價後的相位雜訊,可以更優於傳統 LC 共振腔振盪器直接振在16 24 GHz 所得到相位雜訊,此為注入鎖定式振盪器的最大優點之一。故以下我們 針對注入鎖定式三頻器,也就是諧波注入鎖定式振盪器,來做相關工作的探討。 1 M M2 DD V L L C C Tail M INJ V Tail M INJ V 圖 3.10 注入鎖定式振盪器(以三頻器為例) 如圖 3.10 所示[4],此電路架構主要由基本的 LC 共振腔振盪器進化而成。 最大的差異是利用尾端電流源來饋入所要鎖定的振盪頻率,使上方的電晶體 M1、M2、LC 共振腔組成之振盪器所振盪的核心頻率也就是自由振盪頻率(Free Running Frequency)鎖定成注入訊號的諧波(在此三頻器應用中為三次諧波)。其工 作 原 理 為 在 於 尾 部 電 流 源 MTail 的 各 別 閘 極 (Gate) 饋 入 相 差 180°的 差 動

(Differential)注入訊號,經由電流源非線性反相放大後,於 MTail的各別汲極(Drain)

將具有注入訊號的三次諧波頻率產生。若此三次諧波頻率落在自由振盪頻率附 近,且具足夠功率,則能達到鎖頻功能,使振盪頻率鎖定為注入訊號的三倍頻, 達成三頻器的目標。值得一提的是,使用注入鎖定式振盪器時,注入的訊號不能 過小,故提供注入訊號之主要本地振盪源,必需設計成較高功率輸出的型式,或 多串接一級緩衝放大器來推動此三頻器。

17

3.1.2 壓控振盪器參數介紹

3.1.2.1 相位雜訊

壓控振盪器對於雜訊與溫度影響相當敏感,會使振盪器的輸出訊號在振幅、 相位甚至頻率上產生改變,產生於振幅調變(Amplitude Modulation)、相位調變 (Phase Modulation)及頻率調變(Frequency Modulation)中的雜訊。而振盪器輸出的 振幅,被溫度以及雜訊的影響程度較小,並且會在非常短的時間之內趨於穩定, 故在以下討論中,可忽略振幅調變雜訊。至於輸出相位的變動,會受相位調變雜 訊及頻率調變雜訊所影響,此即定義為相位雜訊(Phase Noise)。圖 3.11 可以在頻 譜上的看出相位雜訊對振盪器的影響。圖 3.11(a)為理想的振盪源輸出,即是一相 當乾淨的單頻頻率訊號,但在實際振盪器情形中,如圖 3.11(b)所示,在以輸出 頻率也就是載波頻率 fc為中心,隨著逐漸增大Δf 位移量(Offest),產生向下遞減 的雜訊,最後趨於熱雜訊的雜訊階級,此「裙帶」狀的雜訊,即為相位雜訊貢獻。 相位雜訊被定義成為「在Δf 位移處,其 1 Hz 頻寬的雜訊量,除以輸出頻率功率」, 如(3.4)所示[6]。 f Output Power C f out

P

f Output Power f fC C f Hz 1)

( f

L

outP

圖 3.11(a)理想振盪器輸出頻譜 圖 3.11(b)實際振盪器輸出頻譜1

@

{

}

Hz Bandwidth Noise Power

f

OffsetL

f

Carrier Power

18

相位雜訊在接收機中的影響甚大,雷達接收機是利用混頻器,將物體反射之 回波與本地振盪源混頻,將回波訊號降至低頻,以利 ADC 以及 DSP 電路處理。 倘若在回波的頻率(fo)附近,存在一功率極高的干擾訊號(fInterfere),如圖 3.13(a)所

示,如此一來在降頻之後,此干擾訊號因相位雜訊的裙帶,很有可能蓋過回波訊 號,或是造成訊雜比(Signal to Noise Ratio, SNR)強烈惡化(圖 3.13(b)),將使車用 雷達偵測功能受限。 f O f fInterfere LO f IF f Output Power IF f fInterfere' f 圖 3.12(a) 受干擾訊號之示意圖 圖 3.12(b) 混頻器降頻後結果 相位雜訊的分析,普遍來講有兩種經典模型,一為 Lesson 於 1966 年所提出 的非時變模型[5],如(3.5)所示。二為時變模型[6],由 Hajimiri 於 1998 年提出, 如(3.6)、(3.7)所示,分別對應到 2 1 f 與 3 1 f 之相位雜訊曲線。此二經典模型將在下 一小節做深入的討論。 3 2 1/

2

(

) 10log

1

1

2

f o s TankFKT

L

P

Q

(3.5) 2 22

(

) 10log

o rms skT

L

P

Q

(3.6) 2 2 0 1/ 2 2 max(

)

10log

8

n fi

c

f

L

q

(3.7)19

3.1.2.3 調頻範圍

LC 共振腔壓控振盪器的調頻範圍(Tuning Range)主要取決於變容二極體 (Varactor)的大小,若是變容二極體尺寸挑選大尺寸,則可變電容值較大,可以調 整的頻率範圍也越大。但不幸的是,LC 共振腔振盪器的可調範圍,往往被整體 電路的寄生電容給限制住。如(3.8)所提,共振頻率 fLO與 LC 乘積根號成反比, 但是其中的 C 值是可變電容容值與寄生電容容值總和(3.9),故調頻比例被寄生電 容限制,尤其越小的可變電容容值受限越大。 01

2

f

LC

(3.8) V PC

C

C

(3.9) 但是過大的可變電容值,將會造成整體電容品質因素(Quality Factor, Q)下降 [7],如(3.10)所示。1

1

P V C V V P P VC

C

Q

Q

Q

C

Q

C

(3.10) 其中 QC為整體電容 Q 值,QV為可變電容 Q 值,QP為寄生電容 Q 值,CP 為寄生電容容值,CV為可變電容容值。通常 QP遠高於 QV,此時 QC與 CV成反 比關係,也就是 CV的增加將造成 QC的下降。這樣的關係不利於整體 LC 共振腔 品質因素(QTank),如(3.11)所示。 L C Tank L CQ Q

Q

Q

Q

(3.11) 而 QTank在Lesson’s 相位雜訊模型(3.12)中,為非常重要的關鍵因素,要有好 的相位雜訊表現,必頇要有高的共振腔品質因素。20 3 2 1/

2

(

) 10log

1

1

2

f o s TankFKT

L

P

Q

(3.12) 因此可以得到調頻範圍的兩個結論:一為調頻範圍由可變電容大小決定,其 會受到電路寄生電容的影響,縮小可調頻範圍;二為可變電容容值大小與電容品 質因素成反比,造成調頻範圍與相位雜訊為互相取捨(Trade Off)的關係,在電路 設計上必頇以實際系統應用來考量。 調頻範圍尚會受其他因素影響,而這些影響是不被預期的,電路設計上希望 能夠避免此類影響。其中一種因素是電路寄生電容的改變,當電晶體的直流偏壓 改變,其寄生電容(主要為接面電容 Cgs)大小也會跟著變動,此現象稱為推頻效應(Pushing Effect)。解決的方法可以使用較穩定的偏壓電路,如 Band-Gap 偏壓 電路,讓直流偏壓穩定。第二種因素為負載拉頻效應(Loading Pulling Effect),其 負載電路若是改變的話,振盪器的核心共振腔所看到的阻抗也會跟著變化,故其 振盪頻率會跟著改變。在實際應用上,振盪器與下級電路例如混頻器之間,必頇 要串接一級緩衝器,提高振盪器的共振腔與負載的隔離度,使振盪頻率不受影響。

3.1.2.4 功率消耗

在Lesson’s 模型中,如(3.12)所示,透過增大輸出訊號的振幅擺幅 PS即可有 效改善相位雜訊的表現。而振幅擺幅與直流偏壓電流有正相關,但並非偏壓電流 持續上升,就能讓相位雜訊不斷改善,而是如圖 3.13 所示,直流偏壓提高到一 定程度之後,相位雜訊會開始變差[8]。主因為過大的電流會使雜訊惡化。 Oscillation Amplitude Phase Noise , M I Bias Current 圖 3.13 偏壓電流與相位雜訊及輸出振幅關係21 在由 NMOS 交連耦合對組成的 LC 共振腔振盪器中,其功率消耗可以如(3.13) 表示之,為直流電晶體電流 IM與系統電壓 VDD的乘積。

2

Diss M DDP

I

V

(3.13) 其中 IM可表示成(3.14)之 MOS 電晶體在飽和區的電流公式。 2 2 0 01

(

)

2

2

m M ox GS T oxg

W

I

C

V

V

W

L

C

L

(3.14) 在振盪時,gm與 RP關係如前所述,可表示為(3.15);且 RP亦可表示為(3.16)。 其中 L 為 LC 共振腔電感值,QTank為共振腔 Q 值,C 為 LC 共振腔電容值。將 (3.14)~(3.16)代入(3.13)後,可得到(3.17),如下所示。2

P IN mR

R

g

(3.15) 2P Tank S Tank Tank

L

R

Q

R

Q

L

Q

C

(3.16) 2 04

DD Diss Tank oxV

C

P

W Q

L

C

L

(3.17) 故可知,在電晶體尺寸固定情形下,如要減少功率消耗,可以增加電感 Q 值,或者降低 C/L 的比例來設計低功率消耗的振盪器。亦可知道,當所要設計的 振盪頻率逐漸增高時,在製程上無可避免地,共振腔 Q 值會惡化,隨之所要付 出代價,除了相位雜訊變差之外,還有直流功率消耗向上攀升。3.1.3 相位雜訊模型

相位雜訊是壓控振盪器設計中最重要的參數,要改善此參數特性,首先必頇 對於此參數做深入的探討。非時變模型[5]最早於 1966 由 Lesson 提出,讓晶片設 計者能夠有所依據地設計其壓控振盪器的各項參數。而時變模型[6],由 Hajimiri22 於 1998 年提出,補足 Lesson 模型中 1/f3區段的準確推導。以下將簡介此二種相 位雜訊模型。

3.1.3.1 非時變模型

此小節中使用非時變模型來分析相位雜訊。非時變的定義為,不論雜訊何時 注入振盪器之中,對壓控振盪器的相位雜訊影響皆為相同貢獻值。換句話說,雜 訊所造成的振盪器相位位移量在任何時間點上都為相同,故無需考慮雜訊於何時 注入,可使用非時變來簡化分析方法。假設振盪器由放大器負阻與共振腔所組 成,其帶通轉換方程(Band-Pass Transfer Function)可以寫成如(3.18)所示。2

(1/

)

(

)

(1/

)

(1/

)

j

RC

H j

LC

j

RC

(3.18) 而通用的帶通轉換方程可以如(3.19)表示之。 2 2(

/ )

(

)

(

/ )

o o oj

Q

H j

j

Q

(3.19) 比較(3.18)及(3.19)後可發現如(3.20)所示。1

Q=

o oRC

LC

and

(3.20) 觀察一具微小頻率位移之頻率點

o

時,若

o時,則 可將上式(3.18)以泰勒展開式展開,並且忽略一階與二階以上的項,如(3.21)所示。2

(

) 1

(

o/ )

H j

j

Q

(3.21) 因此可得振盪器的閉迴路(Close-Loop)響應,如(3.22)所示(

/ )

1

(

)

1

(

)

2

oj

Q

G j

H j

(3.22) 當輸入雜訊密度為S

i( )

時,則經過此振盪器系統,亦即經過振盪器的閉23 迴路響應後,其輸出雜訊密度表示式如(3.23)。 2 2

( )

( )

( )

(

)

2

o o iS

S

G

FkT

Q

(3.23) 上式(3.23)為雙邊帶(Double Sideband)雜訊頻譜密度,因此距離振盪頻率

處之單邊帶(Single Sideband)之訊雜比,以dB型式表示後,即為相位雜訊,如(3.24) 所示。 22

(

) 10log

2

o SFKT

L

P

Q

(3.24) 其中P

S為振盪器之輸出功率。透過觀察(3.24)可知,提升輸出功率以及共振 腔的Q值,可以改善相位雜訊的表現。而增加輸出功率同時意味著增加負阻放大 器的功率,將降低放大器的雜訊指數(Noise Figure),故可以另一直觀的觀點來解 釋相位雜訊的降低現象。 由(3.24)可對相位雜訊得到初步的了解,但此式的描述與實際電路的量測結 果存在一定的差異,如圖3.14所示。 ) log( ) ( L 3/

1 f

2/

1 f

sP

FkT

2

1

log

10

3 / 1 f 0/2Q 圖 3.14 實際電路之相位雜訊頻譜 在極小的頻率位移處,相位雜訊以1/ f

3下降;在極大的頻率位移處,相位24 雜訊將趨於水平降至熱雜訊等級,而非如(3.24)所述持續以

1/ f

2下降。 因此相位雜訊公式(3.24)必頇配合實際量測壓控振盪器頻譜後,做曲線上的 趨近調整(Curve Fitting),修正成為(3.25)所示,即為Lesson模型,其式中的F需要 經由量測才能得到。 3 2 1/2

(

) 10log

1

1

2

f o sFKT

L

P

Q

(3.25) 此模型對於振盪器電路設計時雖然有極大的幫助,但卻無法精準解釋1/ f

3 區域的成因為何。並且在實際量測中,頻譜1/ f

2轉為熱雜訊水平的頻率轉角亦 常非為式中所描述的2

oQ

。下一小節將以時變分析方法來得到相位雜訊時變模 型,可以解釋1/ f

3區域的成因,並能應用其結論,除了增進 Q 值以及輸出功率 大小能改善相位雜訊表現,尚有其他方法亦可優化相位雜訊。3.1.3.2 時變模型

在本小節中,利用Hajimiri模型[6]來解釋相位雜訊。首先,假設一個雜訊脈 衝電流i(t),注入一個理想無損 LC共振腔,如圖3.15所示。若雜訊電流恰於共振 腔振盪電壓擺幅至最高點時注入,如圖3.16(a)所示,則共振腔的振幅將會增加 ΔV=ΔQ/ C,但是振幅與時間軸上的零交點(Zero-Crossing)不會改變,也就是相位 不會變動。而雜訊脈衝i(t)若在其他任何時間注入的話,對共振腔的影響則如圖 3.16(b)所示,僅對零交點,也就是相位有影響。因此,脈衝注入時的影響與相位 息息相關,故此系統必頇使用時變的觀點來分析。 L C i(t) ) ( t t 圖 3.15 在無損共振腔中注入脈衝雜訊電流25 V

V

(a) (b)t

OUT Vt

OUT V 圖 3.16 雜訊脈衝電流注入時相位不同之影響 有鑑於此,於是Hajimiri提出了一個與Lesson截然不同的線性時變相位 雜訊模型。其脈衝響應可寫成如(3.26)所示,表示脈衝訊號於

o 注入時的 振盪器相位偏移量。 max(

)

( , )

o(

)

h t

u t

q

(3.26)其中qmax為LC共振腔所儲存的最大電荷量;u(t)為單位步階函數(Unit Step

Function);

( )

x

脈衝靈敏度方程(Impulse Sensitivity Function),周期為2π,與訊 號頻率及最大振幅無關,但與訊號的時域波形有重大的相依性。 假使其ISF為已知,則可推導出脈衝注入後的相位改變量,如(3.27)所示。 max1

( )

( , ) ( )

(

) ( )

t ot

h t

i

d

i

d

q

(3.27) 又因ISF為一周期性函數,可由傅立葉級數展開成(3.28)。 0 1(

)

cos(

)

2

o n o n nc

c

n

(3.28) 其中CN為ISF的實數傅立葉係數,n為ISF之N次諧波相位。根據雜訊源的不 相依性(uncorrelated),每一雜訊源的相位不互相干擾,故以下推導可將(3.28)中的 n 省略以簡化分析。將(3.28)代回(3.27)後可重寫成為(3.29)如下所示。26 0 1 max

1

( )

( )

( )cos(

)

2

t t n o nc

t

i

d

c

i

n

d

q

(3.29) 至此,若(3.29)中的傅立葉係數已知,則可計算出任意雜訊脈衝電流注入時,所 造成相位位移量。 現在考慮一注入雜訊電流源為弦波形式,頻率與共振腔之振盪頻率的整數倍 相當靠近,為m

o

,如(3.30)。

( )

mcos (

o)

i t

I

m

t

(3.30) 將(3.30)代入(3.29)中,並假設

o,則相位輸出可寫成(3.31)形式。並令 輸出電壓為(3.32)所示。 max( )

sin(

)

2

m mI c

t

t

q

(3.31)

( )

cos

( )

out oV

t

t

t

(3.32) 假設 max1

2

m mI c

q

,並將(3.31)代入至(3.32)中,可以推算出此輸出訊號的頻 譜,將在

o附近,也就是

o頻率處以及

o頻率處,產生二個等功率 大小的雜訊干擾頻譜,大小如(3.33)所示。 2 2 2 2 2 max max(

) 10log

10log

4

16

m m m m SBCI c

I c

P

q

q

(3.33) 一般而言,電流雜訊源可分為兩種型式:一為白色高斯雜訊(White Noise), 另一為閃爍雜訊(Flicker Noise),也就是1/ f

雜訊源。首先若電流雜訊源為白色 高斯雜訊。其功率頻譜密度為 2 22

n mi

I

f

,代入(3.33)後,即為白色高斯雜訊之 貢獻頻譜,將之積分後,即為由白色高斯雜訊貢獻的壓控振盪器相位雜訊。如(3.34)27 所示。 2 2 0 2 2 max

(

) 10log

8

n m mi

c

f

L

q

(3.34) 根據Parseval原理(頻域與時域的能量守恆互換式) 2 2 2 2 0 01

( )

2

m rms mc

x dx

(3.35) 故將(3.35)代入至(3.34),可得到(3.36)如下所示。 2 2 2 2 max(

) 10log

4

rmsi

nL

q

f

(3.36) (3.36)式中q

max

CV

max,V

max為壓控振盪器的最大振幅,C

為共振腔中的電 容值;又 24

n Pi

kT

f

R

;且 2 max2

S PV

P

R

,為振盪器輸出功率; P oQ

R

C

, 為共振腔之並聯寄生電阻;將數式代入(3.36)後,整理可得下式(3.37)。 2 22

(

) 10log

2

o rms skT

L

P

Q

(3.37) 此式(3.37)與Lesson非時變模型中提出的(3.24)式幾乎相同,唯一不同的為 (3.24)中需經由量測才能得到的參數F,在(3.37)式中,卻可以藉由尋找輸出波形 的ISF後,計算而得

2rms。且由(3.27)可知,要降低相位雜訊的方法,除了增加 共振腔Q值以及加強輸出訊號的功率以外,還能藉由改變輸出訊號的波形,以降 低ISF的

rms,進而改善白色高斯雜訊所造成相位雜訊。 其次,若進入共振腔的電流雜訊為閃爍雜訊(1/f),其功率頻譜密度為(3.38)28 所示。其中

1/ f 為閃爍雜訊的轉角頻率。 1/ 2 2 ,1/ f n f ni

i

(3.38) 將上式代入至(3.33)式中,並經過分析知

1/ f 對於傅立葉係數僅影響其C0 項,於是閃爍雜訊對相位雜訊的影響,可以寫成如(3.39)型式。 2 2 0 1/ 2 2 max(

) 10log

8

n fi

c

f

L

q

(3.39) 其中閃爍雜訊1/ f

的轉角頻率,並非如預料中即為相位雜訊中的1/ f

3頻 率。真實的1/ f

3位於(3.39)與(3.36)兩式相等之頻率位移處,可寫成(3.40)所示。 3 2 2 0 0 1/ 2 1/ 1/ 12

f f f rmsc

c

c

(3.40) 由上式(3.40)可以得到一非常寶貴的結論:即便在具較差的閃爍雜訊表現的 CMOS製程使用上,亦即其1/ f

的轉角頻率較高,還是可以透過抑制傅立葉係 數C0,將1/ f

所造成的相位雜訊惡化情形降至最小,使得在極小頻率位移處得 到相當好的相位雜訊表現。而C0在ISF中所代表的意義為直流成分,故要降低C0, 必頇使得壓控振盪器輸出波形越奇對稱(Odd-Symmetry),其C0成分可以越低。 綜合以上兩種分析,各別以白色高斯雜訊電流源注入,以及閃爍雜訊電流源 注入壓控振盪器的共振腔中,將對相位雜訊造成不同的影響。而相位雜訊的變化 亦與壓控振盪器之輸出波形有關。由此二雜訊所造成的相位雜訊變化,會在壓控 振盪器的輸出訊號頻譜週圍,形成裙帶狀的相位雜訊,如圖(3.17)所示意。29 ωo 2ωo 3ωo White noise ωo 2ωo 3ωo ωo 2ωo 3ωo c0 c1 c2 c3 Flicker noise 圖 3.17 閃爍雜訊與白色高斯雜訊貢獻至相位雜訊示意圖 在以上時變模型分析中,準確解釋了相位雜訊各區形成的原因,因此電路設 計者可對相位雜訊做一精確的預測。對於壓控振盪器中任何一個雜訊源,設計者 都可以依照各別的雜訊等效模型,以及其訊號波形,對應至其雜訊源的ISF方程, 以求出相位雜訊。值得一提的是,要找出ISF方程,可以將雜訊源以一個脈衝訊 號代替,並找出壓控振盪器對此脈衝訊號的脈衝響應,其即為壓控振盪器對應於 此雜訊源的ISF。此外,若只是求直觀上的理解,一般將輸出的波形微分運算後, 即可得到接近ISF的計算結果。 時變模型除了比非時變模型更準確的預測相位雜訊之外,更使得電路設計者 理解到,在設計電路時除了要追求共振腔的Q值以及提升輸出訊號的功率,還必 頇考慮輸出波形的對稱程度以及該波形上升下降的快慢程度。尤其是對於具備較 高閃爍雜訊的CMOS製程而言,壓控振盪器輸出波形必頇要越奇對稱越好、波形 上升下降時間越短越好。

30

3.2 混頻器

混頻器(Mixer)在接收機中,扮演著將射頻頻率降至基頻頻率的重要角色。 同時也對整體接收機的線性度有著重大的影響。混頻器需高線性度的原因為前級 電 路 通 常 為 一 低 雜 訊 放 大 器 (Low Noise Amplifier, LNA) 已 將 射 頻 (Radio Frequency)頻率訊號放大,為了維持低的交互調變(Inter-Modulation)特性,而需要 高輸入線性度。當電路不夠線性時會產生如交叉調變(Cross Modulation)、去靈敏 化 (Desensitization) 、 諧 波 項 產 生 (Harmonic Generation) 以 及 增 益 壓 縮 (Gain Compression)等等的問題。其中偶次階非線性(Even-Order)現象可經由差動雙平衡 式架構來改善,但其中奇次(Odd-Order)非線性改善的困難度較高,尤其以三階交 互調變失真(Third-Order Inter-Modulation Distortion, IMD3)挑戰最高,也是奇次非 線性現象的主要來源。

3.2.1 混頻器基本操作原理

混頻器為三端元件,具有本地振盪端(LO Port)、射頻端(RF Port)以及中頻端 (IF Port)。前級電路低雜訊放大器將射頻訊號放大後,由混頻器之射頻端進入; 而本地振盪端則輸入由壓控振盪器輸出的訊號,當做本地振盪源使用。在射頻訊 號與本地振盪源訊號相混之後的中頻訊號,從中頻端輸出至下級電路。 混頻器主要可以分為主動混頻器 (Active Mixer)以及被動混頻器(Passive Mixer)兩種,在電路設計者中,各有其擁護者特別支持。以CMOS製程為例,使 用電晶體式的主被動混頻器[2]可以如圖3.18所示。 LO RF IF RF LO IF 圖 3.18(a)主動式混頻器 圖 3.18(b)被動式混頻器