全金屬矽化物互補式金氧半製程之矽控整流器及其在射頻電路之靜電放電防護設計與應用

166

0

0

全文

(2) 全金屬矽化物互補式金氧半製程之矽控整流器 及其在射頻電路之靜電放電防護設計與應用 SCR-BASED ESD PROTECTION DESIGNS FOR RADIO-FREQUENCY INTEGRATED CIRCUITS IN FULLY SILICIDED CMOS PROCESS. 研 究 生:林群祐 指導教授:柯明道. Student: Chun-Yu Lin Advisor: Ming-Dou Ker. 國 立 交 通 大 學 電子工程學系 電子研究所 博 士 論 文 A Dissertation Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electronic Engineering July 2009 Hsinchu, Taiwan, Republic of China 中華民國九十八年七月.

(3) 全金屬矽化物互補式金氧半製程之矽控整流器 及其在射頻電路之靜電放電防護設計與應用 研究生:林群祐. 指導教授:柯明道 博士. 國立交通大學電子工程學系電子研究所. 摘要 在所有積體電路產品中,皆必須於量產時符合可靠度 (Reliability) 的規範,以提供 該積體電路產品足夠的耐用年限。而隨著奈米級互補式金氧半製程的持續發展,靜電放 電 (Electrostatic Discharge, ESD) 防護已成為積體電路產品可靠度中相當艱鉅的挑戰, 大多數電子產品的故障與損壞均與遭受靜電放電轟擊有關。為避免積體電路遭受靜電放 電的威脅與破壞,所有積體電路與外界接觸的銲墊 (Pad) 皆須搭配靜電放電防護設計。 無線通訊裝置中的射頻 (Radio Frequency, RF) 電路,因其連接射頻收發機與外接 之濾波器或天線,因此亦需搭配靜電放電防護設計。由於射頻電路操作在數十億赫茲 (Gigahertz, GHz) 以上的工作頻率,如此高頻的工作頻率對於訊號路徑上的寄生效應有 極為極嚴格的限制,靜電放電防護電路的寄生效應必須達到最小化的設計,以避免射頻 電路性能的嚴重衰減。在寄生效應嚴格限制的情況下,矽控整流器 (Silicon-Controlled Rectifier, SCR) 是極為有用的靜電放電防護元件。由於在二極體 (Diode)、矽控整流器、 雙載子電晶體 (BJT)、金氧半場效電晶體 (MOSFET)、或者是場氧化層電晶體 (Field Oxide Device, FOD) 等眾多的靜電放電防護元件中,矽控整流器具有面積最小、寄生效 應最小、靜電放電耐受度最好的優點,並且完全相容於一般互補式金氧半製程的步驟, 不需額外的光罩去遮蔽金屬矽化物 (Silicide Blocking),尤其將它應用在先進製程中不 會有閂鎖效應 (Latchup) 的問題,因此可以廣泛應用在積體電路中當作靜電放電防護元 件。然而過高的觸發電壓與較慢的導通速度,使得矽控整流器在實際應用上必須搭配有 -i-.

(4) 效地低電壓觸發與高效率導通之設計。矽控整流器基本特性是由電流觸發而導通的元 件,所以當有一觸發電流施加於矽控整流器的基體時,矽控整流器便可很快地經由正回 授再生機制 (Positive-Feedback Regeneration Mechanism) 觸發進入導通狀態。 搭配矽控整流器的射頻電路之靜電放電防護設計是本論文的研究主題,本論文的章 節包括:(1) 使用交叉耦合 (Cross Couple) 的矽控整流器之差動式低雜訊放大器 (Low-Noise Amplifier, LNA) 設計、(2) 超低寄生電容的矽控整流器設計、(3) 搭配超低 寄生電容的矽控整流器之超寬頻功率放大器 (Power Amplifier, PA)、(4) 應用在射頻電 路與靜電放電防護電路共同設計之寄生電容模型、(5) 利用矽控整流器設計之可耐高工 作電壓以及低漏電之靜電放電箝制電路。 本論文第二章針對一種射頻窄頻前端電路與靜電放電防護電路共同設計。本章使用 130 奈米互補式金氧半製程設計一個工作於 5 GHz 的差動式低雜訊放大器,並探討差 動式低雜訊放大器接點對接點 (Pin to Pin) 之靜電放電耐受度。新提出的靜電放電防護 設計於兩個差動輸入銲墊間使用交叉耦合的矽控整流器,除了可提供單一輸入銲墊至電 源線與接地線的靜電放電防護外,更可提供兩個差動輸入銲墊間的接點對接點模式靜電 放電防護功能。此設計的人體放電模式 (Human Body Model, HBM) 與機械放電模式 (Machine-Model, MM) 靜電放電耐受度分別為 3.5 kV 與 300 V。相關的射頻性能以及 靜電放電耐受度皆於第二章內比較與討論。 第三章藉由改變矽控整流器的元件佈局方式以降低寄生效應。在矽控整流器中使用 方塊狀 (Waffle) 之新型佈局結構,可在相同晶片佈局面積下提供最大靜電放電路徑周 長,因此可在最小寄生電容的前提下,提供最高的靜電放電防護能力。換句話說,方塊 狀之矽控整流器可降低元件本身的寄生電容值。本研究於 0.18 微米互補式金氧半製程 中實現此新型設計,並且不需增加元件和其他成本,故十分適合應用於射頻電路之靜電 放電防護設計。 利用新提出之方塊狀矽控整流器,第四章將其應用於射頻功率放大器之靜電放電防 護電路。本章使用 130 奈米互補式金氧半製程實現此射頻電路,實驗證明此靜電放電 防護策略可有效地提供防護等級超過 8-kV 人體放電模式之靜電放電轟擊測試、與 800-V 機械放電模式之靜電放電轟擊測試。實驗結果亦證明,靜電放電轟擊確實對射頻 功率放大器的射頻操作效能有極大的影響,射頻功率放大器極需靜電放電防護設計,否 則無法於靜電放電轟擊下存活。 隨著射頻電路工作頻率持續升高,靜電放電防護電路的寄生效應也愈來愈難以掌 - ii -.

(5) 握,因此,需要將電路中所使用的元件模型建立起來,才能更有效地控制靜電放電防護 電路的寄生特性。本論文第五章建立起矽控整流器在高頻操作時的元件模型,以便利用 射頻電路與靜電放電防護電路共同設計的方式,設計出具有良好射頻效能以及優異靜電 放電防護能力的射頻積體電路。除了靜電放電防護元件以外,銲墊也會在訊號路徑上對 射頻訊號造成負面影響。本章針對一種具有低電容值的銲墊進行研究,利用其等效電路 模型進一步提出低損耗 (Loss) 設計,並於 65 奈米互補式金氧半製程中實現此設計。 實驗結果顯示,銲墊的等效電容可於特定頻段內大幅降低,同時訊號損耗也可降低,因 此可避免影響射頻電路之性能。 電源箝制靜電放電防護電路 (Power-Rail ESD Clamp Circuit) 是達成積體電路產品 全晶片靜電放電防護極為重要的設計,本論文第六章提出了新型的可耐高工作電壓以及 低漏電之靜電放電箝制電路。本章使用 65 奈米互補式金氧半製程實作,在此可耐高工 作電壓之靜電放電箝制電路中,所有電晶體都是利用低壓元件來實現,可以安全地偏壓 在兩倍工作電壓下而不會有閘極氧化層的可靠度問題,並且不需使用低漏電製程即可達 成降低漏電的目標。由實驗結果可知,此電路擁有極高的靜電放電能力,而且在正常操 作的情況下只有 100-nA 等級的漏電流,因此,本靜電放電箝制電路十分適合應用在系 統 單 晶 片 (System-on-a-Chip, SoC) 之 混 合 電 壓 輸 入 輸 出 界 面 (Mixed-Voltage I/O Interfaces)。 第七章總結本論文的研究成果,並提出數個接續本論文研究方向的研究題目。本論 文所提出的各項新型設計,皆已搭配實驗晶片加以驗證。此外,本研究有數篇國際期刊 與國際研討會論文發表,並有數項創新設計已提出中華民國及美國專利申請。. - iii -.

(6) - iv -.

(7) SCR-BASED ESD PROTECTION DESIGNS FOR RADIO-FREQUENCY INTEGRATED CIRCUITS IN FULLY SILICIDED CMOS PROCESS. Student: Chun-Yu Lin. Advisor: Dr. Ming-Dou Ker. Department of Electronics Engineering and Institute of Electronics National Chiao-Tung University. Abstract In order to be safely used and provide moderate life time, all microelectronic products must meet the reliability specifications during mass production. Electrostatic discharge (ESD), which was one of the most important reliability issues in the integrated circuit (IC), must be taken into consideration during the design phase of all IC products. All pads which connect the IC and the external world, including the input/output (I/O) pads, VDD pads, and VSS pads, need to be equipped with ESD protection circuits to provide effective ESD protection for the IC. Since the radio-frequency (RF) front-end circuits in wireless communication devices connect the RF transceiver to the external antenna or band-select filter, they must need ESD protections. However, the ESD protection devices at the I/O pads inevitably cause parasitic effects on the signal path. For the RF front-end circuits operating in the frequency band from several gigahertzes to tens of gigahertz, they have the strict limitations of the parasitic effects on the signal path in such high operating frequency. This situation leads to the challenge in ESD protection design for RF circuits, which is to achieve the highest ESD robustness with the smallest performance degradation. In other words, the parasitic effects of the ESD protection devices need to be minimized. Moreover, the evolution of CMOS process increases the difficulty of ESD protection design. As CMOS process is continuously scaled down, the power-supply voltage is decreased and the gate oxide becomes thinner, which leads -v-.

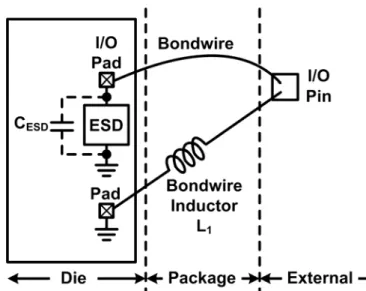

(8) to the reduced gate-oxide breakdown voltage of MOS transistor. However, ESD was not scaled down with the CMOS technology, so the MOS transistors with thinner gate oxide are more vulnerable to ESD. The aforementioned design challenges form the motivation of this dissertation. The research topics of this dissertation including: (1) ESD protection design on a 5-GHz differential low-noise amplifier with cross-coupled SCR, (2) optimization on SCR device with low capacitance for RF ESD protections, (3) ESD protection design on an ultra-wideband power amplifier with waffle-structured SCR, (4) modeling parasitic capacitance for matching network co-designed in RF ICs, and (5) high-voltage-tolerant ESD clamp circuit by using only low-voltage devices with low standby leakage in nanoscale CMOS process. In chapter 2, the pin-to-pin ESD protection design on a 5-GHz differential LNA is proposed. The 5-GHz differential LNA is implemented in a 130-nm CMOS process. The new ESD protection scheme for differential input pads is realized with the cross-coupled SCR. This ESD protection scheme achieves 3.5-kV HBM and 300-V MM ESD levels, respectively. SCR realized in waffle layout structure is proposed to improve ESD current distribution efficiency for ESD protection and to reduce the parasitic capacitance in chapter 3. The proposed waffle-structured SCR has been verified in a 0.18-µm CMOS process. The waffle layout structure of SCR can achieve smaller parasitic capacitance under the same ESD robustness. With smaller parasitic capacitance, the degradation on RF circuit performance due to ESD protection devices can be reduced. The proposed waffle SCR with low parasitic capacitance is suitable for on-chip ESD protection in RF ICs. Besides, the desired current to trigger on the SCR device with waffle layout structure and its turn-on time has also been investigated in silicon chip. In chapter 4, the waffle-structured SCR is applied to an ultra-wideband (UWB) RF power amplifier (PA). The waffle-structured SCR is designed with ESD detection and trigger circuit to provide the best ESD protection capability while contributing minimum parasitic capacitance to the RF PA in a 130-nm CMOS process. The measurement results have verified the effectiveness of the proposed ESD protection strategy and proved that this ESD protection technique indeed provides excellent ESD robustness of up to 8kV HBM ESD level and 800V MM ESD level. As the operating frequencies of RF front-end circuits are increased, on-chip ESD protection designs for RF applications are more challenging, and they should be designed more carefully. In chapter 5, the small-signal circuit model of waffle-structured SCR has been presented and proved in silicon. The measured parasitic capacitances well agree with the - vi -.

(9) simulated capacitances. The RF circuits can be well co-designed with the presented small-signal model to eliminate the negative impacts from ESD protection SCR on RF performances. Besides, the optimized design of the bond pad for RF applications was also investigated. The experimental results in a 65-nm CMOS process have proven that the bond pad capacitance and insertion loss can be successfully reduced by the optimized bond pad structure. The small-signal circuit model of the optimized bond pad has also been presented for RF circuit designs. The efficient power-rail ESD clamp circuit must be included into the RF ICs to reduce the dimensions of ESD devices connected to the I/O pad. In chapter 6, the new 2×VDD-tolerant ESD clamp circuit by using only low-voltage devices with low standby leakage current and high ESD robustness for system-on-a-chip (SoC) applications with mixed-voltage I/O interfaces has been successfully designed and verified in a 65-nm CMOS process. The 2×VDD-tolerant ESD clamp circuit can operate without gate-oxide reliability issue, and the leakage current is only in the order of 100 nA under normal circuit operating condition. Besides, there is no latchup concern in this design. The new ESD clamp circuit by using only low-voltage devices with very low standby leakage current and high ESD robustness is the useful circuit solution for on-chip ESD protection design with mixed-voltage I/O interfaces in SoC applications. In this dissertation, several novel designs have been proposed in the aforementioned research topics. Measured results of the fabricated test chips have demonstrated the performance improvement. The achievements of this dissertation have been published or submitted to several international journal and conference papers. Several innovative designs have been applied for patents.. - vii -.

(10) - viii -.

(11) Acknowledgment 在交通大學電子研究所的碩博士班生涯中,首先要感謝我的指導教授柯 明道教授三年多來的耐心指導與鼓勵,讓我能順利完成博士學業。除了專 業領域上的訓練,柯教授認真且積極的研究態度與明快且嚴謹的處事原 則,讓我學得如何快速解決問題、有效率地處理各項事務、並交出高水準 成果的正確態度與方式。作研究的過程雖然備感艱辛,但培養的能力將造 就無可取代的價值。柯教授為研究群同學爭取的許多福利,更讓人感念在 心。此外,還要感謝實驗室中另外三位教授:吳重雨校長、吳介琮教授、 陳巍仁教授給我的指導與建議。 感謝交通大學吳重雨校長、晶焱科技姜信欽博士、奇景光電陳東暘博 士、工業技術研究院吳文慶博士、中央大學邱煥凱教授、交通大學蘇朝琴 教授在百忙之中抽空擔任我的口試委員,並給予珍貴的指導與建議,讓此 博士論文更加完整。 感謝任職於聯華電子的唐天浩先生、黃新言先生、王暢資先生,與任職 於智原科技的蔡富義先生、彭彥華先生,鼎力協助實驗晶片下線與研究工 作進行,使本論文的研究成果得以成功驗證,並順利發表於國際期刊與國 際研討會。 感謝實驗室的前輩林昆賢博士、陳世倫博士、許勝福博士、張瑋仁博士、 陳榮昇博士、蕭淵文博士、陳世宏博士、顏承正博士、李健銘學長、郭秉 捷學長、王資閔學長、陳穩義學長、陳志豪學長、賴泰翔學長、黃俊學長、 王文傑博士、黃祖德學長、盧台祐學長、黃鈞正學長,以及蒙國軒、邱柏 硯、陸亭州、竹立煒、蔡惠雯、莊介堯、黃曄仁、林彥良、許哲綸、溫詠 儒、張堂龍等同學與學弟妹們在研究與生活上的協助與扶持。此外,感謝 實驗室助理卓慧貞小姐在行政事務上的許多協助。 最後,由衷感謝親愛的父親林宏聲先生、母親鄭瓊如女士、哥哥林群傑 先生,以及女友一路走來無悔的相伴。由於親人的鼓勵、支持、陪伴與照 顧,讓我能順利完成學業。感謝所有幫助我、陪伴我一同成長的師長、朋 友、學長姊、同學、學弟妹們,願大家平安喜樂。. 林 群 祐 誌於竹塹交大 九十八年 夏. - ix -.

(12) -x-.

(13) Contents. Abstract (Chinese). i. Abstract (English). v. Acknowledgment. ix. Contents. xi. Table Captions. xv. Figure Captions. xvii. 1. Introduction. 1. 1.1. Background of ESD Protection Design for RF Circuits 1.2. Review of RF ESD Protection Design Techniques. 1 10. 1.2.1. Stacked ESD Protection Devices. 10. 1.2.2. Parallel LC Resonator. 11. 1.2.3. LC-Tank. 13. 1.2.4. Series LC Resonator. 15. 1.2.5. Impedance Matching. 17. 1.2.6. Inductive ESD Protection. 19. 1.2.7. T-Coil. 20. 1.2.8. Distributed ESD Protection. 22. 1.2.9. Discussion and Comparison. 24. 1.3. Organization of This Dissertation. 26. 2. ESD Protection Design on A 5-GHz Differential Low-Noise Amplifier With High Pin-to-Pin ESD Robustness. 29. 2.1. Background. 29. 2.2. Low-Noise Amplifier Without ESD Protection. 30. 2.2.1. Differential LNA Design. 30. 2.2.2. Experimental Results. 33. - xi -.

(14) 2.3. Differential LNA With Conventional Double-Diode ESD Protection Scheme. 34. 2.3.1. Double-Diode ESD Protection Scheme. 34. 2.3.2. Power-Rail ESD Clamp Circuit. 35. 2.3.3. Experimental Results. 37. 2.3.4. Discussion on ESD Robustness. 38. 2.4. Differential LNA With New Proposed ESD Protection Scheme of Cross-Coupled SCR. 41. 2.4.1. New Proposed Cross-Coupled-SCR ESD Protection Scheme. 41. 2.4.2. Experimental Results. 44. 2.5. Summary. 48. 3. Optimization on SCR Device With Low Capacitance for RF ESD Protections. 51. 3.1. Background. 51. 3.2. SCR Structures. 53. 3.2.1. SCR With Stripe Layout. 53. 3.2.2. SCR With Waffle Layout. 55. 3.2.3. Modified SCR With Stripe Layout. 55. 3.2.4. Modified SCR With Waffle Layout. 57. 3.2.5. Metal Routing Strategy. 57. 3.3. Experimental Results and Discussion. 58. 3.3.1. Transmission Line Pulsing (TLP) Measurement. 58. 3.3.2. ESD Robustness. 58. 3.3.3. Parasitic Capacitance. 60. 3.3.4. Comparison on FOM. 61. 3.3.5. Trigger Mechanism. 62. 3.3.6. Turn-On Speed. 66. 3.3.7. Discussion. 68. 3.4. Summary. 68. 4. ESD Protection Design on An Ultra-Wideband Power Amplifier 71. With Waffle-Structured SCR - xii -.

(15) 4.1. Background. 71. 4.2. UWB Distributed Power Amplifier Basics. 71. 4.2.1. Conventional Architecture of UWB Class-AB PA. 71. 4.2.2. Load-line Design of Each Gm-Cell. 72. 4.2.3. Input and Output Line Design. 74. 4.2.4. Design Principle of the UWB Distributed Amplifier. 76. 4.3. ESD-Protected PA With Waffle-Structured SCR. 76. 4.3.1. UWB Class-AB Distributed PA Design. 76. 4.3.2. ESD Protection Design. 76. 4.3.3. PA With ESD Protection. 79. 4.4. Measured RF Performance After ESD Zapping. 87. 4.5. Summary. 92. 5. Modeling Parasitic Capacitance for Matching Network Co-Designed in RF ICs. 93. 5.1. Background. 93. 5.2. Modeling Parasitic Capacitance on Waffle-Structured SCR. 94. 5.2.1. Waffle-Structured SCR Design. 94. 5.2.2. Experimental results. 96. 5.3. Low-Capacitance and Low-Loss Bond Pad Design for RF ESD Applications in CMOS Technologies. 97. 5.3.1. Optimization on Low-Capacitance Bond Pad. 98. 5.3.2. Implementation on Low-Capacitance Bond Pad 5.4. Summary. 100 102. 6. High-Voltage-Tolerant ESD Clamp Circuit With Low Standby Leakage in Nanoscale CMOS Process. 105. 6.1. Background. 105. 6.2. ESD Protection Scheme With On-Chip ESD Bus for High-Voltage-Tolerant Mixed-Voltage I/O Buffer. 106. 6.3. Traditional Designs of High-Voltage-Tolerant ESD Clamp Circuits. 108. 6.4. New Design of High-Voltage-Tolerant ESD Clamp Circuit. 112. 6.4.1. Circuit Topology. 112. - xiii -.

(16) 6.4.2. 1×VDD-Tolerant ESD Detection Circuit. 113. 6.4.3. High-Voltage-Tolerant ESD Clamp Circuit. 115. 6.4.4. Experimental Results. 119. 6.5. Summary. 123. 7. Conclusions and Future Works. 125. 7.1. Main Results of This Dissertation. 125. 7.2. Future Works. 127. References. 129. Vita. 137. Publication List. 139. - xiv -.

(17) Table Captions. Chapter 1 Table 1.1. Comparison Among the ESD Protection Designs for RF Circuits. 26. Chapter 2 Table 2.2. HBM and MM ESD Robustness Under Different Test Pin Combinations. 34. Table 2.3. Comparison on ESD Robustness Among CMOS Differential LNAs. 49. Chapter 3 Table 3.1. Comparisons on Measured Device Characteristics of SCR Under Different Test Structures. 57. Chapter 4 Table 4.1. Summary of RF Performance of 3-GHz 0-dBm Narrowband Class-AB PA Before ESD Testing. 87. Table 4.2. Bandwidth and Gain of UWB RF PA After HBM ESD Zapping. 90. Chapter 5 Table 5.1. Dimension of Components Used in Small-Signal Model of Waffle-Structured SCR and Comparison on Measured Characteristics Under Different Device Spacing. 95. Table 5.2. Simulation Results on Insertion Loss as Each Component in Bond Pad Model Varied from Double to Half. 100. Chapter 6 Table 6.1. Comparison Among ESD Clamp Circuits. - xv -. 123.

(18) - xvi -.

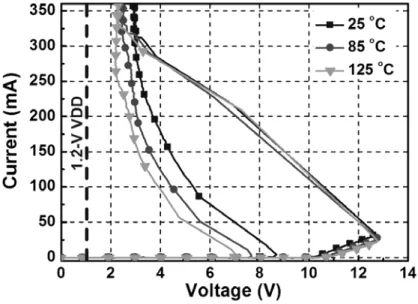

(19) Figure Captions. Chapter 1 Fig. 1.1.. Equivalent circuits of (a) HBM, and (b) MM, ESD tests.. 2. Fig. 1.2.. The typical design of on-chip ESD protection circuits in CMOS ICs.. 2. Fig. 1.3.. ESD-test pin combinations: (a) positive-to-VSS mode (PS-mode), (b) negative-to-VSS mode (NS-mode), (c) positive-to-VDD (PD-mode), and (d) negative-to-VDD (ND-mode).. 3. Fig. 1.4.. Pin-to-pin ESD tests: (a) positive mode, and (b) negative mode.. 3. Fig. 1.5.. VDD-to-VSS ESD tests: (a) positive mode, and (b) negative mode.. 4. Fig. 1.6.. Typical double-diode ESD protection scheme.. 4. Fig. 1.7.. ESD current paths in the typical double-diode ESD protection scheme under (a) PS-mode, (b) ND-mode, and (c) pin-to-pin, ESD stresses.. 5. Fig. 1.8.. Signal loss at input and output pads of IC with ESD protection devices.. 8. Fig. 1.9.. Block diagram of an ESD-protected RF receiver.. 9. Fig. 1.10. Block diagram of an LNA with ESD protection circuit. VS, RS, and RL denote the source voltage, source resistance, and load resistance, respectively.. 9. Fig. 1.11. Stacked ESD protection devices to reduce the parasitic capacitance.. 11. Fig. 1.12. An ideal parallel LC resonator and its simulated S21-parameters under different frequencies.. 12. Fig. 1.13. An example of ESD protection design with the parallel LC resonator.. 12. Fig. 1.14. Another example of ESD protection design with the parallel LC resonator, where the inductor LP provides ESD current path between VDD and the I/O pad.. 13. Fig. 1.15. ESD protection design with a pair of LC-tanks.. 14. Fig. 1.16. ESD protection design with stacked LC-tanks.. 14. - xvii -.

(20) Fig. 1.17. An ideal series LC resonator and its simulated S21-parameters under different frequencies.. 15. Fig. 1.18. An example of ESD protection design with the series LC resonator.. 16. Fig. 1.19. Another example of ESD protection design with the series LC resonator.. 16. Fig. 1.20. ESD protection design with modified series LC resonator, where only one inductor is connected in series with two ESD protection devices.. 17. Fig. 1.21. ESD protection design with impedance matching by using shunt and series components.. 18. Fig. 1.22. An example of ESD protection design with impedance matching.. 19. Fig. 1.23. Equivalent small-signal model of the schematic shown in Fig. 1.22.. 19. Fig. 1.24. Inductive ESD protection design for an LNA.. 20. Fig. 1.25. Inductive ESD protection design with transformer.. 20. Fig. 1.26. ESD protection design with T-coil.. 21. Fig. 1.27. ESD protection with T-diode.. 22. Fig. 1.28. Distribute ESD protection scheme.. 22. Fig. 1.29. Distribute ESD protection scheme with equal-size ESD diodes.. 23. Fig. 1.30. Distribute ESD protection scheme with decreasing-size ESD diodes.. 23. Fig. 1.31. π-model ESD protection scheme.. 24. Fig. 1.32. Distributed ESD protection scheme with the consideration for parasitic capacitance of I/O pad.. 24. Fig. 2.1.. Differential LNA without ESD protection for comparison reference.. 32. Fig. 2.2.. Measured S-parameters of the differential LNA without ESD protection.. 33. Fig. 2.3.. Differential LNA with conventional double-diode ESD protection scheme.. 35. Fig. 2.4.. Power-rail ESD clamp circuit realized with P-STSCR.. 36. Fig. 2.5.. Cross-sectional view and equivalent circuit of P-STSCR.. 36. Chapter 2. - xviii -.

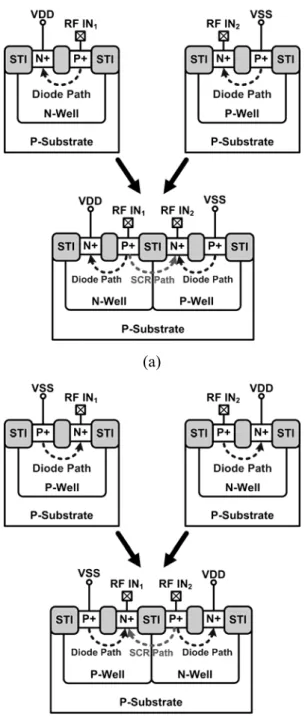

(21) Fig. 2.6.. Chip micrograph of differential LNA with conventional double-diode ESD protection scheme.. 37. Fig. 2.7.. Measured dc I–V curves of stand-alone SCR under different temperatures.. 38. Fig. 2.8.. ESD current paths in differential LNA with conventional double-diode ESD protection scheme under (a) PS-mode, and (b) ND-mode ESD stresses.. Fig. 2.9.. 40. ESD current path in differential LNA with conventional double-diode ESD protection scheme under pin-to-pin ESD stresses.. 41. Fig. 2.10. SEM picture at the failure points of differential LNA with conventional double-diode ESD protection scheme after 3-kV HBM pin-to-pin ESD test. The failure locations are all at the gate oxide of the input NMOS M1.. 41. Fig. 2.11. Establishing the SCR paths between the differential input pads by combining (a) DP1 (P+/N-well diode for RF IN1 pad) with DN2 (N+/P-well diode for RF IN2 pad), and (b) DP2 (P+/N-well diode for RF IN2 pad) with DN1 (N+/P-well diode for RF IN1 pad).. 43. Fig. 2.12. Differential LNA with proposed ESD protection scheme of cross-coupled SCR.. 44. Fig. 2.13. Chip micrograph of differential LNA with proposed cross-coupled-SCR ESD protection.. 44. Fig. 2.14. Measured S11-parameters of differential LNA with the proposed cross-coupled-SCR ESD protection scheme, and the original differential LNA without ESD protection.. 45. Fig. 2.15. Measured S21-parameters of differential LNA with the proposed cross-coupled-SCR ESD protection scheme, and the original differential LNA without ESD protection.. 46. Fig. 2.16. Measured S22-parameters of differential LNA with the proposed cross-coupled-SCR ESD protection scheme, and the original differential LNA without ESD protection.. 46. Fig. 2.17. Measured noise figures of differential LNA with the proposed cross-coupled-SCR ESD protection scheme, and the original differential LNA without ESD protection.. 47. Fig. 2.18. ESD current path in differential LNA with the proposed cross-coupled-SCR ESD protection scheme under pin-to-pin ESD stresses. - xix -. 48.

(22) Chapter 3 Fig. 3.1.. A general concept of on-chip ESD protection in RF ICs.. 52. Fig. 3.2.. Diagram of the low-noise amplifier (LNA) with ESD protection device.. 52. Fig. 3.3.. Device cross-sectional view and layout top view of (a) stripe SCR (SSCR), and (b) waffle SCR (WSCR).. 54. Fig. 3.4.. Equivalent circuit of the SCR device.. 54. Fig. 3.5.. Device cross-sectional view and layout top view of (a) stripe p-modified SCR (SPMSCR), (b) waffle p-modified SCR (WPMSCR), and (c) waffle n-modified SCR (WNMSCR).. Fig. 3.6.. 56. The TLP-measured current-voltage (I-V) characteristics of (a) SSCR and (b) WSCR.. Fig. 3.7.. 59. The dependence of TLP-measured Vtrigger on the trigger diffusion area of SCR devices with different layout structures.. Fig. 3.8.. 60. The layout top view with ground-signal-ground (G-S-G) pads and the equivalent model of (a) including-DUT pattern and (b) excluding-DUT. Fig. 3.9.. pattern.. 61. The extracted capacitances of the SCR devices from 2.4 GHz to 5 GHz.. 61. Fig. 3.10. The dependence of FOM (VMM/CESD) at 2.4 GHz under (a) positive and (b) negative ESD stresses on the trigger diffusion area of SCR devices under different layout structures.. 63. Fig. 3.11. Measurement setup to find the dc I-V curves of each WPMSCR devices under different trigger currents.. 63. Fig. 3.12. The dc I-V curves of (a) WPMSCR1, (b) WPMSCR2, and (c) WPMSCR3, under different trigger currents.. 64. Fig. 3.13. Dependences of the trigger voltages of WPMSCR devices on the trigger current.. 65. Fig. 3.14. Measurement setup to find the dc I-V curves of the base-emitter junction diode of WPMSCRs.. 65. Fig. 3.15. The dc I-V curves of the base-emitter junction diode of WPMSCRs.. - xx -. 66.

(23) Fig. 3.16. Measurement setup to find the turn-on time of WPMSCR devices under different voltage pulses.. 67. Fig. 3.17. The measured voltage waveforms on the anode of (a) WPMSCR1, (b) WPMSCR2, and (c) WPMSCR3, while the WPMSCR is triggering by the 5-V pulse into the trigger node.. 67. Fig. 3.18. Dependence of the turn-on time and the RP-well of WPMSCRs on the different trigger diffusion area.. 68. Fig. 4.1.. Conventional distributed amplifier architecture.. 72. Fig. 4.2.. Typical circuit implementation of the conventional distributed amplifier. Chapter 4. architecture.. 73. Fig. 4.3.. Loading condition of each Gm-cell.. 73. Fig. 4.4.. Distributed amplifier with artificial line.. 74. Fig. 4.5.. Detailed artificial line structure and corresponding design equations of (a) low-pass line, (b) high-pass line, and (c) band-pass line.. Fig. 4.6.. 75. Application of the waffle-structured SCR device in on-chip ESD protection design for RF ICs with low-capacitance consideration, and the discharging current path under (a) PS-mode, (b) PD-mode, (c) NS-mode, and (d) ND-mode ESD zapping.. 78. Fig. 4.7.. Measurement setup to find I-V characteristics of CR-triggered SCR.. 79. Fig. 4.8.. TLP-measured I-V characteristics of SCR with trigger circuit.. 79. Fig. 4.9.. Equivalent circuit of UWB RF PA with the proposed ESD protection circuit (ESD-protected PA).. 80. Fig. 4.10. Post-layout simulation on matching situations of (a) S11, and (b) S22, of the unprotected PA.. 81. Fig. 4.11. Post-layout simulation on power transmission of (a) S21, and (b) S12, of the unprotected PA.. 82. Fig. 4.12. Post-layout simulation results of (a) gain, and (b) OP1dB, vs. frequency of the unprotected PA.. 83. - xxi -.

(24) Fig. 4.13. Post-layout simulation on matching situations of (a) S11, and (b) S22, of the ESD-protected PA.. 84. Fig. 4.14. Post-layout simulation on power transmission of (a) S21, and (b) S12, of ESD-protected PA.. 85. Fig. 4.15. Post-layout simulation results of (a) gain, and (b) OP1dB, vs. frequency of ESD-protected PA.. 86. Fig. 4.16. Die photos of the fabricated (a) unprotected PA and (b) ESD-protected PA.. 88. Fig. 4.17. Measured results on S22-parameter of (a) unprotected PA, and (b) ESD-protected PA, after each HBM ESD zapping.. 89. Fig. 4.18. Measured results on S22-parameter of (a) unprotected PA, and (b) ESD-protected PA, after each MM ESD zapping.. 89. Fig. 4.19. Measured results on S21-parameter of (a) unprotected PA, and (b) ESD-protected PA, after each HBM ESD zapping.. 90. Fig. 4.20. Measured results on S21-parameter of (a) unprotected PA, and (b) ESD-protected PA, after each MM ESD zapping.. 90. Fig. 4.21. Measured results of OP1dB of (a) unprotected PA, and (b) ESD-protected PA, after each HBM ESD zapping.. 91. Fig. 4.22. Measured results of OP1dB of (a) unprotected PA, and (b) ESD-protected PA, after each MM ESD zapping.. 91. Chapter 5 Fig. 5.1.. Waffle-structured SCR: (a) layout top view and (b) device cross-sectional view and small-signal model.. Fig. 5.2.. 96. Measured and simulated parasitic capacitance (CSCR) of the waffle-structured SCR devices.. 97. Fig. 5.3.. Low-capacitance bond pad with stacked inductor.. 99. Fig. 5.4.. Layout top view of one test pattern for low-C pad with embedded inductor with one-port G-S-G pads.. Fig. 5.5.. 101. Extracted bond pad capacitance of each fabricated bond pad under different frequencies.. Fig. 5.6.. 102. Extracted insertion loss of each fabricated bond pad under different frequencies.. 102 - xxii -.

(25) Chapter 6 Fig. 6.1.. ESD protection scheme with on-chip ESD bus for high-voltage-tolerant mixed-voltage I/O buffer.. 107. Fig. 6.2.. Traditional design of 2×VDD-tolerant ESD clamp circuit.. 108. Fig. 6.3.. Traditional design of 3×VDD-tolerant ESD clamp circuit.. 109. Fig. 6.4.. Another traditional design of 3×VDD-tolerant ESD clamp circuit.. 111. Fig. 6.5.. Another traditional design of 2×VDD-tolerant ESD clamp circuit.. 112. Fig. 6.6.. New ESD clamp circuit with n×VDD-tolerant ESD detection circuit to trigger n×VDD-tolerant ESD clamp device.. 113. Fig. 6.7.. Implementation of 1×VDD-tolerant ESD detection circuit.. 114. Fig. 6.8.. Hspice-simulated results of 1×VDD-tolerant ESD detection circuit under normal power-on condition.. Fig. 6.9.. 115. Implementation of 2×VDD-tolerant ESD clamp circuit with 2×VDD-tolerant ESD detection circuit and SCR-based ESD clamp device.. 116. Fig. 6.10. Hspice-simulated results of 2×VDD-tolerant ESD clamp circuit under normal power-on condition: (a) at 25 °C, and (b) summary within 25 °C and 100 °C.. 117. Fig. 6.11. Hspice-simulated transient responses of 2×VDD-tolerant ESD clamp circuit.. 117. Fig. 6.12. Hspice-simulated results of 2×VDD-tolerant ESD detection circuit under ESD-like pulse zapping: (a) 5-V pulse, and (b) summary of different voltage pulse.. 118. Fig. 6.13. Layout top view of one test pattern with high-voltage-tolerant ESD clamp circuit.. 119. Fig. 6.14. TLP I-V curves of (a) 25-μm and (b) 50-μm DTSCR+diode without trigger PMOS.. 120. Fig. 6.15. TLP I-V curves of (a) 25-μm and (b) 50-μm DTSCR+diode with 25-μm trigger PMOS.. 120. Fig. 6.16. TLP I-V curves of (a) 25-μm and (b) 50-μm DTSCR+diode with 50-μm trigger PMOS.. 121 - xxiii -.

(26) Fig. 6.17. (a) HBM ESD robustness and (b) secondary breakdown current of ESD clamp circuits.. 122. Fig. 6.18. Measured dc holding voltages of ESD clamp circuits with (a) 25-μm and (b) 50-μm ESD clamp devices under room temperature.. - xxiv -. 122.

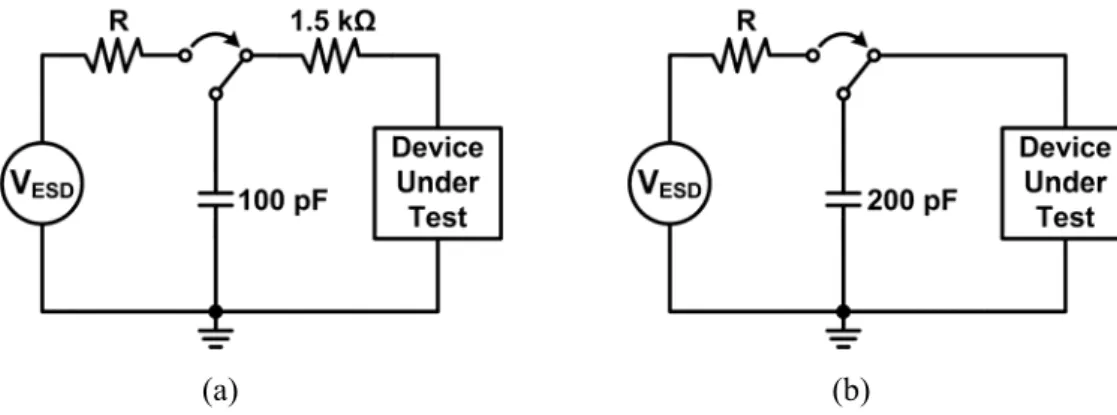

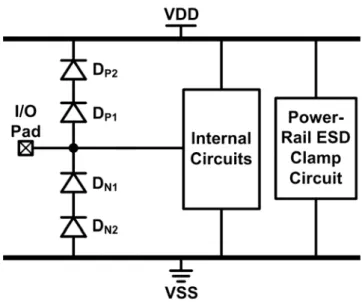

(27) Chapter 1 Introduction. In this chapter, the background and the organization of this dissertation are discussed. First, the electrostatic discharge (ESD) protection designs on radio-frequency (RF) circuits in fully silicided complementary metal-oxide-semiconductor (CMOS) processes are introduced. Then, the organization of this dissertation is described.. 1.1. Background of ESD Protection Design for Radio-Frequency Circuits RF circuits have been widely designed and fabricated in CMOS processes due to the advantages of high integration and low cost for mass production. ESD, which has become one of the most important reliability issues in IC products, must be taken into consideration during the design phase of all ICs [1]-[4], including the RF front-end circuits. Without ESD protection circuits at all I/O pads, the RF performance of a wireless transceiver can be easily damaged by ESD stresses, because RF front-end circuits are always fabricated in advanced CMOS processes. Usually the I/O pads are connected to the gate terminal of MOS transistor or silicided drain/source terminal, which leads to a very low ESD robustness if no ESD protection design is applied to the I/O pad. Once the RF front-end circuit is damaged by ESD, it can not be recovered and the RF functionality is lost. Therefore, on-chip ESD protection circuits must be provided for all I/O pads in ICs. Two common chip-level ESD test standards are human-body-model (HBM) and machine-model (MM) ESD test standards [5], [6]. HBM and MM ESD tests are used to evaluate the ESD robustness of the IC when it is touched by the charged human body or charged machine. The equivalent circuits of HBM and MM ESD tests are shown in Figs. 1.1(a) and 1.1(b), respectively. In order to protect the internal circuits against ESD stresses, ESD protection circuits must be provided at all I/O pads. Fig. 1.2 shows the concept of whole-chip ESD protection design.. -1-.

(28) (a). (b). Fig. 1.1.. Equivalent circuits of (a) HBM, and (b) MM, ESD tests.. Fig. 1.2.. Typical design of on-chip ESD protection circuits in CMOS ICs.. Fig. 1.3 shows the ESD-test pin combinations. ESD stresses may have positive or negative voltages on an I/O pin with respect to the grounded VDD or VSS pin. The typical ESD specifications for commercial IC products in HBM and MM are 2 kV and 200 V, respectively. For comprehensive ESD verification, the pin-to-pin ESD stresses and VDD-to-VSS ESD stresses had also been specified to verify the whole-chip ESD robustness, which are shown in Figs. 1.4 and 1.5, respectively.. -2-.

(29) Fig. 1.3.. (a). (b). (c). (d). ESD-test pin combinations: (a) positive-to-VSS mode (PS-mode), (b) negative-to-VSS. mode (NS-mode), (c) positive-to-VDD (PD-mode), and (d) negative-to-VDD (ND-mode).. (a) Fig. 1.4.. (b). Pin-to-pin ESD tests: (a) positive mode, and (b) negative mode.. -3-.

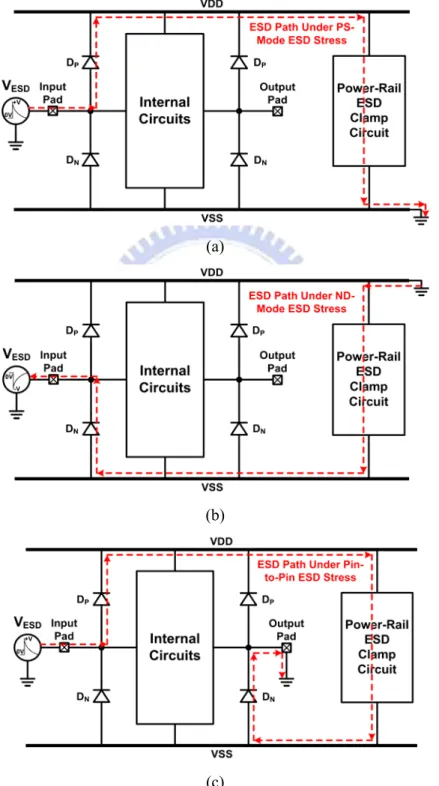

(30) (a) Fig. 1.5.. (b). VDD-to-VSS ESD tests: (a) positive mode, and (b) negative mode.. The typical on-chip double-diode ESD protection scheme is shown in Fig. 1.6, which two ESD diodes at I/O pad are co-designed with the power-rail ESD clamp circuit to prevent internal circuits from ESD damage [7]. In Fig. 1.6, a P+/N-well diode (DP) and an N+/P-well diode or an N-well/P-substrate diode (DN) are placed at input pad or output pad. When the DP and DN are under forward-biased condition, they can provide discharge paths from I/O pad to VDD and from VSS to I/O pad, respectively.. Fig. 1.6.. Typical double-diode ESD protection scheme.. Under positive-to-VDD mode (PD-mode) and negative-to-VSS mode (NS-mode) ESD stresses, ESD current is discharged through the forward-biased DP and DN, respectively. To avoid the ESD diodes from being operated under breakdown condition during positive-to-VSS mode (PS-mode) and negative-to-VDD mode (ND-mode) ESD stresses, which results in a substantially lower ESD robustness, the power-rail ESD clamp circuit is used between VDD and VSS to provide ESD current paths between the power rails [8]. Thus, -4-.

(31) ESD current is discharged from the I/O pad through the forward-biased DP to VDD, and discharged to the grounded VSS pin through the turn-on efficient power-rail ESD clamp circuit during PS-mode ESD stresses, as shown in Fig. 1.7(a). Similarly, ESD current is discharged from the VDD pin through the turn-on efficient power-rail ESD clamp circuit and the forward-biased DN to the I/O pad during ND-mode ESD stresses, as shown in Fig. 1.7(b).. (a). (b). (c) Fig. 1.7.. ESD current paths in the typical double-diode ESD protection scheme under (a) PS-mode,. (b) ND-mode, and (c) pin-to-pin, ESD stresses.. -5-.

(32) During pin-to-pin ESD stresses, ESD current flows from the zapped I/O pad through the forward-biased DP, the power-rail ESD clamp circuit, and the forward-biased DN to the grounded I/O pad, as shown in Fig. 1.7(c). Under VDD-to-VSS ESD tests, ESD current flows through the power-rail ESD clamp circuit between VDD and VSS. Since the power-rail ESD clamp circuit works independently between VDD and VSS, its parasitic effects do not have any impact on the internal circuits. With the turn-on efficient power-rail ESD clamp circuit, the ESD diodes can be assured to be operated in the forward-biased condition under all ESD test modes, which leads to higher ESD robustness. Although using power-rail ESD clamp circuit between VDD and VSS does not cause any effect on the internal circuits, applying ESD protection devices at the I/O pads inevitably introduce some negative impacts to circuit performance due to their parasitic effects. The main parasitic effect caused by ESD protection devices which deteriorates the high-frequency performance is the parasitic capacitance. Since the input signal swing is small at the RF input pad, it is sensitive to the shunt parasitic capacitance of ESD protection devices. Therefore, the parasitic capacitance of the ESD protection device at the RF input pad is strictly limited. For the RF transmitter, the devices in the output stage are implemented with large dimensions to transmit the output signals with large enough signal power. With proper design, the devices in the RF output stage can be used to protect the RF output pad against ESD stresses. Thus, ESD protection design for the input pad of the RF receiver is more challenging than that for the output pad of the RF transmitter. A typical request on the maximum loading capacitance of ESD protection device for a 2-GHz RF input pin was specified as only ~200 fF, which includes the parasitic capacitances of bond pad and ESD protection device [9]. Recently, the negative impacts of ESD protection devices to RF circuit performance had been investigated [10], [11], which had demonstrated that the RF performance such as power gain and noise figure are significantly degraded by the parasitic capacitance of ESD protection devices. The impacts become more serious as the operating frequency of RF front-end circuits increases. Thus, the parasitic capacitance of ESD protection device must be minimized in ESD protection design for high-frequency applications. Generally, ESD protection circuits cause RF performance degradation with several undesired effects, which are will be discussed in the following. Parasitic capacitance is one of the most important design considerations for RF ICs. Conventional ESD protection devices with large dimensions have the parasitic capacitance which is too large to be tolerated for RF front-end circuits. As shown in Fig. 1.8, the parasitic -6-.

(33) capacitance of ESD protection devices causes signal loss from the pad to ground. Moreover, the parasitic capacitance also changes the input matching condition. Consequently, the noise figure is deteriorated and the power gain is decreased. Noise factor is one of the most important merits for RF receivers. Since the RF receiver is a cascade of several stages, the overall noise factor of the RF receiver can be obtained in terms of the noise factor and power gain of each stage in the receiver. For example, if there are m stages cascaded in the RF receiver, the total noise factor of the RF receiver can be expressed as [12]. Ftotal = 1 + ( F1 − 1) +. Fm − 1 F2 − 1 + ⋅⋅⋅ + G p1 G p1 ⋅⋅⋅ G p( m −1). (1.1). where Fi and Gpi are the noise factor and the power gain of the i-th stage, respectively. According to (1.1), the noise factor contributed by the first stage is the dominant factor to the total noise factor of the RF receiver (Ftotal). With the ESD protection circuit added at the input pad to protect the RF receiver IC against ESD damages, the ESD protection circuit becomes the first stage in the RF receiver IC, which is shown in Fig. 1.9. For simplicity, only the first two stages, which are the ESD protection circuit and the low-noise amplifier (LNA), are taken into consideration, as shown in Fig. 1.10. The overall noise factor (FLNA_ESD) of the LNA with ESD protection circuit is. FLNA _ ESD = FESD +. FLNA − 1 G. (1.2). where G is the power gain of the LNA, and FESD and FLNA denote the noise factors of the ESD protection and LNA circuits, respectively. Thus, the noise factor of the ESD protection circuit must be minimized, because it directly increases the total noise factor of the RF receiver and the increased noise factor can not be suppressed by the power gains of succeeding stages. Moreover, the signal loss due to the ESD protection circuit would also cause power gain degradation in RF circuits.. -7-.

(34) Fig. 1.8.. Signal loss at input and output pads of IC with ESD protection devices.. Another negative impact caused by the ESD protection circuit is the input impedance mismatching, which is particularly critical for narrow band RF circuits. With the ESD protection circuit added at the input node, the original input matching condition is changed by the parasitic capacitance from the ESD protection circuit. As a result, the center frequency of the narrow band RF circuit is shifted and the power gain is decreased due to impedance mismatching. The impedance mismatching due to ESD protection devices can be mitigated by co-designing the ESD protection circuit and the input matching network. With the co-design of ESD protection scheme and input matching network, the operating frequency can be tuned to the desired frequency. However, the noise figure is definitely increased after ESD protection circuit is added because more devices indicate more noise sources. Besides the impacts caused by ESD protection device on RF front-end circuits, the parasitic capacitance of the ESD protection device causes signal loss from the pad to ground, which decreases the signal swings. Moreover, RC delay is another impact caused by the ESD protection circuit. With the ESD protection circuit added to the input and output pads, the parasitic capacitance and parasitic resistance from the ESD protection device and the interconnection introduce RC delay to the input and output signals. Thus, the rising and falling time of the signals at the I/O pads with ESD protection become longer.. -8-.

(35) Fig. 1.9.. Fig. 1.10.. Block diagram of an ESD-protected RF receiver.. Block diagram of an LNA with ESD protection circuit. VS, RS, and RL denote the source. voltage, source resistance, and load resistance, respectively.. In addition to parasitic capacitance, the requirements of ESD protection device characteristics under ESD stresses introduce some design considerations. To provide effective ESD protection, the voltage across the ESD protection device during ESD stresses should be carefully designed. First, the trigger voltage and holding voltage of ESD protection device must be designed lower than the gate-oxide breakdown voltage of MOS transistors to prevent the internal circuits from damage before the ESD protection device is turned on during ESD stresses. Second, the trigger voltage and holding voltage of the ESD protection device must be higher than the power-supply voltage of the IC to prevent the ESD protection devices from being mis-triggered under normal circuit operating conditions. Moreover, the turn-on resistance of ESD protection device should be minimized in order to reduce the joule heat generated in the ESD protection device and the voltage across the ESD protection device during ESD stresses. As CMOS process is continuously scaled down, the power-supply voltage is decreased and the gate oxide becomes thinner, which leads to reduced gate-oxide breakdown voltage of MOS transistor. Typically, the gate-oxide breakdown voltage is decreased to only ~5 V in a 65-nm CMOS process with gate-oxide thickness of ~15 Å. As a result, the ESD design window, defined as the difference between the gate-oxide breakdown voltage of the MOSFET and the power-supply voltage of the IC, becomes narrower in nanoscale CMOS technologies [13]. Furthermore, ESD protection circuits need to be quickly -9-.

(36) turned on during ESD stresses in order to provide efficient discharge paths in time. In summary, ESD protection design becomes more challenging in nanoscale CMOS technologies.. 1.2. Review of RF ESD Protection Design Techniques To mitigate the performance degradation due to ESD protection devices, circuit design techniques had been used to reduce the parasitic capacitance from the ESD protection device. In this section, the ESD protection designs in standard CMOS processes are reviewed.. 1.2.1. Stacked ESD Protection Devices Fig. 1.6 has show the conventional double-diode ESD protection design for RF frond-end circuits; however, it is only suitable for small ESD protection devices [14]. The device dimensions of ESD diodes should be decreased to reduce the parasitic capacitance at I/O pad, and then the performance degradation caused by the parasitic capacitances from the ESD diodes could be reduced. However, ESD robustness needs to be maintained, so the minimum device dimensions of ESD diodes can not be shrunk unlimitedly. In order to further reduce the parasitic capacitance from ESD diodes without sacrificing ESD robustness, the ESD diodes in stacked configuration had been proposed, as shown in Fig. 1.11 [15], [16]. The overall equivalent parasitic capacitance will theoretically becomes CESD/n, where CESD is the parasitic capacitance of each ESD protection device and n ESD protection devices are stacked. Thus, more stacked ESD devices lead to the more significant parasitic capacitance reduction. Besides reducing parasitic capacitance, using the stacked configuration can also reduce the leakage current of ESD diodes under normal circuit operating conditions. Although stacked ESD protection devices can reduce the parasitic capacitance and leakage current, this technique is adverse to ESD protection because the overall turn-on resistance and the voltage across the stacked ESD protection devices during ESD stresses were increased as well.. - 10 -.

(37) Fig. 1.11.. Stacked ESD protection devices to reduce the parasitic capacitance.. 1.2.2. Parallel LC Resonator This technique was also called the impedance cancellation, which was composed of a resonant with the parallel inductor and capacitor. In such a resonator, the resonant frequency (ωo) is. ωo =. 1 LC. (1.3). where L and C denote inductance and capacitance, respectively. An ideal parallel LC resonator and the simulated S21-parameters under different frequencies are shown in Fig. 1.12. The signal loss at the resonant frequency is ideally zero, which means that the equivalent capacitance at the resonant frequency is zero. Based on this concept, the ESD protection circuit with a parallel inductor had been proposed, as shown in Fig. 1.13 [17]-[21]. Using the inductance of L1, it was designed to resonate with the parasitic capacitance of the ESD protection device at the operating frequency of the RF front-end circuit. With the parallel LC network resonating at the operating frequency, the shunt impedance of the resonator becomes very large, which can effectively suppress signal loss. Therefore, the ESD protection design using parallel LC resonator can mitigate the impacts on RF performances for circuits operating in a narrow frequency band.. - 11 -.

(38) Fig. 1.12.. An ideal parallel LC resonator and its simulated S21-parameters under different. frequencies.. Fig. 1.13.. An example of ESD protection design with the parallel LC resonator.. Besides the bondwire inductor L1, the inductor can also be realized by the on-chip inductor [17]-[20]. Furthermore, the inductor can not only resonates with the parasitic capacitance of the ESD protection device but also serves as an ESD protection device by itself. In this configuration, the parallel LC resonator can be realized as shown in Fig. 1.14 [22]. Since VDD is an ac ground node, the inductor LP is connected between the I/O pad and VDD with the ESD protection device between the I/O pad and VSS to form a parallel LC resonator. The inductor LP also serves as an ESD protection device between I/O pad and VDD. The inductor and the parasitic capacitance of the ESD protection device are designed to resonate at the operating frequency of the RF front-end circuit to minimize performance - 12 -.

(39) degradation caused by the ESD protection device. With an inductor directly connected between the I/O pad and VDD, the ESD protection device is reverse biased with the largest possible dc voltage under normal circuit operating conditions, which leads to the minimum the parasitic PN-junction capacitance in the ESD protection device. The placement of the inductor and the ESD protection device can be interchanged to provide the same function. It should be noted that the dc biases in this configuration must be equal on both sides of the inductor. A dc blocking capacitor Cblock is required to provide a separated dc bias for the internal circuits.. Fig. 1.14. Another example of ESD protection design with the parallel LC resonator, where the inductor LP provides ESD current path between VDD and the I/O pad.. 1.2.3. LC-Tank LC-tank has been reported for the low-capacitance ESD protection design, which consists of an inductor, a capacitor, and an ESD diode [23]-[28]. As shown in Fig. 1.15, a pair of the LC-tanks was placed at the I/O pad. One LC-tank consists of the inductor LP and the capacitor C1, which is placed between the I/O pad and ESD diodes DP. Another LC-tank consists of the inductor LN and the capacitor C2, which is placed between the I/O pad and ESD diodes DN. These ESD diodes DP and DN are used to block the steady leakage current path from VDD to VSS under normal circuit operating conditions. Furthermore, the capacitors C1 and C2 can also be realized with the ESD protection devices. At the resonant frequency of the LC-tank, there is ideally infinite impedance from the signal path to the ESD diode. Consequently, the parasitic capacitances of the ESD protection devices are isolated, which can mitigate the parasitic effects from the ESD protection devices. - 13 -.

(40) To further reduce the parasitic capacitance from the ESD protection devices, the modified design with stacked LC-tanks had also been proposed, as shown in Fig. 1.16 [24]-[27]. Two or more LC-tanks are stacked to provide better impedance isolation at resonant frequency, and the impacts of the ESD protection devices can be significantly reduced.. Fig. 1.15.. ESD protection design with a pair of LC-tanks.. Fig. 1.16.. ESD protection design with stacked LC-tanks.. - 14 -.

(41) 1.2.4. Series LC Resonator The narrow band ESD protection design can be achieved by using the parallel LC resonator. For the wideband RF front-end circuits, the series LC resonator can be used for ESD protection. The simulated S21-parameter of an ideal series LC resonator under different frequencies is shown in Fig. 1.17. With inductance L and capacitance C in the series LC resonator, the resonant frequency (ωo) is identical to that shown in (1.3). There is a notch at the resonant frequency, where the signal loss is very large, and the signal will be totally lost. However, at frequencies above the resonant frequency, the magnitude of impedance increases, which means the signal loss becomes much smaller. Thus, wideband ESD protection can be achieved by designing the application band of the series LC resonator to cover the frequency band of the RF signal. Fig. 1.18 shows the ESD protection design utilizes the series LC resonator [17]-[20]. The inductance of L1 and the parasitic capacitance of the ESD protection device (CESD) are designed to resonate. During ESD stresses, the ESD current can be discharged through the inductor L1 and the ESD protection device.. Fig. 1.17.. An ideal series LC resonator and its simulated S21-parameters under different frequencies.. - 15 -.

(42) Fig. 1.18.. An example of ESD protection design with the series LC resonator.. Another example of ESD protection design utilizing the series LC resonator is shown in Fig. 1.19 [29]-[31], where a pair of the series LC resonators was placed at the I/O pad. ESD current paths from the I/O pad to both VDD and VSS are provided by the inductors and the ESD protection devices. To reduce the inductors used in the series LC resonators, a modified design used only one inductor is shown in Fig. 1.20 [29]-[31]. One inductor is connected in series with two ESD protection devices connected to VDD and VSS. Because the capacitance in the series LC resonator is the sum of the parasitic capacitances of two ESD protection devices, the inductance used in Fig. 1.20 is smaller than that used in Fig. 1.19 under the same resonant frequency. Consequently, total cost can be reduced in this modified design.. Fig. 1.19.. Another example of ESD protection design with the series LC resonator.. - 16 -.

(43) Fig. 1.20. ESD protection design with modified series LC resonator, where only one inductor is connected in series with two ESD protection devices.. 1.2.5. Impedance Matching The size of ESD protection devices must be large enough to perform good ESD robustness. However, parasitic effects will increase with the large ESD protection devices. To solve this dilemma, ESD protection devices can be treated as a part of the impedance matching network. By co-designing the ESD protection circuit and the impedance matching network, large ESD protection devices can be used to achieve high ESD robustness with their parasitic capacitance matched. The impedance matching technique of ESD protection device had been proposed in [32]-[35]. Fig. 1.21 shows the ESD protection circuit with the impedance matching design. In this design, ESD current can be discharged from the I/O pad through the ESD protection devices to VDD and VSS. The combined impedance of the shunt and series impedance is designed to provide impedance matching at the I/O pad with ESD protection [32], [33]. The shunt and series impedance can be realized by various circuit components.. - 17 -.

(44) Fig. 1.21.. ESD protection design with impedance matching by using shunt and series components.. One example of ESD protection design with impedance matching technique is shown in Fig. 1.22, where uses inductance to match the parasitic capacitances of ESD protection devices [34]. The ESD protection devices are placed next to the I/O pad, and provide ESD protection for the internal circuits. The transmission line (T-Line) connects to the external components. The inductive component L, which can be an inductor or a transmission line, is connected in series with the signal line, and matches the parasitic capacitances of the ESD protection devices, internal circuits, bond pad, and termination element (RT). The small-signal equivalent circuit model of this matching network is shown in Fig. 1.23, where the inductive component L separates two parasitic capacitances C1 and C2. These C1 and C2 are. C1 = Cint + C RT. (1.4). C2 = CPad + CESD. (1.5). and. where Cint, CRT, CPad, and CESD denote the parasitic capacitance at the input node of the internal circuit, the parasitic capacitances of the termination element, bond pad, and ESD protection devices, respectively. The design goal is to neutralize the capacitance of C1 and C2 at the operating frequency by using the inductance of L. Therefore, the design target is. X C1 + X C 2 + X L = 0. (1.6). where XC1, XC2, and XL are the reactance of C1, C2, and L, respectively. The overall impedance matching can be achieved as (1.6) holds.. - 18 -.

(45) Fig. 1.22.. An example of ESD protection design with impedance matching.. Fig. 1.23.. Equivalent small-signal model of the schematic shown in Fig. 1.22.. 1.2.6. Inductive ESD Protection ESD protection design for RF circuits by using inductor as the ESD protection device has been reported [36], [37]. In Fig. 1.24, the ESD protection inductor (LESD) is placed between the input pad and VSS. Inductors exhibits higher impedance at higher frequencies. Since the frequency component of ESD is much lower than that of the RF signal, the inductor can pass the ESD currents while block the RF signal. In the inductor-based ESD protection design, LESD was selected to resonate with the parasitic capacitances at the RF operating frequency. Therefore, the parasitic effects of the ESD protection inductor are compensated. To efficiently sink the ESD current, the metal width of the ESD protection inductor should be wide enough to enhance the current handling capability and the parasitic series resistance. However, inductors realized very wide metal traces occupy large chip area. This is the main design concern in the inductor-based ESD protection. Besides, an ac coupling capacitor Cc is needed in this design to avoid the steady leakage current through the ESD protection inductor. Another inductor-based ESD protection design is shown in Fig. 1.25. The ESD protection inductor can be merged with the gate inductor to save the chip area, since most of the LNAs need a gate inductor connected between the input pad and the gate terminal of the - 19 -.

(46) input MOS transistor [38]. The ESD protection inductor is placed under the gate inductor to form a transformer. Consequently, the transformer-based ESD protection design provides not only the gate inductor in the impedance matching network, but also the ESD protection for the input pad.. Fig. 1.24.. Inductive ESD protection design for an LNA.. Fig. 1.25.. Inductive ESD protection design with transformer.. 1.2.7. T-Coil The ESD protection design with T-coil for wideband applications had been reported [39]. As shown in Fig. 1.26, this circuit can provide a purely resistive input impedance of RT, under the proper impedance matching design. Once the following conditions hold, the input impedance Zin remains resistive at all frequencies:. L1 = L2 =. CL RT 2 ⎛ 1 ⎞ ⎜1 + 2 ⎟ 4 ⎝ 4ζ ⎠. - 20 -. (1.7).

(47) CL 16ζ 2. (1.8). 4ζ 2 − 1 4ζ 2 + 1. (1.9). CB = and. k=. where ζ is the damping factor of the network transfer function VX/Iin. In the T-coil-based ESD protection design, CL can be realized by the parasitic capacitance of ESD protection device. Therefore, large ESD protection device can be used without degrading the RF performances. The NMOS and PMOS transistors with gate-coupled technique is used in the first ESD protection design with T-coil. Recently, the silicon-controlled rectifier (SCR) has been used as the ESD protection device in the T-coil-based ESD protection design for a high-speed transmitter [40]. The return loss of the transmitter was improved with the T-coil to compensate the parasitic effects of the SCR.. Fig. 1.26.. ESD protection design with T-coil.. It has been reported that the transformer plus diode (T-diode) is used to protect the wideband LNA [41], as shown in Fig. 1.27. This is another T-coil-based ESD protection design. In this design, the capacitor CB in the T-diode was realized with the parasitic capacitance between the inductors L1 and L2. Since the T-coil and the T-diode can overcome the band-limiting problems in the narrow band ESD protection circuits, they are suitable for wideband RF front-end circuits. However, the design concern for the T-coil-based ESD protection was the inductor L1, which must be - 21 -.

(48) realized by wide metal trace and occupied large chip area.. Fig. 1.27.. ESD protection with T-diode.. 1.2.8. Distributed ESD Protection The distributed ESD protection scheme had been proposed to achieve wideband impedance matching with ESD protection devices [42]-[44]. The ESD protection devices are divided into several sections and are impedance matched by the transmission lines (T-lines) or inductors, as shown in Fig. 1.28. With the ESD protection devices divided into small sections and matched by the transmission lines, such a distributed ESD protection scheme can achieve wideband impedance matching. The number of ESD protection devices can be varied to optimize the performance. The first reported distributed ESD protection scheme is the equal-size distributed ESD (ES-DESD) protection scheme with ESD diodes, as shown in Fig. 1.29. In the ES-DESD protection scheme, the ESD protection diodes are equally divided into four sections. However, most of ESD current is expected to flow through the section which is closest to the I/O pad. To improve ESD robustness of distributed ESD protection scheme, the modified design of the decreasing-size distributed ESD (DS-DESD) protection scheme had been reported [45].. Fig. 1.28.. Distribute ESD protection scheme.. - 22 -.

(49) Fig. 1.29.. Distribute ESD protection scheme with equal-size ESD diodes.. The DS-DESD protection scheme is shown in Fig. 1.30, which allocates the ESD protection devices with decreasing sizes from the I/O pad to the internal circuit. With larger ESD protection devices close to the I/O pad, ESD robustness is improved. Because the first section of the ESD protection devices in the DS-DESD protection scheme is larger than that in the ES-DESD protection scheme, the DS-DESD protection scheme had been proven to have higher ESD robustness than that of the ES-DESD protection scheme under the same total parasitic capacitance of the ESD protection devices. Moreover, it had also been verified that good wideband impedance matching is still maintained in the DS-DESD protection scheme. However, in these ES-DESD and DS-DESD protection circuits, the de-embedding calculation must be executed to remove the parasitic effects of the I/O pads, and extract the intrinsic characteristics.. Fig. 1.30.. Distribute ESD protection scheme with decreasing-size ESD diodes.. - 23 -.

(50) Considering the parasitic capacitance of I/O pad (CPad), the π-model ESD protection scheme was shown in Fig. 1.31 [46]. The π-model ESD protection scheme consists of one set of ESD protection devices close to the I/O pad, the other set close to the internal circuits, and a transmission line matching these parasitic capacitances. The π-model ESD protection scheme can also be designed to achieve good wideband impedance matching with ESD protection devices. Another distributed ESD protection scheme with the consideration of the capacitive I/O pad is shown in Fig. 1.32 [47]. The wideband impedance matching can be obtained by scaling these ESD protection devices and the transmission lines. Besides, this scheme can be suitable for wideband RF ESD protection with the large tolerance for the parasitic capacitance of I/O pad.. Fig. 1.31.. π-model ESD protection scheme.. Fig. 1.32.. Distributed ESD protection scheme with the consideration for parasitic capacitance of I/O. pad.. 1.2.9. Discussion and Comparison The comparison among various ESD protection designs for RF circuits is summarized in Table 1.1. The evaluated parameters are explained as following.. - 24 -.

(51) z. Design Complexity: − “Low”: The stand-alone ESD protection device is the ESD protection circuit. without extra auxiliary component. − “Moderate”: The stand-alone ESD protection device is the ESD protection circuit. without extra auxiliary component, but the layout of the ESD protection device needs careful consideration. − “High”: Besides the ESD protection device, extra auxiliary components are needed,. and the auxiliary components should be carefully designed. z. Parasitic Capacitance: − “Small”: The parasitic capacitance of the ESD protection circuit at the I/O pad can. be very small with proper design. − “Moderate”: The parasitic capacitance of the ESD protection circuit at the I/O pad. is moderate for RF applications. − “Large”: The parasitic capacitance of the ESD protection circuit at the I/O pad is. large for RF applications. z. ESD Robustness: − “Poor”: ESD robustness of the ESD protection design is poor. − “Moderate”: ESD robustness of the ESD protection design is moderate. − “Good”: ESD robustness of the ESD protection design is good. − “Adjustable”: For some ESD protection designs by circuit solutions, ESD. robustness can be adjusted by using different ESD protection devices and dimensions. z. Area Efficiency: − “Poor”: The area efficiency of the ESD protection design is poor. − “Moderate”: The area efficiency of the ESD protection design is moderate. − “Good”: The area efficiency of the ESD protection design is good.. According to Table 1.1, most of the reported ESD protection designs need additional components to lower the parasitic capacitance. As a result, the chip area is substantially increased, which in turn increases the fabrication cost. Moreover, characteristics of the ESD protection device and the additional components need to be carefully investigated to minimize the undesired effects. Among the ESD protection devices, silicon-controlled rectifier (SCR) is a promising device because it has both good ESD robustness and low parasitic capacitance under a small - 25 -.

(52) layout area. Besides, the holding voltage and turn-on resistance of SCR are quite low. As the power-supply voltage of ICs decreases to be less than SCR’s holding voltage, the latchup issue is avoided. These factors reveal the advantages of SCR devices. With suitable trigger circuit to enhance the turn-on speed and to reduce the trigger voltage, SCR could be the most promising component in the ESD protection design for RF applications. Table 1.1 Comparison Among the ESD Protection Designs for RF Circuits ESD Protection Design. Design Complexity. Parasitic Capacitance. ESD Robustness. Area Efficiency. Stacked ESD Protection Devices. Low. Moderate. Moderate. Good. Parallel LC Resonator. High. Small. Adjustable. Poor. LC-Tank. High. Small. Adjustable. Poor. Series LC Resonator. High. Small. Adjustable. Poor. Impedance Matching. High. Small. Adjustable. Poor. Inductive ESD Protection. High. Small. Adjustable. Poor. T-Coil. High. Small. Adjustable. Poor. Distributed ESD Protection. High. Small. Adjustable. Poor. 1.3. Organization of This Dissertation In order to solve the challenges of ESD protection design for RF circuits, several new SCR-based ESD protection designs are proposed and verified in this dissertation. This dissertation consists of seven chapters. In chapter 2, the pin-to-pin ESD protection design on a 5-GHz differential LNA is investigated. In chapter 3, SCR realized in waffle layout structure is proposed to improve ESD current distribution efficiency for ESD protection and to reduce the parasitic capacitance. With the reduced parasitic capacitance, the waffle-structured SCR co-designed with RF power amplifier (PA) was investigated in chapter 4. In chapter 5, the small-signal model of SCR in RF frequency band is presented firstly. With the matching network co-design between SCR device and RF circuits, the parasitics of the SCR device can be cancelled. Besides, with the consideration of low standby leakage in nanoscale CMOS processes, a new 2×VDD-tolerant ESD clamp circuit by using only 1×VDD devices was presented in chapter 6. The outlines of each chapter are summarized below. In chapter 2, the pin-to-pin ESD protection design on a 5-GHz differential LNA is - 26 -.

(53) proposed. The new ESD protection scheme for differential input pads is realized with the cross-coupled SCR. Verified in a 130-nm CMOS process, this ESD protection scheme achieves 3.5-kV HBM and 300-V MM ESD levels, respectively. In chapter 3, SCR realized in waffle layout structure is proposed to improve ESD current distribution efficiency for ESD protection and to reduce the parasitic capacitance. The proposed waffle-structured SCR has been verified in a 0.18-µm CMOS process. The waffle layout structure of SCR can achieve smaller parasitic capacitance under the same ESD robustness. With smaller parasitic capacitance, the degradation on RF circuit performance due to ESD protection devices can be reduced. The proposed waffle SCR with low parasitic capacitance is suitable for on-chip ESD protection in RF ICs. Besides, the desired current to trigger on the SCR device with waffle layout structure and its turn-on time has also been investigated in silicon chip. With the reduced parasitic capacitance, the waffle-structured SCR is applied to an ultra-wideband (UWB) RF power amplifier (PA) in chapter 4. The waffle-structured SCR is designed with ESD detection and trigger circuit to provide the best ESD protection capability while contributing minimum parasitic capacitance to the RF PA in a 130-nm CMOS process. The measurement results have verified the effectiveness of the proposed ESD protection strategy and proved that this ESD protection technique indeed provides excellent ESD robustness of up to 8kV HBM ESD level and 800V MM ESD level. As the operating frequencies of RF front-end circuits are increased, on-chip ESD protection designs for RF applications are more challenging, and they should be designed more carefully. In chapter 5, the small-signal circuit model of waffle-structured SCR has been presented and proved in silicon. The measured parasitic capacitances well agree with the simulated capacitances. The RF circuits can be well co-designed with the presented small-signal model to eliminate the negative impacts from ESD protection SCR on RF performances. Besides, the optimized design of the bond pad for RF applications was also investigated. The experimental results in a 65-nm CMOS process have proven that the bond pad capacitance and insertion loss can be successfully reduced by the optimized bond pad structure. The small-signal circuit model of the optimized bond pad has also been presented for RF circuit designs. In order to reduce the parasitic effects of ESD devices connected to the I/O pad, the efficient power-rail ESD clamp circuit must be included into the RF ICs. In chapter 6, the new 2×VDD-tolerant ESD clamp circuit by using only low-voltage devices with low standby leakage current and high ESD robustness for SoC applications with mixed-voltage I/O - 27 -.

(54) interfaces has been successfully designed and verified in a 65-nm CMOS process. The 2×VDD-tolerant ESD clamp circuit can operate without gate-oxide reliability issue, and the leakage current is only in the order of 100 nA under normal circuit operating condition. Besides, there is no latchup concern in this design. The new ESD clamp circuit by using only low-voltage devices with very low standby leakage current and high ESD robustness is the useful circuit solution for on-chip ESD protection design with mixed-voltage I/O interfaces in SoC applications. Chapter 7 summarizes the main results of this dissertation. Some suggestions for the future works are also addressed in this chapter.. - 28 -.

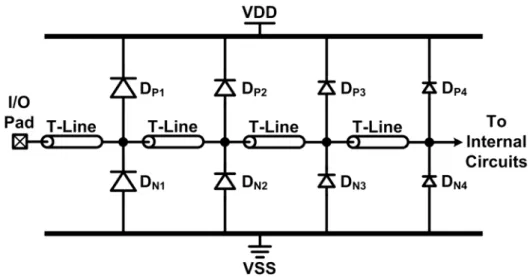

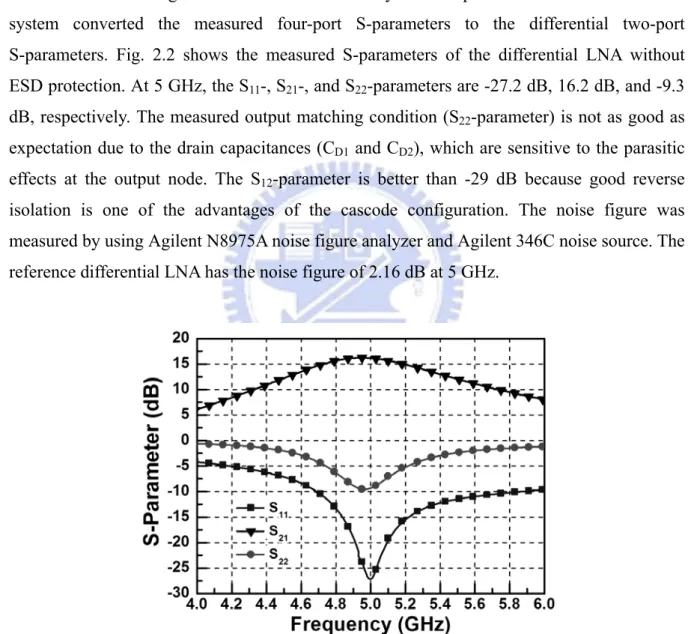

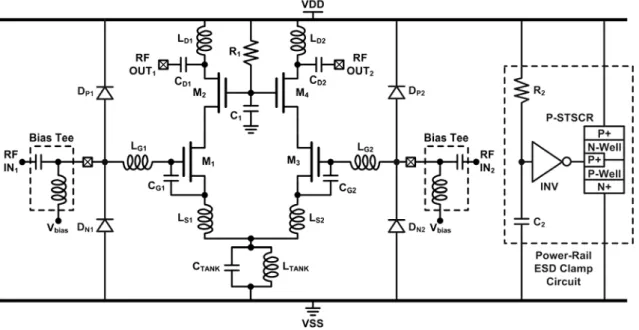

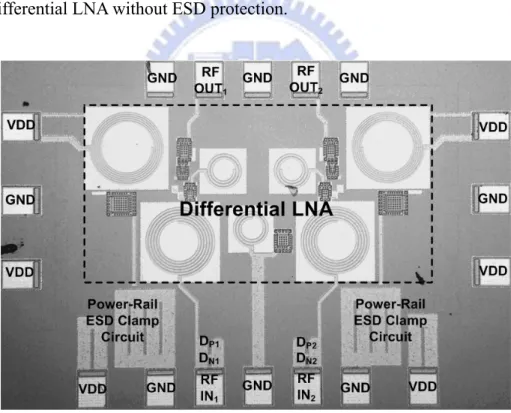

(55) Chapter 2 ESD Protection Design on A 5-GHz Differential Low-Noise Amplifier With Cross-Coupled SCR. In the typical ESD protection design, the ESD test results have shown that the pin-to-pin ESD stress is the most critical ESD-test pin combination for the differential input pads with the conventional double-diode ESD protection scheme. In this chapter, a new ESD protection scheme for differential input pads, which is realized with cross-coupled SCR, is proposed to protect the differential low-noise amplifier (LNA). In Section 2.2, the reference differential LNA was implemented without ESD protection for comparison. In Section 2.3, the conventional double-diode ESD protection scheme is applied to protect the differential LNA. ESD test results have shown that the pin-to-pin ESD test is the most critical ESD-test pin combination for the LNA with double-diode ESD protection scheme. To improve overall ESD robustness of the ESD-protected differential LNA, a new ESD protection scheme with the cross-coupled SCR is proposed in Section 2.4. As compared with the conventional double-diode ESD protection scheme, the pin-to-pin ESD robustness is substantially improved by the new proposed ESD protection scheme in this work. Experimental results have shown that the new proposed on-chip ESD protection circuit co-designed with the input matching network of the LNA can achieve excellent ESD robustness and good RF performance.. 2.1. Background As the feature size of MOS transistor in CMOS technology is continuously scaled down to improve the high-frequency characteristics, the advanced nanoscale CMOS technology is more attractive to implement radio-frequency integrated circuits (RF ICs). In an RF front-end, the low-noise amplifier (LNA) plays a very important role because it is the first stage in the RF receiver. In LNA design, differential configuration is popular because the differential LNA has the advantages of better common-mode noise rejection, as well as less sensitivity to substrate noise, supply noise, and bond-wire inductance variation [48]-[54]. In addition, the - 29 -.

數據

+7

Outline

Background of ESD Protection Design for Radio-Frequency Circuits

Low-Noise Amplifier Without ESD Protection

New Proposed Cross-Coupled-SCR ESD Protection Scheme

SCR Structures

UWB Distributed Power Amplifier Basics

Measured RF Performance After ESD Zapping

Traditional Designs of High-Voltage-Tolerant ESD Clamp Circuits

Future Works

相關文件

【5+2產業】亞洲矽谷 電腦資訊技術類 物聯網自動灌溉與排水系統設計班. 【5+2產業】亞洲矽谷

With the results of the literature review on cooperative learning of game design structures, this research examines the possibilities of applying the “Multi-Touch Control”

鋼絲軌道: (鋼絲型線燈)利用 金屬線的導電性取代傳統 電線。線燈多採用多面反 射燈泡。.. 特殊燈.

◦ 金屬介電層 (inter-metal dielectric, IMD) 是介於兩 個金屬層中間,就像兩個導電的金屬或是兩條鄰 近的金屬線之間的絕緣薄膜,並以階梯覆蓋 (step

Department of Physics and Institute of nanoscience, NCHU, Taiwan School of Physics and Engineering, Zhengzhou University, Henan.. International Laboratory for Quantum

高等電腦輔助設計與製造 (Advanced Computer Aided Design and Manufacturing).

進而能自行分析、設計與裝配各 種控制電路,並能應用本班已符 合機電整合術科技能檢定的實習 設備進行實務上的實習。本課程 可習得習得氣壓-機構連結控制

請繪出交流三相感應電動機AC 220V 15HP,額定電流為40安,正逆轉兼Y-△啟動控制電路之主