國 立 交 通 大 學

電信工程學系

碩 士 論 文

具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器與

2.5-11GHz 主動式寬頻匹配超寬頻低雜訊放大器

Design and Implementation of a Band-Notch Ultra-wideband LNA with Band

Shaping Capability and a 2.5-11GHz Active Matching Ultra-wideband Low

Noise Amplifier

研究生:陳煥能 (

Huan -Neng Chen

)

指導教授:鍾世忠 (

Dr. Shyh-Jong Chung

)

具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器與

2.5-11GHz 主動式寬頻匹配超寬頻低雜訊放大器

Design and Implementation of a Band-Notch Ultra-wideband

LNA with Band Shaping Capability and a 2.5-11GHz Active

Matching Ultra-wideband Low Noise Amplifier

研究生:陳煥能 Student: Huan -Neng Chen

指導教授:鍾世忠 Advisor:Dr. Shyh-Jong Chung

國立交通大學

電信工程學碩士班

碩士論文

A Thesis

Submitted to Department of Communication engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of

Master of Science

In

Communication Engineering

June 2006

HsinChu, Taiwan, Republic of China

具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器的設計與

實現及

2.5-11GHz 主動式寬頻匹配超寬頻低雜訊放大器設計與實

現

學生:陳煥能

指導教授:鍾世忠 博士

交通大學電信工程研究所

中文摘要

本論文描述應用在超寬頻系統中低雜訊放大器之分析與設計。超寬頻低雜訊放大器 需具備有寬頻、增益平坦的特性。 第一部份為具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器,一開始先設計 LC諧振匹配超寬頻低雜訊放大器,其量測結果如下,頻寬3.1~10GHz,增益5± 2dB, S11<-4dB,S22<-8.5dB,消耗功率為16.2 mW。接著進階再設計了具抑制頻寬外增益功 能之帶斥特性超寬頻低雜訊放大器,其模擬結果如下,頻寬3.1~9GHz,3.1~5GHz,增益 12± 1.2dB,6~9GHz,增益10±0.5dB,S11<-9.5dB,S22<-10dB,最低的雜訊指數為3.48 dB。消耗功率為 22mW。 第二部份為2.5-11GHz主動式寬頻匹配超寬頻低雜訊放大器,利用了多級的概念來 設計,並且選擇共閘級做為第一級放大器,中間加上一級共源級疊接組態來提高整體增 益,最後再加上一級電壓追隨器達到輸出阻抗匹配。這個寬頻低雜訊放大器其量測結果 如下,頻寬為2.5~11GHz,增益為7.5 dB ±0.5dB,S11<9.9dB,S22<-12dB,消耗功率為 18.9 mW。Design and Implementation of A Band-Notch Ultra-Wideband Low Noise

Amplifier with Band Shaping Capability And A 2.5-11GHz Active Matching

Ultra-Wideband Low Noise Amplifier

Student:Huan -Neng Chen Advisor:Dr. Shyh-Jong Chung

Institute of Communication engineering

National Chiao Tung University

ABSTRACT

This thesis describes the design and analysis of low-noise amplifier for UWB system. The features of the UWB LNA are wide bandwidth and flatness of gain.

The first part studies on a band-notch ultra-wideband LNA with band shaping capability.For a start , the measured performances of a LC resonance matching ultra-wideband LNA are as follow: The bandwidth of the LNA is ranged from 3 GHz to 10 GHz. The gain is 5 dB ± 2 dB. The input return loss is below -4dB. The output return loss is below -8.5dB . The power consumption is 16.2 mW. The simulation performances of a band-notch ultra-wideband LNA with band shaping capability are as follow: The bandwidth of the LNA is ranged from 3 GHz to 9 GHz. For 3GHz to 5GHz, the gain is 12 dB ± 1.2 dB. For 6GHz to 9GHz, the gain is 10 dB ± 0.5 dB.The input return loss is below -9.5dB. The output return loss is below -10dB . The minimum noise figure is 3.48dB and the power consumption is 22 mW.

The second part studies on a 2.5-11GHz active matching Ultra-wideband Low Noise Amplifier. We utilize the concept of multi-stages to design this circuit. The first stage is a common gate topology and a Cascode amplifier is in the middle stages and the final stage is a voltage follower. the measured performances of a 2.5-11GHz active matching Ultra-wideband Low Noise Amplifier are as follow: The bandwidth of the LNA is ranged from 2.5 GHz to 11 GHz. The gain is 7.5 dB ± 0.5 dB. The input return loss is below -9.9dB. The output return loss is below -12dB . The power consumption is 18.9 mW.

致謝

從對射頻電路一知半解到現在順利完成學業,在研究所的兩年生活,首先我要感謝 我的指導教授鍾世忠博士,提供我一個很優質的研究環境學習成長,對於研究方面給予 相當充足的資源,還有老師豐富的學識、待人處世的寬厚,使自己在學業上找到屬於自 己的方向與目標,另外也讓我在修養方面更上一層樓。在此感謝口試老師:王暉教授、 邱煥凱教授以及陳富強教授,能在百忙之中抽空前來,給予論文上的指導與建議,讓我 受益良多,也使得論文更為完備。 我還要感謝極樂實驗室的所有成員們,一進來實驗室就帶著我的 毛最佳代言人佩 宗、綠島浮潛在我面前狂吐的清標,很謝謝二位學長常常不辭辛勞指導我和給與建議, 在做人處世的部份,也從你們身上學到不少。最專業的源哥、三寸不爛之舌的峻義、一 定早起的敦智、拍照高手的天健,還有顯鴻和郁娟,大家在電資一起互相砥礪和出外遊 玩,度過許多快樂時光。經驗豐富的實驗室大學長何博,常有新奇點子的阿信,常一起 玩樂的台客彥圻、小洪,愛來電資打 aoc 順便啦塞的克強,強者峰哥和鈞富,雷達救星 明達和光甫,曾經同組的小圓和小花, 做什麼事都會被我們虧的小太陽旭哥,以及彥 志、digo、小巴、小黃還有實驗室最有氣質三朵花菁偉、purple、玫翎,謝謝各位讓實 驗室充滿了歡樂氣氛,也很感謝辛苦而且有求必應的助理珮華和明潔,這二年研究所酸 苦甘甜的回憶,因為你們覺得很美好。祝福你們在未來都能完成自己心中的夢想。 最後要感謝我的家人,從不給我壓力讓我無後顧之憂地完成學業與研究的老爸老 媽,一直很疼我的老姊,因為有你們無私的奉獻與支持,才能成就今日的我。謹以此論 文獻給所有幫助過我與關心我的人目錄

中文摘要………..…..I

英文摘要……….………..II

致謝………..III

目錄………..IV

圖目錄………..VI

表目錄………..………..VIII

第一章 緒論

………...1 1-1 研究動機……….1 1-2 章節概述……….………1第二章 接收機架構介紹

………...2 2-1 超外差接收機架構(Superheterodyne Receiver)……….2 2-1-1 鏡像頻率(Image Frequency)……….3 2-1-2 中頻頻率之選擇(Selection of IF)………...42-1-3 半中頻的影響(Effects of half IF)……….6

2-2 直接降頻接收機架構(Direct-Conversion Receiver)………..7 2-2-1 直流偏移(DC Offset)………...8 2-2-2 偶次階失真(Even-Order Distortion)………...8 2-2-3 顫動雜訊(Flicker Noise)………...9 2-2-4 正交信號的不匹配(I/Q Mismatch)………...9 2-3 鏡像消除接收機架構(Image-Rejection Receiver)………....11 2-3-1 Hartley 架構……….11 2-3-2 Weaver 架構……….16

第三章 常用放大器架構介紹

……….………...183-1 低雜訊放大器(Low noise amplifier)簡介……….………..18

3-2 電晶體雜訊模型推導……….……….19 3-3 常用放大器簡介[4]….………21 3-3-1 電阻匹配式放大器.……….21 3-3-2 1/gm 匹配式放大器………..22 3-3-3 並串回授式放大器………..23 3-3-4 源級電感性衰減放大器………..25 3-4 1dB 壓縮點(1dB Compression Point)…...………27 3-5 交互調變失真(Intermodulation Distortion)……….28

第四章 超寬頻低雜訊放大器架構介紹

……….29 4-1 TSMC 0.18um 1P6M CMOS 製程元件簡介………...29 4-1-1 NMOS 電晶體………294-1-2 MIM 電容………..30 4-1-3 螺旋式電感………30 4-1-4 電阻………31 4-1-4 模擬電路所加入實際量測的考量因素………32 4-2 單頻帶共源疊接(Cascode)低雜訊放大器………..33 4-2-1 輸入匹配級………34 4-2-2 輸出匹配級………35 4-2-3 增益………....35 4-3 具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器設計……….36 4-3-1 LC 諧振匹配超寬頻低雜訊放大器[5]……….36 4-3-1-1 LC 諧振輸入匹配的原理………..37 4-3-1-2 寬頻輸出匹配的原理………39 4-3-1-3 寬頻增益之探討………40 4-3-2 抑制頻寬外增益功能超寬頻低雜訊放大器設計………...43 4-3-2-1 加入抑制電容之輸入匹配電路說明………...45 4-3-2-2 具抑制 UWB 頻寬外增益輸入匹配電路進階探討………46 4-3-3 延續以濾波概念設計 UWB 頻段內增益有帶斥特性………...48 4-3-3-1 利用一個零點二個極點之理想 LC 電路達到增益帶斥特性…48 4-3-3-2 實際考量上有內阻之 LC 電路……….49 4-3-3-3 加入負阻-R 之有內阻之 LC 電路………51 4-3-3-4 負阻-R 擺放位置進階探討………..52 4-3-4 模擬與量測結果………55 4-4 主動式匹配超寬頻低雜訊放大器………60 4-4-1 寬頻輸入匹配………..60 4-4-2 寬頻輸出匹配的原理………..61 4-4-3 寬頻增益之探討………..61 4-4-4 模擬與量測結果……….63

第五章 結論

………67參考文獻

………68圖目錄

圖 2.1 超外差接收機架構………..………2 圖 2.2 鏡像頻率問題………..………3 圖 2.3 在混頻器前加上一個鏡像濾波器衰減鏡像頻率…………..………4 圖 2.4 通道隔鄰干擾,會和所要的訊號一起經過混頻器降頻到中頻…………....4 圖 2.5 鏡像濾波器和頻道選擇濾波器的選擇……..………5 圖 2.5 (a)高中頻可抑止較多的鏡像頻率,但抑止隔鄰干擾的效果比較差……....5 圖 2.5 (b)高中頻可抑止較多的鏡像頻率,但抑止隔鄰干擾的效果比較差……....5 圖 2.6 相位雜訊影響接收機的靈敏度與選擇性…………..………6 圖 2.7 半中頻對中頻的影響………..………....7 圖 2.8 直接轉換接收機架構………..………7 圖 2.9 直流偏移的成因………..………8 圖 2.10 在低雜訊放大器和混頻器中偶次階失真的效應………...9 圖 2.11 I/Q 不匹配的分佈情形……….10 圖 2.12 QPSK 信號的星狀圖,(a)增益誤差(b)相位誤差……….10 圖 2.13 Hartley 鏡像抑制示意方塊圖………..11 圖 2.14 Hartley 架構之頻譜分析………..13 圖 2.15 Hartley 鏡像抑制接收機………..14 圖 2.16 RC-CR 的九十度相移網路……….……….…15 圖 2.17 Weaver 鏡像抑制接收機……….16 圖 2.18 Weaver 架構之頻譜分析……….17 圖 3.1 基本接受機架構……….18 圖 3.2 感應閘極雜訊電流示意圖與等效雜訊電流源……….20 圖 3.3 氧化層與矽基板的不連續鍵結……….20 圖 3-4 常用放大器架構………21 圖 3-5 Shunt-series feedback 小訊號模型………23圖 3.6 Inductive Degeneration 型 LNA 之小訊號等效電路圖………25

圖 3.7 輸入端電晶體 M2 的雜訊模型………26 圖 3.8 1dB 增益壓縮點………27 圖 3.9 非線性系統中的交互調變示意圖………28 圖 3.10 Two tone 測試交互調變失真………28 圖 4.1 NMOS 佈局圖及等效電路模型………29 圖 4.2 MIM 電容佈局示意圖及等效電路模型………30 圖 4.3 螺旋式電感佈局圖及等效電路模型………31 圖 4.4 TSMC 電阻………31 圖 4.5 RF Pad 的等效模型………32 圖 4.6 鎊線等效參數………32 圖 4.7 傳統之共源疊接低雜訊放大器………33 圖 4.8 共源疊接低雜訊放大器輸入阻抗的探討………34 圖 4.9 由 Smith 圖觀點探討源疊接低雜訊放大器輸入阻抗………34 圖 4.10 由 Smith 圖觀點探討源疊接低雜訊放大器輸出阻抗………35 圖 4.11 等效小訊號模型………35 圖 4.12 LC 諧振匹配超寬頻低雜訊放大器………36 圖 4.13 LC 諧振輸入匹配電路………37

圖 4.14 輸入阻抗之等效串聯 RLC 電路圖………38

圖 4.15 輸入負載於 Smith Chart 的掃頻圖………38

圖 4.16 並聯共振腔 Y 參數負載………38

圖 4.17 寬頻輸入匹配電路圖………39

圖 4.18 寬頻匹配於 Y chart 可能走勢以及 Smith Chart 掃頻圖………39

圖 4.19 使用電壓隨耦器寬頻輸出匹配電路………39 圖 4.20 共軛匹配以達到最大的功率傳輸………40 圖 4.21 達到中間級共軛匹配低雜訊放大器之電路圖以及增益比較圖[16] ………41 圖 4.22 加上電感 Lseries 設計放大器在高頻共軛匹配………41 圖 4.23 電感 Lseries 加入與否之增益比較圖………42 圖 4.24 中間級共軛匹配之 Smith Chart 圖………42 圖 4.25 基本 MB-OFDM UWB 系統收發機架構………43 圖 4.26 在 LC 諧振匹配中加入抑制電容 Co、Cs………44 圖 4.27 (a)加入抑制電容 Co、Cs 之增益比較………44 圖 4.27 (b)發表於 2005MTT-S 濾波器之頻寬外抑制效果[11] ………45 圖 4.28 加入電容 Cs 抑制 UWB 頻寬外的低頻增益………45 圖 4.29 加入電容 Co 抑制 UWB 頻寬外的高頻增益………46 圖 4.30 加入電容 Cs 與否二者輸入匹配之比較………47 圖 4.31 電容 Co 影響寬頻匹配之探討………47 圖 4.32 DS-CDMA 與 MB-OFDM 頻帶示意圖………48 圖 4.33 可產生一個零點二個極點之 LC 電路與頻率對阻抗圖………49 圖 4.34 考慮實際上有內阻之 LC 電路與頻率對阻抗圖………50 圖 4.35 加上-R 與有內阻之 LC 電路………51 圖 4.36 負阻電路架構與其等效電路推導………51 圖 4.37 並聯 RC 電路等效成串聯 RC 電路………52 圖 4.38 等效串聯負阻之 LC 電路………53 圖 4.39 負阻 m g 2 − 加入與否之阻抗比較與增益比較………54 圖 4.40 抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器………54 圖 4.41 LC 諧振匹配超寬頻低雜訊放大器 S 參數和 NF 模擬圖………55 圖 4.42 LC 諧振匹配超寬頻低雜訊放大器量測結果………56 圖 4.43 LC 諧振匹配超寬頻低雜訊放大器 layout 圖………57 圖 4.44 LC 諧振匹配超寬頻低雜訊放大器實際電路圖………57 圖 4.45 鎊線感值變大對 S11 的影響情形………57 圖 4.46 抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器模擬結果…………58 圖 4.47 主動式匹配超寬頻低雜訊放大器架構………60 圖 4.48 1/gm輸入匹配………61 圖 4.49 輸出匹配電路………61 圖 4.50 Lseries1 和 Lseries2 加入與否增益比較圖………62 圖 4.51 主動式匹配超寬頻低雜訊放大器 S 參數和 NF 模擬圖………63 圖 4.52 主動式匹配超寬頻低雜訊放大器量測結果………65 圖 4.53 主動式匹配超寬頻低雜訊放大器 layout 圖………65

表目錄

表 4-1 LC 諧振匹配超寬頻低雜訊放大器模擬參數表格………56 表 4-2 抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器模擬參數表格…………59 表 4-3 主動式匹配超寬頻低雜訊放大器模擬參數表格………64 表 4-4 設計之 LNA 與其它發表論文比較之表格………66

第一章

緒論

§1-1 研究動機

近年來,超寬頻(Ultra-Wide Band,UWB)技術己逐漸成爲無線通訊領域之研究重 點,並被視爲下一代無線通訊系統的關鍵技術之一。FCC 於 2002 年 2 月 14 日率全球之 先通過UWB 商用化規範,准許在3.1 GHz 到 10.6 GHz 頻段範圍使用低功率之 UWB 系 統,UWB 比起其他無線技術有更多的頻寬可以利用,同時也不至於嚴重干擾位於同頻 段的其他無線通訊系統。在傳輸速率上,UWB 傳輸速率超過 100Mbps,甚至可以高達 480Mbps,涵蓋距離約 10 公尺,相當適合高階影音多媒體傳輸之應用。總而言之,UWB 技術具有高傳輸速率、高測距定位精度、高安全性、低功率消耗、低成本及短距離傳輸 等特性。 超寬頻無線通訊系統操作在非常寬的頻帶上,這對射頻積體電路的設計是一項相當 大的考驗。大致上,射頻積體電路之運作可分成傳送與接收兩方面,對射頻積體電路收 發機來說,主要有幾個關鍵子電路包含低雜訊放大器、混頻器、功率放大器、鎖相迴路 (phase lock loop)。而隨著CMOS製程技術的進步,CMOS在元件上已可以達到高頻電路 的要求,但是為了同時達到寬頻的特性以及系統的規格,即是目前設計的主要的瓶頸。 本論文將針對超寬頻低雜訊放大器部份,在寬頻與其它特性做深入探討§1-2 章節概述

本論文分為五個章節,第一章:敘述UWB 無線通訊的發展,以及論文之研究動機。 第二章:介紹幾種接收機架構之優缺點。第三章:針對常用放大器特性加以探討。第四 章:敘述超寬頻低雜訊放大器的規格參數並說明設計電路達到寬頻特性的原理,以及量 測與模擬的結果。第五章,本章節為結論,說明本論文研究之成果。第二章

接收機系統架構介紹

無線通訊中,接收到的電波訊號(皆為類比訊號)必須轉成數位訊號,再經過特定的 訊號處理,才能成為有用的資訊。而將類比訊號轉為數位訊號的方塊稱之為類比轉換器 (analog-to-digital converter,ADC)。現有實際的ADC因為取樣速率與動態範圍的限制, 無法直接處理由天線接收到的微弱高頻電波訊號,故必須透過射頻接收機。在設計接收 機時,不同的接收機架構各有其特性及應用範圍,端視設計者的考量而定,一般考量的 重點在於接收機的成本、消耗功率、外加元件數目以及複雜度。本章將對於幾種常見的 接收機架構作一簡述及分析[1] [2]。§2-1 超外差接收機架構(Superheterodyne Receiver)

Band Select Filter LNA RF LO Mixer IF Amplifier Channel Select Filter Antenna LPF 90° LPF IF LO I Q Baseband Baseband 圖2.1 超外差接收機架構 西元1918年,超外差接收機架構由Armstrong提出之後,此一接收機架構對於系統 設計者而言,影響深遠,時至今日此一架構仍有多種改良及應用,無論是在工業界抑或 是學術界。適用於多種通訊協定之接收機的實現,具良好的訊號選擇性(selectivity)以及 靈敏度(sensitivity)為其主要優點,其基本架構如圖2.1 所示。 此種接收機架構的工作原理[3],是將外界接收到的高頻(RF)訊號,經過混頻器與本地振盪(LO)訊號產生混頻,將原本高頻(RF)訊號轉換為較低頻的訊號,通常稱之為中頻(IF) 訊號(Intermediate Frequency)。IF訊號的中心頻率對接收機來說是一個關鍵性參數,通常 要跟接收機的其他各方面性能,做適當地調整始能有預期的性能。但缺點是需要較多額 外晶片的元件,因此成本也相對提高許多。

§2-1-1 鏡像頻率(Image Frequency)

鏡像訊號干擾的產生,主要是由於所使用之降頻混波器會將對稱於本地振盪器輸出 頻率的兩側、距離一個中頻的頻帶處之訊號,以相同的轉換響應降頻至中頻頻帶,如圖 2.2 所示,假設所要通道頻率為ωRF = ωLO −ωIF ,和本地振盪頻率(ωLO)進入混頻器 後,會產生中頻(ω

IF),然而假設有一個頻率ωLO + ωIF 也同時進入混頻器,也會和本 地振盪(LO)混出中頻頻率,但這不是所要通道頻率中所降頻出的中頻,所以ωLO + ωIF 稱為鏡像頻率。ω

1 ω ωimω

LO ω IF ω ωIFω

LPF

Mixer LO IF ω 圖2.2 鏡像頻率問題 如圖2.3 所示,可在混頻器前面加一個濾波器,此濾波器稱為鏡像濾波器(Image Reject Filter),用來抑制在鏡像頻率處的干擾;且當選擇的中頻越高時,鏡像頻率離所要的通 道越遠,濾除鏡像頻率的效果也越好。Low Noise Amplifier LPF Mixer RF LO IF

BPF

Image Reject Filter ω 1 ω ωim IF ω 2 Image Reject Filter 圖2.3 在混頻器前加上一個鏡像濾波器衰減鏡像頻率§2-1-2 中頻頻率之選擇(Selection of IF)

通道相鄰干擾會將所要的訊號一起經過混頻器降頻到中頻,而在中頻附近形成干 擾,如圖2.4 所示。因此在混頻器後加上一個頻道選擇濾波器(Channel Select Filter)以濾 除中頻附近的干擾。因為要把中頻附近的干擾濾掉,所以需要非常高Q值的濾波器,即 有較高的裙帶因子(skirt factor),一般是選用表面聲波濾波器(SAW filter)做為頻道選擇濾 波器。 Mixer ω Interferers ω Interferers LO RF IF want ω wantω

圖2.4 通道隔鄰干擾,會和所要的訊號一起經過混頻器降頻到中頻 但是同樣架構的濾波器,其Q值隨著頻率的升高而降低,所以為了有較好的選擇性,最 好選擇較低的中頻,但這和在考慮消除鏡像頻率上,選擇較高的中頻是互相矛盾的。如 圖2.5 所示,為不同的中頻對鏡像濾波器和頻道選擇濾波器的影響,從圖2.5(a),可看出 選擇高中頻可以抑止較多的鏡像頻率,如此鏡像頻率降到中頻處的量較小,但抑止隔鄰干擾的效果比較差;相反的,圖2.5(b)是選擇低中頻,則有較好的抑止隔鄰干擾效果, 但抑止鏡像頻率的效果較差。故中頻頻率需謹慎的選擇才行。 Low Noise Amplifier

BPF

Mixer LOBPF

Image Reject Filter Channel Select Filter 圖2.5 鏡像濾波器和頻道選擇濾波器的選擇ω

1ω

ω

im IF ω 2 Image Reject Filter Desired Channelω

IFω

0 Image Interferer Channel Select Filter High IF 圖2.5 (a)高中頻可以抑止較多的鏡像頻率,但是抑止隔鄰干擾的效果比較差ω

1ω

ω

im IF ω 2 Image Reject Filterω

IFω

0 Low IF 圖2.5 (b)低中頻可以抑止較多的隔鄰干擾,但是抑止鏡像頻率的效果比較差另外,本地振盪訊號的相位雜訊(Phase Noise)對系統的影響也是相當的重要,在混頻的 過程中,相位雜訊會轉移到中頻,故相位雜訊要求越低越好。如圖2.6 所示,當一個很 強的鄰進波道干擾和一個很弱的接收訊號同時出現時,多餘的相位雜訊會和很強的干擾 交互調變到中頻,使得原本很弱的中頻訊號可能被干擾。至於本地振盪頻率的選擇有兩 種方式,一種是頻率低於通訊通道中心頻率,另一種是高於通訊通道中心頻率,一般建 議使用第一種,因為壓控振盪器(VCO)比較容易設計且本地振盪頻率較低,相位雜訊會 比較好。 Mixer ω Unwanted Adjacent Channel ω RF IF Noise LO want ω ωLO IF

ω

Desired Channel Noise LO 0 圖2.6 相位雜訊影響接收機的靈敏度與選擇性§2-1-3 半中頻的影響(Effects of half IF)

如圖2.7 所示為假設干擾頻率為

(

ω

in +ω

L O)

2,經過低雜訊放大器後產生的二 次諧波失真,再與本地振盪的二次諧波項混波後成為(

ωi n + ωL O)

− 2ωL O = ωI F , 這會對中頻造成干擾。此外,干擾頻率(

ω i n + ω L O)

2 與本地振盪(

ω

L O)

混頻後 成為二分之一的中頻訊號(

ωi n − ω L O)

2 = ω I F 2 ,此信號再經過放大器及混頻器 後所產生的二次諧波失真也會在中頻的地方產生干擾。為了降低半中頻對系統的影響, 射頻和中頻主動元件電路應該儘可能的降低二次諧波失真。Low Noise Amplifier Mixer RF LO

BPF

Image Reject Filterω

IF ω 0 2 IF ωω

inω

2 in LO ω ω+ LOω

Interferer Desired Band 圖2.7 半中頻對中頻的影響§2-2 直接降頻接收機架構(Direct-Conversion

Receiver)

由於直接轉換架構的本地振盪頻率與射頻頻率相同,因此沒有鏡像頻率的問題,所 以不需要在混頻器前加一個鏡像濾波器。因為沒有中頻,故不需要在混頻器後加上一個 頻道選擇濾波器和中頻放大器,取而代之的是一個低通濾波器。因此直接轉換架構比超 外差架構所需的元件還要少,也易於將整個接收機整合為單一晶片,接收架構如圖2.8 所 示。雖然直接降頻接收機有以上優點且架構簡單,但過去未被普遍使用,原因有下列幾 點。 Low Noise AmplifierBPF

sinω

ctcos

ω

ct

I Q LPF LPF Base band Amplifier Base band Amplifier 圖2.8 直接轉換接收機架構§2-2-1 直流偏移(DC Offset)

如圖2.9 所示,因為混頻器RF-LO的隔離度是有限的,造成本地振盪信號洩漏的現 象是由於電容與基板耦合及鎊線(Bonding wire)效應,當本地振盪信號洩漏到A點和B點 時,洩漏的信號反射回來與本地振盪再次混頻並在C點混出直流信號;還有另一種情形 是當較大的干擾信號從B點溢漏到本地振盪時(Interferer Leakage),再與同頻率的干擾訊 號混頻,也會在C點混出直流信號。這些現象稱為自我混頻(Self-Mixing)。然而此情形可 能會使後級的主動電路飽和,或是干擾到所要的信號。 Low Noise Amplifier LPF Base band Amplifier ADC Mixer1 LOω

A B C D LO Leakage Low Noise Amplifier LPF Base band Amplifier ADC Mixer1 LOω

A B C D Interferer Leakage 圖2.9 直流偏移的成因§2-2-2 偶次階失真(Even-Order Distortion)

如圖2.10 所示,當有兩個干擾信號A1cosω

1t及A2cosω

2,很接近所要的信號時, 經過低雜訊放大器的非線性效應後,產生的二階調變衍生信號,如果很接近直流訊號, 若混頻器的RF-IF的隔離度不夠大,又經過混頻器溢漏到混頻器的輸出端,而對降頻後 所要的基頻接收信號造成干擾,此視為偶次階失真。實際上,超外差式接收機的混頻器也同樣有這問題存在,所以需要高線性度的低雜訊放大器和混頻器,以防止偶次階失真。

ω

Interferers Desired Channelω

1 ω ω2 Low Noise Amplifier LO ω 0ω

Feedthrough 0( )

y t

( )

x t

2LNA IM 2LNA IM 1 ω ω2 圖2.10 在低雜訊放大器和混頻器中偶次階失真的效應§2-2-3 顫動雜訊(Flicker Noise)

電晶體的顫動雜訊屬於低頻雜訊,功率頻譜密度和頻率成反比(1/f),所以顫動雜訊 會使直接降頻至基頻訊號的訊號雜訊比降低,故一般在低雜訊放大器(LNA)及混頻器的 地方把增益提高,減少顫動雜訊的影響,例如使用主動式混頻器來取代被動式混頻器。§2-2-4 I/Q信號的不匹配(I/Q Mismatch)

如圖2.11 所示,理想的情況下是不會有I/Q不匹配的現象,然而實際上電路卻是會 無法如此;當I/Q信號經過相位或是增益不匹配電路時,I/Q信號的星狀圖(Constellation) 會失真,位元錯誤率因此上升。圖2.12 是QPSK信號經過相位和增益不匹配電路時,所 產生的失真星狀圖。在超外差接收架構中,因I/Q信號是經由中頻降頻而成的,降頻的 頻率比在直接轉換架構中由射頻直接降頻的頻率還要來的低,且在分離I/Q信號後所用 的電路比在直接轉換架構中還要少,所以比較沒有I/Q不匹配的情形。I Q LPF LPF 0

90

RF V VLO Phase and Gain Error Phase and Gain Error Phase and Gain ErrorPhase and Gain Error

圖2.11 I/Q不匹配的分佈情形 Q I I Q Ideal Ideal (a) (b) 圖2.12 QPSK信號的星狀圖,(a)增益誤差(b)相位誤差

§2-3 鏡像消除接收機架構(Image-Rejection

Receiver)

另一種消除鏡像訊號的方式乃利用鏡像抑制接收機。此類型的接收機可省去在超外 差接收機中所需之鏡像抑制濾波器,因此當接收機系統是以晶片方式來製作時,此種鏡 像抑制架構就能免除在晶片外掛一高Q值鏡像抑制濾波器的麻煩。一般而言,常見之鏡 像抑制架構有兩種:Hartley架構、Weaver架構。§2-3-1 Hartley架構

如圖2.13 所示,主要是由兩個具備有九十度相位相差的混頻器所組成,此因混頻器 的本地振盪器源是由兩個相差九十度的信號作為輸入所產生。至於鏡像抑制的現象,則 是使用混頻器與九十度相位轉移器對於I與Q兩路徑之鏡像信號所造180度之相位轉移, 最後用合成器做信號合成,使得鏡像信號被消除。 M ixer LPF LOQ M ixer LPF LOI RF IF90°

A B C E D 圖2.13 Hartley鏡像抑制示意方塊圖 其數學分析如下: 令輸入訊號為 f(t)= ARF coswRFt+AIM coswIMt,其中 、 分別為射頻信號頻率及 鏡像信號頻率,而本地振盪信號具有九十度相差。故在A與B兩點產生的信號分別如2-1 式與2-2式所示: RF w wIM[

]

[

w w t w w t]

A t w w t w w A t f IM LO IM LO IM LO RF LO RF RF A ) sin( ) sin( 2 ) sin( ) sin( 2 ) ( − + + + − + + = ( 式2 - 1 )[

]

[

w w t w w t]

A t w w t w w A t f IM LO IM LO IM LO RF LO RF RF B ) cos( ) cos( 2 ) cos( ) cos( 2 ) ( − + + + − + + = ( 式2 - 2 ) 當 、 兩點信號經由低通濾波器之後,高頻成分將被濾波器濾除,可得C與D 兩點的信號為: ) (t fA fB(t) t w w A t w w A t f IM LO IM LO RF RF C( )= 2 sin( − ) + 2 sin( − ) ( 式2 - 3 ) t w w A t w w A t f IM LO IM LO RF RF D( )= 2 cos( − ) + 2 cos( − ) ( 式2 - 4 ) 而C處的信號又經由一個九十度相位轉移器可得E處的信號為: t w w A t w w A t fE RF RF LO IM cos( LO IM) 2 ) cos( 2 ) ( = − − − ( 式2 - 5 ) 由2-4式與2-5式我們可以觀察到:對於D與E兩處的訊號而言,射頻信號為同相位,而鏡 像信號則為相差180度,此時只需將兩處信號作合成即完成消除鏡像信號的作用。上述 討論的式子,參考圖2.14 可以得到其在頻譜上所表示的涵義。 接著將針對本地振盪信號的不匹配所造成的影響進行探討。假設有兩個振幅與相位不匹 配的本地振盪信號ALO sinwLOt與(ALO +δ)cos(wLOt+θ),其中δ 代表振幅量的偏差、θ代 表相位量的偏差,運用相同的分析方式可得在D與E兩處的信號變成: ] ) cos[( 2 ) ( ] ) cos[( 2 ) ( ) (t = A +δ A w −w t+θ + A +δ A w −w t+θ f LO IM LO IM LO RF RF LO D ( 2 - 6 ) t w w A A t w w A A t f LO IM LO IM LO RF RF LO E( )= 2 cos( − ) − 2 cos( − ) (2 - 7 )ω LO

ω

Desired Channel Image 0 LOω

− RF Input ω 2 j + +j2 0 ω 2 j − −j2 0)

(w

m

C ω 0 ω 0)

(w

m

E ω 0 ω 0)

(w

m

D ω 0 IF Output 圖2.14 Hartley架構之頻譜分析 最後經過一個合成器將把兩個信號合成,即為 fIF(t)= fD(t)+ fE(t),若將此信號分為射 頻信號和鏡像信號則變成 fIF(t)= fRF(t)+ fIM(t),其中 fRF(t)與 fIM(t)分別為: t w w A A t w w A A t fRF LO RF RF LO LO RF cos( RF LO) 2 ] ) cos[( 2 ) ( ) ( = +δ − +θ + − ( 式 2 - 8 ) t w w A A t w w A A t fIM LO RF LO IM LO IM cos( LO IM) 2 ] ) cos[( 2 ) ( ) ( = +δ − +θ − − ( 式 2 - 9 ) 在輸出端來看兩端信號的平均功率比值為:2 2 2 2 2 2 2 2 cos ) ( 2 ) ( cos ) ( 2 ) ( )] ( [ 1 )] ( [ 1 | LO LO LO LO LO LO LO LO RF IM T RF T IM OUT RF IM A A A A A A A A A A dt t f T dt t f T P P + + + + + + − + × = =

∫

∫

θ δ δ θ δ δ ( 式2 - 1 0) 在2-10式中,左邊第一項中 2 2 RF IM A A 是鏡像信號與射頻信號振幅的比值,而我們定義 2 2 2 2 cos ) ( 2 ) ( cos ) ( 2 ) ( LO LO LO LO LO LO LO LO A A A A A A A A + + + + + + − + θ δ δ θ δ δ為鏡像抑制比(Image Rejection Ratio)

2 2 2 2 2 2 2 cos cos 2 B AB A B AB A A A P P IRR RF IM RF IM + + + − = = θ θ ,其中A= ALO,B= ALO +δ。因為δ <<ALO且θ<<1, 故將cosθ以泰勒級數展開(即 = − 2 +… 2 1 1 cosθ θ )可得: 4 2 2 θ δ + ⎟ ⎠ ⎞ ⎜ ⎝ ⎛ = A IRR ,其中 A A A A LO ∆ = = δ δ (式2-11) 因此可知當δ =0與θ =0時,IRR=0表示鏡像信號完全可被消除。 在Hartley架構中,常使用RC-CR網路來實現九十度相移器,使得整體架構如圖2.15 所 示。 Mixer LPF LOQ Mixer LPF LOI R C R C RF Input IF Output 圖2.15 Hartley鏡像抑制接收機

在Hartley架構中,九十度相移網路器(如圖2.16 所示)造成的兩個輸出端振幅不匹配,也 會對鏡像抑制效果造成影響,因此以下對RC的變異對鏡像抑制效果的影響作一分析。 假設電阻R有一變動量為ΔR,電容C有一變動量為ΔC,輸出電壓振幅A有一變動量為 ΔA,可得: 1 ) ( ) ( 1 ) )( ( R 1 1 1 1 1 ) ( ) ( 1 ) )( ( 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 − ∆ + ∆ + + ∆ + ∆ + × + = + + − ∆ + ∆ + + ∆ + ∆ + = ∆ w C C R R w C C R R w C w C R w C R w C C R R w C C R R A A 其中wRC≈1, 2 2 1 R R ∆ << , 2 2 1 C C ∆ << , RC C R∆ ∆ << 1 ,整理後可得下式 R R C C R R C C R R C C A A − ≈ ∆ +∆ ∆ + ∆ + ∆ + ∆ + ≈ ∆ 1 1 1 (式2-12) 由2-12式中可知,若∆R與∆C為零時表示無變動量,亦表示無偏差,所以 A A ∆ 為零。一般 而言,假如電阻的變異量比值 R R ∆ =20%時,鏡像抑制效果的極限大約為20dB。因此若 是使用RC-CR九十度相移網路,則會因為電容與電阻的變異量,使得抑制效果變差。 R C R C V i n V o u t 1 V o u t 2 圖2.16 RC-CR的九十度相移網路

§2-3-2 Weaver架構

在Hartley架構中,於一對具九十度相差混頻器之後放置九十度相移器,進而達到鏡 像抑制效果。但九十度的相移器是由被動元件所構成,傳遞訊號時會有功率的耗損,且 易因製程電容與電阻的變異量使得鏡像抑制效果大打折扣,因此演化成Weaver鏡像抑制 架構。其架構如圖2.17 所示,乃是使用九十度相差混頻器取代九十度相移器,利用二次 混頻將鏡像訊號消除,參考圖2.18 即可知其在頻譜上所表示的操作原理。 Mixer LO1Q Mixer LO1I IF Output A B Mixer LO2Q Mixer LO2I C D + - 圖2.17 Weaver鏡像抑制接收機 Weaver鏡像抑制混頻器主要的優點是使用主動混頻電路取代被動的相移器。如此,訊號 在路徑中傳遞,將不會因被動電路而有衰減的現象;相對的,也因此產生了二次鏡像干 擾的問題。但是與Hartley架構相同,在I、Q兩路徑中,因增益與相位的不匹配而降低鏡 像抑制效果的因素依然存在。ω LO ω Desired Channel Image 0 LO ω − RF Input ω 2 j + 2 j + 0 ω 2 j − −j2 0 ω 0 ω 0 ) (w mC ω 0 ω 0 ω 0 ω 0 ) (w mB ω 0 * ω 0 * 2 j + +j2 2 j + 2 j − ) (w mA

)

(w

m

D 圖2.18 Weaver架構之頻譜分析第三章

常用放大器架構介紹

§3-1低雜訊放大器 (Low Noise Amplifier)簡介

在日益蓬勃發展的無線通訊應用上,低雜訊放大器 (Low Noise Amplifier)是接收端 中不可或缺的一環節,因為低雜訊大器為射頻收發器電路的最前端,其主要的目的是提 供接收來自天線之微弱射頻訊號所需的增益。在一個由數個放大器串接的系統中,其雜 訊指數(Noise Figure) 幾乎由第一級的放大器所決定,由於低雜訊放大器(LNA)為接收端 的前端部分,因此雜訊指數 ( Noise Figure ) 的好壞將決定於低雜訊放大器的雜訊指 數。對於低雜訊放大器的設計,雖需要有足夠的增益使串接的雜訊指數可盡量地減小, 但增益也不可太高,避免讓訊號過度放大,超過下一級的混頻器(mixer)所能操作的線性 區域,一般而言,低雜訊放大器增益大約 10dB~20dB 左右,前節已經介紹過幾個接受 機的架構,而圖3.1 為基本接收機必要的元件,一般濾波器皆會以 50Ω 當設計匹配,旨 在使訊號通過,干擾減少,為了達到良好功率傳輸,低雜訊放大器也需達到良好的輸入 匹配(相對於 50Ω),而往往第一級電晶體尺寸的選擇影響匹配的好壞以及雜訊指數的大 小,尺寸的決定也同時決定功率消秏和增益,所以不大可能既會有極小的雜訊又同時有 極高的增益,必須在每個特性之間做程度上的折衷與取捨。因此如何有效降低雜訊與放 大器之雜訊指數以提升電路之效能並且又有符合系統規格要求,亦是整體收發器設計的 重要課題。 圖3.1 基本接受機架構

§

3-2 電晶體雜訊模型推導[16]

關於CMOS電晶體雜訊模型尚未有完整描述,雖然如此,我們仍可列出以下四種 MOS電晶體雜訊產生機制:

(1) 通道熱雜訊(channel thermal noise)

此雜訊來源是由電子的熱運動所產生,所以可知其值與絕對溫度T有關。實際上, 熱雜訊是直接比例於T,一般等效成輸出並聯雜訊電流源,其功率頻譜密度為: 0 2 4 ) ( d f kT gd i = γ ∆ ,其中gd0為零偏壓時汲極電導值。

(2) 分佈閘極電阻雜訊(distributed gate resistance noise )

在電晶體的閘極佈局時,必須使用多晶矽層(poly),故存在有閘極多晶矽電阻,其 所產生之雜訊可視為一般的電阻性熱雜訊,電阻值為: L n W R R H g = 3 2 , 其中 為多晶矽片電阻,n為多指叉(multi-finger)式佈局之指叉數目,故在設計電路時 可用佈局技巧降低 ,即可降低其雜訊貢獻。 H R g R

(3) 感應閘極電流雜訊(induced gate current noise )

當電晶體受到偏壓而使通道反轉時,通道內部擾動的電荷會經由電容耦至閘極而產 生感應雜訊電流,其雜訊功率頻譜密度為: g kT gg f i δ 4 ) ( 2 = ∆ 。在短通道效應下δ =2γ, 0 2 2 5 ) ( d gs g g C w g = 且因 正比於 ,故此感應電流雜訊並非白色雜訊源,其稱為藍色 雜訊源。經研究發現 與 有關,因此可把 分成與 相關部份 及與 不相關部份 ,且 與 相關係數 ,因此閘極感應雜訊電流可表示為: g g w2 g i id ig id igc id gu i ig id c≈0.395j Correlated g ed Uncorrelat g g

c

g

kT

c

g

kT

f

i

2 2 2|

|

4

)

|

|

1

(

4

)

(

∆

=

δ

−

+

δ

(式3-1)圖3.2 感應閘極雜訊電流示意圖與等效雜訊電流源 (4) 顫抖雜訊(flicker noise) 當電晶體在低頻時,主要呈現的雜訊為顫抖雜訊,由於其雜訊頻譜密度與 f 1 成正 比,故又有 f 1 noise之稱。其發生原因在於電晶體閘極氧化層與矽基板界面存在一個 現象,就是在接面的地方,有許多不連續懸吊的鍵結(dangling bonds),如圖3.13所示, 當電荷載子於介面移動時,某些載子將被隨機捕捉,然後以此能階釋放,使得汲極電流 產生閃爍雜訊。但這並無法像熱雜訊一樣輕易地預測出來,這與氧化層與矽介面之清潔 度有關,也隨著不同的CMOS製程技術而變化。一般而言,顫抖雜訊在頻率大於1MHZ 以上,其影響將遠小於通道熱雜訊,因此在射頻電路的製作上往往忽略其對整體雜訊的 影響。 圖3.3 氧化層與矽基板的不連續鍵結

§

3-3 常用放大器架構簡介[4]

inZ

Z

in (a) 電阻匹配式放大器 (b) 1/gm匹配放大器 inZ

inZ

(c) 並串回授式放大器 (d)源級電感性衰減放大器 圖3-4 常用放大器架構 一 般 而 言 , 放 大 器 有 四 種 常 用 架 構 , 分 別 為 電 阻 匹 配 式 放 大 器(Resistive Termination)Resistive Termination;1/ 匹配式放大器(1/ Termination);並串回授式 放大器(Shunt-series feedback);源級衰減式放大器(Source inductive degeneration) 。以下 將針對這四種架構分析。gm gm

3-3-1

電阻匹配式放大器

使用這種匹配電阻會消耗大量的功率,所以即使輸入匹配狀況很好,LNA 吸收到的功 率卻只有一點點。除此之外,電阻也會產生大量的通道熱雜訊(thermal noise),這種架構 會使整個LNA 的雜訊指數過高。

此架構有以下特性: (i) 適合寬頻匹配

(ii) 高的雜訊指數值( Noise Figure ) (iii) 連接的匹配電阻衰減訊號

3-3-2 1/

gm匹配式放大器

圖 3-4(b)將閘級端接地,從源級端看進去的阻抗等於 1/gm並聯 1/ jw Cgs,若電晶 體操作頻率遠遠小於截止頻率(wT >> w),gm 的值遠大於wC ,故電晶體的gs gm值在某 個範圍裡不太受頻率影響,而且此結構沒有米勒效應,所以讓本身的阻抗和增益有寬頻 的表現。讓1/gm=50Ω,即可完成輸入端的匹配。 以直觀來看,此架構訊號將會從源級走到汲級,所以一般來說,使用 1/ 匹配式 放大器架構雜訊通常會比較高一點,但是目前使用到共源級疊接的架構大部分都比較適 用於窄頻的應用,若要達到寬頻,往往需要加上電感和電容的匹配電路,必需多佔一些 佈局(layout)面積,因此 1/ 匹配式放大器這種架構雜訊指數會稍高一點,但方便用於 寬頻的匹配,不過對於某些通訊系統來說,不利於使用。使用 1/ 匹配放大器架構當 第一級,通常其增益很不高,所以還必須串接放大器來提高整體增益,因此使用 1/ Termination 架構,通常會串接 2 級以上的放大器。 gm gm gm gm 此架構有以下特性: (i) 電晶體的gm值在某個範圍裡不太受頻率影響 (ii) 在寬頻阻抗匹配上有好的特性 (iii) 因為此結構沒有米勒效應,所以讓本身的阻抗和增益有寬頻的表現。3-3-3

並串回授式放大器

此種架構有涉及一顆電阻迴授電路,因此在設計的時候要特別小心,否則很容易產 生振盪。推導過程如下: (1) 此架構小訊號模型圖 1,

V

2,

V

I

2 1,

V

I

1 2,

V

I

2 fR

sR

R

s fR

m gsg v

11

gs m sV

where v

g R

=

+

1I

圖3-5 Shunt-series feedback 小訊號模型 (2)找出 H 參數 1 11 12 1 2 21 22 2*

V

h

h

I

I

h

h

V

⎡ ⎤ ⎡

⎤ ⎡ ⎤

=

⎢ ⎥ ⎢

⎥ ⎢ ⎥

⎣ ⎦ ⎣

⎦ ⎣ ⎦

[ ]

1

1

1

1

f m f m m s m sR

H

g R

g

g R

g

⎡

⎤

⎢

⎥

= ⎢

−

⎥

⎢

+

+

⎥

⎣

R

⎦

(3) 利用 H->S 轉換方程式,找出 S 參數

[ ]

0 0 0 0 0 02

1

1

,

2

1

2(1

)

1

1

f m m s f m m f f m m s m s m sR

g Z

Z

g R

R

g Z

S

g R

R

g Z

Z

g R

g R

Z

g R

⎡

⎤

−

⎢

+

⎥

⎢

⎥

=

∆ =

⎢

⎥

∆

+

−

−

⎢

+

+

⎥

⎢

⎥

⎣

⎦

11 22 0 for S =S = 2 0 1 f m Z Rs R g = −[ ]

0 0 00

1

0

f fZ

R

Z

S

R

Z

⎡

⎤

⎢

+

⎥

⎢

⎥

=

⎢

⎥

−

⎢

⎥

⎢

⎥

⎣

⎦

+

+

若達到理想輸入輸出匹配,則可以找出對應的電阻 值。由[S]矩陣可知當適當的 給定 或 ,即達到寬頻和平坦的增益,而此種架構的唯一的限制是 必須是非零正 數,如果 是負值,系統將會發生振盪,因為這個限制,使得 有一個最低值的限制: f R s R Rf Rs s R gm 0 21 2 0 1 min Z S Z R g gm m f − = = ≥ ,所以電晶體的尺寸必須依據這項規則來做設計。以上討論是 依照操作低頻時的設計概念,在高頻的時候,需把寄生效應考量進去,如開路會有寄生 電容效應,短路時會有電感效應。 此架構有以下特性: (i) 設計上要考慮穩定性問題(ii) 雜訊指數( Noise Figure )不是最小的 (iii) 有好的寬頻表現

3-3-3

源級電感性衰減放大器

源級電感性衰減放大器(Source inductive degeneration)這個名稱的緣由是在源級端

接上一個電感,電感本身的阻值會使電晶體的gm降低, s L m m R g g + = 1 Gm 。 in

Z

L

g sL

gL

SL

gsC

g v

m gs 圖3.6 Inductive Degeneration型LNA之小訊號等效電路圖 如 上 圖 所 推 導 可 知 gs s m gs s g in C L g jwC L L jw Z = ( + )+ 1 + , 為 了 達 到 輸 入 匹 配 , =50Ω,因此 in Z = 50Ω gs s m C L g , ( + )+ 1 =0 gs s g jwC L L jw 。 是寄生電容值,可以從 foundry廠所提供的單位面積電容值可知,所以從上二式可以算出Ls,Lg,這裡有一點要 特別注意,由於LNA是匹配在高頻段區域,Lg算出來很大,非常的佔晶片面積,所以這 個電感通常是Off-chip,但如果加上一個Cd, gs C T s m T s g in C L g jwC L L jw Z = ( + )+ 1 + ,其中 ,讓 ,可以使Lg降低非常多。 d gs T C C C = + Cgs >Cd 由於採用疊接電路設計低雜訊放大器(如圖3.6 所示)時,雜訊主要由輸入級電晶體 所決定,因此探討電晶體所產生之雜訊即可約略推知低雜訊放大器的雜訊指數,但在模 擬時應加入M3電晶體的雜訊貢獻。由上述之雜訊來源可得M2電晶體雜訊模型(在此忽略圖3.7 輸入端電晶體M2的雜訊模型 經過計算所列雜訊源之貢獻後,可得 ) ( 1 T L s Q w R Rs NF α + + + = Rl Rg γ x w0 (式3-2) 其中 0 1 d m g g = α ; (1 ) 5 5 | | 2 1 2 2 2 L L Q Q c x= + + + γ δα γ δα (式 3-3) gs s s g s L C R w R L L w Q 0 0( + ) = 1 = (式 3-4) 由式3-3可知 與 及 均有關係,故必存在一 可使 。另外,由 於在行動通訊中功率消耗為重要課題,因此以下是假設已決定功率消耗為 去求得 及其所對應之 ,將3-3式之 導至 NF (1/QL) QL QL,opt NF = NFopt D P opt L Q , NFopt NF NF(ρ,PD)為: ) , ( 3 1 ) , ( 0 D sat D P P v L w P NF ρ = +γ ρ (式3-5) 其中忽略了分佈閘極電阻(Rg)及閘極電感耦合電阻(Rl)所造成的雜訊。假定ρ<<1, ) , ( PD P ρ 表示如下: 3 4 0 2 0 5 5 | | 2 ) 5 1 ( ) , ( ρ ρ γ δ ρ γ δ γ δ ρ P P c P P P P D D D + + + ≈ ,其中 s 0 sat sat dd R w v V P0 2 3 ε = (式3-6) 因為PD為一個已決定之常數,故變數是ρ,因此欲求NFopt即是求NFmin,故可藉由

) , ( PD NF ρ 之微分求取NFopt,即 ( , ) =0 ∂ ∂ ρ ρ PD NF ,如此即可獲得ρ 之值,再推知opt 及 ,最後代入3-4式可得 如下: opt L Q , opt NF Wopt 1 , 0 ) 3 2 ( − = ox s Lopt opt LC wRQ W (式3-7) 故由3-7式可知,電晶體尺寸的選擇將是設計低雜訊放大器最重要的課程。 此架構有以下特性:

(i) 雜訊指數( Noise Figure )可達到很好的理想值 (ii) 窄頻應用系統上可做到極佳的阻抗匹配 (iii) 設計Lg來達到欲共振的頻率 (iv)可選擇Ls達到阻抗匹配目的 由於整個架構都沒有使用到電阻,就可以達到50Ω匹配,所以雜訊指數是這四個架 構中最低的,但是它只適合應用於窄頻系統,不適合拿來應用在UWB系統。

§3-4 1dB壓縮點(1dB Compression Point)

增益的壓縮與輸入的功率準位有關,當射頻信號輸入功率增加到某一程度時,會使 得輸出功率偏離此線性關係,而會進入飽和,如圖3.8 所示。我們定義當小訊號增益下 降1dB時,稱之為“ 1-dB增益壓縮點(1-dB compression point)”。

Pin (dBm) Pout (dBm) Noise floor Saturation dB iP

,1 dB oP

,1 Dynamic range 1dB compression point mds i P, mds oP

,§3-5 交互調變失真(Intermodulation Distortion)

當輸入端有兩個或兩個以上的信號,同時加入非線性的放大電路時,則在輸出信號 中,將會包含許多附加頻率的信號,是為互調衍生信號,如圖3.9 所示。 ω ω Nonlinear Device 1 ω 1 ω ω2 ω2 2 1 2ω −ω 2ω2−ω1 2 1 ω ω + 1 2ω 2ω2 2 1 ω ω −)

(t

y

圖3.9 非線性系統中的交互調變示意圖 因此,當輸入信號功率大到使輸出功率和第三階互調衍生信號輸出功率相同時,則三階 互調衍生信號將嚴重干擾基頻之輸出信號,此時輸入信號功率的大小稱為輸入三階截止 點(Input Third-order Intercept Point (IIP3)),輸出功率的大小稱為輸出三階截止點(Output Third-order Intercept Point (OIP3))。IIP3的計算方式可參考3-8式。一般而言, 與 的關係大約會相差10dB左右。 dB IP1 IIP3 dBm in dB dBm P P IIP =∆ + 2 3 (式3-8) 2 f 1 f 2 1 2f − f 2f2− f1f

outP

P

∆

圖3.10 Two tone 測試交互調變失真第四章

超寬頻低雜訊放大器架構介紹

§4-1 TSMC 0.18um 1P6M CMOS 製程元件簡介

對於一個電路設計者,首先必須要瞭解到每個元件的特性與模型,方可從這些有限的 元件中設計符合規格的電路。本論文電路設計採用的是國家晶片中心(CIC)所提供的台 積電0.18um 1P6M CMOS 製程,因此在介紹電路設計前,首先介紹 0.18um 1P6M CMOS 製程常使用到之應用於射頻電路相關元件模型的建立。本節內容均參考自TSMC 0.18UM MIXED SIGNAL lP6M SALICIDE 1.8V/3.3V RF SPICE MODEL。

4-1-1 NMOS

電晶體

電晶體在元件佈局上採用多指叉(multi-finger)閘極架構,如圖 4.1 所示,目的在於 降低閘極電阻,以提升元件高頻特性。MOSFET 每一根指叉寬度為可選擇為 1.5~8um, 電晶體通道長度(channel length)為可選擇 0.18~0.5um,而總閘極指叉數目可選擇整數範 圍為1~64,並有電晶體模型相對應。高頻大訊號模型主要是利用 BSIM3v3 模型來模擬 電晶體的直流特性,並加上外接的被動元件以模擬電晶體在高頻時所產生的寄生效應, 整個高頻大訊號模型在模擬的應用中可以視為一個子電路(sub-circuit)的架構。即整個電 晶體可以看成一個子電路,包括了一個BSIM3v3 模型與其他被動的寄生元件。

4-1-2 MIM

電容

TSMC 1P6M 0.18um 製程提供 MIM(metal-insulator-metal)電容,係由絕緣層夾在二層金 屬中間形成電容。而如今製程都可做出Q 值相當不錯的值,至少都大於 100 以上,電容 尺寸上選擇範圍的長和寬為4~30um,長度的大小必大於或等於寬度大小,以 30um×30um 為例其容值 0.951pF。製程提供的電容有分無金屬遮蔽以及有金屬遮蔽二種 電容,有金屬遮蔽的電容其寄生效應較少。其等效電路模型如圖4.2 所示。 (a)無金屬遮蔽電容 (b)有金屬遮蔽電容 圖4.2 MIM 電容佈局示意圖及等效電路模型4-1-3

螺旋式電感

0.18um 製程提供三種螺旋式電感,分別為標準型、對稱型以及有 center-tap 對稱型三 種。本論文僅使用到標準式電感,因為其對稱型多半用於壓控震盪器。以下只就標準式 電感做介紹,標準型電感其感值最小值為0.21nH、最大值為 15.75nH,參數可選擇半徑 範圍30~125um,圈數範圍 0.5~5.5 圈,間隔為 1/4 圈,以及金屬寬度分 6um、9um、15um、 30um 四種,佈局圖及等效電路模型如圖 4.3。

圖4.3 螺旋式電感佈局圖及等效電路模型

4-1-4

電阻

在CMOS製程中,電阻有幾種做法:用SA電阻、PRO電阻、HRI電阻。這三種電阻可使 用的尺寸範圍如圖4.4(a),本論文常使用的電阻為PRO電阻,其佈局圖及等效電路模型 如圖4.4(b),依TSMC 1P6M 0.18um之製程資料,在等效電路的參數,將隨著不同的材質 而變化。 (a)電阻 (b) 電阻佈局及等效電路模型 圖4.4 TSMC 電阻4-1-5

模擬電路所加入實際量測的考量因素

RF Pad 效應之考量 RF Pad 的等效模型如圖 4.5 所示,設計電路時已把 RF Pad 的效應加入。 圖4.5 RF Pad 的等效模型 bondwire 效應考量 鎊線出來到外面金屬,此處可能對電路量測結果有所影響。因鎊線會有電感和電阻的效 應,圖4.6 為鎊線等效參數。圖4.6 鎊線等效參數 傳輸線考量 因鎊線到外面的金屬與外接的偏壓之間,仍會有一段金屬線,這段金屬線會有傳輸線效 應。所以我也把傳輸線效應加入電路內模擬。 量測使用板材:FR4 傳輸線效應參數: W 線寬: 50mil L 長度 : 150 mil 板材厚度: 20mil

§4-2 單頻帶共源疊接(Cascode)低雜訊放大器

在接收機架構中,於帶通濾波器後的第一級通常為低雜訊放大器,使得低雜訊放大 器的雜訊指數主宰了整體接收機鏈路中的雜訊指數,故低雜訊放大器的設計首重於雜訊 指數。另外,射頻收發機前端的外接元件如濾波器(filter)、收發切換開關(T/R switch)、 雙工器(duplexer)一般均以50Ω為標準,為了不影響濾波器的頻率響應,因此CMOS RFIC 中LNA均以50Ω的輸入阻抗為基準。低雜訊放大器設計上常利用電晶體雜訊模型並考量 功率消秏、輸入匹配、雜訊指數、增益等重要參數來設計製作。 如圖4.7 所示,為傳統之共源疊接低雜訊放大器的架構,其中由電晶體 M1 與電阻 提供偏壓;電阻 一般為大電阻,主要是避免RF 訊號洩漏而影響偏壓。疊接架構最大 的好處在於減少米勒效應(Miller effect),將可使得電路的高頻響應因此而提升;疊接的 架構亦可以使得輸入與輸出端的隔離度變佳,因此,輸入與輸出阻抗可較容易與訊號和 負載阻抗達到阻抗匹配。至於此電路的操作原理及電路的重要規格參數將繼續進一步的 探討。 1 R 2 R gL

sL

dL

dC

2R

1R

2

M

1

M

3

M

VDD

_ RF IN _ RF OUT 圖4.7 傳統之共源疊接低雜訊放大器4-2-1

輸入匹配級:

gL

sL

inZ

2

M

圖4.8 共源疊接低雜訊放大器輸入阻抗的探討 利用電晶體小訊號模型並配合KVL 運算可得輸入阻抗為 gs s m gs s g in in in C L g C j L L j I V Z = = + + +ω

ω

( ) 1 ( 式 4 - 1 ) 一般通常將輸入阻抗匹配至50Ω,即Zin = 50Ω,因此可知 gs g s L C L w ) ( 1 + = 且 m gs s g C L = 50 。亦即利用電感Ls 將輸入阻抗的實部項匹配至 50Ω,輸入阻抗的虛部項則 由適當給電感值Lg 來消除。若由 Smith 圖亦可加以分析並了解其中的物理意義,如圖 4.9 所示。g

L

sL

inZ

2

M

g 串聯電感L g Z gZ

圖4.9 由 Smith 圖觀點探討源疊接低雜訊放大器輸入阻抗§4-2-2

輸出匹配級:

由Smith 圖分析,如圖 4.10 所示,只要選擇適當的電感 Ld 與電容 Cd 即可將輸出匹配 至50Ω。 dL

VDD

3

M

Zp dC

_ RF OUT d 串聯電容C d 並聯電感L Zd Zd Zp 圖4.10 由 Smith 圖觀點探討源疊接低雜訊放大器輸出阻抗§4-2-3 增益

gL

sL

inV

C

gsV

gsgmv

gs 圖4.11 等效小訊號模型 如圖4.11 所示,可得轉導為: gs in m in gs m m jwC Z g v v g G = = 。假定已使輸入阻抗匹配至 50Ω(代表Zin = 50Ω),並將 3-2-1 節所得的結論 m gs s g C L = 50 代入,可將之化簡為: s m jwL G = 1 ,因此整體增益 s d d m V L L jwL G A ≈ ( )= 。§4-3 具抑制頻寬外增益功能之帶斥特性超寬頻低雜訊放大器設計

在UWB 的系統規格中,低雜訊放大器最重要的特色就是寬頻。下方列出超寬頻低雜訊 放大器幾個重要特性。 (i) 寬頻的輸入和輸出匹配至50Ω 阻抗(頻寬範圍以常用-10dB 來定義) (ii) 在UWB 頻寬內要求增益的平坦度(一般在 3dB 內) (iii) 盡量低的雜訊指數值 (iv) 功率消秏小 (v) 因UWB 系統所規範發射功率較低,對線性度要求較不高§4-3-1

LC 諧振匹配超寬頻低雜訊放大器 [5]

超寬頻低雜訊放大器的特色是寬頻,包括了寬頻的增益和寬頻的匹配。在前節已經 討論了單頻帶共源疊接(Cascode)低雜訊放大器,但 應用在 UWB 系統其重點是寬頻特 性,以下小節將討論如何達到寬頻機制。圖4.12 為 LC 諧振匹配超寬頻低雜訊放大器。 block C g L s L 1 M 1 L 1 C gs V VDD bypass C d L d R 2 M 3 M 1 R series L Cblock block C out L OUT IN 圖4.12 LC 諧振匹配超寬頻低雜訊放大器4-3-1-1

LC

諧振輸入匹配的原理

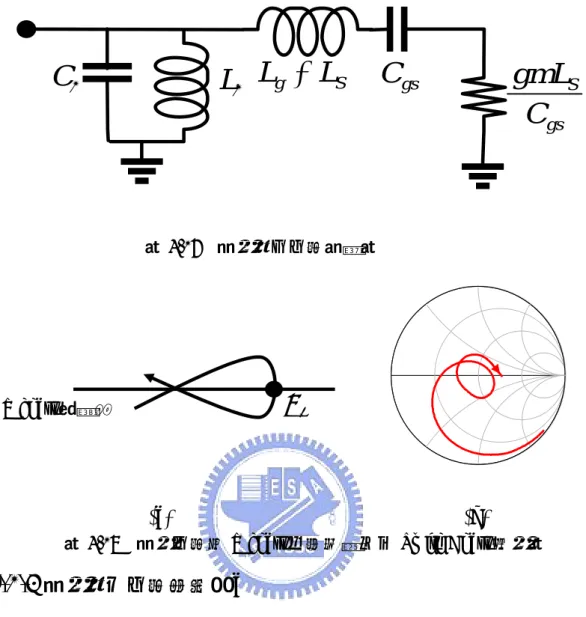

圖4.13 虛線框起來的部份可視為單頻帶共源疊接(Cascode)低雜訊放大器之分析, 可利用電晶體小訊號模型並配合KVL 運算可得輸入阻抗如(4-2)式。 gs s m gs s g in in in C L g C j L L j I V Z = = + + + ω ω( ) 1 ……… (式4-2) (4-2)式輸入阻抗可視為一個的RLC串聯電路,雖然可利用電感Ls將輸入阻抗的實部項 匹配至50Ω,輸入阻抗的虛部項則由適當給電感值Lg來消除。但這是窄頻的設計,圖 4.12運用到LC諧振匹配來達到寬頻的要求,其說明如下。 圖4.14為單頻帶共源疊接(Cascode)低雜訊放大器輸入阻抗的等效RLC串聯電路,適當 設計R約50Ω附近,而對此負載在Smith Chart圖上做一掃頻曲線,箭頭方向代表曲線 由低頻往高頻順時針行走的路徑,這個負載在低頻往高頻是以電容性走向電感性,於Zchart上走勢如圖4.15(a) ,由對稱的關系可知Y chart上走勢如圖4.15 (b)所示。現在我

們加上一個並聯共振腔,其並聯共振腔Y參數阻抗如圖4.16。整體寬頻輸入匹配電路圖

如圖4.17,適當的設計L1、C1的值,可以由共振腔提供Y = − j B f o r ω < ω0 和

0

Y = jB fo r ω > ω 來消除圖4.15(a)負載Y參數Y = jB for

ω ω

< 0和 0Y = − jB for

ω ω

> ,使在Smith Chart上共振頻率ω0前後多二個共振點,上述情形在Y chart上的可能走勢如圖4.18(a),設計S11繞圈路徑在UWB規範頻寬內距Smith Chart中心點<0.316(S11<-10dB),最後電路所得到的S11掃頻圖如圖4.18(b)。 g L s L 1 M 1 L 1 C in Z s L

m s gs g L C g s

L

+

L

C

gs 圖4.14 輸入阻抗之等效串聯RLC電路圖(a)

Z

chart

(b)

Y

chart

圖4.15 輸入負載於Smith Chart的掃頻圖 圖4.16 並聯共振腔Y參數負載 0

for

Z

=

jX

ω ω

>

inductive

0ω

0for

Y

=

jB

ω ω

<

capacitive

0ω

0for

Z

= −

jX

ω ω

<

capactive

Y

= −

jB

for

ω ω

>

0inductive

1

L

1C

0 0 01

1

1

(

1

1

1

0

for

for

Y

j C

j

C

j L

L

Y

at

Y

jB

Y

jB

ω

ω

ω

ω

ω ω

ω ω

ω ω

=

+

=

−

=

=

= −

<

= +

>

)

g S

L

+

L

1L

1C

C

gs S gsgmL

C

圖4.17 寬頻輸入匹配電路圖 Y chart實數軸(a) (b)

圖4.18 寬頻匹配於Y chart可能走勢以及Smith Chart掃頻圖