國 立 交 通 大 學

電信工程學系

碩 士 論 文

2.4-GHz 低功率接收機與應用於 60-GHz 發

射機之 CMOS 電路

2.4-GHz Low-Power Receiver and 60-GHz Transmitter CMOS

Circuits

研究生:陸熙良

指導教授:孟慶宗

2.4-GHz 低功率接收機與應用於 60-GHz 發射機

之 CMOS 電路

2.4-GHz Low-Power Receiver and 60-GHz Transmitter CMOS

Circuits

研究生:陸熙良 Student: Hsi-Liang Lu

指導教授:孟慶宗 博士 Advisor: Dr. Chinchun Meng

國 立 交 通 大 學

電信工程學系碩士班

碩士論文

A Thesis

Submitted to Department of Communication Engineering College of Electrical and Computer Engineering

National Chiao Tung University In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In

Communication Engineering

July 2009

Hsinchu,Taiwan, Republic of China 中華民國九十八年九月

2.4-GHz 低功率接收機與應用於 60-GHz 發射機

之 CMOS 電路

學生:陸熙良 指導教授:孟慶宗 博士 國立交通大學 電信工程學系碩士班摘 要

本篇論文設計並實現適用於無線個人區域網路的射頻積體電路。主 要會依頻段分成兩大部份:第一部份針對現今較為成熟的 ISM band,討 論並比較各種低功率的技術,再實現兩種不同的 2.4-GHz 低功率接收 機。第二部份則是實現出適用於 60-GHz 頻段的高品質元件電路。 論文首先會對於各種低功率的技術作研究,並且探究常見於直接降 頻接收機的被動混頻器,其顫動雜訊的成因。再利用 TSMC 0.18-μm CMOS 製程來實現一個結合被動混頻器的 2.4-GHz 低功率接收機,以及 結合次臨界導通偏壓技術的 2.4-GHz 低功率接收機。 高頻電路的部份,利用 TSMC 0.13-μm CMOS 製程,實現各種不同 架構的 60-GHz 次諧波升頻混波器,並提出變壓器形式的巴倫來作輸出 結合。為了提供良好的 30-GHz 本地震盪訊號源,還設計了一個結合三 線耦合器的正交相位振盪器,可達到 0.6V 低壓操作,功率消耗 7.6mW, 且 FoM 為-203.6dBc/Hz。CMOS Circuits

Student:Hsi-Liang Lu Advisor:Chinchun Meng

Department of Communication Engineering National Chiao Tung University

Abstract

In this thesis, the radios which are suitable for Wireless Personal Area Network (WPAN) applications are designed and implemented. The thesis consists of two parts. The first part focuses on studying various low-power techniques and realizes two different 2.4-GHz low-power receivers. The second part implements high quality component circuits which are suitable for 60-GHz band applications.

First, we study different low-power techniques. Because the passive mixer is a common component of a direct-conversion receiver, we also investigate the flicker noise of passive mixers. Then, we implement a 2.4-GHz low-power receiver with passive mixers, and a 2.4-GHz low-power receiver with subthreshold biasing technique. Both chips are implemented in TSMC 0.18-μm CMOS technology.

Second, we implement different types of 60-GHz sub-harmonic upconverters in TSMC 0.13-μm CMOS technology, and propose transformer-type balun to combine RF signal. In order to provide good LO source, we design a QVCO using three-line coupler. This QVCO operates at 0.6V, and consumes 7.6mW. And the FoM is -203.6dBc/Hz.

誌謝

兩年的碩士生涯,毫無意外的迅速度過。能完成這本論文,要感 謝的人真的很多。首先感謝孟慶宗教授當初的不離不棄,讓我這個從 電控系來的學生能有機會接觸射頻積體電路設計。再來感謝特地抽空 來參與學生口試的呂學士教授、張志揚教授以及鍾世忠教授,老師們 在口試中所提出的問題以及提拔都讓學生銘記在心。而在晶片的量測 過程中,要感謝國家奈米元件實驗室全體同仁的協助,特別是汶德、 志華、榮彥、書毓四大護法,仰賴四位專業的量測技術,而且幾乎每 次都會配合我加班才能取得這些得來不易的數據,實在是萬分感激。 兩年來和我一同奮鬥的 918 實驗室夥伴,因為你們讓我成長許 多。最要感謝的是博士班的金詳學長,不管是修課討論,研究想法的 提供,計畫的討論以及量測的陪伴,幾乎每個環節都給予我很大的幫 助;聖哲學長樂觀積極的態度,給予我許多處事上的啟示;宏儒學長 告訴我多看論文的重要,對我的研究生涯幫助很大;珍儀學姐不定時 的關心,讓人感受到實驗室的溫馨。也非常感謝碩士班的威宇學長, 常與我分享你特殊的人生經歷,並且在我低潮時給我許多鼓勵;揚鮮 學長的聰明才智是我的學習榜樣,更是打球的好伙伴;宜蓁學姊給予及愛笑的個性,常帶給大家歡樂;宜珊學姊的認真,是我們學習的楷 模。還要感謝同屆的大維、欣怡、泰麟,陪我一起打拚兩年。其中特 別感謝大維在我兩次生日都送上了蛋糕,令我非常感動。當然也要感 謝實驗室的學弟妹:智凱、忠佑和嘉苓,你們都相當有趣,為我的實 驗室生活增添許多樂趣。 最後要感謝的還是我的父母,妹妹和爺爺,感謝你們賦予我樂觀 積極、不輕易被擊倒的個性,並且在精神上以及經濟上給予我許多支 持,讓我無後顧之憂的取得碩士學位。在此將本論文的榮耀獻給所有 關心我的人們。 陸熙良 謹於 Lab918, 交通大學 2009 年 9 月

目錄

中文摘要 i 英文摘要 ii 誌謝 iii 目錄 v 表目錄 vii 圖目錄 viii 第一章 導論 1 1.1 研究動機 2 1.2 論文組織 3 第二章 低功率接收機 4 2.1 前言 5 2.2 系統架構比較與選擇 6 2.3 現存的低功率技術之探討 6 2.3.1 低電流操作 7 2.3.2 低電壓操作 10 2.3.3 硬體重複使用 18 2.4 考量功率消耗之低雜訊放大器設計 20 2.5 主動混頻器和被動混頻器的比較 24 2.5.1 被動混頻器的顫動雜訊 25 2.5.2 次臨界導通混頻器 322.6 實作一,Low-Power Low-Noise Direct-Conversion Receiver with Passive Mixers(CMOS 0.18-μm) 33 2.6.1 研究動機 33 2.6.2 架構設計考量 33 2.6.3 增益分析 35 2.6.4 熱雜訊分析 37 2.6.5 顫動雜訊分析 40 2.6.6 電路設計 53 2.6.7 晶片量測結果 57 2.6.8 結果與討論 60

2.7 實作二,Low-Power Low-Noise Direct-Conversion Receiver with Subthreshold Biasing Techniques(CMOS 0.18-μm) 62

2.7.1 研究動機 62

2.7.5 結果與討論 76 第三章 60-GHz 發射機之元件電路設計 79 3.1 前言 80 3.2 60-GHz 次諧波升頻混波器之分析 81 3.2.1 主動式次諧波升頻混波器 81 3.3.2 高頻正交相位之產生 86 3.2.3 輸出 combiner 89 3.3 實作一,60-GHz stacked-LO 次諧波升頻混波器(CMOS 0.13-μm) 96 3.3.1 研究動機 96 3.3.2 電路設計 96 3.3.3 晶片量測結果 100 3.3.4 結果與討論 104 3.4 實作二,60-GHz 具有時間延遲補償的 stacked-LO 次諧波升頻混波 器(CMOS 0.13-μm) 107 3.4.1 研究動機 107 3.4.2 電路設計 107 3.4.3 晶片模擬與部份量測結果 110 3.4.4 結果與討論 113 3.5 實作三,60-GHz leveled-LO 次諧波升頻混波器(CMOS 0.13-μm) 114 3.5.1 研究動機 114 3.5.2 電路設計 114 3.5.3 晶片量測結果 115 3.5.4 結果與討論 120 3.6 30-GHz 正交相位壓控震盪器(CMOS 0.13-μm) 121 3.6.1 研究動機 121 3.6.2 電路設計 121 3.6.3 晶片量測結果 129 3.6.4 結果與討論 132 第四章 結論 135 參考文獻 138 Vita 144

表目錄

表 2.1 切換轉導級混頻器和一般主動混頻器之比較 17

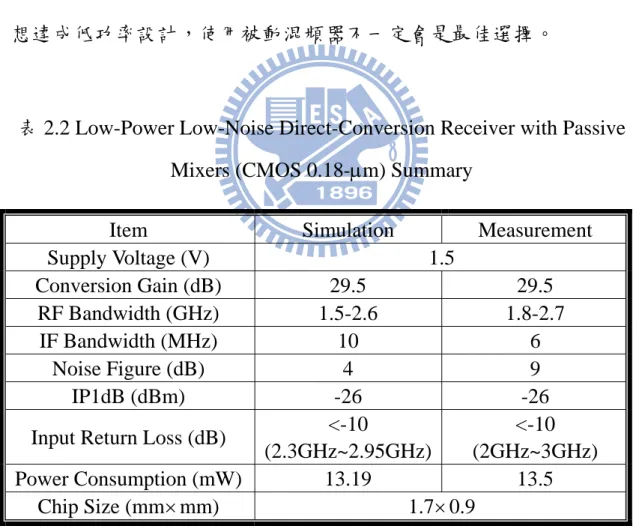

表 2.2 Low-Power Low-Noise Direct-Conversion Receiver with Passive Mixers (CMOS 0.18-μm) Summary 61

表 2.3 Low-Power Low-Noise Direct-Conversion Receiver with Subthreshold Biasing Techniques (CMOS 0.18-μm) Summary 77

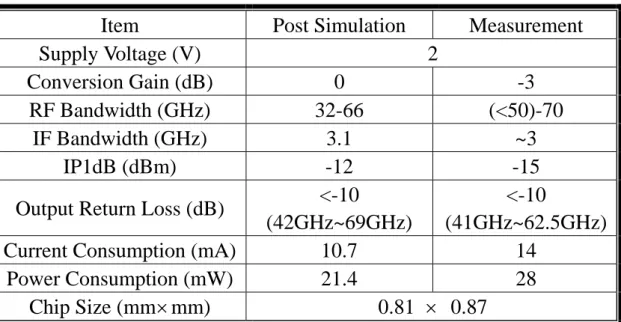

表 2.4 實作一與實作二之比較表 2.4-GHz 低功率接收機文獻比較表 77 表 2.5 2.4-GHz 低功率接收機文獻比較表 78 表 3.1 60-GHz stacked-LO 次諧波升頻混波器整體特性表 105 表 3.2 升頻混波器之文獻比較表 106 表 3.3 60-GHz stacked-LO 具有時間延遲補償的次諧波升頻混波器整 體特性表 113 表 3.4 60-GHz leveled-LO 次諧波升頻混波器整體特性表 120 表 3.5 30-GHz 正交相位壓控振盪器整體特性表 133 表 3.6 高頻正交相位壓控振盪器文獻比較表 134

圖目錄

圖 1.1 無線通訊標準發展層次示意圖 2 圖 2.1 模擬 120μm/0.18μm NMOS 電晶體之 fT, gm/Id, gm and rds 9 圖 2.2 模擬 120μm/0.18μm NMOS 電晶體之 gm and rds 9 圖 2.3 折疊式混頻器 11 圖 2.4 應用於折疊切換式混頻器之轉導器 11 圖 2.5 電流重複使用之交流耦合、折疊切換級混頻器 14 圖 2.6 利用 NMOS 轉導級和 CMOS 反相器當開關之雙平衡式切換轉 導級混波器 14 圖 2.7 假設 ON 和 OFF 的切換時間τsw相同,會出現在切換轉導級混 頻器之波形 15 圖 2.8 低雜訊放大器和混頻器之結合 19 圖 2.9 低雜訊放大器、混頻器和振盪器堆疊成的 LMV cell 20 圖 2.10 源極電感退化低雜訊放大器 21 圖 2.11 考慮功率消耗之低雜訊放大器 22 圖 2.12 比較切換電流的雙平衡式主動混頻器和切換電壓的被動 FET 混頻器 26 圖 2.13 描述電壓切換模式的被動混頻器之關閉重疊(OFF overlap)和開 啟重疊(ON overlap)模式 27 圖 2.14 一連串脈衝之雜訊所造成的切換時間擾動模型。在開啟重疊 (ON overlap),這個脈衝串具有 2fLO的週期,然而在關閉重疊 (OFF overlap),它的週期是 fLO 28 圖 2.15 操作在次臨界導通的混頻器 32 圖 2.16 低功率、低雜訊直接降頻接收機詳細電路圖 35 圖 2.17 系統概念圖 36 圖 2.18 被動混頻器等效成切換電容(switch-capacitor)電路 39 圖 2.19 主動混頻器示意圖 40 圖 2.20 單平衡式主動混頻器 41 圖 2.21 週期穩態電路模型 45 圖 2.22 gm( )

t 和gds( )

t 的線性分段近似 46 圖 2.23 LNA 和電流模式被動混頻器之示意圖 51圖 2.24 LNA 和電流模式被動混頻器操作在 OFF overlap 模式 51

圖 2.25 低雜訊放大器電路圖 54

圖 2.29 轉換增益對 RF 頻率 57 圖 2.30 轉換增益對 RF 功率 58 圖 2.31 輸入返回損耗 58 圖 2.32 IF 頻寬和雜訊指數 59 圖 2.33 雜訊指數(不同偏壓狀況) 59 圖 2.34 Die Photo ( 1.7mm × 0.9mm ) 60 圖 2.35 結合次臨界導通偏壓技術的接收機電路 64 圖 2.36 考量功率消耗的低雜訊放大器 66 圖 2.37 低雜訊放大器模擬圖(50ohm load) 67 圖 2.38 低雜訊放大器模擬圖(非 50ohm load) 69 圖 2.39 負載共振時的低雜訊放大器示意圖 69

圖 2.40 LC tank 共振頻附近 Smith chart 之變化 69

圖 2.41 次臨界導通主動式混頻器電路圖 70 圖 2.42 次臨界導通可變增益放大器電路圖 71 圖 2.43 次臨界導通可變增益放大器之負載小訊號等效模型 72 圖 2.44 轉換增益對 LO 功率 73 圖 2.45 轉換增益對 RF 頻率 73 圖 2.46 輸出功率對 RF 功率 74 圖 2.47 轉換增益對 RF 功率 74 圖 2.48 輸入返回損耗 75 圖 2.49 Die Photo ( 1.1mm × 0.9mm ) 75 圖 3.1 60-GHz 發射機架構 81

圖 3.2 (a) stacked-LO (b)leveled-LO 次諧波混頻器之簡化架構 82

圖 3.3 Stacked-LO 升頻混波器的 switching function 83

圖 3.4 Leveled-LO 混頻器之電流示意圖 84

圖 3.5 Stacked-LO 架構和 level-LO 架構所需之 LO power 比較圖 85

圖 3.6 RC-CR 正交相位產生器與 LR-CR 正交相位產生器 87 圖 3.7 利用變壓器作 combiner 之示意圖 90 圖 3.8 利用鼠徑分合波器作 combiner 之示意圖 92 圖 3.9 馬爾尚巴倫之模擬示意圖 93 圖 3.10 馬爾尚巴倫和 1:1 變壓器之示意圖 94 圖 3.11 馬爾尚巴倫和 1:1 變壓器之模擬圖 94 圖 3.12 變壓器型式巴倫之 3D 圖 95 圖 3.13 變壓器型式巴倫之示意圖 95 圖 3.14 60-GHz stacked-LO 次諧波升頻混波器整體電路圖 96 圖 3.15 四分之一波長耦合器示意圖 98

圖 3.18 變壓器形式之巴倫 3D 圖 99 圖 3.19 轉換增益對 LO 功率 100 圖 3.20 轉換增益對 RF 頻率 100 圖 3.21 輸出功率對 IF 功率 101 圖 3.22 轉換增益對 IF 功率 101 圖 3.23 轉換增益對 IF 頻率 102 圖 3.24 IP1dB 對 RF 頻率 102 圖 3.25 IIP3 對 RF 頻率 103 圖 3.26 輸出返回損耗 103 圖 3.27 Die Photo (0.81mm × 0.87mm ) 104 圖 3.28 60-GHz 具有時間延遲補償的 stacked-LO 次諧波升頻混波器電 路圖 107 圖 3.29 混頻器 cell 的時間延遲問題 108 圖 3.30 時間延遲補償的分析圖 109 圖 3.31 四分之一波長耦合器 3D 圖 109 圖 3.32 轉換增益對 LO 功率 110 圖 3.33 轉換增益對 RF 頻率 110 圖 3.34 轉換增益對 IF 頻率 110 圖 3.35 轉換增益對 IF 功率 111 圖 3.36 2LO-to-RF isolation 對 RF 頻率 111 圖 3.37 LO-to-RF isolation 對 RF 頻率 111 圖 3.38 輸出返回損耗 112 圖 3.39 Die Photo (0.97 mm × 0.9 mm) 112 圖 3.40 60-GHz leveled-LO 次諧波升頻混波器電路圖 114 圖 3.41 轉換增益對 LO 功率 115 圖 3.42 轉換增益對 RF 頻率 116 圖 3.43 轉換增益對 IF 頻率 116 圖 3.44 轉換增益對 IF 功率 117 圖 3.45 2LO-to-RF isolation 對 RF 頻率 117 圖 3.46 輸出返回損耗 118 圖 3.47 輸出功率對 IF 功率(不同 RF 頻率) 118 圖 3.48 轉換增益對 IF 功率(不同 RF 頻率) 119 圖 3.49 Die Photo (0.97 mm × 0.8 mm) 119 圖 3.50 各種不同的正交訊號產生回授方式 123 圖 3.51 各種不同的振盪器回授方式 124 圖 3.52 30-GHz 正交相位振盪器整體電路圖 124

圖 3.55 輸出功率量測結果 129 圖 3.56 頻率和輸出功率對 Vtune 的量測結果 129 圖 3.57 Phase noise 量測結果 130 圖 3.58 相位雜訊對頻率作圖 130 圖 3.59 旁帶消除比對 Vtune 作圖 131 圖 3.60 旁帶消除比 131

圖 3.61 Die Photo (die size:1.1 mm × 0.8 mm,QVCO core size:0.18 mm × 0.45 mm) 132

第一章

1.1

研究動機

IEEE 電機及電子工程師協會綜合數百名業內之專家學者意見, 以涵蓋之區域大小為基準,訂出了無線通訊標準發展層次示意圖,如 所示。該圖包括了從個人區域網 PAN(Personal Area Network)的 IEEE 802.15標準到本地區域網 LAN(Local Area Network)的 IEEE 802.11 標準、都市區域網 MAN(Metropolitan Area Network)的 IEEE 802.16 標準,直至提議中的廣域網 WAN(Wide Area Network)的 IEEE 802.20 標準[1]。 圖(1.1) 無線通訊標準發展層次示意圖 近年來,如家電控制、監控設備控制、保全設備控制等,以小資 料量無線傳輸為主的應用,其需求逐漸增加。以上的應用皆屬於短距 離無線傳輸的範疇,也就是適用於 WPAN 這個標準。儘管以目前 ISM 頻段來看,上述應用大多已有產品問世,但是因為更換電池不易,如 何降低功率消耗以提高產品的方便性,仍舊是電路設計者努力追求的 目標。因此在本論文第二章探討各種現有的低功率技術,並實現了兩 種適用於 ISM 頻段的2.4-GHz 低功率接收機。 然而,ISM 頻段因為頻道擁擠,難以達到高資料傳輸速率。可是 隨著高品質、大容量的影音檔案逐漸普及,如何能無線傳輸這些高品

質的影音資訊,成為研究無線通訊系統等公司或學校的一大挑戰。 UWB 是之前有機會達到高資料傳輸的一種通訊標準,但是近幾年尚 未有產品問世。反觀60-GHz 頻段的通訊標準,在2009年5月,由 Atheros, Broadcom 等知名公司組成的 WiGig 無線技術聯盟,以 60-GHz 頻譜規格來發展無線技術,期望建立傳輸速度達到1Gb 的無 線網路技術。因此60-GHz 電路的研究具有一定的前瞻性。所以在本 論文的第三章,針對60-GHz 頻段,研究並實現了兩種適用於60-GHz 發射機的 CMOS 元件電路。

1.2

論文組織

本篇論文將利用 TSMC 0.18 μm CMOS 以及 TSMC 0.13 μm CMOS 製程技術來設計晶片。本論文分為四個章節,第一章為導論, 說明了研究動機與論文組織。第二章為低功率接收機,介紹各種低功 率的技術,以及被動混頻器的顫動雜訊成因,並實作兩種2.4-GHz 低 功率接收機。第三章為適用於60-GHz 發射機系統的元件電路,實現 各種60-GHz 次諧波升頻器,並提出了變壓器形式的巴倫作的輸出結 合。此外,為了提供此升頻器所需的30-GHz 本地震盪訊號源,結合 三線耦合器實現一個正交相位振盪器。第四章則對上述的所有電路設 計與實作結果做個結論與比較。第二章

2.1

前言

隨著後 PC 時代的來臨,許多電器設備皆朝向可攜式無線通訊設 備發展,因此短距離的無線通訊標準也因而被制定且逐漸佔有重要的 地位。IEEE 制定適用於短距離的無線通訊標準是無線個人區域網 WPAN(Wireless Personal Area Network)標準,諸如家庭娛樂網路、汽 車無線應用、遊戲機連線、PC 無線周邊、消費性電子、家庭保全監 控、工業環境監控以及個人醫療照護,都是屬於此技術的應用。以上 應用,可能由於更換電池不易,或是因為大量使用導致更換電池不 便,會特別需要低功率操作。本章節所實現的電路,就是以低功率為 目標去設計。 低功率的設計,針對不同的規格以及應用上的要求,可以從系統 架構的選擇出發,到電路設計層面,各種電路區塊皆有許多低功率的 技術可供運用與結合,權衡雜訊及線性度等各種不同的特性,方可決 定各子電路的架構。 本章節先比較適用於低功率消耗的系統架構,接下來探討現存的 幾大類低功率消耗技術,並針對不同的電路區塊,分別研究其低功率 設計和其他特性的關係。最後討論實作及量測的結果。

2.2

系統架構比較與選擇

傳 統 的 接 收 機 設 計 , 有 三 種 一 般 常 見 的 架 構 : 超 外 差 (super-heterodyne) 架 構 , 低 中 頻 (low-IF) 架 構 和 直 接 降 頻 (direct conversion)架構。由於超外差架構可以提供良好及穩定的特性,現代 最先進的手持裝置中,超外差架構是最廣泛被使用的架構。但是,對 超外差架構而言,其中一個主要的缺點就是為了解決鏡像訊號問題, 需要用許多晶片外(off-chip)的表面聲波(SAW)濾波器,使得超外差接 收機架構難以達到高度積體化,進而提高了成本。若要解決鏡像訊號 的問題,又希望可以盡量將系統整合在一個晶片上,可以採用威福 (Weaver)鏡像消除架構、哈特利(Hartley) 鏡像消除架構或是直接降頻 架構。前兩者為低中頻(Low-IF)架構,第三者為零中頻(Zero-IF)架構。 其中威福(Weaver)鏡像消除架構是雙降頻(dual conversion)架構,不僅 有第二鏡像訊號問題,還需要多一級降頻器,相對於另外兩種架構, 功率消耗較大。因此適用於低功率接收機的架構,常用的是哈特利 (Hartley)架構和直接降頻(direct conversion)架構。

2.3

現存的低功率技術之探討

低功率之技術,主要可以分成以下三大類:(1)低電流操作,(2) 低電壓操作和(3)硬體重複使用,以下將分別對這三大類技術做探討。2.3.1 低電流操作

低電流操作,可以藉由將電路偏壓在次臨界導通(subthreshold)區 域來達成。次臨界導通偏壓已經是個標準的低功率設計技術,被廣泛 的應用於類比電路的設計。和一般偏壓在強反轉區相比,將 MOSFET 偏壓在次臨界導通主要的優點,可以大幅增加轉導對偏壓電流比。次 臨界導通運作也已經實現在供應電壓低於電晶體臨界電壓的超低功 率數位電路。操作在弱反轉區(weak inversion region)NMOS 電晶體的汲極電流

D i 可以近似成 exp GS D DO W v i I L kT n q ⎛ ⎞ ⎜ ⎟ ⎜ ⎟ = ⎜ ⎛ ⎞⎟ ⎜ ⎜ ⎟⎟ ⎝ ⎠ ⎝ ⎠ (2.1) 在此 n 是次臨界導通的斜率因子,IDO是製程參數,k 是波資曼 常數,T 是溫度(K),q 是電子的電荷量。電晶體的轉導如下 D m I g nkT q = ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ (2.2) 因為次臨界導通的 MOS 電晶體其元件特性類似雙極性(bipolar) 元件,許多雙極性設計技術(像是跨導線性(translinear)迴路電流模式 電路)就變得有關聯。次臨界導通電路也只需要較低的電壓空間

(voltage headroom),導致更容易利用堆疊技術或是降低供應電壓。若 是當作開關,達到硬切換(hard switching)所需之電壓擺幅也比傳統的 CMOS 電路還低:舉例來說,差動對僅需3kT q/

(

≈78mV)

即可硬切 換(hard switching)。 雖然gm /I 比值高過強反轉區,轉導的絕對值卻小得多。舉例來D 說,一個20μm/0.18μm 的NMOS電晶體,偏壓電流為 3mA且偏壓在 強反轉區,可以提供 9.5mS 的 gm。同樣的元件,當偏壓在弱反轉區 且偏壓電流為39μA,可提供 0.8mS的 gm。如(2.2)式所示,gm無法在 ID固定的狀況下,藉由增加W/L而增加,這點不像強反轉區。然而, 如果電流密度保持固定,gm會隨著 W/L 而線性的增加。若將元件寬 度 (到 240μm)和偏壓電流(到 468μA) 增加 12 倍,gm 會增加至 9.5mS。因此,我們藉由使用更大的主動元件操作在次臨界導通,可 以在更低的電流達到相同的轉導,導致極低的功率消耗。然後可以用 晶片上的電感來自振掉大電晶體所具有之更大的電容。越高的輸出阻 抗也可以幫助增加電壓增益。 在次臨界導通區的fT也比強反轉區低很多,而且公式如下 1 1 2 D T js I f WLC kT qπ

= ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ (2.3) js C 是空乏區電容。隨著製程的縮小,次臨界導通的轉換頻率(transition frequency)至今已足以支援許多幾 GHz 的低功率無線應 用。一個 120μm/0.18μm 的 NMOS 電晶體,模擬出來的 fT,gm/Id,gm 和 rds分別如圖(2.1)及圖(2.2)。 100u 1m 10m 0 10 20 30 40 50 60 g m /I d ( S/A) & f T (GHz) Id (A) gm/Id (S/A) fT (GHz) 圖(2.1) 模擬 120μm/0.18μm NMOS 電晶體之 fT, gm/Id, gm and rds。 100u 1m 10m 0 10 20 30 40 50 60 gm (mS) rds (kΩ) r ds (k Ω ) & g m (m S ) Id (A) 圖(2.2) 模擬 120μm/0.18μm NMOS 電晶體之 gm and rds。

除了轉導的減少,次臨界導通的 CMOS 電晶體也會遭受更大的 元件雜訊。通道雜訊,正比於 gm,是強反轉區主要的元件雜訊來源。 當閘極-源極電壓(v )下降至低於臨界電壓,感應出的閘極雜訊會開GS 始主宰整體的元件雜訊。由於高感應閘極雜訊,NFmin 在次臨界導通 會高幾分貝。因此,次臨界導通運作或許對於需要非常高靈敏度的應 用不是個可行的選項。

2.3.2 低電壓操作

低電壓操作,大致上有折疊(folded)和順向基極偏壓(forward body biasing)這兩大類方式可以實現。 折疊方式藉由多出來的電流路徑,換取更多的電壓空間,是常見 的低壓操作技巧。應用在設計混頻器時,如圖(2.3)[1]所示,可以分離 轉導級和切換級的電流,針對各級不同的考量去做最恰當的電流分 配,期望達成低雜訊、高增益和高線性度的需求。但是這種作法,常 常會需要額外的電流,造成多餘的功率消耗。圖(2.3) 折疊式混頻器[1] 但是如圖(2.3)的混頻器,其轉導級為四顆電晶體之堆疊,還是不 易達到低電壓操作。在此先比較各種轉導級,再討論其他作法[2]。 圖(2.4) 應用於折疊切換式混頻器之轉導器 如圖(2.4)所示,輸入級的轉導器可以概分為這幾種架構。最簡單

的轉導器如圖(2.4) (a),使用一個 NMOS,負載端放電阻。由 NMOS 產生的交流電流 In,和流經切換級的電流(Is)與流經電阻的電流(Ir)作 分流。事實上,此轉導器的缺點是:有部份的交流電流流經電阻 R。 為了減少 Ir,電阻的阻值要加大。結果造成 A 點的直流偏壓要特別注 意,得保持足夠高,才能使電晶體仍然能保持在飽和區。對低電壓操 作來說,這個問題會很大。然而負載端放電阻這種轉導器,其缺點可 以藉由負載端放主動負載來改善[見圖(2.4)(b)]。藉由替換電阻成 PMOS 電晶體,會由於 PMOS 電晶體的高輸出阻抗,使得經過此電 晶體的交流電流(Ip)會被大幅減少。使用 PMOS 電晶體,不只可以增 加端點 A 和 VDD 之間的阻抗,還可以用來放大射頻訊號。使用這種 方法,理想上可以完全避免交流電流經過 PMOS 輸出阻抗洩漏至交 流地。因此,還可使用 CMOS 反相器來當轉導器[見圖(2.4)(c)]。在 CMOS 反相器中,基於電流重複使用的原則,射頻訊號可藉由 PMOS 電晶體放大。這是個可以達到高增益,低雜訊指數且低功率消耗的有 效率方法。交流電流 Is等於交流電流 In和 Ip的總和。基於上述理由, 全部的轉導為 gmn+gmp,在此 gmn是 M1 的轉導且 gmp是 M2 的轉導。 在對使用 CMOS 反相器之折疊式混頻器作更進一步的分析之前,先 檢查最低的可操作供應電壓是多少。這是由電晶體 M1 和 M2 的臨界 電壓(Vt)及過驅動電壓(overdrive voltage)所決定。M1 的過驅動電壓

(Vovn)和 M2 的過驅動電壓(Vovp)可以分別表示成 ovn rfcdc t ovp dd rfcdc t V V V V V V V = − = − − (2.4) rfdc V 是應用於電晶體 M1 和 M2 的閘極電壓。最後,這可以使此 混頻器運作的最小的供應電壓(Vdd,min)為 ,min 1 2 2 dd ov ov t V =V +V + V (2.5) 在 0.18-μm CMOS 中,典型的 Vt值大概在 500mV 左右。由上式, 很清楚的得知最低供應電壓會超過 1V。這是將 CMOS 反相器應用至 低壓操作的折疊式混頻器之轉導級,會造成的最大缺點。 為了去克服這個限制,NMOS 和 PMOS 電晶體的偏壓必須要分 開。因此我們可以使用交流耦合的互補式轉導級[見圖(2.4)(d)]。若 Vrfdcn是 M1 電晶體的偏壓,且 Vrfdcp是 M2 電晶體的偏壓,最小可供 應電壓 Vdd,min將會變成 ,min 1 2 2 dd ov ov t rfdcp rfdcn V =V +V + V +V −V (2.6) 選擇 Vrfdcn大於 Vrfdcp,Vdd,min可減少。結合交流耦合的互補式轉 導級、切換級和負載電阻,可以得到具有電流重複使用之交流耦合折 疊式切換混頻器,如圖(2.5)。此電路可以低壓操作,並且具有低功率 的特性,還可以提供高增益,適當的雜訊指數,以及適當的線性度。

圖(2.5) 電流重複使用之交流耦合、折疊切換級混頻器[2] 低壓操作還有另一種特殊的作法,就是將圖(2.3)的架構,射頻(RF) 訊號和本地震盪(LO)訊號的輸入埠對調,如圖(2.6)[3]。 圖(2.6) 利用 NMOS 轉導級和 CMOS 反相器當開關之雙平衡式切 換轉導級混波器[3] 此電路能低壓操作的關鍵,是避免在 VDD 和 VSS 之間,需要一

吃電壓空間的特性來達成。因此,將開關接在 VDD 和 VSS 之間,放 在第一級作切換級,不僅需要較低的電壓空間,且避免了閘極氧化層 的可靠度問題,可以達到低壓操作,轉換增益也和傳統的混波器差不 多,雜訊的表現也很具競爭力。基本上此種型態的混波器,其切換級 的電晶體和 LO 埠是共模造成的雜訊是共模雜訊,可以被差動輸出消 除。 分析此混頻器前,如同[4]的分析,我們假設切換級的 ON 及 OFF 切換時間相同,且使用類似梯形(tapezoid-like)的轉導來作混頻器輸入 大訊號 LO 運作時之模型,可參考圖(2.7)。 τsw τ sw 圖(2.7) 假設 ON 和 OFF 的切換時間

τ

sw相同,會出現在切換轉導 級混頻器之波形接下來深入分析後可知,轉換增益可以表示成

(

)

0 sin 2 2 LO sw L m LO sw f R CG g fπ

τ

π

π

τ

⎛ • ⎞ • • ⎜ • ⎟ ⎝ ⎠ (2.7) 在增益方面,此種混頻器跟傳統的吉伯特混頻器擁有相同的轉換 增益。熱雜訊部份的分析,可以得到下式(

, 0)

0 SSB,SwGm 2 2 2 0 1 2 m G g Gm m m L m s r g g R NF c c g Rγ

α

α

+ + = + (2.8) 而傳統的吉伯特混頻器之熱雜訊如下式(

)

2 , 0 0 , SSB,Gm+Sw 2 2 2 0 1 2 4 4 m m G g Gm m m G Sw g Sw Sw L m s r g g G r G R NF c c g Rγ

α

γ

α

+ + + + = + (2. 9)其中,轉導,雜訊超過因子(noise excess factor)和轉導級的閘極

電阻分別由gm0,

γ

Gm和rg Gm, 來代表。 若拿兩式和相比,會發現切換轉導器的混波器的熱雜訊比傳統的 混波器少了GSw這項,這點即可反映出由開關電晶體和 LO 埠產生的 共模雜訊輸出電流,取差動輸出可以消去。 再針對顫動雜訊(flicker noise)來看,先討論切換轉導器的混頻 器,其轉導級貢獻的顫動雜訊。若我們以等效時變的輸入雜訊電壓 源,串聯在轉導級電晶體的閘極,來作為顫動雜訊(flicker noise)的模 型,這個雜訊電壓藉由每個轉導器,會交替的乘以 0 和gm0[見圖(2.7)]。以一個理想的方波假設來簡化分析:由於方波的傅立葉級數 之直流項為1/2,一半的顫動雜訊(flicker noise)能量『保持』在基頻, 然而另一半會被混頻並出現在諧波項附近。輸出的雜訊也會交替的由 1 m g 和gm2產生[見圖(2.6)],如此會有不相關(uncorrelated)的顫動雜訊

(flicker noise)。整體來說,和傳統轉導級固定偏壓在VB的 MOSFET

差動對相比,顫動雜訊(flicker noise)只有下降3分貝。因此,和傳統 主動混頻器的轉導級相比,切換轉導器的混頻器之轉導級元件會表現 出更嚴重的顫動雜訊(flicker noise)。 傳統的主動混頻器中,切換元件也會貢獻嚴重的顫動雜訊(flicker noise),特別是操作在很高的 LO 頻率。相比之下,切換轉導器的切 換元件有可忽略的顫動雜訊(flicker noise),因為共模雜訊可以取差動 輸出被消除。以上所述整理於表2. 1。 表2. 1 切換轉導級混頻器和一般主動混頻器之比較 特性 切換轉導級 轉導級+切換級 最大的轉換增益 gm0•2 /

π

gm0•2 /π

LO峰值電壓 VGS switch, VDS Gm, +VGS switch, 轉導級的熱雜訊 ∝ gm0 ∝ gm0 轉導級的顫動雜訊 只有一部分混頻上去 混頻上去 切換元件的雜訊 共模雜訊 (可被消去) 差動雜訊最後,低壓操作還可用順向基極偏壓(forward body biasing)的方 式,此種方式是根據下述原理:已知 MOS 由於基板效應,Vt可以表 示成

(

)

0 2 2 t t SB F F V =V +γ

V +φ

−φ

(2.10) 藉由改變VSB的大小,可以達到改變臨界電壓的目的。若電晶體 的臨界電壓可以下降,即可達到低壓操作的目的。此種作法的缺點在 於,會多出額外的一個偏壓,而且順向基極偏壓可能會使 MOSFET 的源極對基極之接面導通,產生一個和基極電壓成指數關係的直流電 流,導致額外的功率消耗及可能的閂鎖效應(latch-up),因此在設計上 要多加注意。2.3.3 硬體重複使用

在電路整合時,另一種節省功率的有效方式便是硬體重複使用(hardware reuse),實現的方法為電流重複使用(current reuse)或是將電

路區塊結合。電流重複使用又可以稱為堆疊(stack),儘管可以節省電

流的使用,但是電壓空間會因此受限,易導致線性度不佳。電路區塊 結合的話也是類似電流重複使用的想法,不過除了有線性度問題之 外,各級之間的洩漏訊號問題要特別小心。

(Gilbert mixer),只是在輸入轉導級作阻抗匹配以及最佳雜訊點匹配。 因此,這個電路和傳統的吉伯特混頻器(Gilbert mixer)相比,主要是多 出許多電感來換取雜訊方面的改善。 圖(2.8) 低雜訊放大器和混頻器之結合 上述電路也可結合折疊技術,類似圖(2.3),將混頻器移至另一條 電流路徑,再將轉導級作阻抗匹配,使轉導級達到類似低雜訊放大器 的功用[1]。 為了追求更低的功率消耗以及更低的成本。可以將低雜訊放大 器、混頻器和振盪器結合在一起,形成 LMV cell[6],如圖(2.9)。圖(2.9) 只有振盪器部份需要使用一個電感,面積大幅縮減,但是這樣產生出 的LO不是正交相位。不過若是針對 802.15.4這個規格的應用,其對 鏡像消除的要求不高,可以在RF級使用其他的架構來完成正交相位 的產生。

圖(2.9) 低雜訊放大器、混頻器和振盪器堆疊成的LMV cell

2.4

考量功率消耗之低雜訊放大器設計

對整個接收機系統來說,低雜訊放大器通常是功率消耗最大的一 個元件,如何降低低雜訊放大器的功率消耗成為很重要的問題,先從 一般的低雜訊放大器設計出發,再思考是否有方法能在不太影響雜訊 和增益表現的情況下,降低功率的消耗。一般的LNA 設計,可以加 入源極電感Ls來同時達到輸入阻抗及雜訊匹配[7],如圖(2.10)所示。 根據[7],可知雜訊參數如下 0 n n m R R gγ

α

= = (2.11)0 0 1 Re

opt opt s opt s

gs Z Z sL Z m sL sC ⎡ ⎤ = − = ⎣ ⎦− − (2.12)

(

2)

0 2 1 1 5 min min T F Fω γδ

cω

= = + − (2.13)(

)

(

)

2 0 2 2 2 1 5 5 1 1 5 5 1 opt gs j c c Z C c cδ

δ

α

α

γ

γ

α δ

δ

ω

α

γ

γ

⎛ ⎞ + ⎜ + ⎟ − ⎝ ⎠ = ⎧ ⎛ ⎞ ⎫ ⎪ + + ⎪ ⎨ ⎜ ⎟ ⎬ − ⎝ ⎠ ⎪ ⎪ ⎩ ⎭ (2.14) 在設計上如果想降低電流消耗,但是電流密度不可以過低,以免 雜訊指數最小值暴增,可以選用小電晶體 size。參考(2.11)-(2.14)式,如果選用過小的電晶體size,Cgs會過小,使得 Re[Zopt]過高;此外,

如果操作頻率過低,

ω

會過小,同樣也會使得 Re[Zopt]過高。在Cgs變小的狀況下,如果還想要達到輸入阻抗匹配,則Ls要放大,但是過

大的Ls會使得(2.13)式中的Fmin失去意義,且Fmin會大幅上升。

因此,若希望降低功率消耗,卻又不希望Cgs過小,使得 Re[Zopt] 過高,可以在輸入級電晶體的閘極和源極之間多加一個電容 Cex,如 圖(2.11)。 圖(2.11) 考慮功率消耗之低雜訊放大器 根據[7],可知此低雜訊放大器之雜訊參數如下 0 n n m R R g

γ

α

= = (2.15)(

)

(

)

2 2 2 2 5 5 1 5 5 1 t gs opt s t gs gs C j c C c Z sL C C c C cδ

δ

α

α

γ

γ

α δ

δ

ω

α

γ

γ

⎛ ⎞ + ⎜⎜ + ⎟⎟ − ⎝ ⎠ = − ⎧ ⎛ ⎞ ⎫ ⎪ + + ⎪ ⎜ ⎟ ⎨ ⎜ ⎟ ⎬ − ⎪ ⎝ ⎠ ⎪ ⎩ ⎭ (2.16)(

2)

0 2 1 1 5 min min T F Fω γδ

cω

= = + − (2.17) 其中 Ct=Cgs+Cex。由上三式可知,Rn和 Fmin不會隨著外加的 Cex(

)

(

)

2 2 2 2 5 1 Re[ ] 5 5 1 Re[ ] opt t gs gs s c Z C C c C c Zδ

α

γ

α δ

δ

ω

α

γ

γ

− = ⎧ ⎛ ⎞ ⎫ ⎪ + + ⎪ ⎜ ⎟ ⎨ ⎜ ⎟ ⎬ − ⎪ ⎝ ⎠ ⎪ ⎩ ⎭ = (2.18)(

)

2 2 2 5 Im[ ] 5 5 1 Im[ ] t gs opt s t gs gs s C j c C Z sL C C c C c Zδ

α

γ

α δ

δ

ω

α

γ

γ

⎛ ⎞ + ⎜ ⎟ ⎜ ⎟ ⎝ ⎠ = − ⎧ ⎛ ⎞ ⎫ ⎪ + + ⎪ ⎜ ⎟ ⎨ ⎜ ⎟ ⎬ − ⎪ ⎝ ⎠ ⎪ ⎩ ⎭ = (2.19) 1 Im[ ]= Im[ ] in s t s Z sL sC Z + = − (2.20) Re[ ]= Re[ ] m s in t s g L Z C Z = (2.21) 現今的先進CMOS 製程參數,會使得(2.19)式約等於(2.20)式。因 此(2.20)式可以省去,也就是說,只要給定 Ls值,Im[Zin]≈ −Im[Zs]。 接下來由(2.18)式和(2.21)可知,(

2)

5 1 s T t c L Cδ

α

γ

ωω

− ≈ (2.22) 未加入Cex的時候,Ls如下(

2)

5 1 s T gs c L Cδ

α

γ

ωω

− ≈ (2.23) 可明顯看出外加Cex後,可以在縮小Cgs的情況下,需要的Ls也 不會因此放大,有機會在低頻的情況下達到低功率操作。除此之外, 參考圖(2.11),Zin =s L(

g +Ls)

+1/ sC( )

t +ω

tLs,故外加Cex還可以使Lg 變小。在2.4GHz這種頻段的應用,Lg通常都具有需要相當大的感值, 若是實現在矽製程上,其寄生的阻抗相當可觀,這個阻抗會成為雜訊 貢獻的主因之一,因此外加的Cex若能減少Lg,對於雜訊指數也可能 會有改善的效果。可是過大的Cex會減少等效的截止頻率,進而降低 增益,因此Cex的值要慎選。2.5

主動混頻器和被動混頻器的比較

主動混頻器和被動混頻器,就字面上的意義來看,最大的差異就 是主動混頻器有增益,可幫助抑制後級的雜訊貢獻,而被動混頻器沒 有。但是被動混頻器沒有直流功率消耗,具有較佳的線性度,以及較 低的顫動雜訊(flicker noise),在實際使用上也有其優勢。 本章節討論的是低功率的應用,若以0.18μm 製程來實現2.4GHz 的接收機為例,使用傳統的主動混頻器,希望有適當的增益、頻寬、 線性度、和雜訊表現,大概需要 1mA 左右的電流消耗,不易符合低接收機造成嚴重困擾。因此,不具直流功率消耗的被動混頻器似乎是 個不錯的選擇,且其顫動雜訊也較小,但是其顫動雜訊的成因需要仔 細去探討。適合低功率操作的混頻器還有次臨界導通混頻器,和傳統 主動混頻器相比,只要一半不到的電流即可具有適當的增益、頻寬和 線性度,但是雜訊的問題會更為嚴重。以下將討論被動混頻器的顫動 雜訊成因和次臨界導通混頻器的操作原理。

2.5.1 被動混頻器的顫動雜訊

主動混頻器出現在輸出的顫動雜訊和LO切換級的偏壓電流成正 比[8],這或許暗示了沒有偏壓電流的被動混頻器,其輸出端就沒有 顫動雜訊。因此有人會誤以為被動混頻器不具有顫動雜訊。然而事實 卻不然,不需要任何偏壓電流流過 LO切換級,顫動雜訊仍然會出現 在訊號的頻率附近[9]。 在探討顫動雜訊之前,先比較主動混頻器和被動混頻器運作上的 差異。見圖(2.12),主動式吉伯特混頻器用差動對切換訊號電流,然 而被動混頻器可以說是切換訊號電壓。其實被動混頻器可以依據其輸入輸出阻抗的不同,分成電壓模式(voltage mode)和電流模式(current

圖(2.12) 比較切換電流的雙平衡式主動混頻器和切換電壓的被動 FET 混頻器 對於主動混頻器而言,會將電晶體皆偏壓在飽和區(saturation region),藉由外加的LO訊號使切換級的差動對切換RF轉導級輸出 之電流,達到混頻的運作。但是對被動混頻器而言,不管將電晶體偏 壓在關閉區(off region)、飽和區(saturation region)或是三極管區(triode

region),打入適當振幅大小的LO訊號皆可達到混頻的運作。因此,

被動混頻器的運作,可以依據電晶體偏壓操作區域的不同,分成關閉

重疊(OFF overlap),零重疊(zero overlap),和開啟重疊(ON overlap),

圖(2.13) 描述電壓切換模式的被動混頻器之關閉重疊(OFF

overlap)和開啟重疊(ON overlap)模式

重 疊(overlap)是 指 一 個 在 LO 零 交 會 點 附 近 的 時 間 窗 口 (window),在此時兩個具有相同輸出點的 FETs 會處於同一個狀態; 它們不是兩者都開啟(ON),就是兩者都關閉(OFF)。在剩下的 LO 週 期,一個 FET 是開啟,另一個是關閉。由以上描述可知,傳統的主 動混頻器是操作在開啟重疊(ON overlap),因為設計上會把全部的電 晶體偏壓在飽和區,使得在電流轉換區(transition region),差動對的 兩個FETs都開啟(ON)。 重疊的型態會由源極偏壓(或是差動對零交會點的電壓)和閘極 偏壓的相對值決定。見圖(2.12),對NMOS 來說,若VB + >Vt VG,此 混頻器會操作在關閉重疊(OFF overlap)。這是假設 LO電壓的振幅大 於 VB + −Vt VG 。 若VB + <Vt VG, 此 混 頻 器 會 操 作 在 開 啟 重 疊(ON

同的重疊型態,混頻器輸出的雜訊頻譜密度(spectral density)會有很大 的不同。

以下分成開啟重疊(ON overlap)和關閉重疊(OFF overlap)來討論。

(1) 開啟重疊(ON overlap): 見圖(2.12),電晶體 M1 和 M2 偏壓在開啟重疊的時候,其導通 狀態和LO輸入波形的關係如圖(2.14)(a)。將圖(2.14)(a)的兩個圖形重 疊後畫在一起,可以得到圖(2.14)(b)最上方的圖形。 (a) (c) (b) (d) 圖(2.14) 一連串脈衝之雜訊所造成的切換時間擾動模型。在開啟 重疊(ON overlap),這個脈衝串具有2fLO的週期,然而在關閉 重疊(OFF overlap),它的週期是 fLO

接下來使用和主動混頻器相同的分析方式[8]:理想上來說,當 LO 為正,M1 導通且M2 關閉;當 LO為負,M1關閉且 M2 導通。 再來,在閘極包含一個顫動雜訊源來分析。當 FET 開關被有限斜率 的LO訊號驅動,等效在閘極的顫動雜訊(flicker noise)會調變它們開 啟/關閉的瞬間,也就是會提前或延遲零交會點(zero-crossing)發生的 時間。換句話說,這會調變輸出的循環週期(duty cycle),而且經過任 意的循環週期,雜訊會出現在輸出。此雜訊源造成之切換瞬間的調 變,可以由一連串雜訊脈衝來作為雜訊的等效模型(參考圖(2.14),此 為直流輸入的狀況)。這一串脈衝具有 2fLO的週期,而且脈衝的高度 和vin有關。對一個弦波差動輸入vin = Ainsin

ω

int,由脈衝列(impulse train)的頻譜,得到之雙平衡式混頻器的輸出雜訊如下:( )

in(

2)

no n in LO n LO A v v f f nf ST ∞ =−∞ ⎛ ⎞ = ⎜ ± − ⎟ ⎝∑

∓ ⎠ (2.24) S是切換時的斜率,T是VLO( )

t 的週期,vn2( )

f 是一個FET 的閘 極輸入參照(input-referred)雜訊之頻譜密度;在這個情況下,是顫動 雜訊的頻譜密度。對於具有單端振幅為ALO之弦波 LO訊號,(

)

2 2 2 LO G t B ST =π

A − V − −V V (2.25) 顫動雜訊(flicker noise)出現在頻率 fin,2fLO ± fin,…,然而 IF 訊號會出現在 fin − fLO 。廣義來說,顫動雜訊(flicker noise)出現在和 IF訊號不同的頻率,不會侵害到想要的訊號。但是,當 fin =3flO / 2,顫動雜訊會和 IF 訊號會相撞。此外,如果一個很大且不想要的訊號 出現在 fLO + fin或3fLO − fin,它會堆積顫動雜訊(flicker noise)至IF訊 號的附近頻帶。而且混頻器的輸出雜訊正比於輸入訊號。若有很大且 不想要的訊號堆積顫動雜訊(flicker noise)到想要訊號的附近頻帶,那 麼訊號對雜訊比(SNR)會因為不想要的訊號之相對強度而變差。這對 於某些無線接收機造成很大的困擾,因為很大的閉塞訊號(blocking signal)可以存在2fLO附近。 (2) 關閉重疊(OFF overlap): 在此操作模式,會有一小段時間,混頻器的輸出和輸入呈現開

路。當一個 FET開啟,輸出會跟隨此輸入。在關閉重疊(OFF overlap)

期間,負載電容會保持這個輸出。如圖(2.14)所示,對於直流輸入, 只有在 FET 開關開啟的時候,FET 的雜訊才會調變輸出;開關關閉 的時候不會對輸出有影響,並且保持這個輸出。因此,輸出雜訊脈衝 和這一個 FET 有關且隨著頻率 fLO重複,而不是2fLO。對於弦波輸 入,雙平衡式混頻器的輸出雜訊電壓頻譜為:

( )

in(

)

no n in LO n LO A v v f f nf ST ∞ =−∞ ⎛ ⎞ = ⎜ ± − ⎟ ⎝∑

∓ ⎠ (2.26) 現在顫動雜訊(flicker noise)會往輸出端轉換至 fin− fLO,剛好也是 經過降頻後得到的訊號頻率。因此,在關閉重疊(OFF overlap)模式之性電路中,我們習慣藉由傳送訊號之大小來對抗固定的雜訊,如此訊 號對雜訊比(SNR)會隨著提高訊號的大小而改善。然而在此混頻器, 輸出的顫動雜訊(flicker noise)會隨著訊號的增加而上升,這意味著輸 出的訊號對雜訊比(SNR)和輸入訊號無關。這個訊號對雜訊比(SNR) 可以表示為:

( )

1 2 LO out n ST SNR vπ

= (2.27) 當 LO 波形變得更像方波,ST乘積會上升,使得訊號對雜訊比 (SNR)獲得改善;也就是說,在一個接收機,其他元件將會限制最終 的訊號對雜訊比(SNR)。 經過上述的分析,可以有以下的結論:被動混頻器依照輸入和閘 極偏壓的不同,可以在兩種不同的模式下操作。在開啟重疊(ONoverlap)模式下,顫動雜訊(flicker noise)出現的頻率會遠離訊號頻率。

然而,在混頻器的輸出端,若不想要的輸入訊號很大,在某些頻率會

堆積顫動雜訊(flicker noise)到想要的訊號。在關閉重疊(OFF overlap)

模式下,混頻器的輸出端,顫動雜訊(flicker noise)會和想要的訊號相

撞。當雜訊和訊號成正比,輸出的訊號對雜訊比(SNR)會由於顫動雜

訊(flicker noise)而變成常數,只能藉由更像方波的 LO訊號來改善,

2.5.2 次臨界導通混頻器

圖(2.15)是操作在次臨界導通的混頻器。混頻動作是藉由應用射 頻訊號在閘極,本地震盪訊號在源極,再利用次臨界導通電晶體的非 線性指數特性來完成。次臨界元件等式中,使用指數的泰勒級數展開 之二次項,可得此混頻器的轉換增益為(

)

3 2 Mixer 3 1 1 2 Conv. Gain 1 2 DO LO M ds L W I v L kT g n R q ⎛ ⎞ ⎛ ⎞ ⎜ ⎟ ⎜ ⎟ ⎛ ⎞ ⎜ ⎟ ⎜ ⎟ = ⎜ ⎟ ⎜ ⎛ ⎞⎟ ⎝ ⎠ ⎜ + ⎟ ⎜ ⎟ ⎜ ⎜ ⎟⎟ ⎝ ⎠ ⎝ ⎠ ⎝ ⎠ (2.28) 在此vLO是本地震盪訊號的振幅。LO 埠的輸入阻抗很高,單端看 入大概 430Ω,故 LO 訊號擺幅在此架構可以小。因此,振盪器和 LO 緩衝器的驅動需求適當,可以節省很多 LO 產生電路的功率消耗。 圖(2.15) 操作在次臨界導通的混頻器2.6

實作一,Low-Power Low-Noise Direct-Conversion

Receiver with Passive Mixers (CMOS 0.18-

μm)

2.6.1 研究動機

減少可攜式無線通訊設備的電池更換和充電的次數,可以提高使 用上的方便性,因此低功率設計絕對是必須的。為了某些特定的應 用,如無線影音傳輸,雜訊指數的要求也相對嚴格。可是低功率和低 雜訊對於電路設計來說,是互相權衡的。在此藉由架構的選取,並且 結合被動混頻器,設計一操作電壓為 1.5V,電流消耗小於 10mA,雜 訊指數在 IF 為 100kHz 時小於 4dB 的直接降頻前端電路。2.6.2 架構設計考量

低中頻架構和直接降頻架構皆具有可高度積體化的特色,但是以 設計整體接收機電路來看,相較於直接降頻架構,低中頻架構的類比 數位轉換器及基頻電路之操作頻率都會較高,功率消耗也因此較大。 故在此選用直接降頻架構來實現接收機前端電路。 第一級用堆疊式(cascode)低雜訊放大器,其共源級提供高轉導及 低雜訊表現,並結合源極退化電感,希望可以同時達到最佳阻抗匹配 及最佳雜訊匹配。共閘級的部份,可以減少米勒效應,提高頻寬,並 且減少 LO 訊號的反向洩漏。詳細的分析如 2.4 節,在此不再贅述。混頻器的部份,有主動式和被動式兩大種可以選擇,先針對雜訊 問題來考量。實現在 CMOS 製程,儘管其具有低成本的優勢,但是 顫動雜訊會對於直接降頻架構會造成很大的問題。而且接收機系統 中,混頻器通常是顫動雜訊的主要來源之一。因此根據前述分析,選 用被動式混頻器,不僅顫動雜訊貢獻也比較少,且沒有直流功率消耗。 選擇使用被動混頻器而非主動混頻器,線性度也是其中一個重要 的考量。主動混頻器的輸入轉導級,天生就不線性,再由於低雜訊放 大器需要高轉換增益以抑制後方雜訊,會使得主動式混頻器的輸入端 (在幾 GHz 看入是高阻抗)易感受到大電壓擺幅,進而限制了整體系統 的線性度。若使用電壓模式的被動混頻器,因為其負載是高阻抗,可 以減少流經當電晶體導通狀態時的電流,也就是減少流經非線性汲極 -源極電阻的電流。但值得注意的是,當 RF 訊號和降頻過的訊號 (downconverted signals)之震幅變大,在 RF 及基頻埠的電壓擺幅會調 變混頻器的切換,造成額外的失真。因此,本實作採用電流模式被動 混頻器,將被動混頻器的輸出端以低阻抗作負載,以減輕混頻器輸入 端感受到過大電壓擺幅所造成的失真。 為了使混頻器的輸出端看到低阻抗,又希望可以滿足整體接收機 是電壓輸出,故實現了一個轉阻放大器(trans-impedance amplifier)在 混頻器的後方。此轉阻放大器還可以設計成一階主動濾波器,幫助壓

抑 LO 洩漏訊號,並省去額外需要的濾波器,降低成本和功率消耗。 詳細電路如圖(2.16),第一級使用堆疊式(cascode)低雜訊放大 器,接下來交流耦合(AC-couple)至雙平衡式被動混頻器,最後將降頻 後的訊號送至具有一階低通濾波效果的轉阻放大器輸出。 RF_in LOI_n LOI_p LOI_p LOI_n LOQ_n LOQ_p LOQ_n LOQ_p VDD Vref VB OUTI_n OUTI_p VDD Vref OUTQ_n OUTQ_p VB VDD

圖(2.16) 低功率、低雜訊直接降頻接收機詳細電路圖

2.6.3 增益分析[26]

探討增益前,因為整體接收機 I-path 和 Q-path 的電路結構相同, 可針對其中一個 path 來探討,所得之系統概念圖如圖(2.17)。圖(2.17) 系統概念圖 假設 LNA 的轉導是G ,且輸入訊號是弦波,在混頻器輸入電流M 訊號為

( )

sin 2(

)

RF M RF RF i t =G vπ

f t (2.29) 再假設輸入的 LO 電壓訊號也是弦波,( )

sin 2(

)

LO LO LO v t =vπ

f t (2.30) 由vLO( )

t 形成的切換函數S t 為( )

( )

(

)

0 4 1 sin[2 2 1 ] 2 1 LO n S t n f t nπ

π

∞ = = + +∑

(2.31) 我們有興趣的輸出電流,是在 fIF = fRF − fLO這個頻率,故混頻器 的輸出電流可表示為( )

(

)

2(

)

sin 2 sin 2 IF IF IF M RF IF i t iπ

f t G vπ

f tπ

= i = (2.32) 由於轉阻放大器的輸入阻抗為( )

( )

, 2 1 2 f in TIA f f R Z f A fπ

R C ≈ + (2.33) 若 OP 的增益A f 大,也就是說( )

Zin TIA,( )

f 很小,因此整體電壓 轉換增益可近似為( )

( )

2 1 2 f out IF M in RF IF f f R v f G v fπ

jπ

f R C ⎛ ⎞ ≈ ⎜⎜ ⎟⎟ + ⎝ ⎠ (2.34) 其中, f 是 IF 端的輸出頻率,IF fRF是 RF 頻率, 2 /π

和混頻器 的週期時變轉移函數之一次諧波項有關,R 和f C 分別是轉阻放大器f 的回授電阻和電容。2.6.4 熱雜訊分析[26]

輸出端的熱雜訊如下:(

)

(

)

( )

2 2 2 , , 4 0 m n out IF RF g ds f IF V f f = kT gγ

β

Z f Δf (2.35)(

)

( )

2 2 2 2 , ' 4 , ON n out IF RF switches f IF ON ON gm kT R V f f Z f f R R Zβ

= Δ + (2.36)(

)

( )

2 2 2 , , 2 , 1 f IFn out IF RF opamp n opamp

gm Z f V f f V Z = + (2.37)

(

)

2 , 2 4 , 1 2 f f n out IF RF R IF f f kTR V f f f jπ

f R C = Δ + (2.38) 其中,γ

是製程相關因子。β

2是代表切換動作的常數, 2 , n opamp V 是 OP 放大器的輸入參照(input-referred)雜訊電壓,RON是開關的平均電 阻,Zgm是由轉阻放大器往開關看入的等效阻抗,如圖(2.17)。若假設被動混頻器的導通電阻(on-resistance)小, 2

(

)

, , n out IF RF switches V f f 可忽略。 可得整體輸出的熱雜訊電壓為(

)

(

)

( )

( )

2 2 2 , 0 2 2 , , 4 2 4 1 1 2 n out IF RF ds f IF f IF f n opamp gm IF f f V f f kT g Z f f Z f kTR V f Z j f R Cγ

β

π

= Δ + + + Δ + (2.39) 將上式除以整體系統的電壓增益,可以得到輸入參照電壓雜訊為(

)

(

)

( )

( )

( )

( )

( )

2 2 0 2 , 2 2 2 2 2 , 2 2 2 2 2 2 4 , 2 2 1 4 2 2 1 2 ds f IF n in IF RF M f IF f IF n opamp gm f M f IF M f IF IF f f kT g Z f f V f f G Z f Z f V Z kTR f G Z f G Z f j f R Cγ

β

π

π

π

π

Δ = ⎛ ⎞ ⎜ ⎟ ⎝ ⎠ + Δ + + ⎛ ⎞ ⎛ ⎞ + ⎜ ⎟ ⎜ ⎟ ⎝ ⎠ ⎝ ⎠ (2. 40) 若Zf Zgm且定義α

=gm /gds0,(2.42)式可化簡為(

)

( )

2 2 , 2 2 , 2 2 4 , 2 n in IF RF m n amp m gm RF f kT V f f f g V kT f g Z f Rγ βπ

α

π

⎛ ⎞ = ⎜ ⎟ Δ ⎝ ⎠ ⎛ ⎞ ⎜ ⎟ + + Δ ⎜ ⎟ ⎝ ⎠ (2.41) 值得注意的是,當Zgm( )

fRF 變小,整體雜訊上升。 這其實有另一個看法,見圖(2.18),A 點可由 LNA 的負載電容, 混頻器的 push-push 點以及 AC 耦合電容,等效成一寄生電容Cpar。 因 此 , 從 混 頻 器 的 輸 出 端 往 左 看 , 可 以 等 效 成 一 個 切 換 電 容 (switch-capacitor)電路,故Zgm( )

fRF 可以表示成( )

1 4 gm RF LO par Z f f C = (2.42) 由(2.31)式,可將(2.32)式化為(

)

2 2 , 2 2 2 , 2 4 , 2 4 n in IF RF m LO par n amp m m f kT V f f f g f C kT V f g g Rγ βπ

α

π

π

⎛ ⎞ = ⎜ ⎟ Δ ⎝ ⎠ ⎛ ⎞ +⎜ ⎟ + Δ ⎝ ⎠ (2.43) 觀察(2.43)式,可看出操作頻率的上升和雜散電容Cpar的增加, 輸入參照的雜訊電壓也會增加。也就是說,被動混頻器的電晶體大小 不可為了降低雜訊,而無限制的放大以求更低的導通電阻,因為這樣 作會使得Cpar增加。此現象可以由LNA 的負載電感在RF頻率共振掉 寄生電容來改善。 圖(2.18) 被動混頻器等效成切換電容(switch-capacitor)電路2.6.5 顫動雜訊分析

此實作設計的第一級 LNA 作轉導級,將 RF 電流 AC 耦合至被 動混頻器,而被動混頻器之作用如同開關,切換電流以達到降頻效 果。參考主動式混頻器的架構,如圖(2.19),第一級為轉導級,將RF 電流DC 耦合至切換開關級,藉由切換電流的動作達到降頻的效果。 可以發現,儘管此實作是使用被動混頻器,但考慮整體的運作,其實 和主動混頻器是相當類似的。兩者差別在於主動式混頻器的切換級有 直流電流通過,而且轉導級電晶體的汲極直流偏壓會受到切換級的影 響。 圖(2.19) 主動混頻器示意圖 因此,本實作的顫動雜訊成因,可應用主動式混頻器的概念來類 推。以下先討論主動混頻器的顫動雜訊廣義量化分析[11],再推廣至 本實作的狀況。探討主動混頻器的顫動雜訊成因之前,根據 2.5.1 節的定義,主動混頻器也可以根據偏壓狀況,分成開啟重疊(ON overlap)

和關閉重疊(OFF overlap)兩種運作模式。傳統的主動混頻器,所有電

晶體皆偏壓在飽和區,因此操作開啟重疊模式。

有幾種方式可討論主動混頻器的顫動雜訊成因。由於混頻器的元 件,其運作點會隨時間週期性的改變,而且產生在輸出的雜訊也是週

期時變的,因此可以使用線性週期時變(linear periodic time-varying)

系統來當作混頻器雜訊的模型[12]。但是若用以上方式討論雜訊,需 要相當複雜的數值運算。如果假設混頻器為無記憶性(memoryless)元 件,藉由計算混頻器輸出端之時間平均(time-average)雜訊,來求出雜 訊指數[4],或是利用簡單的顫動雜訊形成之物理意義來探討[8],對 於電路設計上都相當有幫助,但是僅適用於低頻。在此探討廣義的線 性週期時變分析法[11],來分析主動混頻器在開啟重疊模式和關閉重 疊模式的運作。 圖(2.20) 單平衡式主動混頻器

討論雙平衡式主動混頻器和單平衡式差不多,但是後者的討論上 會比較簡便,因此以下針對一個單平衡式主動混頻器來討論。見圖 (2.20),接下來的討論都有做出以下的假設:在 ON overlap 或 OFF overlap以外的時間,M3 都偏壓在飽和區;此外,M3在ON overlap 都偏壓在飽和區,然而在 OFF overlap,會漸漸的由飽和區變成三極 管區。如此,M3 在 OFF overlap 的狀態,可以看成一個電阻,會使 Cp放電,導致Vds3最終減少至零。

接下來將混頻器以線性週期時變(linear periodic time-varying,

LPTV)系統來作模型,有別於之前文獻中假設無記憶性(memoryless) 的LPTV 混頻器模型[4],此處的分析有考慮混頻器push-push 點寄生 電容Cp的記憶影響(memory effect)。 見圖(2.20),根據KCL,可以寫出非線性的微分方程式。其中由 於 P 點的寄生電容會和Cgs1、Cgs2、M1 和 M2 的源極接面電容以及 M3 的汲極電容有關,這些電容的特性都會和電壓成非線性關係,破 壞了時變模型的線性假設,還導致分析更為複雜。因此將這些接面電 容近似成時間不變(time--invariant)電容Ceff ,再併入 Cp中作討論。 根據以上假設,接下來,首先要決定LPTV轉移函數,因此將之 前由 KCL 得到的微分方程式作線性化。得到如下的線性小訊號微分 方程式

![表 2. 5 2.4-GHz 低功率接收機文獻比較表 Ref. [18] [19] [20] [21] [22] [23] [24] [25] This work Process 0.18- μm CMOS 0.18- μm CMOS 0.18- μm CMOS 0.18- μm CMOS 0.18- μm CMOS 90nm CMOS 90nm CMOS 0.18- μm CMOS 0.18-μm CMOS P DC (mW) 9 44 16.2 6.3 9 3.6 8](https://thumb-ap.123doks.com/thumbv2/9libinfo/7492543.115389/91.892.126.764.162.869/GHz低功率接收機文獻比較ThisμμCMOSμCMOSCMOSμCMOSCMOSμCMOSCMOS.webp)

![表 3. 2 升頻混波器之文獻比較表 Ref Topology Freq[GHz] LO power [dBm] CG [dB] OP1dB[dBm] LO-RF Iso](https://thumb-ap.123doks.com/thumbv2/9libinfo/7492543.115389/119.892.131.760.177.1074/表32升頻混波器之文獻比較表RefTopologyFreqGHzLOpowerdBmCGdBOP1dBdBmLORFIso.webp)